# RENESAS

# ISL59450

# NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

# DATASHEET

FN7510 Rev 0.00 Feb 14, 2008

Multiformat Video Crosspoint with Integrated Sync Separator

The ISL59450 is a video crosspoint switch supporting multiple video input formats (CVBS, S-Video, YPbPr, and RGB signals). Embedded anti-aliasing filters with programmable corner frequencies eliminate glitch noise from video DACs. The large number of inputs, wide range of The ISL59450 is a video crosspoint switch supporting multiple video input formats (CVBS, S-Video, YPbPr, and RGB signals). Embedded anti-aliasing filters with programmable corner frequencies eliminate glitch noise from video DACs. The large number of inputs, wide range of The ISL59450 is a video crosspoint switch supporting multiple video input formats (CVBS, S-Video, YPbPr, and RGB signals). Embedded anti-aliasing filters with programmable corner frequencies eliminate glitch noise from video DACs. The large number of inputs, wide range of formats, integrated anti-aliasing filters, and dual sync-separators make the ISL59450 an ideal choice for video switching in nearly all display systems.

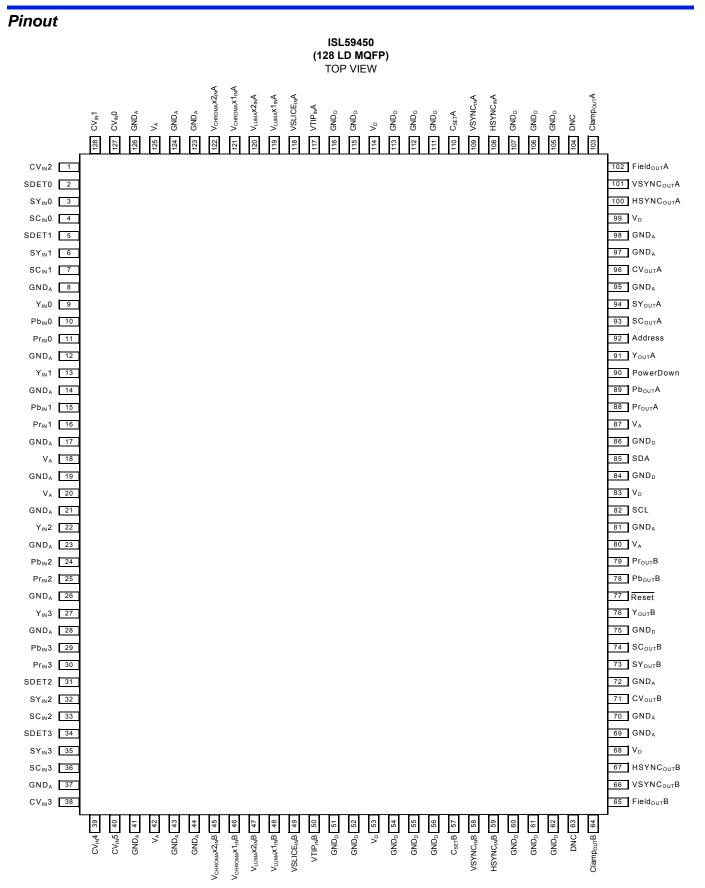

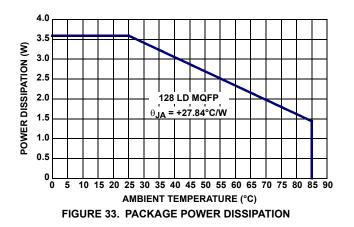

The ISL59450 is available in a 128 Ld MQFP package and is specified for operation over the full -40°C to +85°C temperature range.

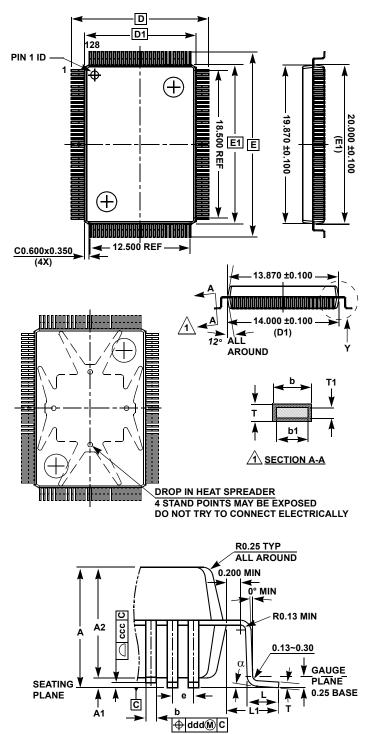

# **Ordering Information**

| PART NUMBER | PART        | PACKAGE     | PKG.    |

|-------------|-------------|-------------|---------|

| (Note)      | MARKING     | (Pb-free)   | DWG. #  |

| ISL59450IQZ | ISL59450IQZ | 128 Ld MQFP | MDP0055 |

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

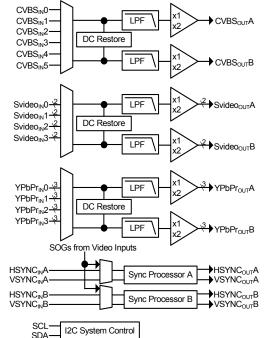

# Simplified Block Diagram

# Features

- · 6 Composite, 4 S-Video and 4 Component Video Sources

- 2 Component Inputs can be Configured for VGA with Separate H and V Sync Inputs

- Multi-format Video Filtering

- · Compatible with Macrovision® Encoded Signals

- Programmable Gain of x1 or x2

- · Outputs have High Impedance Disable Mode

- Two Universal Sync Separators support SD, HD, and Computer Signals

- Pb-free (RoHS compliant)

# Applications

- AV Receivers

- LCD-TVs

- · AV Switch Boxes

- Projectors

- HDTV Systems

- Multiple Video Input Systems

#### Absolute Maximum Ratings

| Voltage on V <sub>A</sub><br>(referenced to GND = GND <sub>A</sub> = GND <sub>D</sub> )6.0V |

|---------------------------------------------------------------------------------------------|

| Voltage on V <sub>D</sub>                                                                   |

| (referenced to GND = GND <sub>A</sub> = GND <sub>D</sub> ) 4.0V                             |

| Voltage on any Analog Input Pin                                                             |

| Voltage on any Digital Input Pin0.3V to V <sub>D</sub> + 0.3V                               |

| Current into any Output Pin                                                                 |

| ESD Classification                                                                          |

| Human Body Model                                                                            |

| Machine Model 125V                                                                          |

#### **Thermal Information**

| Thermal Resistance                               | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| MQFP Package                                     | 27.84                  |

| Maximum Biased Junction Temperature              | +150°C                 |

| Storage Temperature                              | C to +150°C            |

| Pb-free Reflow Profiles                          | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

## **Recommended Operating Conditions**

| Temperature (Commercial) | 40°C to +85°C                                |

|--------------------------|----------------------------------------------|

| Supply Voltage           | V <sub>A</sub> = 5.0V, V <sub>D</sub> = 3.3V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### AC Electrical Specifications

**ns**  $V_A = 5.0V, V_D = 3.3V, V_{IN} = 0.7V_{P-P}, T_A = +25^{\circ}C, R_L = 150\Omega, V_{TIP}INx = 0.5V, VSLICE_{INx} = 0.6V, V_{LUMA}x1_{INx} = V_{LUMA}x2_{INx} = 0.8; V_{CHROMA}x1_{INx} = V_{CHROMA}x2_{INx} = 1.15V$ , all frequency response measurements relative to f = 100kHz, unless otherwise specified.

| PARAMETER     | DESCRIPTION                      | CONDITIONS         | MIN  | TYP  | MAX  | UNIT |

|---------------|----------------------------------|--------------------|------|------|------|------|

| YPbPr/RGB (Co | omponent) Video Inputs           | ÷                  |      |      |      |      |

| YPbPr-10MHz   | Passband Flatness, 10MHz Filter  | f = 6MHz, GAIN 1   | -1.6 | -1.1 | -0.4 | dB   |

|               |                                  | f = 6MHz, GAIN 2   | -1.6 | -1.1 | -0.4 | dB   |

|               | Cutoff Flatness, 10MHz Filter    | f = 10MHz, GAIN 1  | -4.2 | -2.7 | -1.5 | dB   |

|               |                                  | f = 10MHz, GAIN 2  | -4.2 | -2.7 | -1.5 | dB   |

|               | Stopband Rejection, 10MHz Filter | f = 27MHz, GAIN 1  | -30  | -19  | -11  | dB   |

|               |                                  | f = 27MHz, GAIN 2  | -30  | -19  | -11  | dB   |

|               |                                  | f = 54MHz, GAIN 1  |      | -51  |      | dB   |

|               |                                  | f = 54MHZ, GAIN 2  |      | -51  |      | dB   |

| YPbPr-20MHz   | Passband Flatness, 20MHz Filter  | f =12MHz, GAIN 1   | -1.5 | -0.9 | -0.4 | dB   |

|               |                                  | f =12MHz, GAIN 2   | -1.5 | -0.9 | -0.4 | dB   |

|               | Cutoff Bandwidth, 20MHz Filter   | f = 20MHz, GAIN 1  | -3.6 | -2.3 | -1.3 | dB   |

|               |                                  | f = 20MHz, GAIN 2  | -3.6 | -2.3 | -1.3 | dB   |

|               | Stopband Rejection, 20MHz Filter | f = 54MHz, GAIN 1  | -30  | -15  | -9   | dB   |

|               |                                  | f = 54MHz, GAIN 2  | -30  | -15  | -9   | dB   |

| YPbPr-36MHz   | Passband Flatness, 36MHz Filter  | f = 20MHz, GAIN 1  | -1.6 | -1   | -0.4 | dB   |

|               |                                  | f = 20MHz, GAIN 2  | -1.6 | -1   | -0.4 | dB   |

|               | Cutoff Bandwidth, 36MHz Filter   | f = 36MHz, GAIN 1  | -4.7 | -2.7 | -1.5 | dB   |

|               |                                  | f = 36MHz, GAIN 2  | -4.7 | -2.7 | -1.5 | dB   |

|               | Stopband Rejection, 36MHz Filter | f = 108MHz, GAIN 1 |      | -22  |      | dB   |

|               |                                  | f = 108MHz, GAIN 2 |      | -22  |      | dB   |

## **AC Electrical Specifications**

$\begin{array}{l} \mathsf{V}_{\mathsf{A}} = 5.0\mathsf{V}, \, \mathsf{V}_{\mathsf{D}} = 3.3\mathsf{V}, \, \mathsf{V}_{\mathsf{IN}} = 0.7\mathsf{V}_{\mathsf{P}-\mathsf{P}}, \, \mathsf{T}_{\mathsf{A}} = +25^\circ\mathsf{C}, \, \mathsf{R}_{\mathsf{L}} = 150\Omega, \, \mathsf{V}_{\mathsf{TIP}}\mathsf{INx} = 0.5\mathsf{V}, \, \mathsf{VSLICE}_{\mathsf{INx}} = 0.6\mathsf{V}, \\ \mathsf{V}_{\mathsf{LUMA}}\mathsf{x}^{1}\mathsf{I}_{\mathsf{Nx}} = \mathsf{V}_{\mathsf{LUMA}}\mathsf{x}^{2}\mathsf{I}_{\mathsf{Nx}} = 0.8; \, \mathsf{V}_{\mathsf{CHROMA}}\mathsf{x}^{1}\mathsf{I}_{\mathsf{Nx}} = \mathsf{V}_{\mathsf{CHROMA}}\mathsf{x}^{2}\mathsf{I}_{\mathsf{Nx}} = 1.15\mathsf{V}, \, \text{all frequency response} \\ \text{measurements relative to f} = 100\mathsf{kHz}, \, \text{unless otherwise specified.} \ \textbf{(Continued)} \end{array}$

| PARAMETER               | DESCRIPTION                         | CONDITIONS                                                                                   | MIN  | ТҮР  | MAX  | UNIT |

|-------------------------|-------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| YPbPr-Bypass            | Passband Flatness, Filter Bypassed  | f = 220MHz, GAIN 1                                                                           |      | ±1   |      | dB   |

|                         |                                     | f = 220MHz, GAIN 2                                                                           |      | ±1   |      | dB   |

|                         | Cutoff Bandwidth, Filter Bypassed   | GAIN 1                                                                                       |      | 275  |      | MHz  |

|                         |                                     | GAIN 2                                                                                       |      | 275  |      | MHz  |

|                         | Positive Slew Rate, Filter Bypassed | V <sub>OUT</sub> = 2V <sub>P-P,</sub> GAIN 1                                                 | 350  | 450  |      | V/µs |

|                         |                                     | V <sub>OUT</sub> = 2V <sub>P-P,</sub> GAIN 2                                                 | 450  | 590  |      | V/µs |

|                         | Negative Slew Rate, Filter Bypassed | V <sub>OUT</sub> = 2V <sub>P-P,</sub> GAIN 1                                                 | 350  | 440  |      | V/µs |

|                         |                                     | V <sub>OUT</sub> = 2V <sub>P-P,</sub> GAIN 2                                                 | 720  | 950  |      | V/µs |

| S-Video VIDEO           | INPUTS                              |                                                                                              | I    |      |      |      |

| SV-10MHz                | Passband Flatness, 10MHz Filter     | f =7MHz, GAIN 1                                                                              | -2.3 | -1.5 | -0.8 | dB   |

|                         |                                     | f =7MHz, GAIN 2                                                                              | -2.3 | -1.5 | -0.8 | dB   |

|                         | Cutoff Rejection, 10MHz Filter      | f = 11MHz, GAIN 1                                                                            | -5.5 | -3.4 | -2   | dB   |

|                         |                                     | f = 11MHz, GAIN 2                                                                            | -5.5 | -3.4 | -2   | dB   |

|                         | Stopband Rejection, 10MHz           | f = 27MHz, GAIN 1                                                                            | -32  | -21  | -11  | dB   |

|                         |                                     | f = 27MHz, GAIN 2                                                                            | -32  | -21  | -11  | dB   |

| SV-Bypass               | Passband Flatness, Filter Bypassed  | f = 27MHz, GAIN 2                                                                            | -2.3 | -1   | -0.8 | dB   |

|                         | Cutoff Rejection, Filter Bypassed   | f = 54MHz, GAIN 2                                                                            | -12  | -3.6 | -2.5 | dB   |

| CVBS (Compos            | ite) VIDEO INPUTS                   |                                                                                              |      |      |      |      |

| CVBS-7MHz               | Passband Flatness, 7MHz Filter      | f = 5MHz, GAIN 1                                                                             | -2.7 | -1.7 | -1   | dB   |

|                         |                                     | f = 5MHz, GAIN 2                                                                             | -2.7 | -1.7 | -1   | dB   |

|                         | Cutoff Rejection, 7MHz Filter       | f = 7MHz, GAIN 1                                                                             | -5   | -3.2 | -1.8 | dB   |

|                         |                                     | f = 7MHz, GAIN 2                                                                             | -5   | -3.2 | -1.8 | dB   |

|                         | Stopband Rejection, 7MHz Filter     | f = 27MHz, GAIN 1                                                                            | -50  | -39  | -26  | dB   |

|                         |                                     | f = 27MHz, GAIN 2                                                                            | -50  | -39  | -26  | dB   |

| CVBS-Bypass             | Passband Flatness, Filter Bypassed  | f = 27MHz, GAIN 2                                                                            | -1.9 | -1.1 | -0.7 | dB   |

|                         | Cutoff Rejection, Filter Bypassed   | f = 54MHz, GAIN 2                                                                            | -7.2 | -3.8 | -2.7 | dB   |

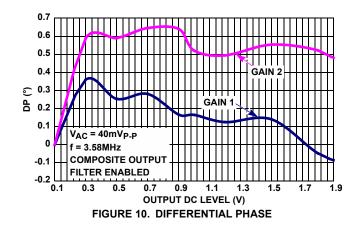

| dG                      | Differential Gain                   | f = 3.58MHz, GAIN 1                                                                          |      | 0.5  |      | %    |

|                         |                                     | f = 3.58MHz, GAIN 2                                                                          |      | 0.3  |      | %    |

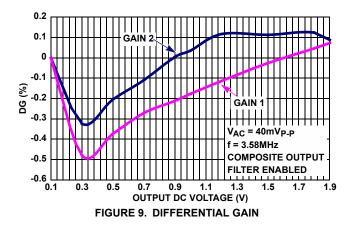

| dP                      | Differential Phase                  | f = 3.58MHz, GAIN 1                                                                          |      | 0.45 |      | ٥    |

|                         |                                     | f = 3.58MHz, GAIN 2                                                                          |      | 0.65 |      | ٥    |

| ALL VIDEO INP           | UTS                                 |                                                                                              |      |      |      |      |

| INTER-X <sub>TALK</sub> | Inter-Channel Crosstalk             | Any input of Channel A to any output<br>Channel B and vice-versa, GAIN 1 and 2,<br>f = 10MHz |      | 85   |      | dB   |

#

| PARAMETER                | DESCRIPTION                                                                     | CONDITIONS                                                                | MIN                        | TYP  | MAX                        | UNIT |

|--------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------|------|----------------------------|------|

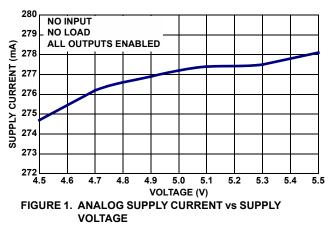

| VA                       | Analog Supply Range                                                             |                                                                           | 4.5                        |      | 5.5                        | V    |

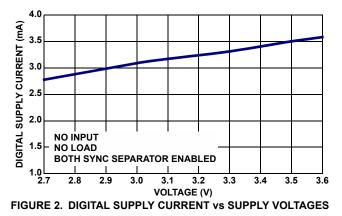

| VD                       | Digital Supply Range                                                            |                                                                           | 2.7                        |      | 3.6                        | V    |

| Ι <sub>Α</sub>           | Analog Supply Current                                                           | All output groups enabled                                                 |                            | 290  | 350                        | mA   |

|                          |                                                                                 | 1 Composite output enabled                                                |                            | 25   |                            | mA   |

|                          |                                                                                 | 1 S-video output group enabled                                            |                            | 48   |                            | mA   |

|                          |                                                                                 | 1 Component output group enabled                                          |                            | 75   |                            | mA   |

| I <sub>D</sub>           | Digital Supply Current                                                          | Both sync separators enabled                                              |                            | 3.5  | 6                          | mA   |

| IDISABLED                | Standby Supply Current                                                          | Disabled Analog Current, I <sub>A</sub>                                   |                            | 0.7  | 3                          | mA   |

|                          |                                                                                 | Disabled Digital Current, ID                                              |                            | 0.7  | 2.5                        | mA   |

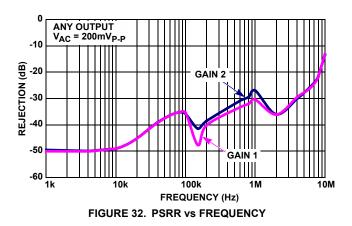

| PSRR                     | Power Supply Rejection                                                          | GAIN 1 or 2, any output                                                   |                            | 50   |                            | dB   |

| PSRR <sub>CLAMP_ON</sub> | Rejection with Clamp Enabled                                                    | GAIN 1 or 2                                                               |                            | 45   |                            | dB   |

| Gain                     | Low Frequency Gain                                                              | GAIN 1                                                                    | 0.95                       | 1    | 1.05                       | V/V  |

|                          |                                                                                 | GAIN 2                                                                    | 1.9                        | 2.0  | 2.1                        | V/V  |

| V <sub>OS-CLAMP</sub>    | Clamp Offset (Delta between external reference voltage and output during clamp) | V <sub>REF</sub> = any reference input, GAIN 1                            | V <sub>REF</sub> -<br>30mV |      | V <sub>REF</sub> +<br>30mV | mV   |

|                          |                                                                                 | V <sub>REF</sub> = any reference input, GAIN 2                            | V <sub>REF</sub> -<br>30mV |      | V <sub>REF</sub> +<br>30mV | mV   |

| V <sub>OS</sub>          | V <sub>IN</sub> - V <sub>OUT</sub><br>(Useful if DC-Coupling)                   | Clamp disabled, A <sub>V</sub> = 1                                        |                            | 0.45 |                            | V    |

| IPULLDOWN                | Input Pulldown Current                                                          | V <sub>IN</sub> = 2V, clamp enabled (sinking)                             |                            | 1    |                            | μA   |

| ICLAMP                   | Clamp Pullup Current                                                            | CV and S-Video, normal offset mode, clamp enabled (sourcing)              | 100                        | 130  | 170                        | μA   |

|                          |                                                                                 | Component/RGB, normal offset mode, clamp enabled (sourcing)               | 220                        | 270  | 320                        | μA   |

|                          |                                                                                 | CV and S-Video, low offset mode, clamp enabled (sourcing)                 | 220                        | 270  | 320                        | μA   |

|                          |                                                                                 | Component/RGB, low offset mode, clamp enabled (sourcing)                  | 400                        | 500  | 650                        | μA   |

| I <sub>SC</sub>          | Short Circuit Current                                                           | VIN = 3V, AV2 = 2.0V, Sourcing, $R_L = 10\Omega$ to GND                   | 60                         | 102  | 140                        | mA   |

|                          |                                                                                 | VIN = 0V, Sinking, $R_L = 10\Omega$ to +3V                                | 20                         | 30   | 40                         | mA   |

| V <sub>OUT-LIN</sub>     | Output Linear Voltage Range                                                     |                                                                           | 0.5                        |      | 2.5                        | V    |

| LOGIC INPUTS (S          | DA, SCL, Address, Reset, PowerDown, H                                           | SYNC <sub>INx</sub> , VSYNC <sub>INx</sub> , SDETx)                       |                            |      |                            |      |

| V <sub>IH</sub>          | Input High Voltage (HIGH)                                                       | All logic pins, except Reset                                              | 2                          |      |                            | V    |

|                          |                                                                                 | Reset (Pin must be >3.5V to ensure part is not resetting)                 | 3.5                        |      |                            | V    |

| V <sub>IL</sub>          | Input Low Voltage (LOW)                                                         |                                                                           |                            |      | 0.8                        | V    |

| IIH                      | Input High Current (VIN = 5V, Logic Inputs,                                     | No pull-up or pull-down                                                   | -1                         | 0    | 1                          | μA   |

|                          | Sinking)                                                                        | Pins with $300k\Omega$ internal pull-downs:<br>Address, Reset, Power-down | 8                          | 17   | 34                         | μA   |

| ۱ <sub>IL</sub>          | Input Low Current (VIN = 0V, Logic Inputs,                                      | No pull-up or pull-down                                                   | -1                         | 0    | 1                          | μA   |

|                          | Sourcing)                                                                       | Pins with 300k $\Omega$ internal pull-up: SDETx                           | 10                         | 15   | 25                         | μA   |

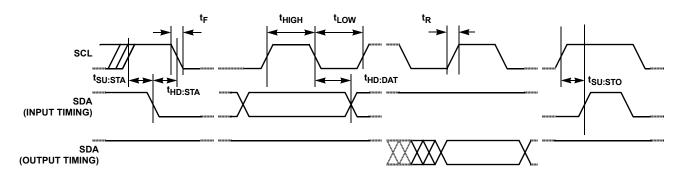

| SYMBOL              | PARAMETER                        | CONDITIONS                                                                                                                         | MIN<br>(Note 1)  | ТҮР | MAX<br>(Note 1) | UNIT |

|---------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----------------|------|

| V <sub>OL</sub>     | SDA Output Buffer LOW Voltage    | I <sub>OL</sub> = 4mA                                                                                                              | 0                |     | 0.4             | V    |

| ILI                 | Input Leakage Current on SCL     | V <sub>IN</sub> = 5.5V                                                                                                             |                  | 0.1 | 1               | μA   |

| ILO                 | I/O Leakage Current on SDA       | V <sub>IN</sub> = 5.5V                                                                                                             |                  | 0.1 | 1               | μA   |

| IING CHARA          | ACTERISTICS                      |                                                                                                                                    |                  |     |                 |      |

| f <sub>SCL</sub>    | SCL Frequency                    |                                                                                                                                    |                  |     | 400             | kHz  |

| tLOW                | Clock LOW Time                   | Measured at the 30% of $V_D$ crossing.                                                                                             | 1.3              |     |                 | μs   |

| t <sub>HIGH</sub>   | Clock HIGH Time                  | Measured at the 70% of $V_D$ crossing.                                                                                             | 0                |     | 0.9             | μs   |

| <sup>t</sup> SU:STA | START Condition Set-up Time      | SCL rising edge to SDA falling edge. Both crossing 70% of $V_D.$                                                                   | 0.6              |     |                 | μs   |

| <sup>t</sup> HD:STA | START Condition Hold Time        | From SDA falling edge crossing 30% of $\rm V_D$ to SCL falling edge crossing 70% of $\rm V_D.$                                     | 0.6              |     |                 | μs   |

| t <sub>HD:DAT</sub> | Input Data Hold Time             | From SCL falling edge crossing 70% of $\rm V_D$ to SDA entering the 30% to 70% of $\rm V_D$ window.                                | 0                |     | 0.9             | μs   |

| tsu:sto             | STOP Condition Set-up Time       | $\begin{array}{c} \mbox{From SCL rising edge crossing 70\% of V_D,} \\ \mbox{to SDA rising edge crossing 30\% of V_D} \end{array}$ | 0.6              |     |                 | μs   |

| <sup>t</sup> R      | SDA and SCL Rise Time            | From 30% to 70% of V <sub>D</sub>                                                                                                  | 20 +<br>0.1 x Cb |     |                 | ns   |

| t <sub>F</sub>      | SDA and SCL Fall Time            | From 70% to 30% of $V_D$                                                                                                           | 20 +<br>0.1 x Cb |     |                 | ns   |

| Cb                  | Capacitive Loading of SDA or SCL | Total on-chip and off-chip                                                                                                         |                  |     | 400             | pF   |

| Cpin                | SDA and SCL Pin Capacitance      |                                                                                                                                    |                  |     | 10              | pF   |

NOTE:

1. Parts are 100% tested at +25°C. Temperature limits established by characterization and are not production tested.

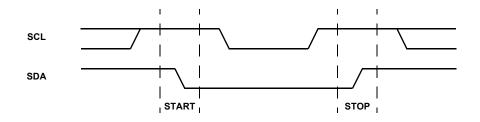

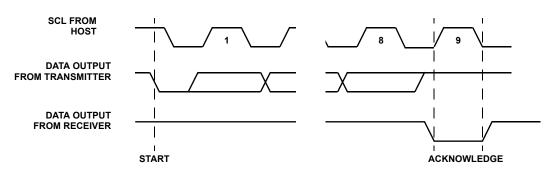

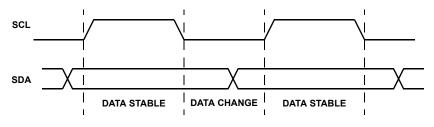

# I<sup>2</sup>C Timing Diagram

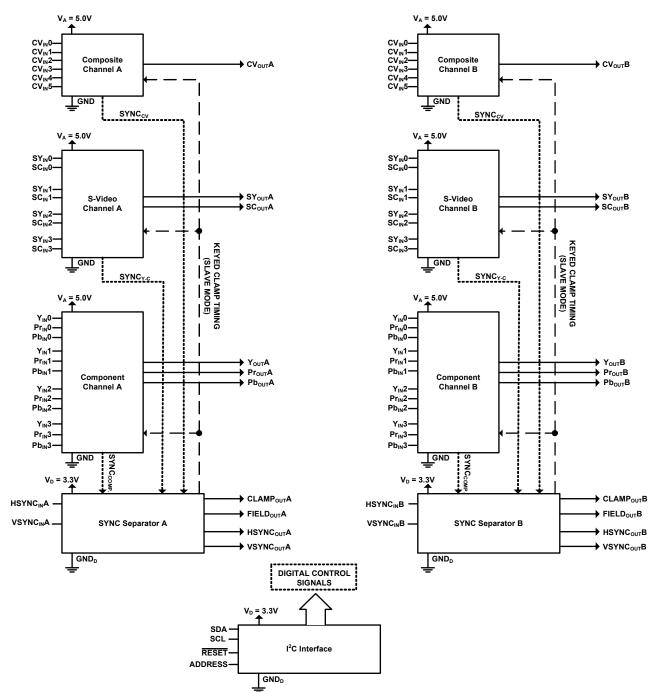

# Functional Diagram

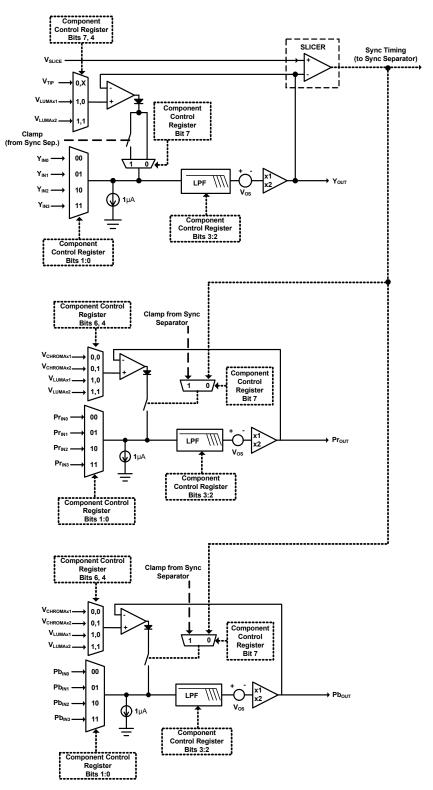

# Component Block Diagram

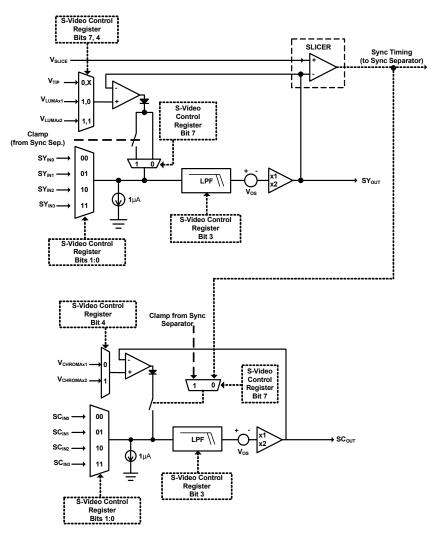

# S-Video Block Diagram

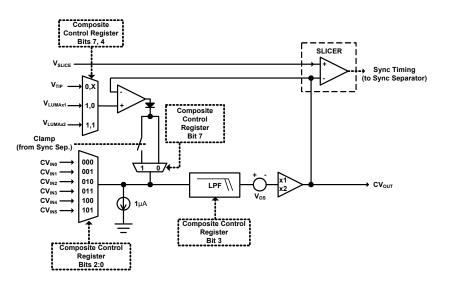

# Composite Block Diagram

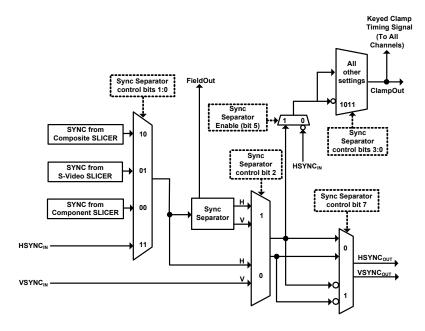

# Sync Separator Block Diagram

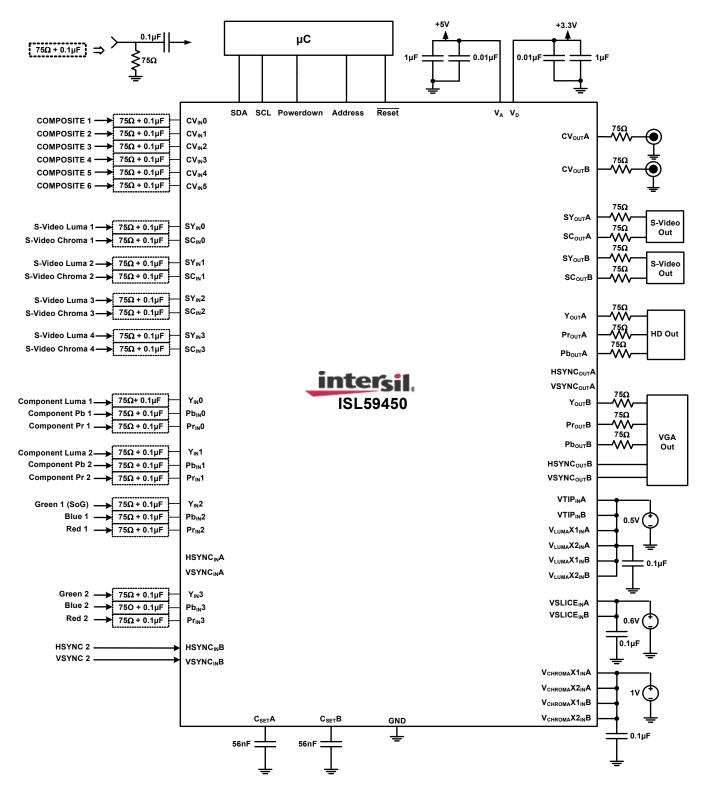

# Typical Application Circuit

# **Pin Descriptions**

| PIN NUMBER   | PIN NAME            | DESCRIPTION                                                                                                                                                                                                                                          |

|--------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPOSITE (  | CV) VIDEO INPUTS    | (6x1)                                                                                                                                                                                                                                                |

| 127          | CV <sub>IN</sub> 0  | Composite Video Input 0                                                                                                                                                                                                                              |

| 128          | CV <sub>IN</sub> 1  | Composite Video Input 1                                                                                                                                                                                                                              |

| 1            | CV <sub>IN</sub> 2  | Composite Video Input 2                                                                                                                                                                                                                              |

| 38           | CV <sub>IN</sub> 3  | Composite Video Input 3                                                                                                                                                                                                                              |

| 39           | CV <sub>IN</sub> 4  | Composite Video Input 4                                                                                                                                                                                                                              |

| 40           | CV <sub>IN</sub> 5  | Composite Video Input 5                                                                                                                                                                                                                              |

| COMPOSITE (  | CV) VIDEO OUTPU     | TS                                                                                                                                                                                                                                                   |

| 96           | CV <sub>OUT</sub> A | Composite Video Output A with High-Z disable mode                                                                                                                                                                                                    |

| 71           | CV <sub>OUT</sub> B | Composite Video Output B with High-Z disable mode                                                                                                                                                                                                    |

| S-VIDEO (SV) | INPUTS (4x2)        |                                                                                                                                                                                                                                                      |

| 3            | SY <sub>IN</sub> 0  | S-Video Luma Input 0                                                                                                                                                                                                                                 |

| 4            | SC <sub>IN</sub> 0  | S-Video Chroma Input 0                                                                                                                                                                                                                               |

| 6            | SY <sub>IN</sub> 1  | S-Video Luma Input 1                                                                                                                                                                                                                                 |

| 7            | SC <sub>IN</sub> 1  | S-Video Chroma Input 1                                                                                                                                                                                                                               |

| 32           | SY <sub>IN</sub> 2  | S-Video Luma Input 2                                                                                                                                                                                                                                 |

| 33           | SC <sub>IN</sub> 2  | S-Video Chroma Input 2                                                                                                                                                                                                                               |

| 35           | SY <sub>IN</sub> 3  | S-Video Luma Input 3                                                                                                                                                                                                                                 |

| 36           | SC <sub>IN</sub> 3  | S-Video Chroma Input 3                                                                                                                                                                                                                               |

| S-VIDEO (SV) | OUTPUTS             |                                                                                                                                                                                                                                                      |

| 94           | SY <sub>OUT</sub> A | S-Video Luma Output A with High-Z disable mode                                                                                                                                                                                                       |

| 93           | SC <sub>OUT</sub> A | S-Video Chroma Output A with High-Z disable mode                                                                                                                                                                                                     |

| 73           | SY <sub>OUT</sub> B | S-Video Luma Output B with High-Z disable mode                                                                                                                                                                                                       |

| 74           | SC <sub>OUT</sub> B | S-Video Chroma Output B with High-Z disable mode                                                                                                                                                                                                     |

| S-VIDEO CON  | NECTION DETECTI     | ON PINS                                                                                                                                                                                                                                              |

| 2            | SDET0               | Digital Input with internal pull-up to $V_A$ . Detects S-Video connector 0. Tie to NC switch on S-Video connector, with other end of switch tied to ground. $0V =$ no cable attached, $V_A =$ S-Video cable attached. 300k pull-up to analog supply. |

| 5            | SDET1               | Digital Input with internal pull-up to $V_A$ . Detects S-Video connector 1. Tie to NC switch on S-Video connector, with other end of switch tied to ground. $0V =$ no cable attached, $V_A =$ S-Video cable attached. 300k pull-up to analog supply. |

| 31           | SDET2               | Digital Input with internal pull-up to $V_A$ . Detects S-Video connector 2. Tie to NC switch on S-Video connector, with other end of switch tied to ground. $0V =$ no cable attached, $V_A =$ S-Video cable attached. 300k pull-up to analog supply. |

| 34           | SDET3               | Digital Input with internal pull-up to $V_A$ . Detects S-Video connector 3. Tie to NC switch on S-Video connector, with other end of switch tied to ground. $0V =$ no cable attached, $V_A =$ S-Video cable attached. 300k pull-up to analog supply. |

| COMPONENT    | (YPbPr) VIDEO INP   | UTS (4x3)                                                                                                                                                                                                                                            |

| 9            | Y <sub>IN</sub> 0   | Luma component (or Green RGB) video input 0                                                                                                                                                                                                          |

| 10           | Pb <sub>IN</sub> 0  | Chroma Pb component (or Blue RGB) video input 0                                                                                                                                                                                                      |

| 11           | Pr <sub>IN</sub> 0  | Chroma Pr component (or Red RGB) video input 0                                                                                                                                                                                                       |

| 13           | Y <sub>IN</sub> 1   | Luma component (or Green RGB) video input 1                                                                                                                                                                                                          |

| 15           | Pb <sub>IN</sub> 1  | Chroma Pb component (or Blue RGB) video input 1                                                                                                                                                                                                      |

# **Pin Descriptions** (Continued)

| PIN NUMBER  | PIN NAME                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16          | Pr <sub>IN</sub> 1                     | Chroma Pr component (or Red RGB) video input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22          | Y <sub>IN</sub> 2                      | Luma component (or Green RGB) video input 2                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24          | Pb <sub>IN</sub> 2                     | Chroma Pb component (or Blue RGB) video input 2                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25          | Pr <sub>IN</sub> 2                     | Chroma Pr component (or Red RGB) video input 2                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27          | Y <sub>IN</sub> 3                      | Luma component (or Green RGB) video input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29          | Pb <sub>IN</sub> 3                     | Chroma Pb component (or Blue RGB) video input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 30          | Pr <sub>IN</sub> 3                     | Chroma Pr component (or Red RGB) video input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| COMPONENT   | VIDEO OUTPUTS                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 91          | Y <sub>OUT</sub> A                     | Component Video Luma Output A with High-Z disable mode                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 89          | Pb <sub>OUT</sub> A                    | Chroma Pb component (or Blue Component) Video Output A with High-Z disable                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 88          | Pr <sub>OUT</sub> A                    | Chroma Pr component (or Red Component) Video Output A with High-Z disable                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 76          | Y <sub>OUT</sub> B                     | Component Video Luma Output B with High-Z disable mode                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 78          | Pb <sub>OUT</sub> B                    | Chroma Pb component (or Blue Component) Video Output B with High-Z disable                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 79          | Pr <sub>OUT</sub> B                    | Chroma Pr component (or Red Component) Video Output B with High-Z disable                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A SYNC SEPA | RATOR INPUTS AN                        | DOUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 108         | HSYNCINA                               | Horizontal External Sync Source for Sync Separator A. This signal may be pure HSYNC or CSYNC.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 109         | VSYNC <sub>IN</sub> A                  | Vertical External Sync Source for Sync Separator A                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 110         | C <sub>SET</sub> A                     | Sync Separator filter capacitor. Connect a 0.056µF capacitor between this pin and analog ground.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 100         | HSYNC <sub>OUT</sub> A                 | Horizontal Sync Output for Sync Separator A                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 101         | VSYNC <sub>OUT</sub> A                 | Vertical Sync Output for Sync Separator A                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 102         | Field <sub>OUT</sub> A                 | Field Flag for Sync Separator A. Low = odd field, high = even field.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 103         | Clamp <sub>OUT</sub> A                 | External Clamp Timing Pulse for Sync Separator A (for timed back porch clamping)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B SYNC SEPA | RATOR INPUTS AN                        | DOUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 59          | HSYNC <sub>IN</sub> B                  | Horizontal External Sync Source for Sync Separator B. This signal may be pure HSYNC or CSYNC.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 58          | VSYNC <sub>IN</sub> B                  | Vertical External Sync Source for Sync Separator B                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 57          | C <sub>SET</sub> B                     | Sync Separator filter capacitor. Connect a 0.056µF capacitor between this pin and analog ground.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 67          | HSYNC <sub>OUT</sub> B                 | Horizontal Sync Output from Sync Separator B                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 66          | VSYNC <sub>OUT</sub> B                 | Vertical Sync Output from Sync Separator B                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 65          | Field <sub>OUT</sub> B                 | Field Flag for Sync Separator B. Low = odd field, high = even field.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 64          | Clamp <sub>OUT</sub> B                 | External Clamp Timing Pulse for Sync Separator B (for timed back porch clamping)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EXTERNAL DO | REFERENCE LEV                          | ELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 122         | V <sub>CHROMA</sub> x2 <sub>IN</sub> A | Analog Input. Chroma Reference Level for DC-Restore when $A_V = 2$ , for Channel A. This DC voltage set the midpoint voltage of the C signal (S-Video) and the Pb, Pr signals (Component video) for Channel A when the gain is set to x2. <b>When using the YPbPr inputs in YPbPr mode</b> , this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel A. This input is typically tied together with V <sub>CHROMA</sub> x2 <sub>IN</sub> B and driven with the same voltage. |

| 121         | V <sub>CHROMA</sub> x1 <sub>IN</sub> A | Analog Input. Chroma Reference Level for DC-Restore when $A_V = 1$ , for Channel A. This voltage sets the midpoint voltage of the C signal (S-Video) and the Pb, Pr signals (Component video) for Channel A when the gain is set to x1. <b>When using the YPbPr inputs in YPbPr mode</b> , this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel A. This input is typically tied together with V <sub>CHROMA</sub> x1 <sub>IN</sub> B and driven with the same voltage.   |

#### PIN NUMBER **PIN NAME** DESCRIPTION 120 Analog Input. Luma Reference Level for DC-Restore when A<sub>V</sub> = 2, for Channel A. When using the YPbPr V<sub>LUMA</sub>x2<sub>IN</sub>A inputs in RGB mode, this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel A when the gain is set to x2. When using the YPbPr inputs in YPbPr mode, this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel A.This input is typically tied together with VI UMAx2INB and driven with the same voltage. The Y/G signal is clamped to the VTIPINA voltage in master mode and V<sub>LUMA</sub>x2<sub>IN</sub>A in slave mode. 119 V<sub>LUMA</sub>x1<sub>IN</sub>A Analog Input. Luma Reference Level for DC-Restore when A<sub>V</sub> = 1, for Channel A. When using the YPbPr inputs in RGB mode, this DC voltage sets the clamp voltage of the R and B signals for Channel A when the gain is set to x1. This input is typically tied together with VLUMAx1INB and driven with the same voltage. The Y/G signal is clamped to the VTIP<sub>IN</sub>A voltage in master mode and V<sub>I UMA</sub>x1<sub>IN</sub>A in slave mode. 118 VSLICEINA Analog Input. Slicer comparator threshold for extracting composite sync from video, for Channel A. This DC voltage is typically set to 0.07V above VTIPINA, creating a sync tip slicing level of 70mV. This input is typically tied together with VSLICEINB and driven with the same voltage. 117 VTIPINA Analog Input. Sync Tip Reference Level for DC-Restore, for Channel A. This DC voltage sets the level of the sync tip of Channel A's output signal. This input is typically tied together with VTIPINB and driven with the same voltage. In RGB mode (with no Sync-on-Green), this sets the black level of the G channel. Analog Input. Chroma Reference Level for DC-Restore when $A_{V} = 2$ , for Channel A. This DC voltage sets 45 V<sub>CHROMA</sub>x2<sub>IN</sub>B the midpoint voltage of the C signal (S-Video) and the Pb, Pr signals (Component video) for Channel A when the gain is set to x2. When using the YPbPr inputs in YPbPr mode, this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel B. This input is typically tied together with V<sub>CHROMA</sub>x2<sub>IN</sub>A and driven with the same voltage. 46 Analog Input. Chroma Reference Level for DC-Restore when $A_{V} = 1$ , for Channel A. This voltage sets the V<sub>CHROMA</sub>x1<sub>IN</sub>B midpoint voltage of the C signal (S-Video) and the Pb, Pr signals (Component video) for Channel A when the gain is set to x1. When using the YPbPr inputs in YPbPr mode, this DC voltage sets the clamp voltage of the Pr/R and Pb/B signals for Channel B. This input is typically tied together with V<sub>CHROMA</sub>x1<sub>IN</sub>A and driven with the same voltage. 47 Analog Input. Luma Reference Level for DC-Restore when Ay = 2, for Channel B. When using the YPbPr V<sub>LUMA</sub>x2<sub>IN</sub>B inputs in RGB mode, this DC voltage sets the clamp voltage of the R and B signals for Channel B when the gain is set to x2. This input is typically tied together with VLUMAx2INA and driven with the same voltage. The Y/G signal is clamped to the VTIPINB voltage in master mode and VLUMAX2INB in slave mode. 48 V<sub>LUMA</sub>x1<sub>IN</sub>B Analog Input. Luma Reference Level for DC-Restore when $A_V = 1$ , for Channel B. When using the YPbPr inputs in RGB mode, this DC voltage sets the clamp voltage of the R and B signals for Channel B when the gain is set to x1. This input is typically tied together with V<sub>LUMA</sub>x1<sub>IN</sub>A and driven with the same voltage. The Y/G signal is clamped to the VTIP<sub>IN</sub>B voltage in master mode and V<sub>LUMA</sub>x1<sub>IN</sub>B in slave mode. 49 **VSLICEINB** Analog Input. Slicer comparator threshold for extracting composite sync from video, for Channel B. This DC voltage is typically set to 0.07V above VTIPINB, creating a sync tip slicing level of 70mV. This input is typically tied together with VSLICEINA and driven with the same voltage. 50 Analog Input. Sync Tip Reference Level for DC-Restore, for Channel B. This DC voltage sets the level of VTIPINB the sync tip of Channel B's output signal. This input is typically tied together with VTIPINA and driven with the same voltage. In RGB mode (with no Sync-on-Green), this sets the black level of the G channel. I<sup>2</sup>C CONTROL AND I/O I<sup>2</sup>C Bus Data I/O SDA 85 I<sup>2</sup>C Bus Clock 82 SCL Digital Input with internal pull-down. Sets I<sup>2</sup>C address: 0x84 if tied low, 0x8C if tied high. (300k pull-down) 92 Address IC RESET, ENABLE AND MISC. 77 Reset 5V Digital Input, with 3.5V logic threshold and a 300k pull-down. Tie to +5V for normal operation. Taking Reset to 0V and back to 5V initializes all data registers to 0x00. 90 PowerDown Digital Input with 300k pull-down. When this pin is taken high, all analog circuitry is disabled to minimize power consumption. In PowerDown mode, the outputs are tri-stated while the I<sup>2</sup>C interface remains active and all register data is retained. POWER SUPPLIES 18, 20, 42, 125 VA +5V Analog supply

#### **Pin Descriptions** (Continued)

| PIN NUMBER                                                                                                  | PIN NAME          | DESCRIPTION                                                              |

|-------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------|

| 80, 87                                                                                                      | V <sub>A</sub>    | +5V Analog supply for output drivers                                     |

| POWER SUPP                                                                                                  | LIES DIGITAL (3V) |                                                                          |

| 83                                                                                                          | VD                | Digital Plus Supply for I <sup>2</sup> C                                 |

| 53, 68, 99, 114                                                                                             | V <sub>D</sub>    | Digital Supply for Sync Separators                                       |

| POWER SUPP                                                                                                  | LIES ANALOG GRO   | 0V) DUND (0V)                                                            |

| 8, 12, 14, 17,<br>19, 21, 23, 26,<br>28, 37, 41, 43,<br>44, 69, 70, 72,<br>81, 95, 97, 98,<br>123, 124, 126 | GND <sub>A</sub>  | Analog Ground                                                            |

| POWER SUPP                                                                                                  | LIES DIGITAL GRO  | UND (0V)                                                                 |

| 51, 52, 54, 55,<br>56, 60, 61, 62,<br>75, 84, 86,<br>105, 106, 107,<br>111, 112, 113,<br>115, 116           | GND <sub>D</sub>  | Digital Ground                                                           |

| UNUSED PINS                                                                                                 | i<br>i            |                                                                          |

| 63, 104                                                                                                     | DNC               | Not Implemented. Do Not Connect these pins to anything (leave floating). |

## Pin Descriptions (Continued)

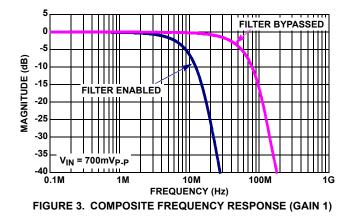

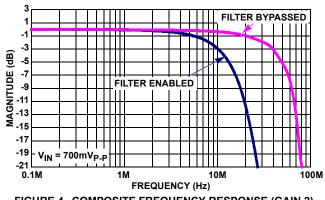

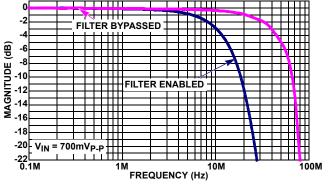

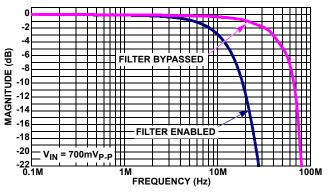

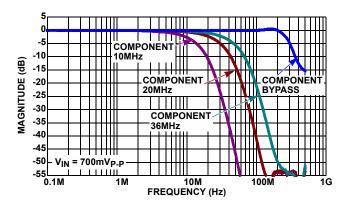

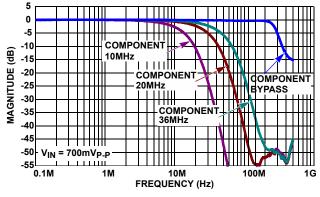

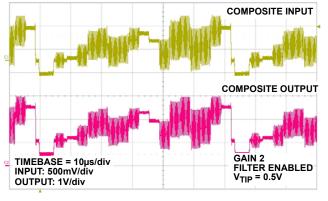

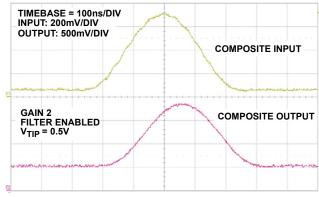

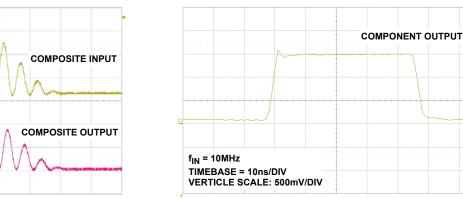

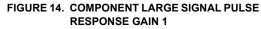

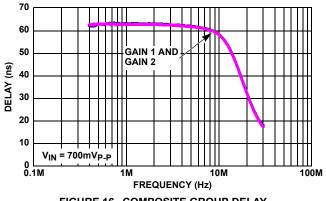

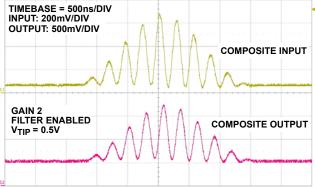

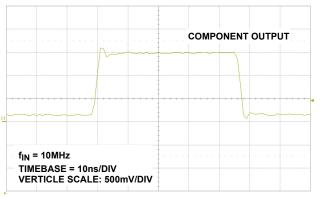

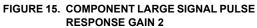

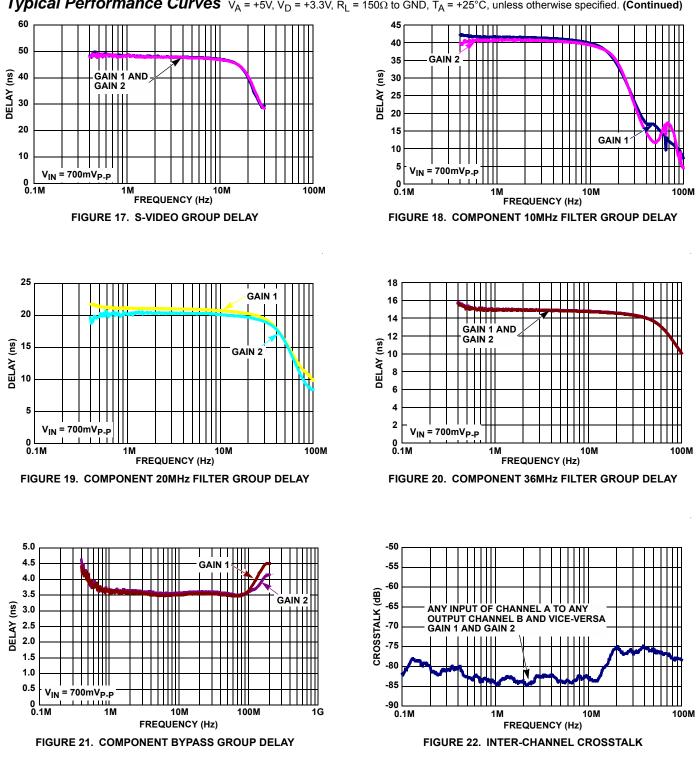

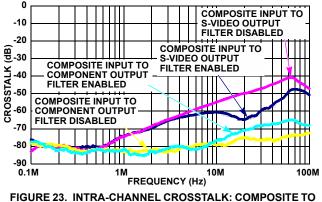

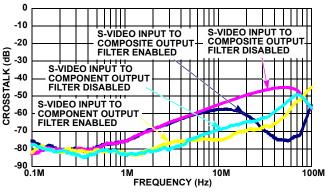

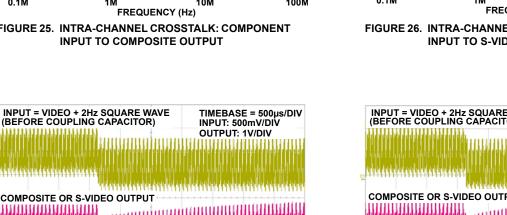

**Typical Performance Curves**  $V_A = +5V$ ,  $V_D = +3.3V$ ,  $R_L = 150\Omega$  to GND,  $T_A = +25^{\circ}C$ , unless otherwise specified.

FIGURE 5. S-VIDEO FREQUENCY RESPONSE (GAIN 1)

FIGURE 6. S-VIDEO FREQUENCY RESPONSE (GAIN 2)

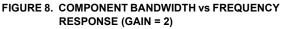

FIGURE 7. COMPONENT BANDWIDTH vs FREQUENCY RESPONSE (GAIN = 1)

FIGURE 12. 2T RESPONSE

FIGURE 13. 12.5T RESPONSE

-20

COMPONENT/S-VIDEO

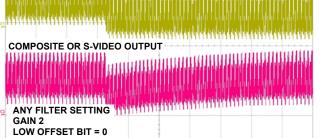

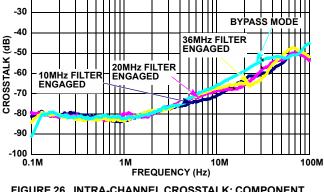

FIGURE 24. INTRA-CHANNEL CROSSTALK: S-VIDEO TO COMPONENT/COMPOSITE

FIGURE 31. PULL-DOWN CURRENT RESPONSE

# Functional Description

## Signal Muxes

The ISL59450 accepts 6 composite, 4 S-video and 4 component video sources. Each signal type is routed into a crosspoint mux with two outputs. The 6 composite signals are routed into a 6:2 mux, the S-video inputs are routed into a double 4:2 mux and the component video signals are routed into a triple 4:2 mux. Each mux is controlled through the  $l^2C$  interface.

Each signal type has two dedicated outputs, A and B. Signal types cannot be routed to different signal type outputs. For example, an S-video signal (Y, C) cannot be routed to the composite outputs.

For the luma (Y and CVBS) channels, the DC-restore function is either a standard sync-tip clamp (Master Mode) or slaved to a clamp signal generated from the sync separator (Slave Mode).

For the chroma (C and Pr/Pb) channels, the DC-restore function is a keyed clamp timed to the luma channel (Master Mode) or timed to a clamp signal generated from the sync separator (Slave Mode).

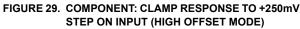

The clamping circuit restores the AC-coupled video signal to a fixed DC level (V<sub>TIP</sub>, or V<sub>LUMA</sub>). The clamping circuit provides line-by-line restoration of the video sync level to a the selected DC reference voltage during the sync tip.

## **Clamp Modes**

The ISL59450 has two clamp modes: master and slave. Each output group can operate in either mode. In master mode, sync timing is derived directly from the video signal and video levels are clamped using this internal sync signal. In slave mode, video sync is derived from the input groups corresponding sync separator (A or B) or an external source connected to the corresponding sync separator. In the slave mode, the sync timing can come from HSYNC<sub>IN</sub> and VSYNC<sub>IN</sub> or it can be derived from the sync timing on the active video on the composite, S-video, or component channels (see "Sync Separator Block Diagram" on page 9). In the slave mode, clamping occurs during the sync tip of the selected video signal or the HSYNC signal (external HSYNC input).

## Filters

The ISL59450 has integrated anti-aliasing/smoothing filters for SD and HD video signals. For the Composite Video signals, the user can use a 7MHz low pass filter or bypass it (40MHz bandwidth). S-video signals have an 10MHz filter with bypass (43MHz). Component Video signals have a user-selectable 36MHz, 20MHz, or 10MHz filter, or bypass (275MHz). All filters selections are made via the I<sup>2</sup>C host interface.

## Clamps

The clamps for all the luma and composite channels can be sync tip clamps (master mode) or timed keyed clamps (slave

mode) driven off the sync separator. The clamps for the chroma channels (C/Pr/Pb) are keyed clamps timed to either the luma (master mode) or the sync separator (slave mode).

## Clamp Disable

The clamp can be disabled for each channel by setting the appropriate bit high in the Miscellaneous 2 register (0x16).

For the S-video and component channels, additional action needs to be taken in order to completely disable the clamps.

For S-video, setting the bit in the Miscellaneous 2 register disables the pull-down  $1\mu$ A pull-down current for both the luma and chroma channel along with the clamp pull-up current for the luma channel. However, it does not disable the clamp pull-up current for the chroma channel unless the sync separator for that channel is set to 0x25.

For component, setting the bit in the Miscellaneous 2 register disables the pull-down 1 $\mu$ A pull-down current for all three channels, along with the clamp pull-up current for the luma channel. However, it does not disable the clamp pull-up current for the Pr and Pb channels unless the sync separator for that channel is set to 0x24.

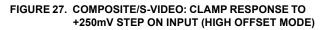

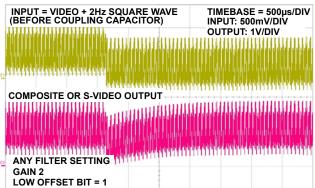

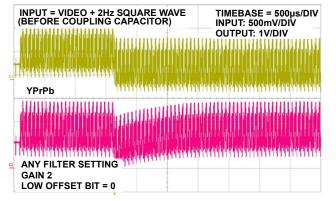

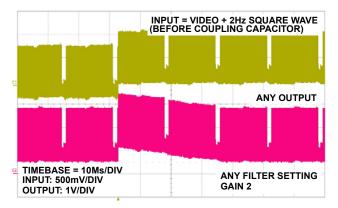

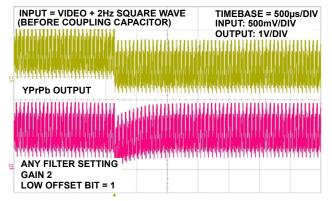

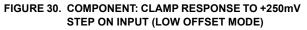

#### Low Offset Mode

Setting bit 6 in the Composite and S-Video Channel registers increases the maximum amount of pull-up clamp current available from  $130\mu A$  to  $270\mu A$ , which slightly reduces the offset between the reference and the output when the clamp is enabled.

For the component channels, this setting can be enabled by setting Bit 7 in the Miscellaneous 2 register for Channel A and Bit 3 for Channel B. This mode increases the maximum amount of pull-up clamp current available from 270µA to 500µA.

## References

Table 1 shows the references used for clamping depending on the mode and video input being used.  $V_{SLICE}$  should usually be set to 70mV to 100mV above the selected reference level for luma.

| TABLE 1. | CHANNEL | REFERENCE | LEVELS |

|----------|---------|-----------|--------|

|----------|---------|-----------|--------|

| VIDEO                                    | MASTE                  | R MODE                 | SLAVE MODE             |                        |  |  |  |  |  |

|------------------------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|--|

| OUTPUT                                   | GAIN 1                 | GAIN 2                 | GAIN 1                 | GAIN 2                 |  |  |  |  |  |

| Composite                                | V <sub>TIP</sub>       | V <sub>TIP</sub>       | V <sub>LUMA</sub> x1   | V <sub>LUMA</sub> x2   |  |  |  |  |  |

| S-Video<br><b>Luma</b>                   | V <sub>TIP</sub>       | V <sub>TIP</sub>       | V <sub>LUMA</sub> x1   | V <sub>LUMA</sub> x2   |  |  |  |  |  |

| S-Video<br>Chroma                        | V <sub>CHROMA</sub> x1 | V <sub>CHROMA</sub> x2 | V <sub>CHROMA</sub> x1 | V <sub>CHROMA</sub> x2 |  |  |  |  |  |

| Component:<br>Luma/Green<br>(YPrPb Mode) | V <sub>TIP</sub>       | V <sub>TIP</sub>       | V <sub>LUMA</sub> x1   | V <sub>LUMA</sub> x2   |  |  |  |  |  |

| Component:<br>Luma/Green<br>(RGB Mode)   | V <sub>TIP</sub>       | VTIP                   | V <sub>LUMA</sub> x1   | V <sub>LUMA</sub> x2   |  |  |  |  |  |

|                                                   | - ( ,                |                        |                        |                        |  |  |  |  |

|---------------------------------------------------|----------------------|------------------------|------------------------|------------------------|--|--|--|--|

| VIDEO                                             | MASTE                | R MODE                 | SLAVE MODE             |                        |  |  |  |  |

| OUTPUT                                            | GAIN 1               | GAIN 2                 | GAIN 1                 | GAIN 2                 |  |  |  |  |

| Component:<br><b>Pr/Pb</b><br>(YPrPb Mode)        |                      | V <sub>CHROMA</sub> x2 | V <sub>CHROMA</sub> x1 | V <sub>CHROMA</sub> x2 |  |  |  |  |

| Component:<br><b>Pr/Pb</b><br>( <i>RGB Mode</i> ) | V <sub>LUMA</sub> x1 | V <sub>LUMA</sub> x2   | V <sub>LUMA</sub> x1   | V <sub>LUMA</sub> x2   |  |  |  |  |

TABLE 1. CHANNEL REFERENCE LEVELS (Continued)

Bypass each reference voltage with a  $0.01\mu F$  capacitor to ground to reduce noise injection.

TABLE 2. SUGGESTED REFERENCE LEVELS

| REFERENCE                              | VOLTAGE<br>(V) |

|----------------------------------------|----------------|

| VTIP <sub>IN</sub> A                   | 0.5            |

| VTIP <sub>IN</sub> B                   | 0.5            |

| V <sub>LUMA</sub> x1 <sub>IN</sub> A   | 0.5            |

| V <sub>LUMA</sub> x2 <sub>IN</sub> A   | 0.5            |

| V <sub>LUMA</sub> x1 <sub>IN</sub> B   | 0.5            |

| V <sub>LUMA</sub> x2 <sub>IN</sub> B   | 0.5            |

| V <sub>CHROMA</sub> x1 <sub>IN</sub> A | 1              |

| V <sub>CHROMA</sub> x2 <sub>IN</sub> A | 1              |

| V <sub>CHROMA</sub> x1 <sub>IN</sub> B | 1              |

| V <sub>CHROMA</sub> x2 <sub>IN</sub> B | 1              |

| VSLICE <sub>IN</sub> A                 | 0.6            |

| VSLICE <sub>IN</sub> B                 | 0.6            |

## **Outputs/Levels**

Each signal output has a selectable gain of 0dB (GAIN 1) or 6dB (GAIN 2).

The input to the sync separators can be any of the video inputs, as shown in the "Sync Separator Block Diagram" on page 9. The HSYNC and VSYNC inputs are dedicated to their respective sync separator (i.e. Sync Separator A can connect to  $HSYNC_{IN}A$  and  $VSYNC_{IN}A$ , but not  $HSYNC_{IN}B$  and  $VSYNC_{IN}B$ ).

## Sync Separators

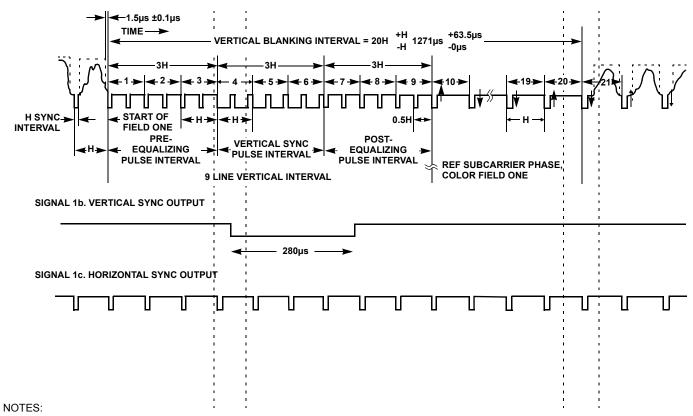

The ISL59450 contains two high performance video sync separators that automatically lock to any SD and HD video signal. They will also extract sync timing information from non-standard video inputs and in the presence of Macrovision pulses. Composite sync, vertical sync and horizontal sync outputs are provided from each sync separator. Timing is adjusted automatically for various video standards. The composite sync output follows video in sync pulses and a vertical sync pulse is output on the rising edge of the first vertical serration following the vertical pre-equalizing string. For non-standard vertical inputs, a default vertical pulse is output when the vertical signal stays low for longer than the vertical sync default delay time. The horizontal output gives horizontal timing with pre/post equalizing pulses.

The use of two sync separators allows the user to send independent sync information for two signals to downstream devices. An example would be two video decoders or two ADCs that are used in a picture-in-picture application. Each sync separator is dedicated to its respective channel, Sync Separator A for Channel A and Sync Separator B for Channel B. It is important to note that the syncs for each channel cannot be MUXed onto the other channel. For example, HSYNC<sub>IN</sub>A and VSYNC<sub>IN</sub>A **cannot** be MUXed to HSYNC<sub>OUT</sub>B and VSYNC<sub>OUT</sub>B.

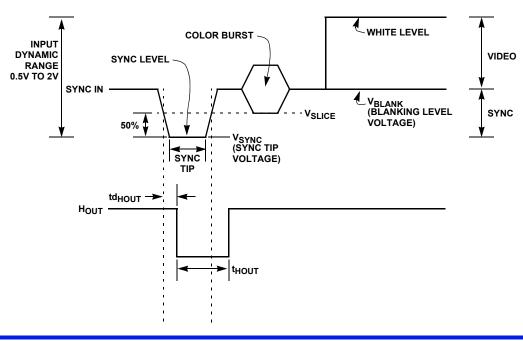

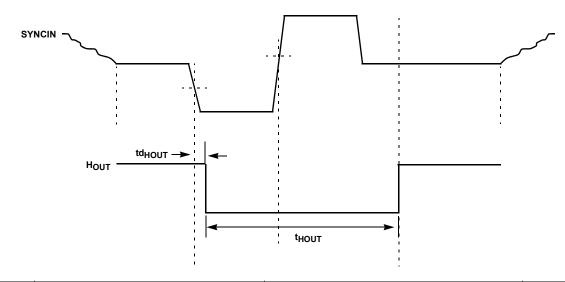

See the "Sync Separator Timing Diagrams" beginning on page 32 for typical horizontal and vertical sync output timing.

## VERTICAL SYNC

A low-going Vertical Sync pulse is output during the start of the vertical cycle of the incoming video signal. The vertical cycle starts with a pre-equalizing phase of pulses with a duty cycle of about 93%, followed by a vertical serration phase that has a duty cycle of about 15%. Vertical Sync is clocked out of the ISL59450 on the first rising edge during the vertical serration phase. In the absence of vertical serration pulses, a vertical sync pulse will be forced out after the vertical sync default delay time, approximately 60µs after the last falling edge of the vertical equalizing phase.

## HORIZONTAL SYNC

The horizontal circuit senses the composite sync edges and produces the true horizontal pulses of nominal width 5µs for standard definition NTSC signals. The pulse width of the HSYNC output changes as the line frequency of the input signal changes. For example, an NTSC input generates an HSYNCOUT with a pulse width of 5µs; while a 720p HD video input generates an HSYNCOUT with a pulse width of 1.9µs. The leading edge is triggered from the leading edge of the input HSYNC with the same propagation delay as composite sync. The half line pulses present in the input signal during vertical blanking are removed with an internal 2H line eliminator circuit. This is a circuit that inhibits horizontal output pulses until 75% of the line time is reached, then the horizontal output operation is enabled again. Any signals present on the I/P signal after the true H sync will be ignored, thus the horizontal output will not be effected by MacroVision copy protection. When there is a loss of sync, the Horizontal Sync output is held high.

## CSET

Connect external capacitors from  $C_{SET}A$  and  $C_{SET}B$  to ground. The  $C_{SET}$  capacitor should be a X7R grade or better as the Y5U general use capacitors may be too leaky and cause faulty operation. The  $C_{SET}$  capacitor should be very close to the  $C_{SET}A$  and  $C_{SET}B$  pins to reduce possible board leakage. 56nF is recommended. The  $C_{SET}$  capacitor rectifies a 5µs pulse current and creates a voltage on  $C_{SET}$ .

The  $C_{\mbox{SET}}$  voltage is converted to bias current for  $H_{\mbox{SYNC}}$  and  $V_{\mbox{SYNC}}$  timing.

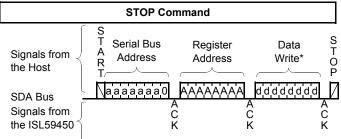

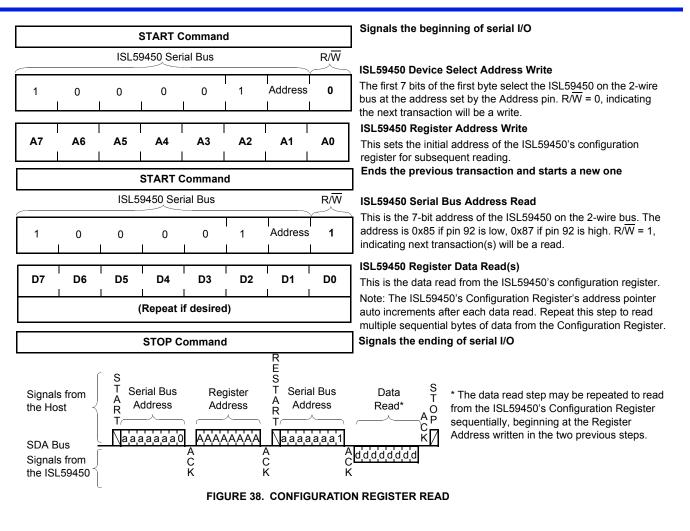

## Internal Control Registers