## **Brief Description**

The ZSPM4141 is an ultra-low-power linear regulator optimized for minimal quiescent current losses via advanced, proprietary technology. It can improve energy efficiency and reduce heat due to power dissipation because it draws low nA-level quiescent current for light loads, yet it can regulate current loads as high as 200mA. The linear regulated output voltage is factory-configured to an option from 1.2V to 4.2V in 100mV steps. The ZSPM4141 also provides over-current protection.

# Features

- Low operating voltage range: 2.5V to 5.5V

- Power-Down Mode for 100pA quiescent current

- Over-current protection: 250mA

- Output voltage options of 1.2V to 4.2V in 100mV steps (programmed at manufacturing)

## **Benefits**

- Ultra-low 100pA quiescent current in power down mode

- Best-in-class quiescent current of 20nA at I<sub>LOAD</sub>=0

- 0.5% DC line regulation (typical)

- Extends battery life

- Enables power harvesting applications

- High level of integration minimizes board space

## **Related IDT Smart Power Products**

ZSPM4121 Under-Voltage Load Switch for Smart Battery Management

### **Available Support**

- ZSPM4141W12KIT Evaluation Kit

- Support Documentation

### **Physical Characteristics**

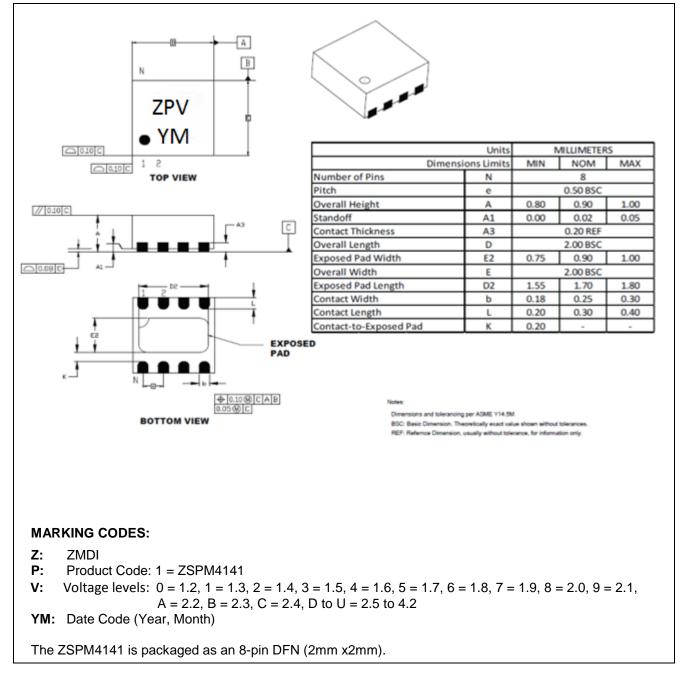

• Package: 8-pin DFN (2mm x2mm)

# **Typical ZSPM4141 Application Circuits**

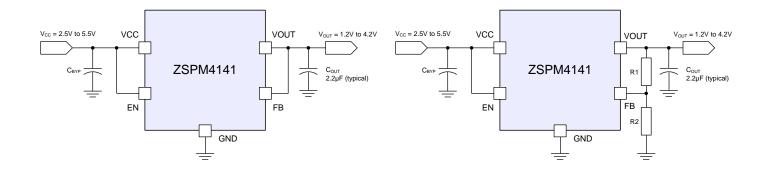

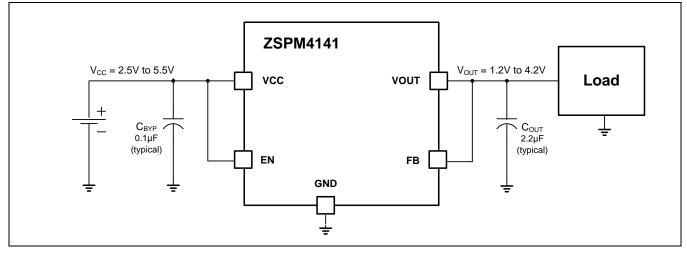

### ZSPM4141 Basic (Fixed Output) Application

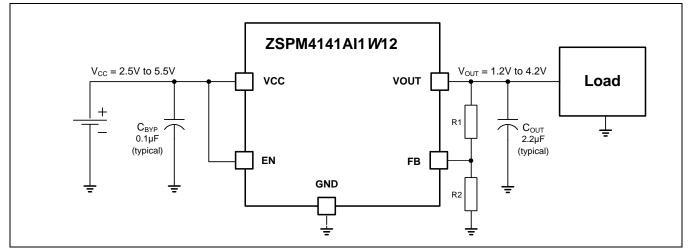

### ZSPM4141AI1W12 Variable VOUT via Resistor Divider

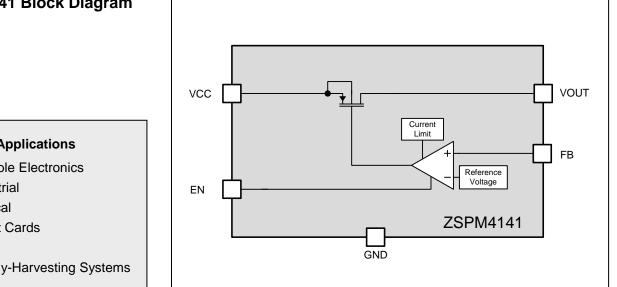

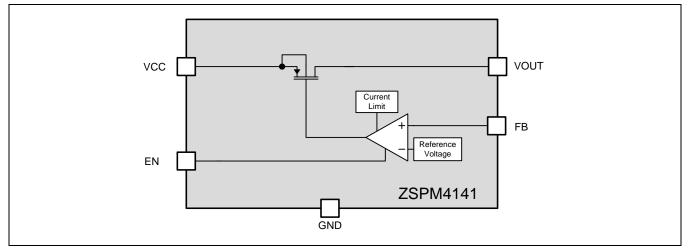

ZSPM4141 Block Diagram

### **Typical Applications**

- Portable Electronics

- Industrial .

- Medical

- Smart Cards •

- RFID

- **Energy-Harvesting Systems** .

## **Ordering Information**

| Ordering Code*          | Description                                                                     | Package          |

|-------------------------|---------------------------------------------------------------------------------|------------------|

| ZSPM4141AI1 <i>W</i> 12 | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 1.2V          | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 18 | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 1.8V          | 8-pin DFN / Reel |

| ZSPM4141AI1W25          | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 2.5V          | 8-pin DFN / Reel |

| ZSPM4141AI1W30          | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 3.0V          | 8-pin DFN / Reel |

| ZSPM4141AI1W31          | ZSPM4141 Ultra-Low Power Line Regulator — $V_{OUT}$ factory set to 3.1V         | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 33 | ZSPM4141 Ultra-Low Power Line Regulator —V <sub>OUT</sub> factory set to $3.3V$ | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 42 | ZSPM4141 Ultra-Low Power Line Regulator —V <sub>OUT</sub> factory set to 4.2V   | 8-pin DFN / Reel |

| ZSPM4141W12KIT          | ZSPM4141 Evaluation Kit w/Vout adjusting resistors (default 1.2 Vout)           |                  |

\* W for 7" reel with 2500 parts. Custom V<sub>OUT</sub> values are also available: 1.2V to 4.2V (typical) in 100mV increments.

**Corporate Headquarters** 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com

Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

## **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

# Contents

| 1 | ZSI  | PM4141 Characteristics                            | 5    |

|---|------|---------------------------------------------------|------|

|   | 1.1. | Absolute Maximum Ratings                          | 5    |

|   | 1.2. | Thermal Characteristics                           | 5    |

|   | 1.3. | Recommended Operating Conditions                  | 6    |

|   | 1.4. | Electrical Characteristics                        | 6    |

| 2 | Тур  | vical Performance Characteristics                 | 7    |

| 3 | Des  | scription of Circuit                              | 9    |

| 4 | Арр  | plication Circuits                                | . 10 |

|   | 4.1. | Selection of External Components                  | . 10 |

|   | 4.1. |                                                   |      |

|   | 4.1. | .2. Input Bypass Capacitor C <sub>BYP</sub>       | . 10 |

|   | 4.1. | .3. Output Voltage Adjustment Resistors R1 and R2 | .10  |

|   | 4.2. | Typical Application Circuit                       | . 11 |

| 5 | Pin  | Configuration and Package                         | . 12 |

|   | 5.1. | ZSPM4141 Package Dimensions and Marking Diagram   | .12  |

|   | 5.2. | Pin Assignments                                   | .13  |

| 6 | Lay  | out and Soldering Requirements                    | .14  |

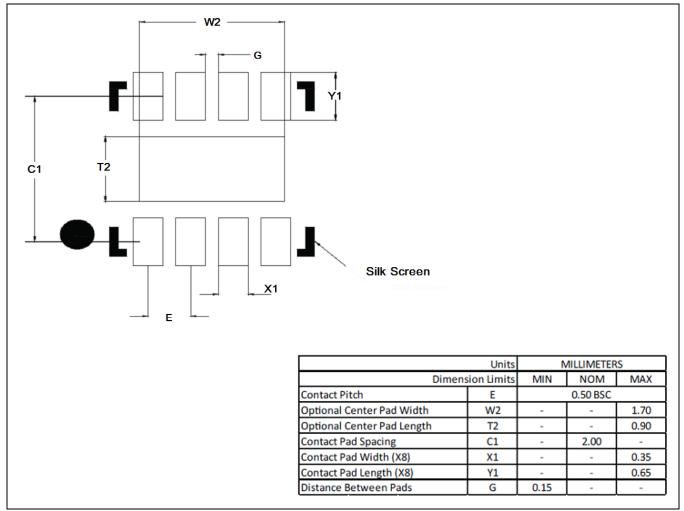

|   | 6.1. | Recommended Landing Pattern for PCBs              | .14  |

|   | 6.2. | Multi-Layer PCB Layout                            | . 15 |

|   | 6.3. | Single-Layer PCB Layout                           | .16  |

| 7 | Orc  | dering Information                                | . 17 |

| 8 | Rel  | ated Documents                                    | . 17 |

| 9 | Doo  | cument Revision History                           | . 18 |

# List of Figures

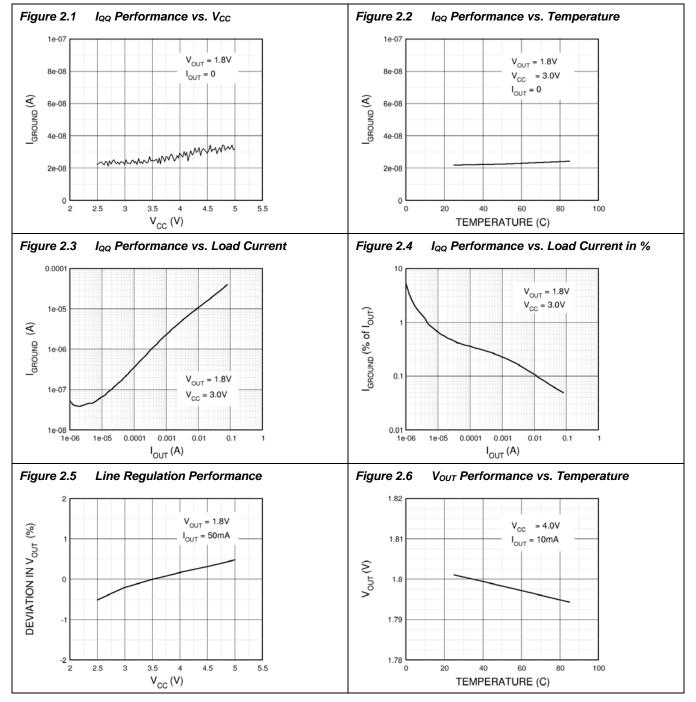

| Figure 2.1  | I <sub>QQ</sub> Performance vs. V <sub>CC</sub>   | .7 |

|-------------|---------------------------------------------------|----|

| Figure 2.2  | $I_{\text{QQ}}$ Performance vs. Temperature       | .7 |

| Figure 2.3  | I <sub>QQ</sub> Performance vs. Load Current      | .7 |

| Figure 2.4  | I <sub>QQ</sub> Performance vs. Load Current in % | .7 |

| Figure 2.5  | Line Regulation Performance                       | .7 |

| Figure 2.6  | V <sub>OUT</sub> Performance vs. Temperature      | .7 |

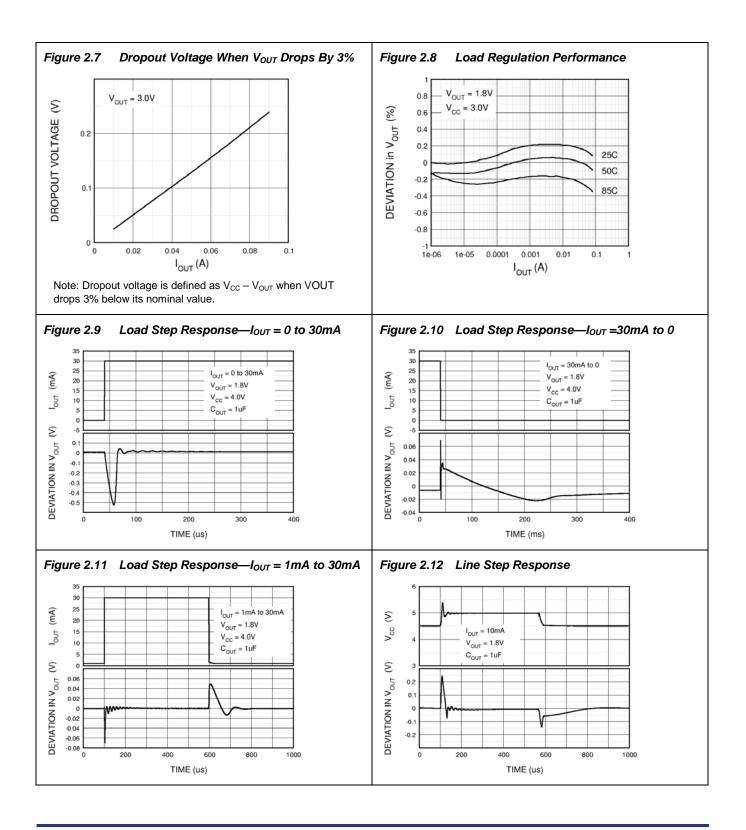

| Figure 2.7  | Dropout Voltage When V <sub>OUT</sub> Drops By 3% | .8 |

| Figure 2.8  | Load Regulation Performance                       | .8 |

| Figure 2.9  | Load Step Response—I <sub>OUT</sub> = 0 to 30mA   | .8 |

| Figure 2.10 | Load Step Response—I <sub>OUT</sub> =30mA to 0    | .8 |

| Figure 2.11 | Load Step Response—I <sub>OUT</sub> = 1mA to 30mA | .8 |

| Figure 2.12 | Line Step Response                                | .8 |

$<sup>^{\</sup>ensuremath{\textcircled{O}}}$  2016 Integrated Device Technology, Inc.

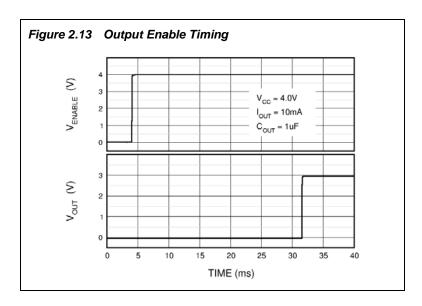

| Output Enable Timing                                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZSPM4141 Block Diagram                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Basic ZSPM4141 Application Circuit—Fixed Output                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ZSPM4141AI1W12 Application Circuit—Variable Output             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ZSPM4141 Package Drawing                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ZSPM4141 Pin Assignments (top view)                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Recommended Landing Pattern for 8-Pin DFN                      | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Package and PCB Land Configuration for Multi-Layer PCB         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| JEDEC Standard FR4 Multi-Layer Board – Cross-Sectional View    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conducting Heat Away from the Die using an Exposed Pad Package | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

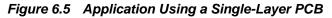

| Application Using a Single-Layer PCB                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                | Output Enable Timing<br>ZSPM4141 Block Diagram<br>Basic ZSPM4141 Application Circuit—Fixed Output<br>ZSPM4141AI1W12 Application Circuit—Variable Output<br>ZSPM4141 Package Drawing<br>ZSPM4141 Pin Assignments (top view)<br>Recommended Landing Pattern for 8-Pin DFN<br>Package and PCB Land Configuration for Multi-Layer PCB<br>JEDEC Standard FR4 Multi-Layer Board – Cross-Sectional View<br>Conducting Heat Away from the Die using an Exposed Pad Package<br>Application Using a Single-Layer PCB |

# List of Tables

| Table 1.1 | Absolute Maximum Ratings                                                   | 5  |

|-----------|----------------------------------------------------------------------------|----|

| Table 1.2 | Thermal Characteristics for 8-pin DFN (2x2) Package                        | 5  |

| Table 1.3 | Recommended Operating Conditions                                           | 6  |

| Table 1.4 | Electrical Characteristics                                                 | 6  |

| Table 4.1 | Output Voltage Adjustment Resistors and Resulting I <sub>aq</sub> Increase | 10 |

| Table 5.1 | Pin Description, 8-Pin DFN (2mmx2mm)                                       | 13 |

|           |                                                                            |    |

# 1 **ZSPM4141** Characteristics

Important: Stresses beyond those listed under "Absolute Maximum Ratings" (section 1.1) may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" (section 1.3) is not implied. Exposure to absolute-maximum-rated conditions for extended periods could affect device reliability.

## 1.1. Absolute Maximum Ratings

Over operating free-air temperature range unless otherwise noted. All voltage values are with respect to network ground terminal.

| Parameter                                                                                              | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------------------------------------|------------------|-------------|------|

| Maximum input/output on VCC, VOUT, EN, and FB pins                                                     |                  | -0.3 to 6.0 | V    |

| Electrostatic Discharge – Human Body Model, according to the respective JESD22 JEDEC standard          |                  | 2           | kV   |

| Electrostatic Discharge – Charged Device Model, according to the respective JESD22-C101 JEDEC standard |                  | 500         | V    |

| Operating Junction Temperature Range                                                                   | TJ               | -20 to 85   | °C   |

| Storage Temperature Range                                                                              | T <sub>stg</sub> | -65 to 150  | °C   |

| Lead Temperature (soldering, 10 seconds)                                                               |                  | 260         | °C   |

### Table 1.1 Absolute Maximum Ratings

# **1.2.** Thermal Characteristics

### Table 1.2 Thermal Characteristics for 8-pin DFN (2x2) Package

| θ <sub>JA</sub> (°C/W) <sup>1)</sup> |                                                                                                             | $\theta_{JC}$ (°C/W) <sup>2)</sup> |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|

| 73.1                                 |                                                                                                             | 10.7                               |  |  |

| 1)                                   | 1) This assumes a FR4 board only.                                                                           |                                    |  |  |

| 2)                                   | 2) This assumes a 1oz. copper JEDEC standard board with thermal vias. See section 6.1 for more information. |                                    |  |  |

## 1.3. Recommended Operating Conditions

### Table 1.3 Recommended Operating Conditions

| Parameter                                                                                                                               | Symbol           | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Unregulated Supply Input at VCC pin                                                                                                     | Vcc              | 2.5 |     | 5.5 | V    |

| Enable Input (EN pin)                                                                                                                   | V <sub>EN</sub>  | 0   |     | 5.0 | V    |

| Typical Regulated Supply Output Voltage                                                                                                 | V <sub>OUT</sub> | 1.2 |     | 4.2 | V    |

| Operating Ambient Temperature <sup>1)</sup>                                                                                             | T <sub>A</sub>   | -20 |     | 55  | °C   |

| Operating Junction Temperature                                                                                                          | TJ               | -20 |     | 85  | °C   |

| 1) Operating ambient temperature is only intended as a guideline. The operating junction temperature requirements must not be exceeded. |                  |     |     |     |      |

### **1.4. Electrical Characteristics**

Electrical characteristics,  $V_{CC}$  = 2.5V to 5V (unless otherwise noted). Minimum and maximum characteristics tested at  $T_J$  = 25°C.

### Table 1.4 Electrical Characteristics

| Parameter                              | Symbol              | Condition                                                                                                                            | Min                 | Тур | Max                 | Unit |

|----------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Input Supply Voltage                   | V <sub>cc</sub>     |                                                                                                                                      | 2.5                 |     | 5.5                 | V    |

| Input Low Logic Level                  | Vil <sub>EN</sub>   |                                                                                                                                      |                     |     | 0.3*V <sub>CC</sub> | V    |

| Input High Logic Level                 | Vih <sub>EN</sub>   |                                                                                                                                      | 0.7*V <sub>CC</sub> |     |                     | V    |

| Output Bypass Capacitor                | C <sub>OUT</sub>    |                                                                                                                                      | 1                   | 2.2 | 4.7                 | μF   |

| Input Bypass Capacitor                 | C <sub>BYP</sub>    |                                                                                                                                      |                     | 0.1 |                     | μF   |

| Quiescent Current:                     | I <sub>QQ</sub>     | V <sub>CC</sub> = 4.2V, I <sub>OUT</sub> =0                                                                                          |                     | 20  |                     | nA   |

| Quiescent Current: Power-<br>Down Mode | I <sub>QQpd</sub>   | I <sub>OUT</sub> =0, EN = 0                                                                                                          |                     | 100 |                     | pА   |

| Operating Current                      | I <sub>OP-GND</sub> | V <sub>CC</sub> = 2.5V, I <sub>OUT</sub> = 200mA                                                                                     |                     | 200 |                     | μA   |

|                                        |                     | $V_{CC} = 3.3V, I_{OUT} = 200mA$                                                                                                     |                     | 200 |                     | μA   |

|                                        |                     | $V_{CC} = 5.5V, I_{OUT} = 200mA$                                                                                                     |                     | 200 |                     | μA   |

| Load Capability                        | I <sub>OUT</sub>    |                                                                                                                                      | 0                   |     | 200                 | mA   |

| DC Line Regulation                     | V <sub>LINE</sub>   | $V_{CC}$ = 2.5V to 5V, $V_{OUT}$ =1.8V,<br>I <sub>OUT</sub> = 50mA                                                                   |                     | 0.5 | 1                   | %    |

| DC Load Regulation                     | Vload               | $\label{eq:V_CC} \begin{array}{l} V_{CC} = 4.2V, \\ I_{OUT} = 0.02mA \ to \ 200mA, \\ V_{OUT} = V_{OUT,nominal} + 300mV \end{array}$ |                     | 1   | 2                   | %    |

| Current Limit                          | I <sub>LIMIT</sub>  | $I_{OUT}$ measured at $V_{OUT} = 0.9^* V_{OUT,nominal}$                                                                              |                     | 250 |                     | mA   |

<sup>© 2016</sup> Integrated Device Technology, Inc.

# 2 Typical Performance Characteristics

$C_{IN}$  = 10µF and T = 25°C (unless otherwise noted)

© 2016 Integrated Device Technology, Inc.

# 3 Description of Circuit

The ZSPM4141 is an ultra-low-power linear regulator optimized for minimal quiescent current losses via advanced, proprietary technology. It draws low nA-level quiescent current for light loads, yet it can regulate current loads as high as 200mA. The linear regulated output voltage is factory-configured to an option from 1.2V to 4.2V in 100mV steps. The ZSPM4141 also provides over-current protection (see Table 1.4).

Figure 3.1 ZSPM4141 Block Diagram

© 2016 Integrated Device Technology, Inc.

# **4** Application Circuits

## 4.1. Selection of External Components

### 4.1.1. Output Bypass Capacitor C<sub>OUT</sub>

Connect a bypass capacitor (C\_{OUT}) from the VOUT pin to ground. The typical value for C\_{OUT} is 2.2  $\mu$ F.

See Table 1.4 for further specifications.

## 4.1.2. Input Bypass Capacitor C<sub>BYP</sub>

Connect a bypass capacitor ( $C_{BYP}$ ) from the VCC pin to ground. The typical value for  $C_{OUT}$  is 0.1µF.

## 4.1.3. Output Voltage Adjustment Resistors R1 and R2

The ZSPM4141W12KIT includes a set of output adjustment resistors for R1 and R2 shown in the variable output circuit on page 2. Refer to Table 4.1 for the effect of different combinations of the resistors on the output voltage and the resulting increase in  $I_{QQ}$  current.

| Vout | R1 (+/-0.1%) | R2 (+/-1%) | IQQ increase |

|------|--------------|------------|--------------|

| 1.2  | 0            |            |              |

| 1.5  | 1.00ΜΩ       | 4.02ΜΩ     | 0.30µA       |

| 1.8  | 1.00ΜΩ       | 2ΜΩ        | 0.60µA       |

| 3    | 1.00ΜΩ       | 665kΩ      | 1.80µA       |

| 3.3  | 1.00ΜΩ       | 576kΩ      | 2.10µA       |

| 4.2  | 1.00ΜΩ       | 402kΩ      | 3.00µA       |

Table 4.1

Output Voltage Adjustment Resistors and Resulting Iqq Increase

## 4.2. Typical Application Circuit

Figure 4.2 ZSPM4141AI1W12 Application Circuit—Variable Output

# 5 Pin Configuration and Package

# 5.1. ZSPM4141 Package Dimensions and Marking Diagram

Figure 5.1 ZSPM4141 Package Drawing

<sup>© 2016</sup> Integrated Device Technology, Inc.

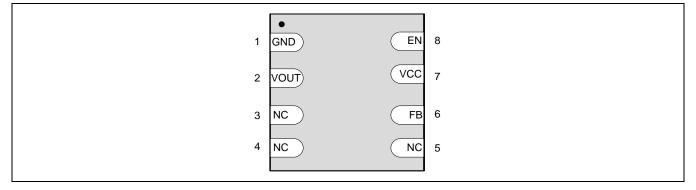

### 5.2. Pin Assignments

### Figure 5.2 ZSPM4141 Pin Assignments (top view)

Table 5.1 Pin Description, 8-Pin DFN (2mmx2mm)

| Pin # | Name | Function | Description                             |

|-------|------|----------|-----------------------------------------|

| 1     | GND  | Ground   | GND                                     |

| 2     | VOUT | Output   | Regulated Output Voltage                |

| 3     | NC   |          | No Connection (connect to GND or float) |

| 4     | NC   |          | No Connection (connect to GND or float) |

| 5     | NC   |          | No Connection (connect to GND or float) |

| 6     | FB   | Input    | Feedback Input                          |

| 7     | VCC  | Supply   | Input Power                             |

| 8     | EN   | Input    | Enable Input                            |

# 6 Layout and Soldering Requirements

To maximize the efficiency of this package for applications on a single layer or multi-layer printed circuit board (PCB), certain guidelines must be followed when laying out this part on the PCB.

## 6.1. Recommended Landing Pattern for PCBs

Figure 6.1 Recommended Landing Pattern for 8-Pin DFN

## 6.2. Multi-Layer PCB Layout

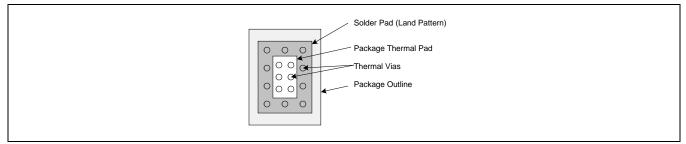

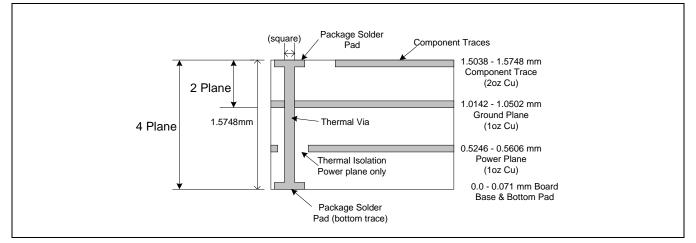

The following are guidelines for mounting the exposed pad ZSPM4141 on a multi-layer PCB with ground a plane. In a multi-layer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane. The efficiency of this method depends on several factors, including die area, number of thermal vias, and thickness of copper, etc.

Figure 6.2 Package and PCB Land Configuration for Multi-Layer PCB

Figure 6.3 JEDEC Standard FR4 Multi-Layer Board – Cross-Sectional View

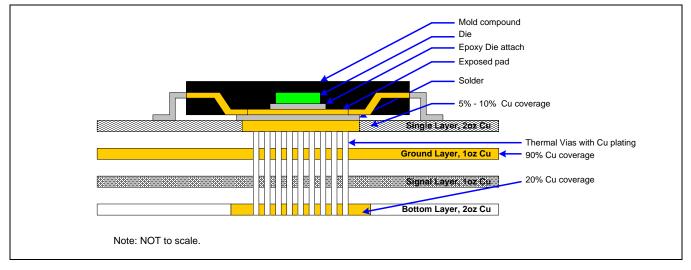

Figure 6.4 is a representation of how the heat can be conducted away from the die using an exposed pad package. Each application will have different requirements and limitations, and therefore the user should use sufficient copper to dissipate the power in the system. The output current rating for the linear regulators might need to be de-rated for ambient temperatures above 85°C. The de-rated value will depend on calculated worst-case power dissipation and the thermal management implementation in the application.

### Figure 6.4 Conducting Heat Away from the Die using an Exposed Pad Package

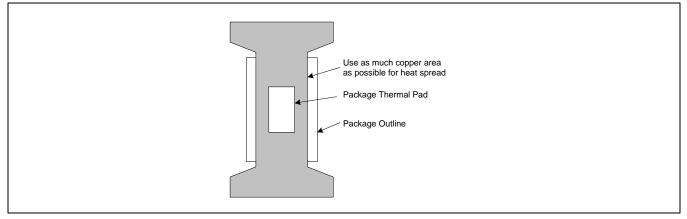

### 6.3. Single-Layer PCB Layout

Layout recommendation for a single-layer PCB: utilize as much copper area for power management as possible. In a single-layer board application, the thermal pad is attached to a heat spreader (copper areas) by using a low thermal impedance attachment method (solder paste or thermal conductive epoxy).

In both of the methods mentioned above, it is advisable to use as much copper trace as possible to dissipate the heat.

**Important:** If the attachment method is NOT implemented correctly, the functionality of the product is not guaranteed. Power dissipation capability will be adversely affected if the device is incorrectly mounted onto the circuit board.

<sup>© 2016</sup> Integrated Device Technology, Inc.

# 7 Ordering Information

| Ordering Code*          | Description                                                                     | Package          |

|-------------------------|---------------------------------------------------------------------------------|------------------|

| ZSPM4141AI1 <i>W</i> 12 | ZSPM4141 Ultra-Low Power Line Regulator — $V_{OUT}$ factory set to 1.2V         | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 18 | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 1.8V          | 8-pin DFN / Reel |

| ZSPM4141AI1W25          | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 2.5V          | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 30 | ZSPM4141 Ultra-Low Power Line Regulator —V <sub>OUT</sub> factory set to 3.0V   | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 31 | ZSPM4141 Ultra-Low Power Line Regulator —V <sub>OUT</sub> factory set to $3.1V$ | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 33 | ZSPM4141 Ultra-Low Power Line Regulator —V <sub>OUT</sub> factory set to $3.3V$ | 8-pin DFN / Reel |

| ZSPM4141AI1 <i>W</i> 42 | ZSPM4141 Ultra-Low Power Line Regulator $-V_{OUT}$ factory set to 4.2V          | 8-pin DFN / Reel |

| ZSPM4141W12KIT          | ZSPM4141 Evaluation Kit w/Vout adjusting resistors (default 1.2 Vout)           |                  |

Custom  $V_{OUT}$  values are also available: 1.2V to 4.2V (typical) in 100mV increments.

# 8 Related Documents

| Document                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------|--|

| ZSPM4141 Feature Sheet                                                                                               |  |

| ZSPM4141 Evaluation Kit Description                                                                                  |  |

| ZSPM4141 Application Note—Low Power<br>Battery Control and Voltage Regulator<br>Solutions for Remote Sensor Networks |  |

Visit IDT's website <u>www.IDT.com</u> or contact your nearest sales office for the latest version of these documents.

# 9 Document Revision History

| Revision | Date             | Description                                                                                                                                                                 |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00     | August 6, 2012   | First release.                                                                                                                                                              |

| 2.00     | January 11, 2013 | Addition of variable output illustration and Table 4.1. Update for ordering codes and contact information. Update for "Electrostatic Discharge" specification in Table 1.1. |

|          | January 29, 2016 | Changed to IDT branding.                                                                                                                                                    |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

Tech Support

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of DT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <u>www.idt.com/go/glossary</u>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

© 2016 Integrated Device Technology, Inc.