### **TUSB6015 USB 2.0 High Speed Peripheral Controller Data Sheet**

#### **FEATURES**

- USB 2.0 High-Speed (HS) Compliant Peripheral Controller Core

- USB-IF TID # 40630005

- Integrated USB 2.0 PHY

- NOR FLASH Like External Host Interface

- DP/DM lines are high impedance when the device is not powered

- Six physical endpoints

- Each endpoint is configurable as IN or OUT with dedicated 1K buffer

- NOR Flash Interface Access modes:

- Asynchronous 16-bit single access

- Asynchronous 32-bit single access

- Asynchronous 16x16 burst access w/ DMA

- Synchronous 16x16 burst access with DMA (Max GPMC clock is 65 MHz)

- Interrupt on DP/DM line state change for CEA-936-A detect

- VBUS MAX Voltage rating will be 6V for USB Charging

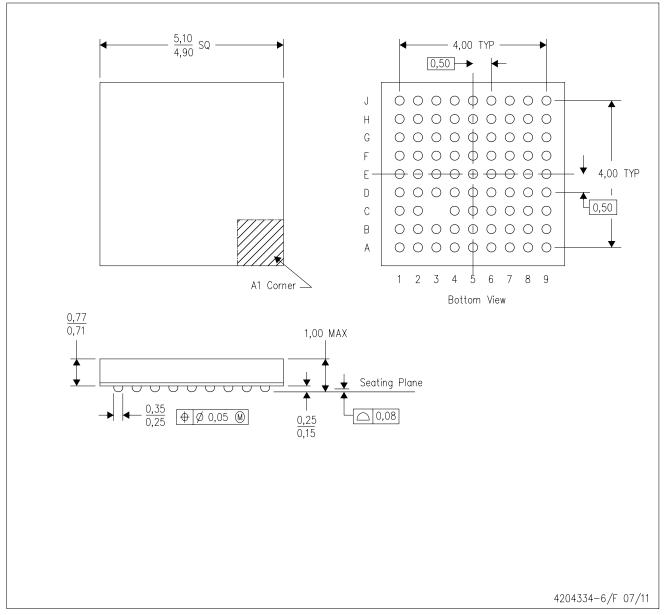

- RoHS Complaint 80 Terminal BGA MICROSTAR JUNIOR Package

#### **DESCRIPTION**

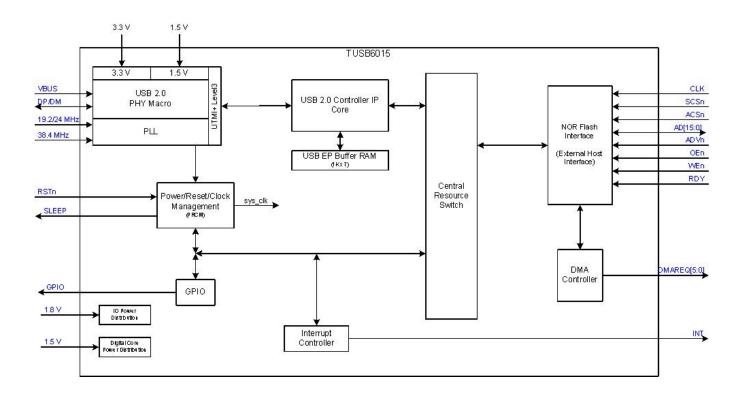

The TUSB6015 is a USB 2.0 HS Peripheral Controller designed for seamless interface to an external Host processor through the NOR FLASH-like interface.

The NOR FLASH-like interface is a 16-bit, multiplexed address/data, interface with support for synchronous burst and single asynchronous read/write access. Configuration registers are accessible via the asynchronous chip select only; the End Point FIFO's are accessible via both the synchronous and asynchronous chip selects.

The device also has eight user configurable general purpose I/O interface pins. The GPIO can be configured as an interrupt or wakeup source. Some GPIO have secondary NOR-flash DMA Request functionality.

The device is fully compliant with the Universal Serial Bus Specification Rev. 2.0.

The ESD protection level is 2KV HBM (JESD22-A114D), 500V CDM (JESD22-C101C).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appear at the end of this data sheet.

## Ordering Information<sup>1</sup>

| PACKAGED DEVICES | PACKAGE <sup>2</sup> | MARKING   |

|------------------|----------------------|-----------|

| TUSB6015IZQE     | ZQE                  | TUSB6015I |

| TUSB6015IZQER•3  | ZQE                  | TUSB6015I |

<sup>&</sup>lt;sup>1</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at <a href="https://www.ti.com">www.ti.com</a>.

<sup>&</sup>lt;sup>2</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at <a href="www.ti.com/sc/package">www.ti.com/sc/package</a>. The tape and reel option is available for TUSB6015IZQE by adding an R suffix.

### **Device Block Diagram**

SLLS937 REVISION 1.4 SEPTEMBER 12, 2008

#### **Electrical Characteristics**

#### **Absolute Maximum Ratings**<sup>1</sup>

| 3.3V Supply Voltage, VDDA3P3                           | 0.5 V to 4.2 V           |

|--------------------------------------------------------|--------------------------|

| 1.8V Supply Voltage VDD18                              |                          |

| 1.5V Supply Voltage, VDD15, VDDD1P5, VDDCM1P5, VDDA1P5 |                          |

| USB VBUS Supply Voltage <sup>2</sup>                   | 0 V to 6.0 V             |

| Input voltage, V, 3.3V USB <sup>3</sup>                | 0.5 V to VDDA3P3 + 0.5 V |

| Output voltage, V <sub>o</sub> , 3.3V USB              | 0.5 V to VDDA3P3 + 0.5 V |

| Input clamp current, I <sub>IK</sub>                   | ±20 mA                   |

| Output clamp current, I <sub>ok</sub>                  | ±20 mA                   |

| Storage temperature range, Tstg                        | 65°C to 150°C            |

#### **Recommended Operating Conditions**

|                | PARAMETER                            |                              |      | TYP | MAX  | UNIT |

|----------------|--------------------------------------|------------------------------|------|-----|------|------|

| VDDA3P3        | Supply voltage for PHY A             | Analog                       | 3    | 3.3 | 3.6  | ٧    |

| VDD18          | Supply voltage for Digital           | I/O                          | 1.62 | 1.8 | 1.98 | V    |

| VDD15          | Supply voltage for Digital Core      |                              |      |     |      |      |

| VDDD1P5        | Supply voltage for PHY Digital       |                              | 1.05 | 4.5 | 4.05 | .,   |

| VDDCM1P5       | Supply voltage for PHY Common Module |                              | 1.35 | 1.5 | 1.65 | V    |

| VDDA1P5        | A1P5 Supply voltage for PHY Analog   |                              |      |     |      |      |

| T <sub>A</sub> | Operating Temperature                | TUSB6015I (Industrial grade) | -40  |     | 85   | °C   |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2</sup>VBUS can tolerate 6V for the lifetime of the device. It can handle 6.5V for 36 hours.

<sup>&</sup>lt;sup>3</sup>TUSB6015 complies with short circuit withstand and AC stress conditions as described in Chapter 7.1.1 of the USB 2.0 specification.

Electrical Characteristics for the Digital I/O  $T_A = -30^{\circ}\text{C} - 85^{\circ}\text{C}$ ,  $V_{DD18} = 1.8 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$  (Unless otherwise noted)

|                                 | PARAMETER                                             |                                       | TEST<br>CONDITIONS                 | MIN            | ТҮР | MAX             | UNIT |

|---------------------------------|-------------------------------------------------------|---------------------------------------|------------------------------------|----------------|-----|-----------------|------|

| VI                              | Input voltage                                         | LVCMOS                                |                                    | 0              |     | VDD18           | V    |

| $V_{o}$                         | Output voltage                                        | LVCMOS                                |                                    | 0              |     | VDD18           | V    |

| V <sub>IH</sub>                 | High-level input voltage                              | LVCMOS                                |                                    | 0.7 x<br>VDD18 |     | VDD18           | V    |

| V <sub>IL</sub>                 | Low-level input voltage                               | LVCMOS                                |                                    | 0              |     | 0.3 x<br>VDD18  | V    |

| V <sub>OH</sub>                 | High-level output voltage                             | LVCMOS                                | I <sub>OH</sub> = 8mA              | 0.8 ×<br>VDD18 |     |                 | V    |

|                                 |                                                       | LVCMOS open-drain                     | $I_{OL} = 4mA$                     |                |     | 0.22 x<br>VDD18 | v    |

| V <sub>OL</sub>                 | Low-level output voltage                              | LVCMOS                                | I <sub>oL</sub> = 8mA              |                |     | 0.22 x<br>VDD18 | V    |

|                                 |                                                       | LVCMOS<br>(1.5V_SWEN, 3.3V_SWEN only) | I <sub>oL</sub> = 100uA            |                | 10  |                 | mV   |

| I <sub>IH</sub>                 | High-level input current                              | LVCMOS                                | $V_i = V_i \max$                   |                |     | ±1              | uA   |

| I                               | Low-level input current                               | LVCMOS                                | $V_{_{\rm I}} = V_{_{\rm I}} \min$ |                |     | ±1              | uA   |

| l <sub>oz</sub>                 | I <sub>oz</sub> Output leakage current (high–Z)       |                                       | $V_i = V_i \max or V_{ss}$         |                |     | ±20             | uA   |

| C <sub>i</sub>                  | C <sub>i</sub> Input Capacitance (1.8V NOR Interface) |                                       |                                    |                |     | 2.43            | pF   |

| t <sub>r</sub> , t <sub>f</sub> | Input rise/fall time                                  |                                       |                                    | 0              |     | 25              | ns   |

### TUSB6015ZQE

SLLS937 REVISION 1.4 SEPTEMBER 12, 2008

### Vbus - Electrical Characteristics for the Integrated USB 2.0 Transceiver,

$$\begin{split} & T_{_{A}} = -30^{\circ}\text{C} - 85^{\circ}\text{C}, V_{_{DD15}} = 1.5\text{v} \pm 10\%, \ V_{_{DD18}} = 1.8\text{V} \pm 10\%, \ V_{_{DDA1P5}} = 1.5\text{ V} \ \pm 10\%, \\ & V_{_{DDA3P3}} = 3.3 \pm 10\%, V_{_{DDD1P5}} = 1.5\text{ V} \ \pm 10\%, \ V_{_{DDCM1P5}} = 1.5 \pm 10\%, \ V_{_{SS}} = 0\text{ V (unless otherwise noted)}^{\dagger} \end{split}$$

| PARAMETER                                         | MIN | TYP | MAX  | UNIT |

|---------------------------------------------------|-----|-----|------|------|

| Input Levels                                      |     |     |      |      |

| Vbus Input Impedance                              | 360 |     | 690  | kΩ   |

| Vbus Valid Comparator                             | 4.4 |     | 4.75 | ٧    |

| Vbus leakage current (when device is powered off) |     |     | 11   | uA   |

<sup>†</sup>Characterization only. Limits approved by design.

### DP and DM - Electrical Characteristics for the Integrated USB 2.0 Transceiver

$$\begin{split} & \textbf{T}_{\text{A}} = \textbf{-30}^{\circ} \text{C} \textbf{-85}^{\circ} \text{C}, \textbf{V}_{\text{DD15}} = \textbf{1.5} \textbf{v} \pm \textbf{10\%}, \ \textbf{V}_{\text{DD18}} = \textbf{1.8} \textbf{V} \pm \textbf{10\%}, \ \textbf{V}_{\text{DDA1P5}} = \textbf{1.5} \ \textbf{V} \ \pm \textbf{10\%}, \ \textbf{V}_{\text{DDA3P3}} = \textbf{3.3} \\ & \pm \textbf{10\%}, \textbf{V}_{\text{DDD1P5}} = \textbf{1.5}, \ \textbf{V} \ \pm \textbf{10\%}, \ \textbf{V}_{\text{DDCM1P5}} = \textbf{1.5} \pm \textbf{10\%}, \ \textbf{V}_{\text{SS}} = \textbf{0} \ \textbf{V} \ (\text{unless otherwise noted})^{\dagger} \end{split}$$

|                      | PARAMETER                                                              | MIN    | TYP | MAX     | UNIT |

|----------------------|------------------------------------------------------------------------|--------|-----|---------|------|

| Input Levels f       | or Full Speed                                                          |        |     |         |      |

| $V_{_{\mathrm{DI}}}$ | Full-speed differential input threshold                                | 0.2    |     |         | V    |

| V <sub>CM</sub>      | Input (was differential) common mode range                             | 0.8    |     | 2.5     | ٧    |

| Input Levels f       | or High Speed                                                          |        |     |         |      |

| V(HSSQ)              | High-speed squelch detection threshold (differential signal amplitude) | 100    |     | 150     | mV   |

| VDI                  | High-speed differential input threshold voltage                        | 100    |     |         | mV   |

| CHSLOAD              | Capacitance to ground on each line                                     |        |     | 5.5     | pF   |

| <b>Output Levels</b> | for Full Speed                                                         |        |     |         |      |

| VOL                  | Low-level output voltage                                               | 0      |     | 0.3     | V    |

| VOH                  | High-level output voltage (driven)                                     | 2.8    |     | 3.6     | ٧    |

| VO(SE1)              | Output voltage on SE1                                                  | 0.8    |     |         | ٧    |

| VO(CRS)              | Output signal crossover voltage                                        | 1.3    |     | 2       | V    |

| Output Levels        | for High Speed                                                         |        |     |         |      |

| V(HSOI)              | High-speed idle level                                                  | -10    |     | 10      | mV   |

| V(HSOH)              | High-speed data signaling high                                         | 360    |     | 440     | mV   |

| V(HSOL)              | High-speed data signaling low                                          | -10    |     | 10      | mV   |

| VID(CHIRPJ)          | Chirp J level (differential voltage)                                   | 700    |     | 1100    | mV   |

| VID(CHIRPK)          | Chirp K level (differential voltage)                                   | -900   |     | -500    | mV   |

| <b>Driver Charac</b> | teristics (Full Speed)                                                 |        |     |         |      |

| tr                   | Full-speed rise time                                                   | 4      |     | 20      | ns   |

| tf                   | Full-speed fall time                                                   | 4      |     | 20      | ns   |

| t(RFM)               | Full-speed rise/fall time matching                                     | 90%    |     | 110%    |      |

| <b>Driver Charac</b> | teristics (High Speed)                                                 |        |     |         |      |

| tr                   | Rise time (10%-90%)                                                    | 500    |     |         | ps   |

| tf                   | Fall time (10%-90%)                                                    | 500    |     |         | ps   |

| ro(HSDRV)            | Driver output resistance (serves as a high–speed termination)          | 40.5   |     | 49.5    | Ω    |

| t(FRFM)              | Differential rise and fall time matching                               | 90%    |     | 111.11% |      |

| Clock Timings        |                                                                        |        |     |         |      |

| t(HSDRAT)            | High-speed data rate                                                   | 479.76 |     | 480.24  | Mb/s |

| Single-Ended         | Receiver                                                               |        | - I |         |      |

| VIT+                 | Positive-going input threshold voltage                                 |        |     | 2.0     | V    |

| VIT-                 | Negative-going input threshold voltage                                 | 0.8    |     |         | V    |

| Vhys                 | Hysteresis voltage                                                     | 200    |     | 500     | mV   |

SLLS937 REVISION 1.4 SEPTEMBER 12, 2008

### DP and DM - Electrical Characteristics for the Integrated USB 2.0 Transceiver (CONT'D)

|       | INPUT LEAKAGE                                                        | TEST CONDITION              | MIN  | TYP                       | MAX | UNIT |

|-------|----------------------------------------------------------------------|-----------------------------|------|---------------------------|-----|------|

| DP/DM | Measurement taken with pull-up/dn disabled and device in idle mode   | DP/DM Voltage = 0 – VDDA3.3 | -1.3 |                           | 1.3 | uA   |

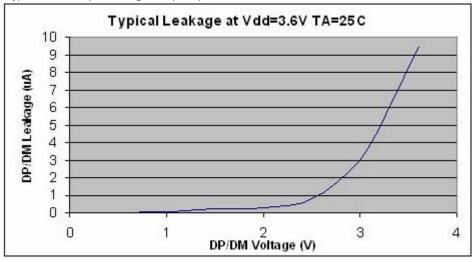

| DP/DM | Measurement taken with pull-up/dn disabled and device in active mode | DP/DM Voltage = 2V          |      | See<br>Chart <sup>1</sup> | 1.3 | uA   |

<sup>†</sup>Characterization only. Limits approved by design.

<sup>&</sup>lt;sup>1</sup>Typical DP/DM Input Leakage with pull-up/dn disabled and device in active mode

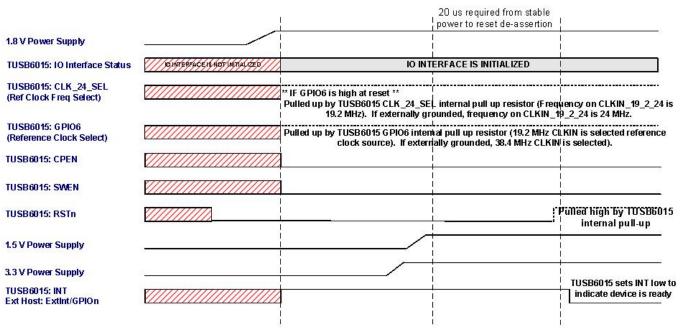

### **Power Sequencing Guidelines**

#### **Power-On Reset**

The system reset function ensures an orderly start-up sequence for the TUSB6015. There is a one active low external system reset input (RSTn). The reset initializes the Power/Reset/Clock Manager (PRCM) module, which in turn generates all the internal resets to initialize USB 2.0 PHY Macro and synchronous logic in the core. While reset is asserted (active low), the dual functional pin is sampled to determine device configuration after reset.

Since TUSB6015 relies on a dual function pin to configure the device during reset, the reset must be sufficiently long for (external) marginal pull-up/pull-down to achieve the intended levels. Reset pulse duration should be at least three times actual RC constant time (with typical 22 kOhm marginal pull-up resistor with 50 pF load, reset pulse should be at least  $3.3 \, \mu s$ ).

All functional pins remain in same state even after RSTn is de-asserted and stay in that state until internal core reset is cleared. The internal core reset is held for 16 system clock cycles following low-to-high RSTn transition.

Upon power-on reset, the following must be determined for proper device initialization:

System reference clock source

Device uses dual-mode pin to determine initial clock input setup. Dual function pin is latched during the reset. After the reset this terminal assumes the normal functionality.

| External Pin | Function                            | Description                                                                                                                                                    |

|--------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO6        | Reference Clock<br>Frequency Select | Determines the reference clock pin  0 - 38.4 MHz (CLKIN_38_4 pin is used)  1 - 19.2 MHz (CLKIN_19_2_24 pin is used)                                            |

| CLK_24_SEL   | CLKIN_19_2_24 Frequency Select      | Determines the reference frequency of the CLKIN_19_2_24 pin  0 - RSVD 1 - 19.2 MHz  If GPIO6 is low at reset, this pin will have no effect on clock selection. |

Upon exiting reset, the USB 2.0 PHY is not in the suspend state and the system clock (60 MHz) is enabled and free running. The USB 2.0 HS Peripheral Controller Core powers up and a session is not enabled. With session not enabled, all the USB 2.0 HS Peripheral Controller Core State Machine's are in the idle state.

After reset is de-asserted, the device asserts the DevReady interrupt to the External Host to indicate that it is ready to be programmed. The host reads the NOR Flash Interrupt Source register and decides how to proceed based on the device's current status.

#### **System Power-Up Sequence**

NOTE: Reference Clock Source selection is latched on RSTn rising edge.

No external components are required to select 19.2 MHz CLKIN as a reference clock source.

Signal state cannot be guaranteed

Signal state is stable and valid

### **Input Supply Current**

$T_{\Delta} = 25^{\circ}C$

#### VDDA3.3 = 3.3V + - 10%, VSS = 0V

|     | PARAMETER    | TEST CONDITIONS                          | TYP  | UNIT |

|-----|--------------|------------------------------------------|------|------|

|     |              | Idle <sup>1</sup>                        | 16.5 | uA   |

| IDD | Input supply | No Bus Activity <sup>2</sup>             | 3.7  | mA   |

| IDD | current      | Active (Transmit / Receive) <sup>3</sup> | 3.6  | mA   |

|     |              | Reset <sup>4</sup>                       | 2.7  | mA   |

#### $VDD1.8^7 = 1.8V +/- 10\%, VSS = 0V$

|     | PARAMETER    | TEST CONDITIONS                          | TYP   | UNIT |

|-----|--------------|------------------------------------------|-------|------|

|     |              | Idle <sup>1</sup>                        | 0.26  | uA   |

| IDD | Input supply | No Bus Activity <sup>2</sup>             | 157.0 | uA   |

| IDD | current      | Active (Transmit / Receive) <sup>3</sup> | 350.0 | uA   |

|     |              | Reset⁴                                   | 1.8   | mA   |

#### Cumulative VDD1.5 = 1.5V +/- 10%, VSS = 0V (VDD1.5, VDDD1.5, VDDCM1.5, VDDA1.5)

| (122110, 1222110, 122011110, |              |                                          |      |      |

|------------------------------|--------------|------------------------------------------|------|------|

|                              | PARAMETER    | TEST CONDITIONS                          | TYP  | UNIT |

|                              |              | Idle <sup>1</sup>                        | 2.0  | uA   |

| IDD                          | Input supply | No Bus Activity <sup>2</sup>             | 56.5 | mA   |

| IDD                          | current      | Active (Transmit / Receive) <sup>3</sup> | 58.0 | mA   |

|                              |              | Reset <sup>4</sup>                       | 29.2 | mA   |

Devidle bit set in Device PRCM Management Register, USB cable unplugged.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appear at the end of this data sheet.

<sup>&</sup>lt;sup>2</sup>Normal operation with no packets being transferred on the USB, except SOF every 125 μs. <sup>3</sup>Bulk IN and OUT on one End Point. Packet size is 512 bytes.

<sup>&</sup>lt;sup>4</sup>TUSB6015 RSTn asserted.

## **Input Clock Requirements**

### **CLKIN 19.2 MHz Recommended Operating Conditions**

|                             | . •              |

|-----------------------------|------------------|

| PARAMETER                   | VALUE            |

| Nominal Clock Frequency     |                  |

| (GPIO6 = high @ reset)      | 19.20 MHz        |

| (CLK_24_SEL = high @ reset) |                  |

| Frequency Accuracy          | +/- 100 ppm      |

| Maximum Rise/Fall Time      | 5ns (10% to 90%) |

| Input Clock Type            | Square Wave      |

| Duty Cycle                  | 45% - 55%        |

| Input Capacitance Loading   | 4pF              |

| Jitter                      | 118 ps           |

### **CLKIN 38.4 MHz Recommended Operating Conditions**

| •                                                | •                     |

|--------------------------------------------------|-----------------------|

| PARAMETER                                        | VALUE                 |

| Nominal Clock Frequency (GPIO6 = low @ reset)    | 38.40 MHz             |

| Frequency Accuracy                               | +/- 100 ppm           |

| Input Clock Type                                 | Sinusoid              |

| Duty Cycle                                       | 45% - 55%             |

| Input Common Mode Voltage VCM (V <sub>CM</sub> ) | 1 V +/- 100 mV        |

| Vp-p                                             | 200 mV – 800 mV       |

| Input Capacitance Loading                        | 5 pF                  |

| Rin                                              | 180 kOhms             |

| Jitter                                           | 100 ps (peak-to-peak) |

# **Timing Diagrams**

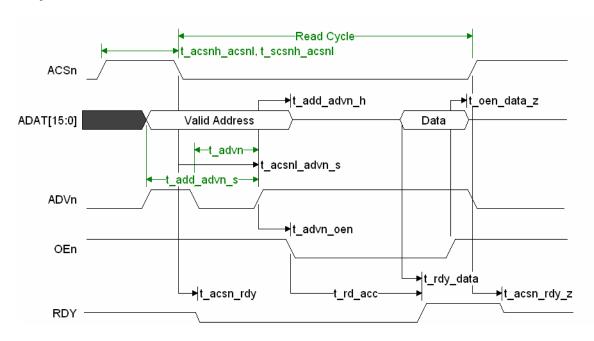

### **Asynchronous Read Access**

|                | PARAMETER                                                             | MIN | MAX | UNIT    |

|----------------|-----------------------------------------------------------------------|-----|-----|---------|

| t_acsnh_acsnl  | Delay time, ACSn high to ACSn low                                     | 8   |     | ns      |

| t_scsnh_acsnl  | Delay time, SCSn high to ACSn low                                     | 8   |     | ns      |

| t_add_advn_h   | Address Hold to ADVn high                                             | 0.8 |     | ns      |

| t_acsnl_advn_s | ACSn low Setup to ADVn high                                           | 18  |     | ns      |

| t_add_advn_s   | Address Setup to ADVn high                                            | 18  |     | ns      |

| t_advn_oen     | Sampled Address to OEn low                                            | 1   |     | ns      |

| t_advn         | ADVn low pulse                                                        | 7   |     | ns      |

|                | OEn low to RDY high (16-bit Register Access)                          | 6   | 8   | Sys Clk |

|                | OEn low to RDY high (32-bit Register Access) 1st 16-bit               | 5   | 7   | Sys Clk |

| t_rd_acc       | OEn low to RDY high (32-bit Register Access) 2 <sup>nd</sup> 16-bit   | 2   | 4   | Sys Clk |

|                | OEn low to RDY high (FIFO Access, with DMAREQ) 1st 16-bit             | 3   | 4   | Sys Clk |

|                | OEn low to RDY high (FIFO Access, with DMAREQ) 2 <sup>nd</sup> 16-bit | 3   | 4   | Sys Clk |

| t_acsn_rdy     | ACSn low to RDY low                                                   |     | 7   | ns      |

| t_acsn_rdy_z   | ACSn high to RDY high-Z                                               |     | 7   | ns      |

| t_oen_data_z   | OEn high to Data high-Z                                               |     | 8   | ns      |

| t_rdy_data     | Delay time, RDY high to data valid                                    | -1  | 6   | ns      |

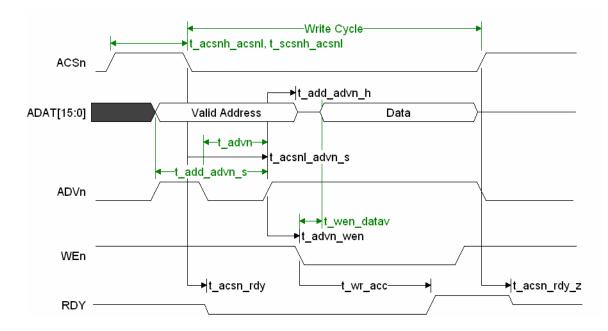

### **Asynchronous Write Access**

|                | PARAMETER                                                             | MIN | MAX   | UNIT    |

|----------------|-----------------------------------------------------------------------|-----|-------|---------|

| t_acsnh_ascnl  | Delay time, ACSn high to ACSn low                                     | 8   |       | ns      |

| t_scsnh_ascnl  | Delay time, SCSn high to ACSn low                                     | 8   |       | ns      |

| t_add_advn_h   | Address Hold to ADVn high                                             | 0.8 |       | ns      |

| t_acsnl_advn_s | ACSn low Setup to ADVn high                                           | 18  |       | ns      |

| t_add_advn_s   | Address Setup to ADVn high                                            | 18  |       | ns      |

| t_advn         | ADVn low pulse                                                        | 7   |       | ns      |

| t_advn_wen     | ADVn to WEn low                                                       | 1   |       | ns      |

|                | WEn low to RDY high (16-bit Register Access)                          | 3   | 5     | Sys Clk |

|                | WEn low to RDY high (32-bit Register Access) 1st 16-bit               | 2   | 4     | Sys Clk |

| t_wr_acc       | WEn low to RDY high (32-bit Register Access) 2 <sup>nd</sup> 16-bit   | 3   | 7     | Sys Clk |

|                | WEn low to RDY high (FIFO Access, with DMAREQ) 1st 16-bit             | 3   | 4     | Sys Clk |

|                | WEn low to RDY high (FIFO Access, with DMAREQ) 2 <sup>nd</sup> 16-bit | 3   | 4     | Sys Clk |

| t_acsn_rdy     | ACSn low to RDY low                                                   |     | 7     | ns      |

| t_acsn_rdy_z   | ACSn high to RDY high-Z                                               |     | 7     | ns      |

| t_wen_datav    | Delay time, WEn low to Data valid                                     |     | 1-5ns | Sys Clk |

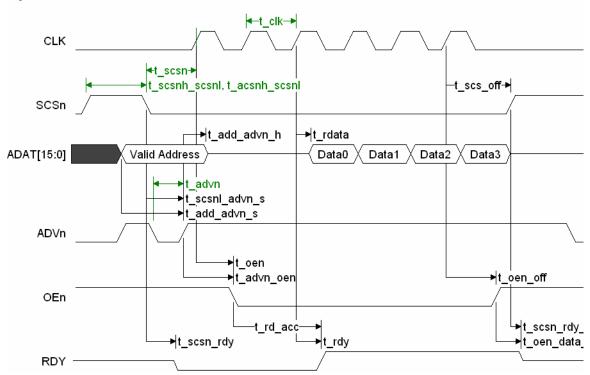

### **Synchronous Burst Read Access**

Notes: RDY going low is asynchronous to t\_scsn\_rdy. Going high, it is synchronous to CLK. Read Data output and RDY going high are synchronous to CLK. Valid Data Time programmable through Device Wait Count Register. Wait Count is not used for non-DMA synchronous reads.

|                | PARAMETER                                        | MIN            | MAX             | UNIT |

|----------------|--------------------------------------------------|----------------|-----------------|------|

| t_clk          | Cycle Time (max 67.5 MHz)                        | 14.8           |                 | ns   |

| t_scsnh_scsnl  | Delay time, SCSn high to SCSn low                | 8              |                 | ns   |

| t_acsnh_scsnl  | Delay time, ACSn high to SCSn low                | 8              |                 | ns   |

| t_scsn         | Delay time, SCSn low to first rising edge of CLK | 3ns            | 1+3ns           | CLK  |

| t_scs_off      | CLK to SCSn high                                 | 4              |                 | ns   |

| t_rdata        | Read data output delay                           | 2.2            | 9.2             | ns   |

| t_rdy          | RDY output delay                                 | 2.2            | 8.2             | Ns   |

| t_advn         | ADVn low pulse                                   | 7              |                 | Ns   |

| t_advn_oen     | ADVn high to OEn low                             | 3              |                 | Ns   |

| t_oen_off      | CLK to OEn high                                  | 4              |                 | Ns   |

| t oen          | OEn setup to CLK high                            | 3.75           |                 | Ns   |

| i_oen          | OEn hold time                                    | 0              |                 |      |

| t_rd_acc       | Valid Data Time (with DMAREQ)                    | 1 <sup>1</sup> | 32 <sup>2</sup> | CLK  |

| t_add_advn_h   | Addr Hold time to ADVn high                      | 0.8            |                 | Ns   |

| t_scsnl_advn_s | SCSn low Setup to ADVn high                      | 12             |                 | Ns   |

| t_add_advn_s   | Address Setup to ADVn high                       | 12             |                 | Ns   |

| t_scsn_rdy     | SCSn low to RDY valid low                        |                | 7               | ns   |

| t_scsn_rdy_z   | SCSn high to RDY high-Z                          |                | 7               | ns   |

| t_oen_data_z   | OEn high to Data high-Z                          |                | 8               | ns   |

Device Wait Count Register = 0 or 1.

Device Wait Count Register = 31.

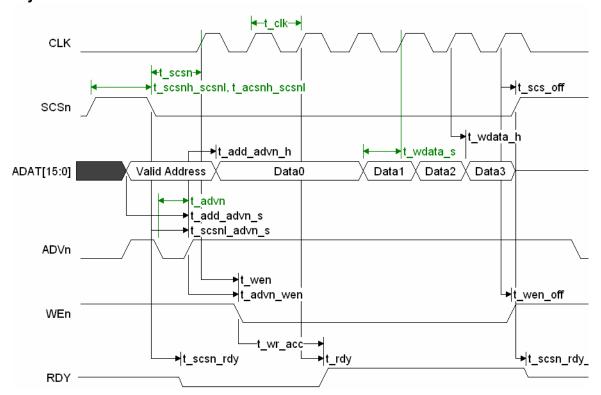

### **Synchronous Burst Write Access**

Note: RDY going low is asynchronous to t\_scsn\_rdy. Going high, it is synchronous to CLK. Valid Data Time programmable through Device Wait Count Register. For Wait Count values other than 0 or 1 (when DMAREQ is used), t\_wr\_acc = Wait Count + 1.

|                | PARAMETER                                        | MIN            | MAX             | UNIT    |

|----------------|--------------------------------------------------|----------------|-----------------|---------|

| t_clk          | Cycle Time (max 67.5 MHz)                        | 14.8           |                 | ns      |

| t_scsnh_scsnl  | Delay time, SCSn high to SCSn low                | 8              |                 | ns      |

| t_acsnh_scsnl  | Delay time, ACSn high to SCSn low                | 8              |                 | ns      |

| t_scsn         | Delay time, SCSn low to first rising edge of CLK | 3ns            | 1+3ns           | CLK     |

| t_scs_off      | CLK to SCSn high                                 | 1+3ns          |                 | Sys Clk |

| t_wdata_s      | Data setup to CLK high                           | 3.75           |                 | ns      |

| t_wdata_h      | Data hold time                                   | 0.6            |                 | ns      |

| t_rdy          | CLK to RDY output delay                          | 2.2            | 8.2             | ns      |

| t_add_advn_h   | Address Hold                                     | 0.8            |                 | ns      |

| t_scsnl_advn_s | SCSn low Setup to ADVn high                      | 12             |                 | ns      |

| t_add_advn_s   | Address Setup to ADVn high                       | 12             |                 | ns      |

| t_advn         | ADVn low pulse                                   | 7              |                 | ns      |

| t_advn_wen     | ADVn high to WEn low                             | 1+3ns          |                 | CLK     |

| t_wen_off      | CLK to WEn high                                  | 1+3ns          |                 | Sys Clk |

| t won          | WEn setup to CLK high                            | 3.75           |                 | ns      |

| t_wen          | WEn hold time                                    | 0              |                 |         |

| t_wr_acc       | Valid Data Time (with DMAREQ)                    | 1 <sup>1</sup> | 32 <sup>2</sup> | CLK     |

| t_scsn_rdy     | SCSn low to RDY valid low                        |                | 7               | ns      |

| t_scsn_rdy_z   | SCSn high to RDY high-Z                          |                | 7               | ns      |

Device Wait Count Register = 0 or 1.

<sup>&</sup>lt;sup>2</sup>Device Wait Count Register = 31.

# **Pin Descriptions**

| TERMINAL      |      |                                 |     |                 |                                                                                                                                                                        |

|---------------|------|---------------------------------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | BALL | TYPE                            | I/O | RESET STATE     | DESCRIPTION                                                                                                                                                            |

| VDD15         | A1   | Supply                          | -   | -               | Digital core power supply, 1.5 V                                                                                                                                       |

| VSS           | A2   | Supply                          | -   | -               | Ground                                                                                                                                                                 |

| CLK_24_SEL    | А3   | LVCMOS<br>Failsafe <sup>1</sup> | I   | In with Pull-up | CLKIN_19_2_24 Frequency Select at Reset CLK 24 SEL = HIGH, 19.2 MHz CLK 24 SEL = LOW, RSVD  If GPIO6 is low at reset, this pin will have no effect on clock selection. |

| CLKIN_38_4    | A4   | LVCMOS<br>Failsafe <sup>1</sup> | I   | In              | System Clock In. Connect directly to ground if not used.                                                                                                               |

| CLKIN_19_2_24 | A5   | LVCMOS<br>Failsafe <sup>1</sup> | I   | In              | System Clock In. Connect directly to ground if not used.                                                                                                               |

| VSS           | A6   | Supply                          | -   | -               | Ground                                                                                                                                                                 |

| VDD18         | A7   | Supply                          | -   | -               | IO Power Supply, 1.8 V                                                                                                                                                 |

| OEn           | A8   | LVCMOS<br>Failsafe <sup>1</sup> | I   | In with Pull-up | Output Enable                                                                                                                                                          |

| VDD15         | A9   | Supply                          | -   | -               | Digital core power supply, 1.5 V                                                                                                                                       |

| VSSREF        | B1   | Supply                          | -   | -               | Ground reference for the reference circuits                                                                                                                            |

| GPIO7         | B2   | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 7                                                                                                                                                                 |

| VDD15         | В3   | Supply                          | -   | -               | Digital core power supply, 1.5 V                                                                                                                                       |

| VSS           | B4   | Supply                          | -   | -               | Ground                                                                                                                                                                 |

| VDD18         | B5   | Supply                          | -   | -               | IO Power Supply, 1.8 V                                                                                                                                                 |

| GPIO2_DMAREQ2 | В6   | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 2 / DMA Request 2                                                                                                                                                 |

| ADAT15        | В7   | LVCMOS                          | I/O | In with Pull-up | Multiplexed ADDRESS.15/DATA.14                                                                                                                                         |

| ADAT16        | B8   | LVCMOS                          | I/O | In with Pull-up | Multiplexed ADDRESS.16/DATA.15                                                                                                                                         |

| VSS           | В9   | Supply                          | -   | -               | Ground                                                                                                                                                                 |

| VDDA3P3       | C1   | Supply                          | -   | -               | 3.3V Analog Supply                                                                                                                                                     |

| R1            | C2   | Bias                            | I   | -               | High precision external resistor used for calibration. (R1 value: 10.7 K +/- 1%)                                                                                       |

| GPIO4_DMAREQ4 | C4   | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 4 / DMA Request 4                                                                                                                                                 |

| VDD15         | C5   | Supply                          | -   | -               | Digital core power supply, 1.5 V                                                                                                                                       |

| ADVn          | C6   | LVCMOS<br>Failsafe <sup>1</sup> | I   | In with Pull-up | Address Valid                                                                                                                                                          |

| ADAT12        | C7   | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.12/DATA.11                                                                                                                                         |

| ADAT14        | C8   | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.14/DATA.13                                                                                                                                         |

|               | ·  |                                 |     |                 |                                                                                              |

|---------------|----|---------------------------------|-----|-----------------|----------------------------------------------------------------------------------------------|

| CLK           | C9 | LVCMOS<br>Failsafe <sup>1</sup> | ı   | In with Pull-up | NOR Interface Clock                                                                          |

| DP            | D1 | USB                             | I/O | -               | USB Differential Pair                                                                        |

| VDDCM1P5      | D2 | Supply                          | -   | -               | 1.5V PLL Supply                                                                              |

| VSSCM1P5      | D3 | Supply                          | _   | _               | 1.5V PLL Ground                                                                              |

| TEST          | D4 | LVCMOS                          | I   | -               | Test Mode. Under normal operation this signal should be tied directly to GND.                |

| GPIO1         | D5 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 1                                                                                       |

| WEn           | D6 | LVCMOS<br>Failsafe <sup>1</sup> | ı   | In with Pull-up | Write Enable                                                                                 |

| ADAT13        | D7 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.13/DATA.12                                                               |

| ADAT11        | D8 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.11/DATA.10                                                               |

| VDD15         | D9 | Supply                          | -   | -               | Digital core power supply, 1.5 V                                                             |

| VSSA1P5       | E1 | Supply                          | -   | -               | 1.5V Analog Ground                                                                           |

| DM            | E2 | USB                             | I/O | -               | USB Differential Pair                                                                        |

| VDDA1P5       | E3 | Supply                          | -   | -               | 1.5V Analog Supply                                                                           |

| VSSA3P3       | E4 | Supply                          | -   | -               | 3.3V Analog Ground                                                                           |

| VSS           | E5 | Supply                          | -   | -               | Ground                                                                                       |

| ADAT2         | E6 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.2/DATA.1                                                                 |

| GPIO5_DMAREQ5 | E7 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 5 / DMA Request 5                                                                       |

| GPIO3_DMAREQ3 | E8 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 3 / DMA Request 3                                                                       |

| VSS           | E9 | Supply                          | -   | -               | Ground                                                                                       |

| VDDD1P5       | F1 | Supply                          | -   | -               | 1.5V Digital Supply                                                                          |

| ID            | F2 | USB                             | I   | -               | Should be left floating as a USB device.                                                     |

| VBUS          | F3 | USB                             | ı   | -               | USB VBUS                                                                                     |

| VSSD1P5       | F4 | Supply                          | _   | -               | 1.5V Digital Ground                                                                          |

| GPIO6         | F5 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | GPIO 6 / Input Clock Source Select at reset. GPIO6 = HIGH, 19.2/24 MHz GPIO6 = LOW, 38.4 MHz |

| ADAT1         | F6 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.1/DATA.0                                                                 |

| ADAT10        | F7 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.10/DATA.9                                                                |

| ADAT9         | F8 | LVCMOS<br>Failsafe <sup>1</sup> | I/O | In with Pull-up | Multiplexed ADDRESS.9/DATA.8                                                                 |

| VDD15         | F9 | Supply                          | -   | In with Pull-up | Digital core power supply, 1.5 V                                                             |

| VSS           | G1 | Supply                          | -   | -               | Ground                                                                                       |

| 1.5V_SWEN     | G2 | LVCMOS                          | 0   | 0               | Switch Enable for 1.5V supply for Vbat/Vbus                                                  |

|               |                                    | Failsafe <sup>1</sup> |     |                     | Switch, if applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------|------------------------------------|-----------------------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.01/.014/51/ |                                    | LVCMOS                |     |                     | Switch Enable for 3.3V supply for Vbat/Vbus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3.3V_SWEN     | G3                                 | Failsafe <sup>1</sup> | 0   | 0                   | Switch, if applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|               |                                    | LVCMOS                |     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ACSn          | G4                                 | Failsafe <sup>1</sup> | ı   | In with Pull-up     | Asynchronous Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|               |                                    | LVCMOS                |     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ADAT3         | G5                                 | Failsafe <sup>1</sup> | I/O | In with Pull-up     | Multiplexed ADDRESS.3/DATA.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ADAT4         | 00                                 | LVCMOS                | 1/0 | la viitla Dvill va  | Multiplaced ADDDECC 4/DATA 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ADAT4         | G6                                 | Failsafe <sup>1</sup> | I/O | In with Pull-up     | Multiplexed ADDRESS.4/DATA.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RDY           | G7                                 | LVCMOS                | 0   | high z              | Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| KDT           | G/                                 | tri-state             | U   | high z              | Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SCSn          | G8                                 | LVCMOS                | I   | In with Pull-up     | Synchronous Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| VSS           | G9                                 | Supply                | -   | -                   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |