# **AK2401A**

# **Direct Conversion Transceiver**

## 1. General Description

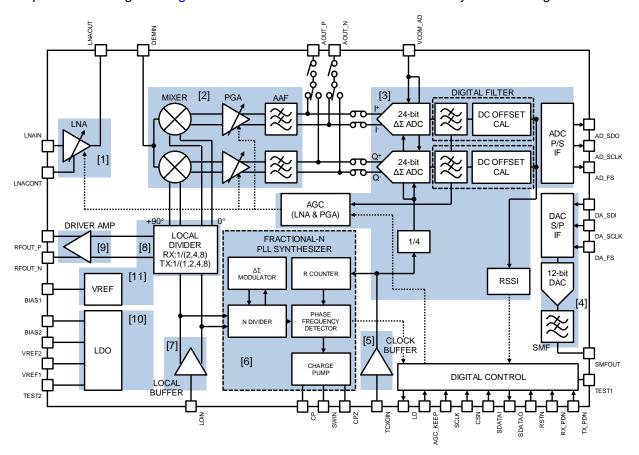

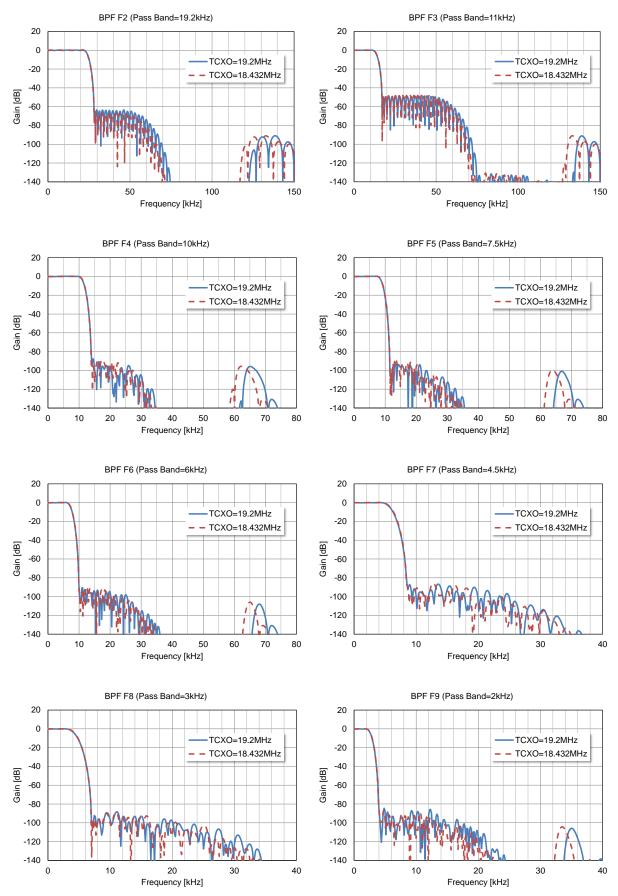

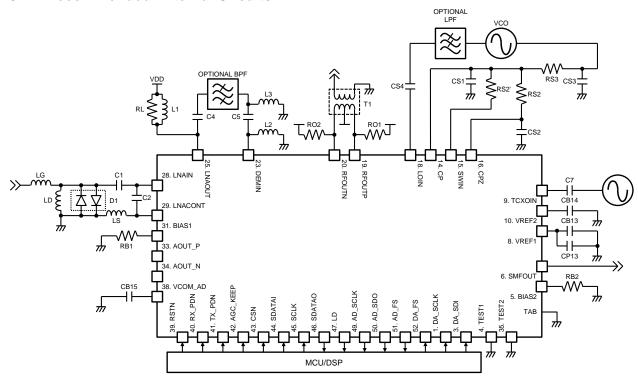

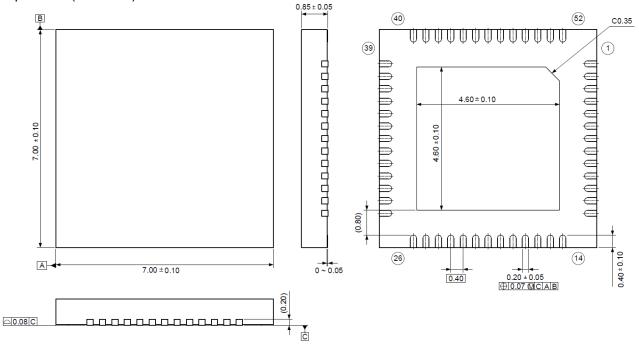

The AK2401A is a direct conversion transceiver that provides high performance narrow-band radio communication. The receiver block of the AK2401A integrates a LNA, I/Q demodulator, PGA and 24-bit delta-sigma ADC, and realizes both performances of high sensitivity and high tolerance to adjacent channel interference, intermodulation and blocking. Digital filter that is able to support channel selection for multiple radio systems, enabling simple system designing for a radio platform. The AK2401A also integrates a delta-sigma Fractional-N synthesizer that composes a high performance PLL with an external VCO. The transmission block has a DAC and a driver amplifier. The AK2401A is housed in a small QFN package (7mm x 7mm), realizing to downsize wire-less applications.

| <ul> <li>□ Operating Frequency: 29MHz to 960MHz</li> <li>□ Power Supply: 2.7 to 3.3V (DVDD: (1.7 to 1.9V) or (2.7 to 3.3V))</li> <li>□ Operational Temperature: -40 to +85°C</li> <li>□ LNA: Gain 15dB, NF 1.5dB, IIP3 +7dBm</li> <li>□ High Linearity Direct Conversion I/Q Demodulator</li> <li>□ 24-bit ΔΣ A/D Converter: up to 150kHz Output Sampling Frequency (TCXO=19.2MHz)</li> <li>□ Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>□ Automatic Gain Control (AGC) function for LNA and PGA</li> <li>□ Real-time DC Offset Canceller (RDOC) Function</li> </ul> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>□ Operational Temperature: -40 to +85°C</li> <li>□ LNA: Gain 15dB, NF 1.5dB, IIP3 +7dBm</li> <li>□ High Linearity Direct Conversion I/Q Demodulator</li> <li>□ 24-bit ΔΣ A/D Converter: up to 150kHz Output Sampling Frequency (TCXO=19.2MHz)</li> <li>□ Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>□ Automatic Gain Control (AGC) function for LNA and PGA</li> </ul>                                                                                                                                                                                      |

| <ul> <li>LNA: Gain 15dB, NF 1.5dB, IIP3 +7dBm</li> <li>High Linearity Direct Conversion I/Q Demodulator</li> <li>24-bit ΔΣ A/D Converter: up to 150kHz Output Sampling Frequency (TCXO=19.2MHz)</li> <li>Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>Automatic Gain Control (AGC) function for LNA and PGA</li> </ul>                                                                                                                                                                                                                                                 |

| <ul> <li>High Linearity Direct Conversion I/Q Demodulator</li> <li>24-bit ΔΣ A/D Converter: up to 150kHz Output Sampling Frequency (TCXO=19.2MHz)</li> <li>Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>Automatic Gain Control (AGC) function for LNA and PGA</li> </ul>                                                                                                                                                                                                                                                                                               |

| <ul> <li>24-bit ΔΣ A/D Converter: up to 150kHz Output Sampling Frequency (TCXO=19.2MHz)</li> <li>Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>Automatic Gain Control (AGC) function for LNA and PGA</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>□ Band Changeable Digital Filter (Bandwidth can be set arbitrarily)</li> <li>□ Automatic Gain Control (AGC) function for LNA and PGA</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ☐ Automatic Gain Control (AGC) function for LNA and PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ☐ Real-time DC Offset Canceller (RDOC) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| □ RSSI Function: Data read by SPI communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18-bit ΔΣ Fractional-N PLL Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| □ Digital Frequency Modulation (FM/FSK) by Frequency Offset Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| □ Fast Lock Function reduces Lock-up Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| □ 12-bit D/A Converter: 200kHz Max. Sampling Frequency, S/N 72dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| □ Transmission Driver Amplifier: −6 to +4 dBm Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| □ Local Signal Dividing Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ☐ TCXO Frequency: 18.432MHz / 19.2MHz are recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

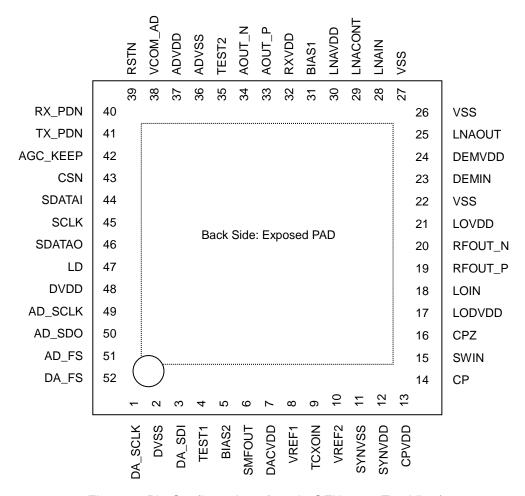

| ☐ Package: 52-pin QFN (7×7×0.85mm 0.4 mm pitch)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### 3. Application

- Narrow Band Radio Communication: 6.25kHz/7.5kHz/12.5kHz/15kHz/20kHz/25kHz/ 50kHz/100kHz/150kHz / etc.

- Modulation Method: FM/2FSK/4FSK/QPSK/π/4 DQPSK /16QAM/64QAM (Modulation / demodulation needs to be done externally. Modem function is not installed.)

- Analog/Digital Dual Mode Transceiver

- Digital Radio System for Industrial Use

- Public safety and Community/Emergency Radio System

- Convenience Transceiver

- Marine/Mobile Communication System

- Low power / Telemeter Transmitter

- Amateur Radio System

# 4. Table of Contents

| 1.                    | General                  | Description                                                         | . 1 |

|-----------------------|--------------------------|---------------------------------------------------------------------|-----|

| 2.                    |                          |                                                                     |     |

| <br>3.                |                          | on                                                                  |     |

| 3.<br>4.              |                          | Contents                                                            |     |

| <del>-1</del> .<br>5. |                          | agram and Functions                                                 |     |

| ວ.<br>5.1             |                          | sk Diagram                                                          |     |

| 5.1                   |                          |                                                                     |     |

|                       |                          | ctions                                                              |     |

| 6.                    |                          | igurations and Functions                                            |     |

| 6.1                   |                          | Configurations                                                      |     |

| 6.2                   |                          | Functions                                                           |     |

| 6.3                   |                          | dling of Unused Pins                                                |     |

| 7.                    |                          | Maximum Ratings                                                     |     |

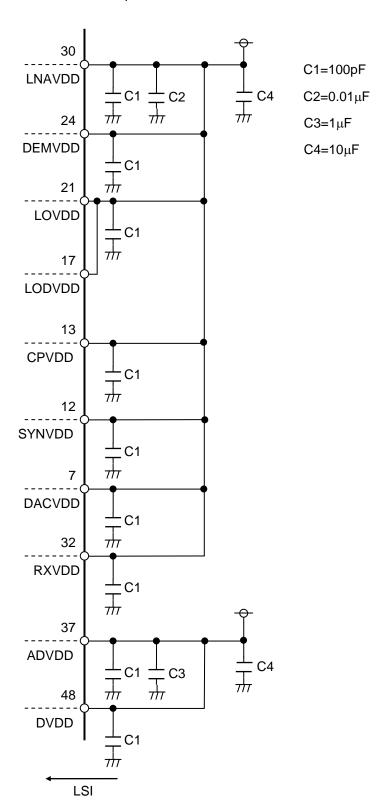

| 8.                    | Recomm                   | nended Operating Conditions                                         | 11  |

| 9.                    | Digital C                | haracteristics                                                      | 12  |

| 9.1                   | . DC                     | Characteristics                                                     | 12  |

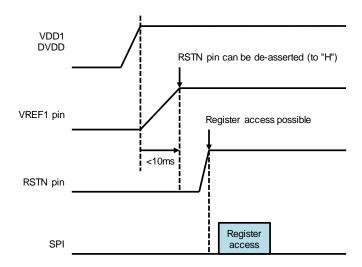

| 9.2                   |                          | tem Reset                                                           |     |

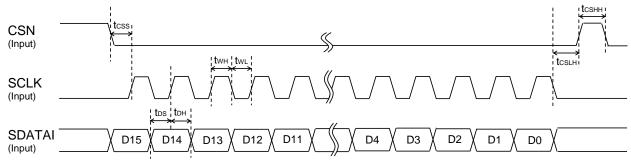

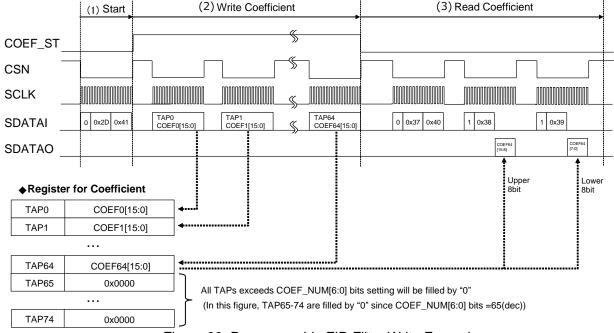

| 9.3                   |                          | al Interface Timing for Register Access                             |     |

| 9.4                   |                          | al Interface Timing for Programmable FIR Filter Coefficient Setting |     |

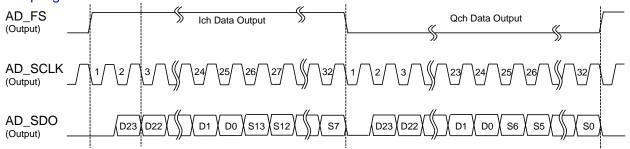

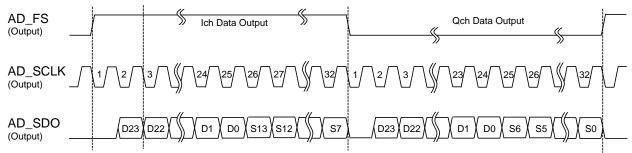

| 9.5                   |                          | al Interface Timing for ADC Data Readout                            |     |

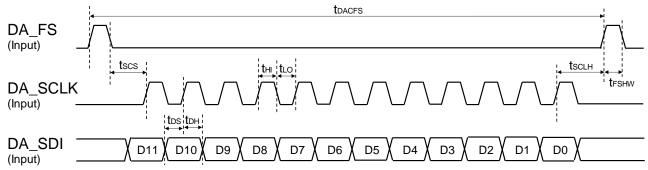

| 9.6                   |                          | al Interface Timing for DAC Data Write                              |     |

| 9.6<br>10.            |                          | Characteristics                                                     |     |

|                       |                          |                                                                     |     |

| 10.                   |                          | eiving Characteristics                                              |     |

|                       | 10.1.1.                  | LNA                                                                 |     |

|                       | 10.1.2.                  | MIXER+PGA+AAF+ADC                                                   |     |

|                       |                          | LOCAL BUFFER+LOCAL DIVIDER (RX)                                     |     |

|                       | 10.1.4.                  | PLL SYNTHESIZER                                                     |     |

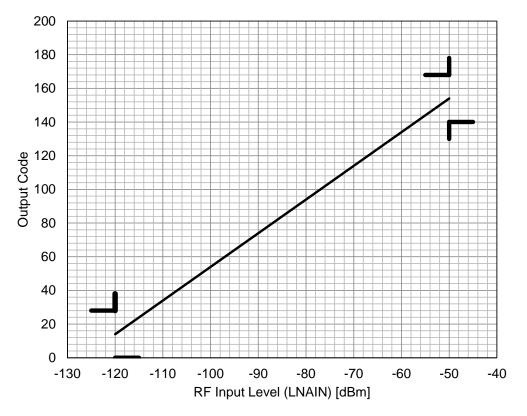

|                       | 10.1.5.                  | RSSI                                                                |     |

| 10.                   | <ol><li>Trar</li></ol>   | nsmission Characteristics                                           |     |

| •                     | 10.2.1.                  | DAC+SMF                                                             |     |

| •                     | 10.2.2.                  | LOCAL BUFFER+LOCAL DIVIDER(TX)+DRIVER AMP                           | 21  |

| 10.                   | 3. Curi                  | ent Consumption                                                     | 22  |

| 11.                   | Typical F                | Performance Characteristics                                         | 23  |

| 12.                   |                          | n Sequence                                                          |     |

| 12.                   |                          | ver-up Sequence                                                     |     |

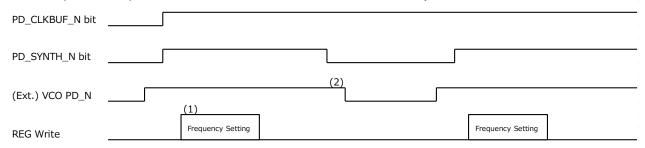

| 12.                   |                          | ver-up Sequence of PLL Synthesizer                                  |     |

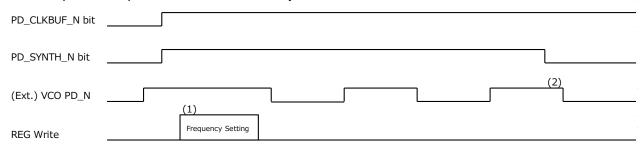

| 12.                   | _                        | ver-down Sequence of PLL Synthesizer                                |     |

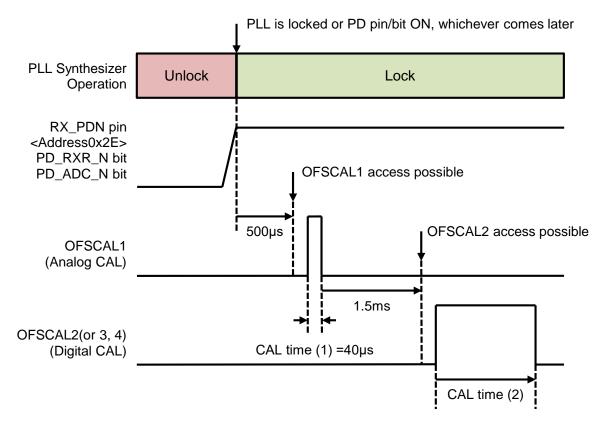

| 12.                   |                          | Offset Calibration Sequence                                         |     |

|                       |                          |                                                                     |     |

| 13.                   |                          | al Descriptions                                                     |     |

| 13.                   |                          | ver Management                                                      |     |

| 13.                   |                          | ration Mode Setting                                                 |     |

| 13.                   |                          | el Diagram                                                          |     |

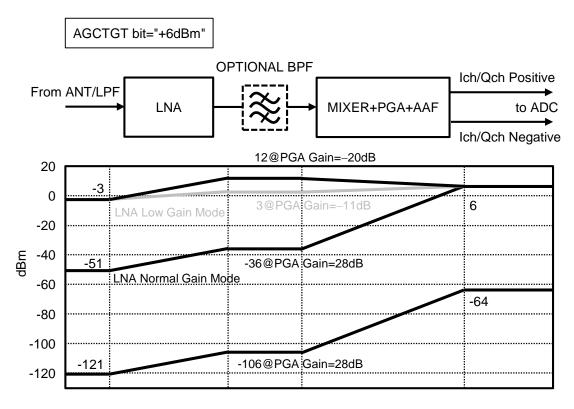

|                       | 13.3.1.                  | Level Diagram of Analog Receiving Circuit                           |     |

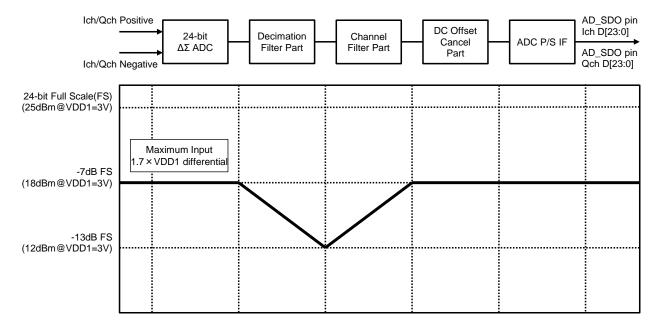

|                       | 13.3.2.                  | Level Diagram of Digital Receiving Circuit                          |     |

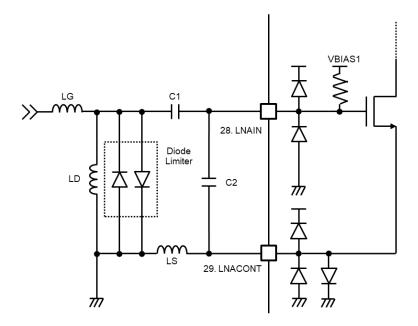

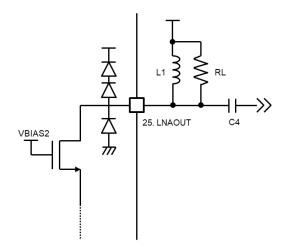

| 13.                   | 4. Ana                   | log Receiving Circuit (LNA)                                         | 32  |

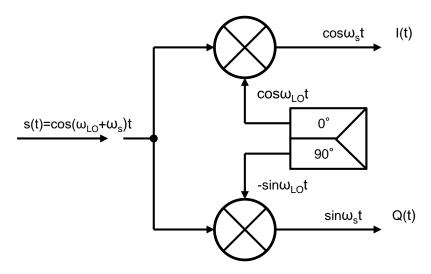

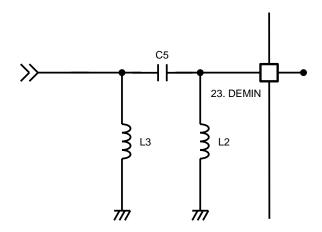

| 13.                   | <ol><li>5. Ana</li></ol> | log Receiving Circuit (MIXER, PGA, AAF)                             |     |

| •                     | 13.5.1.                  | MIXER                                                               | 34  |

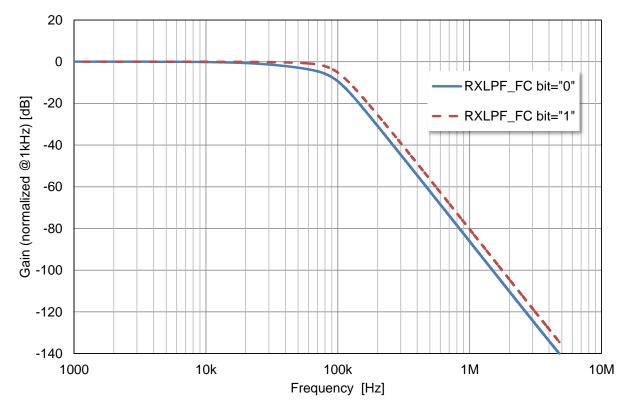

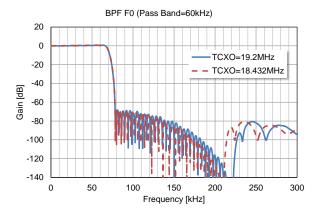

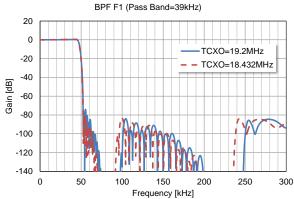

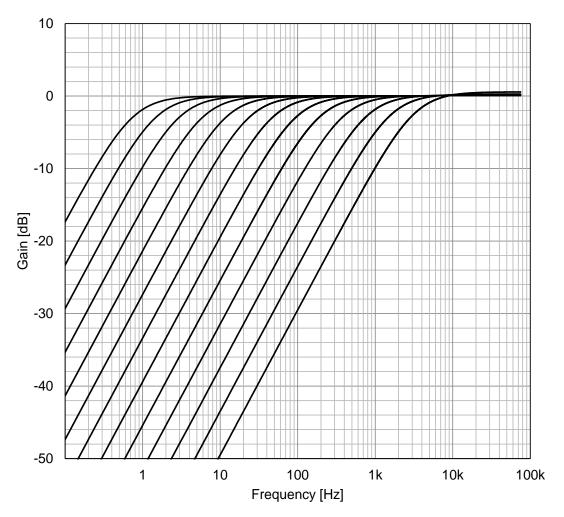

| •                     | 13.5.2.                  | Analog Filter Frequency Characteristics                             |     |

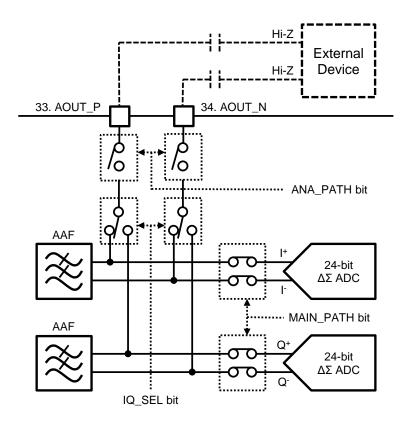

|                       | 13.5.3.                  | Output Path Selection of Analog Baseband Signal                     |     |

| 13.                   |                          | CAL BUFFER, LOCAL DIVIDER                                           |     |

|                       | 0. <u> </u>              | LOCAL BUFFER                                                        |     |

|                       | 13.6.2.                  | LOCAL DIVIDER.                                                      |     |

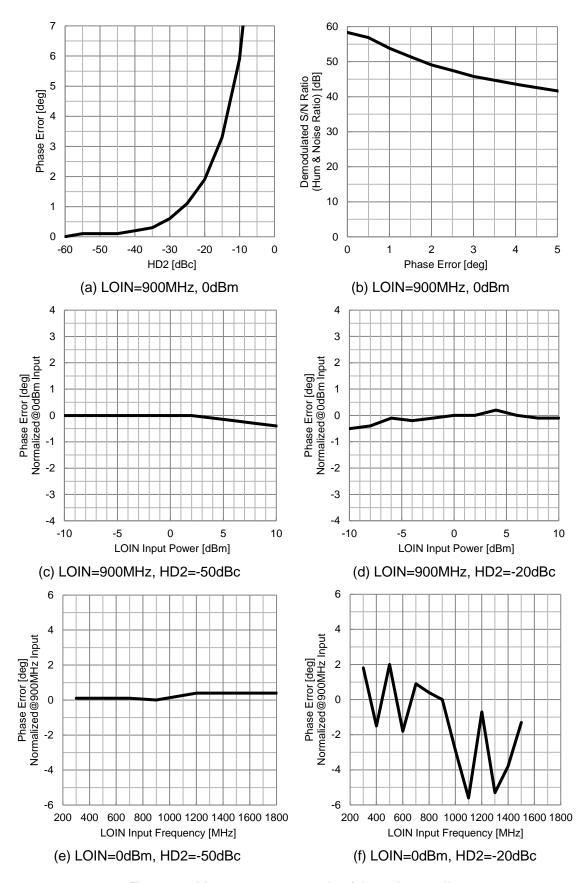

|                       | 13.6.3.                  | Phase Calibration                                                   |     |

|                       |                          |                                                                     |     |

| 13.                   |                          | SYNTHESIZER                                                         |     |

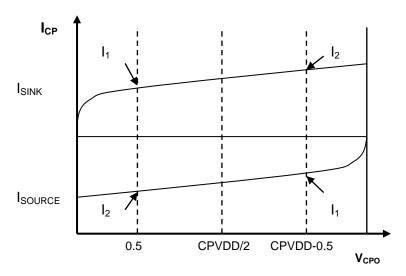

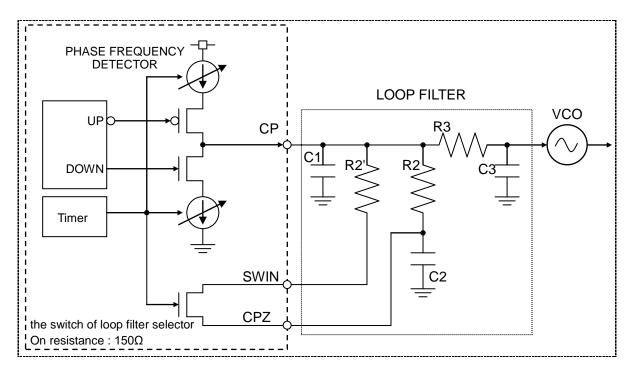

|                       |                          | CHARGE PUMP, LOOP FILTER                                            |     |

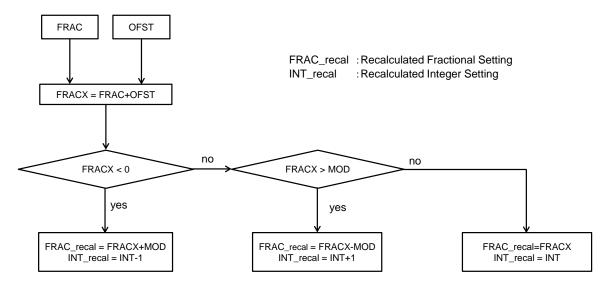

|                       | 13.7.2.                  | Frequency Setting                                                   | 4(  |

| 13.7.3           | and a series of the series of |          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

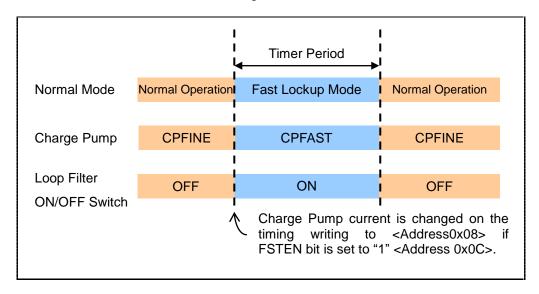

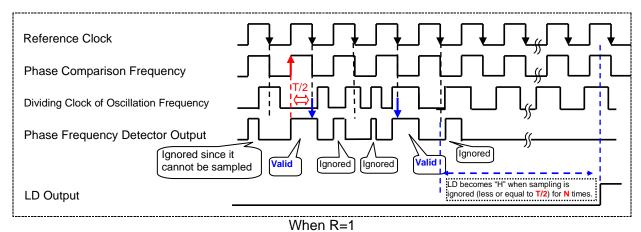

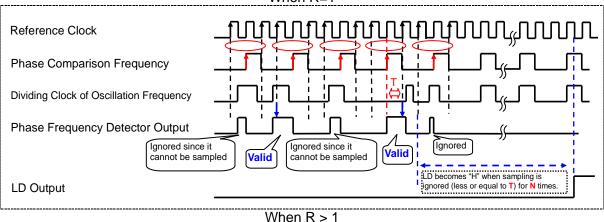

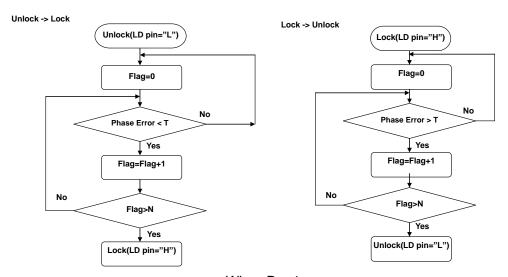

| 13.7.4           | Fast Lock Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43       |

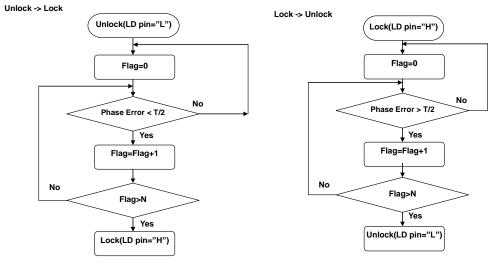

| 13.7.5           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44       |

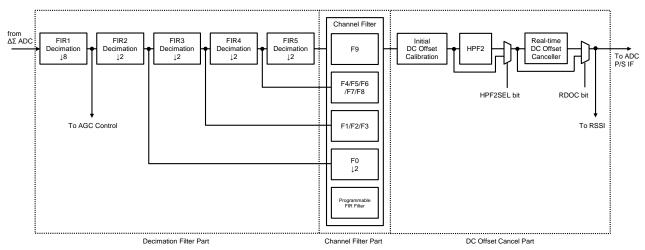

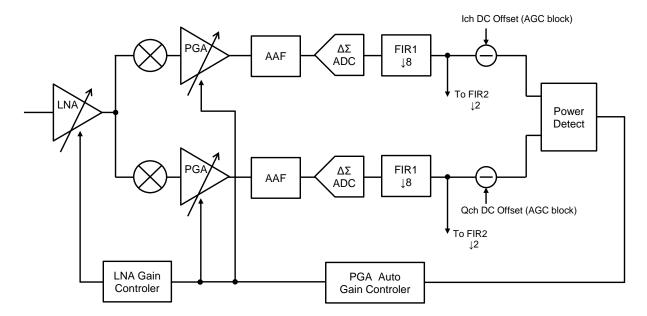

| 13.8.            | Digital Receiving Circuit (ADC, DIGITAL FILTER, RSSI, AGC, ADC P/S IF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46       |

| 13.8.1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.2           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46       |

| 13.8.3           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

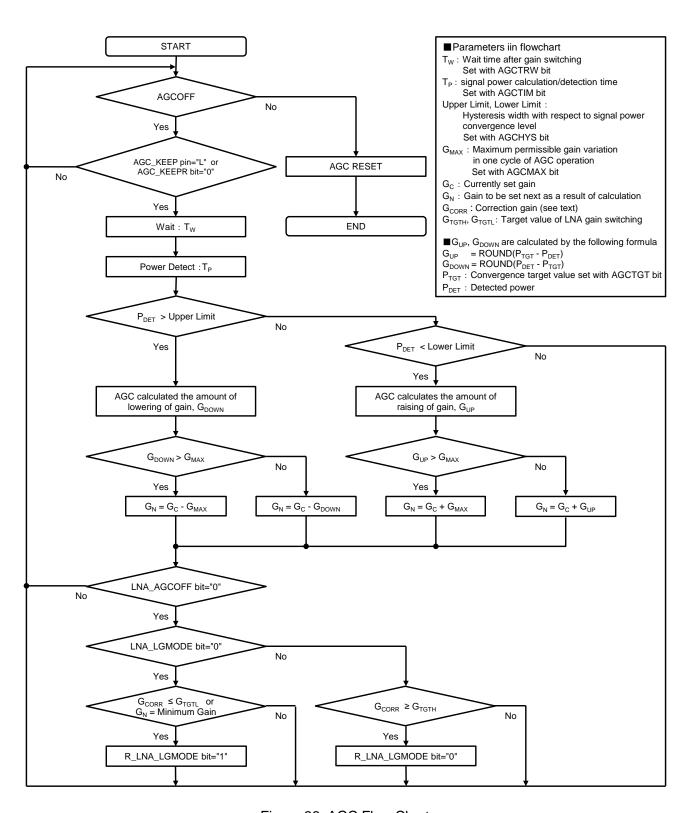

| 13.8.4           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.5           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.6           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.8           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.9           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 13.8.1           | 1 1 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 13.8.1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                  | ister Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|                  | ister Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 15.1.            | <0x01-0x03>FRAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 15.2.            | <0x04-0x06>MOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       |

| 15.3.            | <0x07-0x08>INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       |

| 15.4.            | <0x09>RDIV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72       |

| 15.5.            | <0x0A-0x0B>CP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 15.6.            | <0x0C>SYNTH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 15.7.            | <0x0D-0x0E>FAST TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 15.8.            | <0x0F-0x11>FREQ OFFSET1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 15.9.            | <0x12>LOCAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

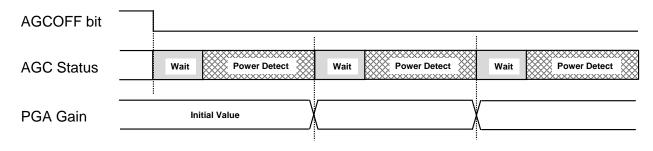

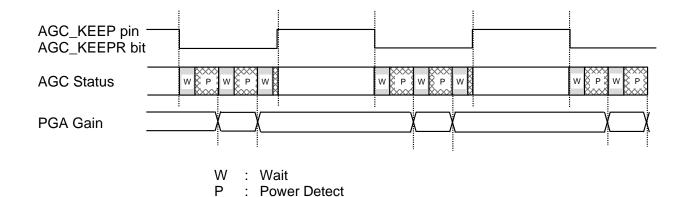

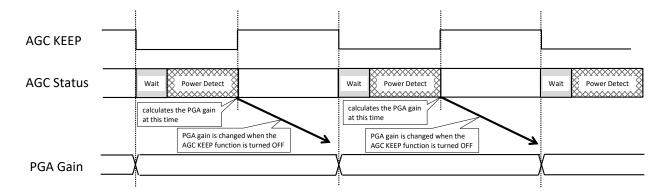

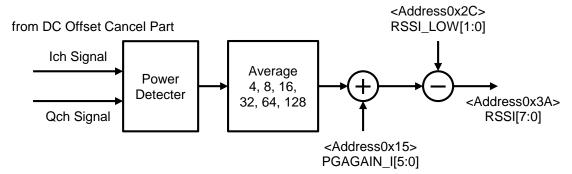

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |