# Piccolo F280049 controlCARD Information Guide

The Piccolo F280049 controlCARD from Texas Instruments (TI) is intended to provide a well-filtered robust design capable of working in most environments. This document describes the hardware details of the F280049 controlCARD and explains the functions, locations of jumpers, and connectors present on the board.

| Contents |

|----------|

|----------|

| 1 | Introduction |                                                     |   |  |

|---|--------------|-----------------------------------------------------|---|--|

| 2 | Errata       |                                                     |   |  |

|   | 2.1          | Warnings, Notes, and Errata                         | 3 |  |

| 3 | Getting      | g Familiar With the controlCARD                     | 3 |  |

|   | 3.1          | F280049 controlCARD Features                        | 3 |  |

|   | 3.2          | F28004x Device Description                          | 3 |  |

|   | 3.3          | Assumed Operating Conditions                        | 4 |  |

|   | 3.4          | Using the controlCARD                               | 4 |  |

|   | 3.5          | Software Development                                | 4 |  |

| 4 | Specia       | al Notes                                            |   |  |

|   | 4.1          | XDS100v2 Emulator and SCI/UART Connectivity         | 5 |  |

|   | 4.2          | cJTAG Usage                                         |   |  |

|   | 4.3          | Evaluation of the Programmable Gain Amplifier (PGA) | 6 |  |

|   | 4.4          | Evaluation of the Internal DC/DC Converter          |   |  |

| 5 | Hardw        | are References                                      | 8 |  |

#### List of Figures

| 1 | F280049 controlCARD Installed on TMDSHSECDOCK                         | 2 |

|---|-----------------------------------------------------------------------|---|

| 2 | XDS100v2 Emulation Circuitry and Isolation Circuitry is Denoted by :A | 5 |

| 3 | PGA With S7 Open (Output Filter Usable)                               | 6 |

| 4 | PGA With S7 Closed (Output Filter Not Usable)                         | 6 |

| 5 | Key Components on the controlCARD                                     | 8 |

#### List of Tables

| 1 | F280049 controlCARD Part Numbers | 3  |

|---|----------------------------------|----|

| 2 | Getting Started Reference        | 4  |

| 3 | Hardware References              | 9  |

| 4 | Boot Mode Switch (S1) Positions  | 11 |

|   |                                  |    |

#### 1 Introduction

The Piccolo F280049 controlCARD from Texas Instruments (TI) provides a great way to learn and experiment with the F28004x device family within TI's C2000 family of microcontrollers (MCUs). This controlCARD uses the 120HSEC connector (compatible with the TMDSHSECDOCK docking station) and is intended to provide a well-filtered robust design capable of working in most environments. This document describes the hardware details of the F280049 controlCARD and explains the functions, locations of jumpers, and connectors present on the board.

The Hardware Developer's Kit, which is a full set of files necessary to evaluate and develop with the F280049 device, can be found in C2000Ware and includes:

- Schematics designed in Altium

- Bill of materials (BOM)

- Layout PCB files designed in Altium

- Gerber files

**NOTE:** This kit is designed to explore the functionality of the F28004x microcontroller family. The controlCARD can be treated as a good reference design, but it is not intended to be a complete customer design. Full compliance to safety, EMI/EMC, and other regulations are left to the designer of the final customer system.

2

This controlCARD can be obtained by ordering one of the products from Table 1.

| Part Number     | Status       | Description                                           |

|-----------------|--------------|-------------------------------------------------------|

| TMDXDOCK280049M | Experimental | XF280049M controlCARD and HSEC docking station bundle |

| TMDSDOCK280049C | Qualified    | F280049C controlCARD and HSEC docking station bundle  |

| TMDSCNCD280049C | Qualified    | F280049C controlCARD                                  |

### Table 1. F280049 controlCARD Part Numbers

# 2 Errata

Current revision of controlCARD as of June, 2018: PCB rev - B, ASSY rev - none.

# 2.1 Warnings, Notes, and Errata

Notes for all controlCARDs:

- The docking station is capable of drawing power through the included USB cable. However, when

external components are added to the docking station for experimentation, the system may require

more power than a standard USB port can provide (5-V and 500-mA). This is especially true when

additional circuitry has been added to the docking station. In such cases, an external 5-VDC power

supply (2.5-mm inner diameter × 5.5-mm outer diameter) plugged into J1 is recommended. A

compatible supply could be the: Phihong PSAC05R-050(P)-R-C2 + Phihong RPBAG.

- The F28004x by default expects GPIO24 and GPIO32 to be the input pins responsible for determining the device boot mode at power up; the external pull directions for GPIO24 and GPIO32 are configured with S1 (see Table 4). If desired, the GPIO pins used for boot mode selection can be modified by programming the OTP in the device. Refer to the Boot ROM section of the specific device's Technical Reference Manual (TRM) for more information.

- The controlCARD included with TMDXDOCK280049M uses prototype silicon XF280049M. XF280049M is a prototype variant only, and is not offered in production. It has the same functionality and configuration as the qualified variant F280049C.

# **3** Getting Familiar With the controlCARD

### 3.1 F280049 controlCARD Features

- **Piccolo F280049 Microcontroller** High performance C2000 microcontroller on the controlCARD.

- 120pin HSEC8 Edge Card Interface Allows for compatibility with all of C2000's 120- or 180-pin controlCARD-based application kits and TMDSHSECDOCK. Compatibility with 100-pin DIMM controlCARDs can be accomplished using the TMDSADAP180TO100 adapter card (sold separately).

- Built-in Isolated JTAG Emulation An XDS100v2 emulator provides a convenient interface to Code Composer Studio without additional hardware. Flipping a switch allows an external JTAG emulator to be used. This external emulator may use standard 4-pin JTAG or 2-pin cJTAG.

- Key Signal Breakout Most GPIO, ADC, and other key signals routed to hard gold connector fingers.

- **Robust Power Supply Filtering** Single 5-VDC supply provides power to onboard 3.3-V LDO. All MCU inputs are then decoupled using LC filters near the device.

- ADC Clamping ADC inputs are clamped by protection diodes.

- Anti-Aliasing Filters Noise filters (small RC filters) can be easily added on several ADC input pins.

# 3.2 F28004x Device Description

For a complete description of the F28004x devices, see Section 1.3 of the *TMS320F28004x Piccolo™ Microcontrollers* data sheet (SPRS945).

Errata

#### 3.3 Assumed Operating Conditions

This kit is assumed to run at standard room conditions. The EVM should run at approximately Standard Ambient Temperature and Pressure (SATP) with moderate-to-low humidity.

### 3.4 Using the controlCARD

For the controlCARD to work, the controlCARD MCU must be powered. This is usually done by inputting 5-VDC through the HSEC connector through an accompanying baseboard. For example, if using a docking station baseboard, 5-VDC should be input into the docking station's J1 or J17, then SW1 must be toggled to the appropriate position.

Based on the way that the controlCARD is used, additional hardware settings may be necessary, as shown in Table 2.

| Component                                                              | Debug Using CCS and the<br>on-card XDS100v2 Emulator                                                                                                       | Debug Using CCS and an<br>External Emulator Through<br>the Baseboard                                                                                  | Standalone (Boot From<br>FLASH or Other Boot Mode)           |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| S1:A (controlCARD)                                                     | Left (Switch 1): Up (ON)                                                                                                                                   | Left (Switch 1): Down (OFF)                                                                                                                           | Left (Switch 1): Down (OFF)                                  |

| J1:A (controlCARD)                                                     | Connect a mini USB cable<br>between J1:A and the<br>computer.<br>In CCS, use this target<br>configuration:<br>F280049 device with an<br>XDS100v2 emulator. | _                                                                                                                                                     | _                                                            |

| S1 (controlCARD)                                                       | Left (Switch 2): Down (ON)<br>Right (Switch 1): Up (OFF)<br>Putting the C2000 device into<br>Wait Mode can reduce the risk<br>of connectivity issues.      | Left (Switch 2): Down (ON)<br>Right (Switch 1): Up (OFF)<br>Putting the C2000 device into<br>Wait Mode can reduce the risk<br>of connectivity issues. | Set S1 as desired<br>(See Table 4 for supported<br>settings) |

| Baseboard's JTAG connector<br>(J2 on the Docking Station<br>baseboard) | _                                                                                                                                                          | Connect an external emulator<br>and appropriately configure the<br>CCS target configuration.                                                          | _                                                            |

# Table 2. Getting Started Reference

The F280049 controlCARD to docking station signal mapping can be found in the C2000Ware controlCARD product directory at \ti\c2000\C2000Ware\_XXXX\boards\controlCARDs:

- TMDSCNCD28004x\_RevA\_120cCARD\_pinout.pdf -- F280049 signal mapping on the default HSEC docking station

- TMDSCNCD28004x\_RevA\_100DIM\_map.pdf -- F280049 signal mapping on the legacy DIM100 docking station if using TMDSADAP180TO100 adapter card

Hardware support files for the F280049 controlCARD and docking station can also be found in the C2000Ware product directories:

- F280049 controlCARD: \ti\c2000\C2000Ware\_XXXX\boards\controlCARDs

- Docking station: \ti\c2000\C2000Ware\_XXXX\boards\ExperimenterKits

### 3.5 Software Development

4

Code Composer Studio (CCS) is the recommended integrated development environment (IDE) for developing and debugging software for the C2000 series of MCUs. CCS is free to download and use with the controlCARD. Introductory videos for CCS are available at training.ti.com.

#### NOTE: For users of TMDXDOCK280049M

TMS320F280049M is a discontinued part number that is not supported on new installations of CCS. Use the functionally equivalent TMS320F280049C part number when creating a new target configuration for TMDXDOCK280049M on new installations of CCS.

C2000Ware contains a full suite of example software designed to work with the F280049 controlCARD. This software package includes many example projects which allow the user to experiment with the ADC, PWM, and other C2000 peripherals.

Support files for both register-level and driver-level programming are included with C2000Ware:

- Register programming examples are located at: \ti\c2000\C2000Ware\_XXXX\device\_support\f28004x\examples

- Driverlib programming examples are located at: \ti\c2000\C2000Ware\_XXXX\driverlib\f28004x\examples

## 4 Special Notes

# 4.1 XDS100v2 Emulator and SCI/UART Connectivity

The F280049 controlCARD provides on-board emulation and USB-to-UART adapter functionality. This allows for a convenient method to debug and demo the F280049 MCU.

The FTDI chip, its support circuitry, and associated isolation components are placed in Macro A, the left section of the controlCARD. Each of these components contains an additional A within the component reference designator (that is R2:A for resistor 2 in Macro A).

Each F280049 controlCARD's XDS100v2 is programmed with a fixed serial number. If a debug session must involve two or more F280049 controlCARDs, each controlCARDs must have a unique serial number, and some must be reprogrammed. See:

http://processors.wiki.ti.com/index.php/XDS100#Q:\_Can\_I\_change\_the\_serial\_number\_on\_my\_XDS100v2 .3F.

The configuration of the switches on S1:A (shown in Figure 2) determine whether the onboard emulator is active, whether an external emulator can be used, or whether the device will boot from FLASH/peripherals.

# Figure 2. XDS100v2 Emulation Circuitry and Isolation Circuitry is Denoted by :A

# 4.2 cJTAG Usage

The F280049 MCU supports the cJTAG 2-pin debugging interface, but the onboard XDS100v2 emulator does not. To experiment with cJTAG, an external emulator must be connected through the baseboard. To enable cJTAG:

- 1. Connect an external emulator to the controlCARD's baseboard.

- 2. Change S4 to the cJTAG position (switch flipped up).

- If cJTAG is used, the F280049 MCU will have two additional GPIOs which can be used by the application. Configure S2 and S3, as desired, to control which controlCARD fingers or pins the newly available GPIOs are connected to.

#### Special Notes

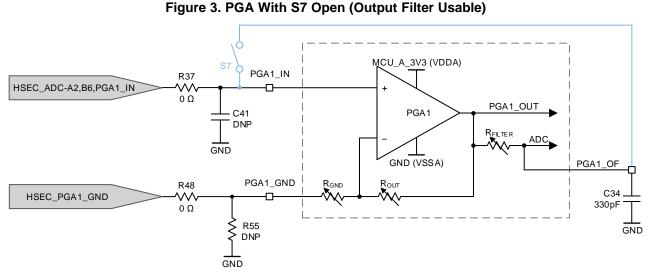

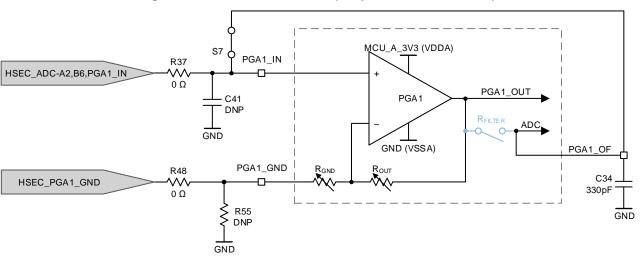

# 4.3 Evaluation of the Programmable Gain Amplifier (PGA)

When evaluating the PGA, the PGA\_GND pin must be driven to the ground reference of the PGA\_IN signal. The PGA\_GND signal may be provided using differential signaling through the HSEC fingers for improved noise immunity, or the PGA\_GND pin may be tied to the GND reference of the controlCARD through a  $0-\Omega$  resistor (R55 in Figure 3) for simplicity.

The S7 switch bank provides the flexibility to either use the PGA output filter pin (PGAn\_OF) for filtering (S7 open in Figure 3) or for sampling the PGA input voltage directly by bypassing the internal PGA (S7 closed in Figure 4).

#### Figure 4. PGA With S7 Closed (Output Filter Not Usable)

- **NOTE:** The S7 closed implementation for PGA6 is different from the other PGAs. Instead of shorting PGA6\_OF and PGA6\_IN, the PGA6\_OF signal may be accessed from the HSEC connector independently of the PGA6\_IN signal.

- **NOTE:** The PGA R<sub>FILTER</sub> resistor should never be enabled while the S7 switch is closed. Prolonged exposure to contention between the PGA\_IN and PGA\_OF pins may result in permanent damage to the internal R<sub>FILTER</sub> resistor.

6

# 4.4 Evaluation of the Internal DC/DC Converter

The controlCARD, by default, assumes the F280049 internal VREG will be used to generate the 1.2-V power supply required by the MCU. The controlCARD enables the user to use the internal DC/DC converter capabilities, with some soldering.

To enable the internal DC/DC converter:

- R18 and R19 must be unpopulated.

- R21 and R22 must be populated with a  $0-\Omega$  resistor.

- C19 must be populated with a 2.2-µF X5R/X7R capacitor.

- C20 and C21 must each be populated with a 10-µF X5R/X7R capacitor.

Functionally, the F280049 powers up the 1.2-V power rail using the internal VREG, then requires software to change from the VREG to the DC/DC. See the F28004x Technical Reference Manual for more details.

7

Hardware References

#### www.ti.com

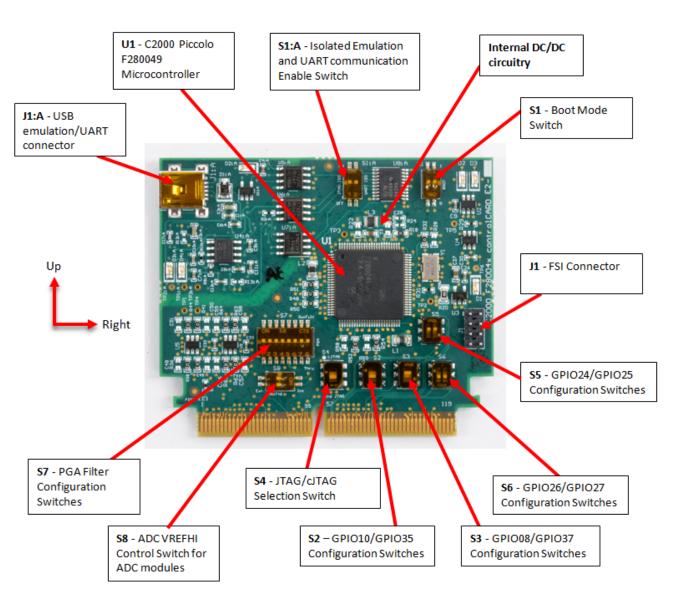

# 5 Hardware References

Table 3 shows the various connections available on the board. Figure 5 illustrates the location of many of these components on the board.

### Figure 5. Key Components on the controlCARD

#### **Table 3. Hardware References**

| Connectors                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1:A                                              | Emulation/UART connector - USB mini A connector used to provide XDS100v2 emulation and USB-to-UART(SCI) communication through FTDI logic. S1:A determines which connections are enabled to the MCU.                                                                                                                                                                                                                                                                                                                             |

| Jumpers                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J1<br>LEDs                                        | FSI Connector - Gives an ability to connect FSI signals from the F280049 to another board.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D1                                                | Controlled by GPIO-31 with negative logic (red)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D2                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                   | Controlled by GPIO-34 with negative logic (red)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D3                                                | Turns on when the controlCARD is powered ON (green)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D2:A                                              | Turns on when ISO JTAG logic is powered on (green)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D3:A                                              | JTAG/UART RX toggle indicator (blue)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D4:A                                              | JTAG/UART TX toggle indicator (blue)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Resistors and Capacitors (default sett            | ing in BOLD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R18, R19, R21, R22                                | GPIO22/23 configuration resistors<br>These resistors allow the user to choose whether GPIO22/23 is used as GPIO (and go to the<br>baseboard) or whether they will be used in conjunction with the F280049 MCU's internal DC/DC<br>capability:                                                                                                                                                                                                                                                                                   |

|                                                   | <ul> <li>R18,R19 populated with 0-Ω resistors and R21,R22 unpopulated – GPIO22 and<br/>GPIO23 are used as GPIO and go to the baseboard through EC1. The internal DC/DC<br/>cannot be used.</li> </ul>                                                                                                                                                                                                                                                                                                                           |

|                                                   | <ul> <li>R18,R19 unpopulated and R21,R22 populated with 0-Ω resistors – Internal DC/DC can be<br/>used to generate the 1.2-V VDD power rail. GPIO22 and GPIO23 are used as VFBSW and<br/>VSW, respectively. The internal DC/DC can be used.</li> </ul>                                                                                                                                                                                                                                                                          |

| C19, C20, C21                                     | These capacitors should be populated when the F280049's internal DC/DC capability is used. C19 should be populated with a 2.2- $\mu$ F capacitor. C20 and C21 should each be populated with a 10- $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                            |

| R24, C28                                          | R24 and C28 create an optional snubber circuit, which can be used if the DC/DC is used.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| R36-R47,R49,R53, R60-R64, C41-C47,<br>and C48-C59 | Optional RC input filter for all ADC/PGA inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C34-C40                                           | PGA filter capacitor when PGA filtering is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R55-R59                                           | PGA-GND configuration resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R48,R50-R52,R54                                   | These resistors control whether the negative input (PGAGND) for each PGA are grounded locally or whether they should be grounded through pins on the HSEC connector (for use in Kelvin grounding).<br>By default, <b>resistors R55-R59 are not populated and R48, R50-R52, R54 are populated</b> .<br>Because of this, all the PGAs are, by default, expected to be referenced to ground by the baseboard. If, for example, R55 was populated and R48 was unpopulated, then PGA1's PGAGND would be grounded on the controlCARD. |

| Switches (default position in BOLD)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| S1<br>(Installed with 180 degree rotation)        | Boot Mode Selection Switch<br>See Table 4 for a list of selectable boot modes. See the device datasheet and TRM for more<br>information about device boot behavior.<br>Left (Switch 2) – GPIO24 Configuration Switch:                                                                                                                                                                                                                                                                                                           |

|                                                   | <ul> <li>In the up position – GPIO24 is pulled high</li> <li>In the down position – GPIO24 is pulled low<br/>Right (Switch 1) – GPIO32 Configuration Switch:</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

|                                                   | <ul> <li>In the up position – GPIO32 is pulled high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                   | <ul> <li>In the down position – GPIO32 is pulled low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| S2                                                | GPIO10/GPIO35 Configuration Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   | <ul> <li>In the up position – GPIO10 goes to pin 60 of the HSEC connector. If S4's switch 1 is in the up position, GPIO35 goes to pin 85 of the HSEC connector.</li> <li>In the down position – GPIO10 goes to pin 85 of the HSEC connector. If S4's switch 1 is</li> </ul>                                                                                                                                                                                                                                                     |

|                                                   | in the up position, GPIO35 goes to pin 60 of the HSEC connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | Table 3. Hardware References (continued)                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S3<br>(Installed with 180 degree rotation) | <ul> <li>GPIO08/GPIO37 Configuration Switches</li> <li>In the up position – GPIO08 goes to pin 87 of the HSEC connector. If S4's switch 2 is in the up position, GPIO37 goes to pin 58 of the HSEC connector.</li> <li>In the down position – GPIO08 goes to pin 58 of the HSEC connector. If S4's switch 2 is in the up position, GPIO37 goes to pin 87 of the HSEC connector.</li> </ul>                                                 |

| S4                                         | JTAG/cJTAG Selection Switch                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | <ul> <li>In the up position – 2-pin cJTAG mode is expected to be used. GPIO35 and GPIO37 go to<br/>the baseboard based on the settings of S2 and S3, respectively.</li> </ul>                                                                                                                                                                                                                                                              |

|                                            | <ul> <li>In the down position – 4-pin standard JTAG is expected to be used. GPIO35 and GPIO37<br/>are used to support JTAG functionality. The on-card XDS100v2 emulator requires 4-pin<br/>JTAG to be used.</li> </ul>                                                                                                                                                                                                                     |

| S5<br>(Installed with 180 degree rotation) | GPIO24/GPIO25 Configuration Switches<br>Left (Switch 2) – GPIO25 Configuration Switch:                                                                                                                                                                                                                                                                                                                                                     |

|                                            | • In the up position – GPIO25 goes to pin 77 of the HSEC connector.                                                                                                                                                                                                                                                                                                                                                                        |

|                                            | <ul> <li>In the down position – GPIO25 goes to pin 102 of the HSEC connector.</li> <li>Right (Switch 1) – GPIO24 Configuration Switch:</li> </ul>                                                                                                                                                                                                                                                                                          |

|                                            | • In the up position – GPIO24 goes to pin 75 of the HSEC connector.                                                                                                                                                                                                                                                                                                                                                                        |

|                                            | <ul> <li>In the down position – GPIO24 goes to pin 100 of the HSEC connector.</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

| S6                                         | GPIO26/GPIO27 Configuration Switches<br>Left (Switch 1) – GPIO26 Configuration Switch:                                                                                                                                                                                                                                                                                                                                                     |

|                                            | <ul> <li>In the up position – GPIO26 goes to pin 107 of the HSEC connector.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

|                                            | <ul> <li>In the down position – GPIO26 goes to pin 79 of the HSEC connector.</li> <li>Right (Switch 2) – GPIO27 Configuration Switch:</li> </ul>                                                                                                                                                                                                                                                                                           |

|                                            | <ul> <li>In the up position – GPIO27 goes to pin 109 of the HSEC connector.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

|                                            | <ul> <li>In the down position – GPIO27 goes to pin 81 of the HSEC connector.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |

| S7                                         | PGA Filter Configuration Switches<br>From the left, the switches control whether PGA1-PGA7's outputs, respectively, are filtered. The<br>eighth switch of S7 is not used.<br>Each switch:                                                                                                                                                                                                                                                  |

|                                            | <ul> <li>In the up position – an HSEC pin is connected to the respective PGA+ input pin, and is<br/>now also tied to an additional ADC input pin. In software, PGA output filtering, for the<br/>respective PGA, functionality should NOT be used.</li> </ul>                                                                                                                                                                              |

|                                            | <ul> <li>In the down position – an HSEC pin only goes to the PGA+ input pin. PGA output filtering, for the respective PGA, may be used.</li> <li>The up position for S7's switch 6 (PGA6) is implemented differently from the other PGAs.</li> <li>PGA6_OF may be accessed through the HSEC connector independently of PGA6_IN, whereas the other PGAs will have their respective PGAn_OF and PGAn_IN signals shorted together.</li> </ul> |

| S8<br>(Installed with 90 degree rotation)  | ADC VREFHI Control Switch for ADC modules<br>Top (Switch 1) – VREFHI Control Switch for ADC module A:                                                                                                                                                                                                                                                                                                                                      |

|                                            | • In the left position – ADC-A should be configured to use the internal voltage reference.                                                                                                                                                                                                                                                                                                                                                 |

|                                            | <ul> <li>In the right position – ADC-A is configured to use an external voltage reference, which<br/>should be connected to pin 45 of the HSEC connector.</li> <li>Bottom (Switch 2) – VREFHI Control Switch for ADC module B and module C:</li> </ul>                                                                                                                                                                                     |

|                                            | <ul> <li>In the left position – ADC-B and ADC-C should be configured to use the internal voltage reference.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

|                                            | <ul> <li>In the right position – ADC-B and ADC-C are configured to use an external voltage<br/>reference, which should be connected to pin 45 of the HSEC connector.</li> </ul>                                                                                                                                                                                                                                                            |

| S1:A                                       | Isolated emulation and UART communication enable switches<br>Left (Switch 1) – JTAG Enable:                                                                                                                                                                                                                                                                                                                                                |

|                                            | <ul> <li>Up (on) – All signals between the XDS100v2 emulation logic and the MCU are connected.<br/>This setting is valid when the MCU is being debugged or programmed through the on-card<br/>XDS100v2 emulator.</li> </ul>                                                                                                                                                                                                                |

|                                            | <ul> <li>Down (off) – The XDS100v2 emulation logic will NOT be connected to the MCU. This<br/>setting is valid when the device boots from FLASH, boots from a peripheral directly, or when<br/>an external JTAG emulator is used.</li> </ul>                                                                                                                                                                                               |

|                                            | <ul> <li>Right (Switch 2) – ISO UART communication enable:</li> <li>Up (on) – The C2000 MCU's GPIO-28 (and pin76 of the 180pin controlCARD connector) are coupled to the FTDI's USB-to-Serial adapter. This allows UART communication to a computer through the FTDI chip. However, in this position, GPIO-28 is forced high by the FTDI chip. Functionality of pin76 on the connector is limited.</li> </ul>                              |

|                                            | <ul> <li>Down (off) – The C2000 MCU will NOT be connected to the FTDI USB-to-Serial adapter.<br/>Pin76 of the 180pin controlCARD connector is directly connected to GPIO-28.</li> </ul>                                                                                                                                                                                                                                                    |

Table 3. Hardware References (continued)

#### Hardware References

#### Table 4. Boot Mode Switch (S1) Positions

| Mode # | GPIO-24 (Left, Switch 2) | GPIO-32 (Right, Switch 1) | Boot from                 |

|--------|--------------------------|---------------------------|---------------------------|

| 00     | 0 (Down)                 | 0 (Down)                  | Parallel I/O              |

| 01     | 0 (Down)                 | 1 (Up)                    | Boot from SCI / Wait Mode |

| 02     | 1 (Up)                   | 0 (Down)                  | Boot from CAN             |

| 03     | 1 (Up)                   | 1 (Up)                    | Boot from FLASH           |

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from A Revision (December 2017) to B Revision

# Page

| _ |                                                                           |    |

|---|---------------------------------------------------------------------------|----|

| • | Updated F280049C references to F280049.                                   | 1  |

| • | Updated F280049 controlCARDs Part Numbers.                                | 3  |

| • | Added CCS target configuration note for TMDXDOCK280049M.                  | 4  |

| • | Added Evaluation of the Programmable Gain Amplifier (PGA) section.        | 6  |

| • | Clarified S1 orientation in Hardware References table.                    | 9  |

| • | Added boot switch information                                             | 9  |

| • | Clarified S3 orientation in Hardware References table.                    | 10 |

| • | Clarified S5 orientation in Hardware References table.                    | 10 |

| • | Clarified S8 orientation in Hardware References table.                    | 10 |

| • | Clarified S1:A switches in Hardware References table.                     | 10 |

| • | Clarified boot switch positions in Boot Mode Switch (S1) Positions table. | 11 |

|   |                                                                           |    |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated