# **USRP-TB B210 Datasheet**

# Overview

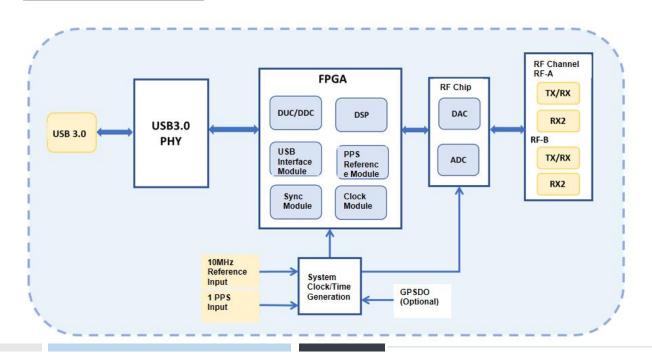

The USRP-TB B210 is a highly integrated, industrial-grade universal software-defined radio platform supporting dual-channel transceiver operation. Featuring high-speed USB 3.0 interface, it accommodates multiple frameworks through the open-source USRP Hardware Driver (UHD). The device offers three programmable FPGA options: Spartan 6 XC6SLX150 FPGA, Xilinx Artix 7 100T FPGA, and Xilinx Artix 7 200T FPGA, catering to diverse logic resource requirements. With its AD9361 RF front-end, the platform delivers up to 56MHz instantaneous bandwidth. Its compact form factor ensures portability for both laboratory and field deployment scenarios.

# Block Diagram

sdrfamily.com Email: sales@sdrfamily.com

# Features

Dual-channel transceiver with RF coverage from 70MHz to 6GHz

Maximum 56MHz real-time bandwidth

Features dual signal chains based on AD9361 for coherent MIMO capability

Supports high-speed USB 3.0 connectivity

Open-source UHD supports multiple frameworks

# Specification

| тх                                                     |                  | RX                                          |                                      |

|--------------------------------------------------------|------------------|---------------------------------------------|--------------------------------------|

| Channel Count                                          | 2                | Channel Count                               | 2                                    |

| Frequency Range                                        | 70 MHz - 6 GHz   | Frequency Range                             | 70 MHz - 6 GHz                       |

| LO (Local<br>Oscillator) Accuracy                      | ± 2.0 ppm        | Noise Figure                                | <8.5dB                               |

| Maximum Output<br>Power                                | 16 dBm           | Maximum Input<br>Power                      | -15 dBm                              |

| Maximum Real-<br>Time Bandwidth                        | 56 MHz           | Maximum Real-Time<br>Bandwidth              | 56 MHz                               |

| Phase Noise<br>@10kHz Offset                           | 1GHz: -102dBc/Hz | Input Third-Order<br>Intercept Point (IIP3) | -20dBm                               |

|                                                        | 5GHz: -91dBc/Hz  | Input/Output                                |                                      |

| Conversion Module                                      |                  | DC Input Voltage                            | 6 V                                  |

| ADC Maximum Sampling<br>Rate                           | 61.44 MSps       | Power<br>Consumption                        | 8 W                                  |

| ADC Resolution                                         | 12 bits          | Physical Characteristics                    |                                      |

| ADC Wideband Spurious-<br>Free Dynamic Range<br>(SFDR) | 78dBc            | Size and Weight                             | Size: 0.7kg<br>Weight: 17.5*10*1.7cm |

| DAC Sampling Rate                                      | 61.44 MSps       | GOSDO                                       |                                      |

| DAC Resolution                                         | 12 bits          | TCXO Accuracy (GPS<br>Unlocked)             | ±75ppb                               |

| Maximum Host Transfer                                  | 61.44 MSps       | TCXO Accuracy (GPS                          | <1ppb                                |

sdrfamily.com Email: sales@sdrfamily.com

## **Key Functions**

### Wide Frequency Range & High Bandwidth

- frequency range from 70MHz to 6GHz

- Up to 56MHz instantaneous bandwidth with maximum sampling rate of 61.44MSps per channel

### High-Speed Data Transfer

- Enables high-speed data transmission via USB 3.0 host interface

- Supports bidirectional streaming up to 61.44 MSps (16-bit samples)

### **Synchronization & Clocking**

- Integrated high-stability TCXO with:10 MHz external reference clock input and PPS synchronization

- Multi-device synchronization via shared clock/trigger signals

### **Programmable FPGA**

- Multiple FPGA Options: Spartan 6 FPGA, Xilinx Artix 7 100T FPGA, and Xilinx Artix 7 200T FPGA

- Users can develop custom FPGA logic through the programmable FPGA

### **MIMO Capability**

- Features 2 transmit + 2 receive channels for full-duplex communication and 2x2 MIMO systems

- Scalable for larger MIMO arrays through synchronized multi-device connectivity

### **Open Ecosystem & Compatibility**

- Universal Hardware Driver (UHD) supported

- Cross-platform development withGNU Radio, LabVIEW, MATLAB, other open-source SDR toolchains

# Compatible Platforms

# **Applications**

#### **Wireless Communication Research**

- Physical layer development & testing for 5G/6G, Wi-Fi, LTE protocols

- 2x2 MIMO system experiments (e.g. beamforming)

#### **Portable Field Applications**

- On-site spectrum monitoring & interference detection

- Mobile comms testing (drone communications, IoT nodes)

#### **IoT & Sensor Networks**

- Custom wireless protocol development (LoRa/ZigBee)

- Low-power communication system experiments

#### **Education & Labs**

- University communication engineering courses

- Open-source projects (GNU Radio signal processing workflows)

sdrfamily.com Email: sales@sdrfamily.com