## **AEDR-9920**

# 3-Channel Reflective Incremental Encoders Programmable Interpolator Digital Output (225 LPI)

## **Description**

The Broadcom<sup>®</sup> AEDR-9920 is a three-channel reflective optical encoder. The selectable and programmable options available are three-channel digital differential A, B, and I outputs.

The AEDR-9920 digital encoder mode offers two-channel (AB) quadrature digital outputs and a third channel digital index output. Being TTL compatible, the outputs of the AEDR-9920 encoder can be interfaced with most of the signal processing circuitries. Therefore, the encoder provides easy integration and flexible design-in into existing systems.

The AEDR-9920 encoder is designed to operate over –40°C to 115°C temperature range and is suitable for commercial, industrial, and automotive end applications.

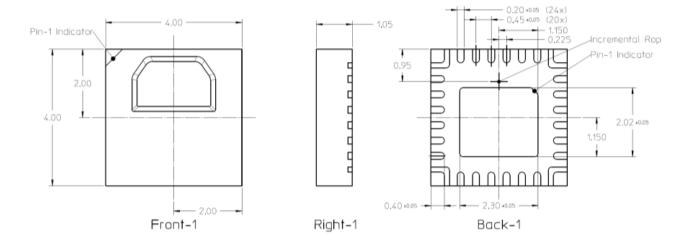

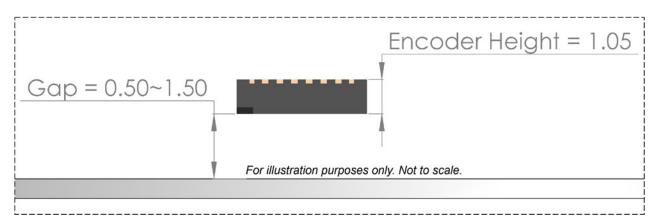

The encoder houses an LED light source and a photo-detecting circuitry in a single package. The small size of 4.00 mm (L) × 4.00 mm (W) × 1.05 mm (H) allows it to be used in a wide range of miniature commercial applications, where size and space are primary concerns.

#### **Features**

- Digital output option: 3-channel differential or TTL compatible; 2-channel quadrature (AB) digital outputs for direction sensing and a third channel, index digital output

- Built-in pin-selectable interpolator for 1x, 2x, 4x, 8x, 16x, 32x, 64x, 128x, and 256x interpolation

- SPI programmable interpolator from 1x to 512x

- Surface mount leadless package: 4.0 mm (L) × 4.0 mm

(W) × 1.05 mm (H)

- Operating voltage of 3.3V and 5.0V supply

- Built-in LED current regulation

- Wide operating temperature range from –40°C to 115°C

- High encoding resolution: 225 LPI (lines/inch) or 8.86 LPmm (lines/mm)

# **Applications**

- Closed-loop stepper motors

- Small motors, actuators

- Industrial printers

- Robotics

- Card readers

- Pan-tilt-zoom (PTZ) camera

- Portable medical equipment

- Optometric equipment

- Linear stages

**Disclaimer:** Except as expressly indicated in writing, the component is not designed or warranted to be suitable for use in safety-related applications where its failure or malfunction can reasonably be expected to result in injury, death, or severe equipment damage.

Broadcom AEDR-9920-DS103

January 12, 2022

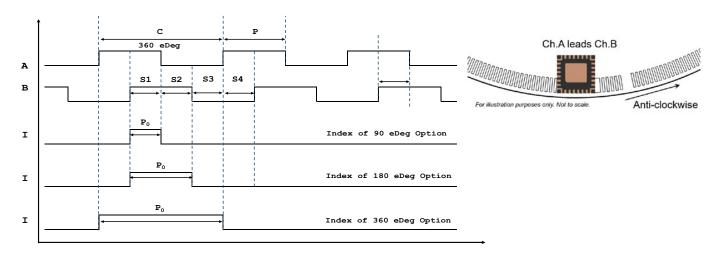

# **Output Waveform**

Figure 1: Output Waveform

## **Test Parameter Definitions**

| Test                     | Parameter       | Definition                                                                                                                                                                                     |

|--------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count                    | N               | The number of bar and window pairs or counts per revolution (CPR) of the code wheel.                                                                                                           |

| Cycle                    | С               | 360 electrical degrees (°e), 1 bar and window pair.                                                                                                                                            |

|                          |                 | One Shaft Rotation: 360 mechanical degrees, N cycles.                                                                                                                                          |

| Cycle Error              | ΔC              | An indication of cycle uniformity. The difference between an observed shaft angle that gives rise to one electrical cycle, and the nominal angular increment of 1/N of a revolution.           |

| Pulse Width (Duty) Error | ΔΡ              | The deviation, in electrical degrees, of the pulse width from its ideal value of 180°e.                                                                                                        |

| State                    | S               | The number of electrical degrees between a transition in the output of channel A and the neighboring transition in the output of channel B. There are 4 states per cycle, each nominally 90°e. |

| Phase                    | φ               | The number of electrical degrees between the center of the high state of channel A and the center of the high state of channel B. This value is nominally 90°e for quadrature output.          |

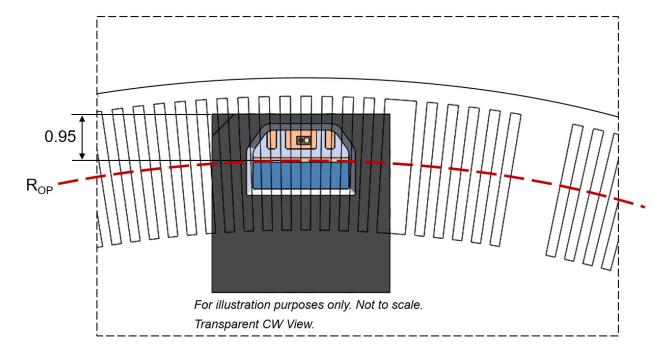

| Optical Radius           | R <sub>OP</sub> | The distance from the code wheel's center of rotation to the optical center (O.C.) of the encoder module.                                                                                      |

| Index Pulse Width        | P <sub>0</sub>  | The number of electrical degrees that an index is high in one cycle.                                                                                                                           |

# **Absolute Maximum Ratings**

| Parameter             | Symbol          | Value          |

|-----------------------|-----------------|----------------|

| Storage Temperature   | T <sub>S</sub>  | –40°C to 125°C |

| Operating Temperature | T <sub>A</sub>  | –40°C to 115°C |

| Supply Voltage        | V <sub>CC</sub> | 7V             |

#### NOTE:

- 1. Proper operation of the encoder cannot be guaranteed if the maximum ratings are exceeded.

- 2. Remove kapton tape only after SMT reflow process and just before final assembly. Take precautions to keep the encoder ASIC clean at all times.

- 3. Some particles might be present on the surface of the encoder ASIC surface. The presence of these particles does not degrade the performance of the encoder.

**CAUTION!** Take anti-static discharge precautions when handling the encoder in order to avoid damage, degradation, or both, induced by ESD.

# **Recommended Operating Condition**

| Parameter                               | Sym.            | Min. | Тур. | Max.  | Unit | Notes                 |

|-----------------------------------------|-----------------|------|------|-------|------|-----------------------|

| Operating Temperature                   | T <sub>A</sub>  | -40  | 25   | 115   | °C   |                       |

| Supply Voltage                          | V <sub>CC</sub> | 3.0  | 3.3  | 3.6   | V    | Ripple < 100 mVp-p    |

|                                         |                 | 4.5  | 5    | 5.5   |      |                       |

| Current                                 | I <sub>CC</sub> | _    | 48   | 85    | mA   | No load               |

| Pin Current (All I/O Outputs)           | I               | -20  | _    | 20    | mA   |                       |

| Max Output Frequency                    | F               | _    | _    | 0.2   | MHz  | At 1x Interpolation   |

| (External Pin Selectable)               |                 | _    | _    | 0.4   | MHz  | At 2x Interpolation   |

|                                         |                 | _    | _    | 0.8   | MHz  | At 4x Interpolation   |

|                                         |                 | _    | _    | 1.6   | MHz  | At 8x Interpolation   |

|                                         |                 | _    | _    | 2.0   | MHz  | At 16x Interpolation  |

|                                         |                 | _    | _    | 2.0   | MHz  | At 32x Interpolation  |

|                                         |                 | _    | _    | 2.0   | MHz  | At 64x Interpolation  |

|                                         |                 | _    | _    | 2.0   | MHz  | At 128x Interpolation |

|                                         |                 | _    | _    | 2.0   | MHz  | At 256x Interpolation |

| Max Output Frequency (SPI Programmable) | F               | _    | _    | 2.0   | MHz  | At >16x Interpolation |

| Radial Misalignment                     | ER              | _    | _    | ± 0.5 | mm   |                       |

| Tangential Misalignment                 | ET              | _    | _    | ± 0.5 | mm   |                       |

| Code Wheel Gap                          | G               | 0.5  | 1.00 | 1.5   | mm   |                       |

# **Power-Up Behavior**

When AEDR-9920 is powered on, the A+,A–,B+, and B– digital outputs will be low and I+ and I– will be high until the encoder is ready.

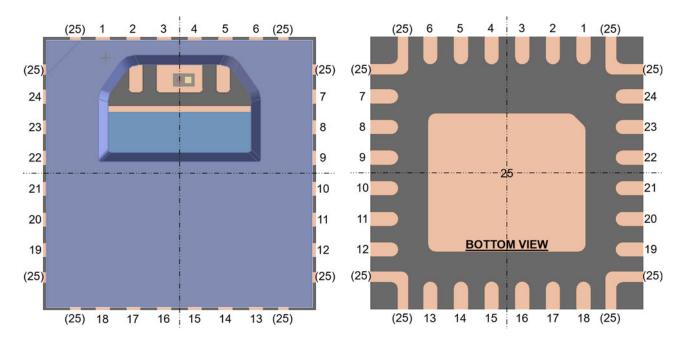

# **Encoder Pinout**

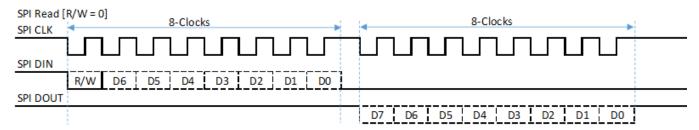

Figure 2: Encoder Pinout

| Pin | Name <sup>a</sup> | Function         |

|-----|-------------------|------------------|

| 1   | N.C.              | _                |

| 2   | N.C.              | _                |

| 3   | LED ANODE         | LED Anode        |

| 4   | LED ANODE         | LED Anode        |

| 5   | LED CATHODE       | LED Cathode      |

| 6   | N.C.              | _                |

| 7   | LED REG           | LED Regulation   |

| 8   | VDDA <sup>b</sup> | Supply Voltage   |

| 9   | VSSA <sup>c</sup> | Ground           |

| 10  | SEL2              | Mode Selection 2 |

| 11  | SEL1              | Mode Selection 1 |

| 12  | CH_I-             | Digital I-       |

| 13  | N.C.              | _                |

| Pin               | Name              | Function              |  |  |

|-------------------|-------------------|-----------------------|--|--|

| 14                | CH_I+ / SPI_DOUT  | Digital I+ / SPI Dout |  |  |

| 15                | N.C.              | _                     |  |  |

| 16                | N.C.              | _                     |  |  |

| 17                | INDEX_SEL         | Index Selection       |  |  |

| 18                | N.C.              | _                     |  |  |

| 19                | CH_B-/SPI_CLK     | Digital B–/SPI Clk    |  |  |

| 20                | CH_B+             | Digital B+            |  |  |

| 21                | CH_A-/SPI_DIN     | Digital A-/SPI Din    |  |  |

| 22                | CH_A+             | Digital A+            |  |  |

| 23                | VSSD <sup>c</sup> | Ground                |  |  |

| 24                | VDD <sup>b</sup>  | Supply Voltage        |  |  |

| 25                | VSSA <sup>c</sup> | Ground                |  |  |

| (25) <sup>d</sup> | N.C.              | _                     |  |  |

- a. N.C. = No connect.

- b. VDD and VDDA can be connected to the same voltage supply.

- c. VSSA and VSSD *must* be connected together.

- d. No connection to all corner pads indicated as (25).

AEDR-9920-DS103 Broadcom

# **Select Options – Encoder Built-in Interpolation**

| SEL 1             | SEL 2 | IND SEL | Interpolation<br>Factor  | Index                        | Max Output<br>Frequency | CPR at R <sub>OP</sub><br>4.6 mm | CPR at R <sub>OP</sub><br>11.23 mm |

|-------------------|-------|---------|--------------------------|------------------------------|-------------------------|----------------------------------|------------------------------------|

| Open <sup>a</sup> | Open  | Low     | 1X                       | Gated 90 edeg                | 0.2 MHz                 | 256                              | 625                                |

| ·                 |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Ungated raw                  | _                       |                                  |                                    |

| Open              | Low   | Low     | 2X                       | Gated 90 edeg                | 0.4 MHz                 | 512                              | 1250                               |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               |                         |                                  |                                    |

| High              | High  | Low     | 4X                       | Gated 90 edeg                | 0.8 MHz                 | 1024                             | 2500                               |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               | _                       |                                  |                                    |

| Low               | Low   | Low     | 8X                       | Gated 90 edeg                | 1.6 MHz                 | 2048                             | 5000                               |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               | _                       |                                  |                                    |

| High              | Low   | Low     | 16X                      | Gated 90 edeg                | 2.0 MHz                 | 4096                             | 10000                              |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               | _                       |                                  |                                    |

| Open              | High  | Low     | 32X                      | Gated 90 edeg                | 2.0 MHz                 | 8192                             | 20000                              |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               | _                       |                                  |                                    |

| Low               | High  | Low     | 64X                      | Gated 90 edeg                | 2.0 MHz                 | 16384                            | 40000                              |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               |                         |                                  |                                    |

| High              | Open  | Low     | 128X                     | Gated 90 edeg                | 2.0 MHz                 | 32768                            | 80000                              |

|                   |       | High    |                          | Gated 180 edeg               |                         |                                  |                                    |

|                   |       | Open    |                          | Gated 360 edeg               |                         |                                  |                                    |

| Low               | Open  | High    | 256x or SPI              | Gated 90edeg or              | 2.0 MHz                 | 65536                            | 160000                             |

|                   |       |         | Mode Output <sup>b</sup> | SPI Mode Output <sup>c</sup> |                         |                                  |                                    |

|                   |       | Low     | SPI Mode <sup>d</sup>    | SPI Mode: Program Selection  | NA                      | NA                               | NA                                 |

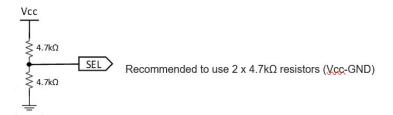

a. Open selection must be connected to middle of a voltage divider circuit.

b. Factory default = 256x ABI output; SPI Mode Output = AB interpolation based on Page 8 setting.

c. Factory default = 90°e output; SPI Mode Output = Index width based on Page 8 setting.

d. SPI Mode = Enable SPI communication.

#### Figure 3: Open Selection

The digital interpolation factor above can be used with the following equations to cater to various rotational speed (RPM) and count per revolution (CPR).

The CPR (at 1X interpolation) is based on the following equation, which is dependent on radius of operation (R<sub>OP</sub>).

CPR = LPI ×

$$2\pi$$

×  $R_{OP}$  (inch) or CPR = LP mm ×  $2\pi$  ×  $R_{OP}$  (mm)

NOTE: LPmm (lines per mm) = LPI / 25.4

# **Programmable Select Options**

The AEDR-9920 digital encoder features an SPI programmable interpolator with a factor from 1x to 512x.

- Configure external selection to SPI Mode: Program Selection.

- 2. For signals output after configuration, set external selection to SPI Mode: Output Enabled.

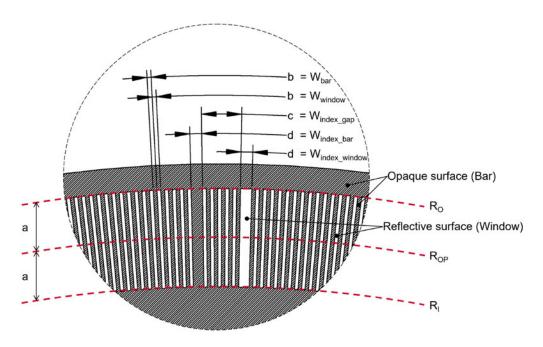

# **SPI Communication Pinout (for Programming Interpolation Settings)**

**Table 1: SPI Protocol Pinout**

| Pin | Name     | Function        |

|-----|----------|-----------------|

| 14  | SPI DOUT | SPI Data Output |

| 21  | SPI DIN  | SPI Data Input  |

| 19  | SPI CLK  | SPI Clock       |

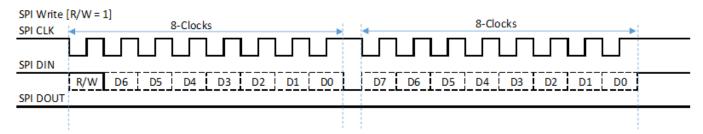

## SPI Read and Write Timing Diagram (Maximum Clock Frequency 1 MHz)

Table 2: SPI Read and Write Memory Map

| Bit   | 15 | 14           | 13           | 12 | 11 | 10 | 9         | 8 | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|--------------|--------------|----|----|----|-----------|---|-----------|---|---|---|---|---|---|---|

| Read  | 0  |              | Address[6:0] |    |    |    |           |   | Data[7:0] |   |   |   |   |   |   |   |

| Write | 1  | Address[6:0] |              |    |    |    | Data[7:0] |   |           |   |   |   |   |   |   |   |

# SPI Write: <Write Command = 1><7bits address><8bits data>

#### Figure 4: SPI Write Timing Diagram

#### SPI Read: <Read Command = 0><7bits address>

Figure 5: SPI Read Timing Diagram

# **Unlock Sequence**

- 1. Write to SPI Address 0x10 with value AB (Hex) to unlock Level 1.

- 2. Write to SPI Address 0x14 with value 00 (Hex) to go to Page 0.

# Interpolation, Index (90°e, 180°e, and 360°e) Setting and Programming

- 1. Write to SPI Address 0x0B and 0x0C with the value shown in the following tables.

- 2. After finalizing the CPR settings in the following tables, write to SPI Address 0x11 (Hex) with a value A1 (Hex) to program EEPROM.

| Byte Address |      |   | Bit |             |         |    |   |    |         |            |

|--------------|------|---|-----|-------------|---------|----|---|----|---------|------------|

| [hex]        | Page | 7 | 6   | 5           | 4       | 3  | 2 | 1  | 0       | Note       |

| 0x0B         | 0    |   |     | Index [1:0] |         |    |   | IN | T [9:8] | INT: 0-512 |

| 0x0C         |      |   |     |             | INT [7: | 0] |   |    |         |            |

| Interpolation<br>Index, 90°e | 0x0B<br>(HEX) | 0x0C<br>(HEX) |

|------------------------------|---------------|---------------|

| 1x                           | 00            | 01            |

| 2x                           | 00            | 02            |

|                              |               |               |

|                              |               |               |

| 10x                          | 00            | 0A            |

| 11x                          | 00            | 0B            |

|                              |               |               |

|                              |               |               |

| 256x                         | 01            | 00            |

|                              |               |               |

|                              |               |               |

| 512x                         | 02            | 0             |

| Interpolation<br>Index, 180°e | 0x0B<br>(HEX) | 0x0C<br>(HEX) |

|-------------------------------|---------------|---------------|

| 1x                            | 10            | 1             |

| 2x                            | 10            | 2             |

|                               |               |               |

|                               |               |               |

| 10x                           | 10            | 0A            |

| 11x                           | 10            | 0B            |

|                               |               |               |

|                               |               | -             |

| 256x                          | 11            | 0             |

|                               |               |               |

|                               |               |               |

| 512x                          | 12            | 0             |

| Interpolation<br>Index, 360°e | 0x0B<br>(HEX) | 0x0C<br>(HEX) |

|-------------------------------|---------------|---------------|

| 1x                            | 30            | 1             |

| 2x                            | 30            | 2             |

|                               |               |               |

|                               |               |               |

| 10x                           | 30            | 0A            |

| 11x                           | 30            | 0B            |

|                               |               |               |

|                               |               |               |

| 256x                          | 31            | 0             |

|                               |               |               |

|                               |               |               |

| 512x                          | 32            | 0             |

# Recommended Setup for the Power Supply Pins and General Routing

Both VDDA, VDD, and the respective grounds (VSSA and VSSD) are to be connected as shown in Figure 6. Be sure to follow these schematic design rules:

- Use a pair of 22-μF and 0.1-μF capacitors as bypass on VDD and VDDA. Place them in parallel as close as possible to the encoder ASIC package, in between the power and ground pins.

- Design separate VDD and VDDA traces from a common input.

- Design separate VSSD and VSSA traces from a common input.

- Minimize trace or cable length where possible.

Figure 6: Power Supply Pins

#### NOTE:

- 1. Pin 25 is the center pad of the package and is designated as AGND.

- 2. Refer to the Select Options Encoder Built-in Interpolation for SEL1X, SEL2X, and IND SEL configuration.

- 3. VDDA and VDD *must* be the same voltage level.

- 4. VSSA and VSSD must be connected together.

# Digital Encoder Characteristics (Code Wheel of R<sub>OP</sub> at 4.6 mm)

|                                 |        |        | Dynamic Performance <sup>a</sup> |     |     |     |     |     |      |      |      |

|---------------------------------|--------|--------|----------------------------------|-----|-----|-----|-----|-----|------|------|------|

| Parameter                       |        |        | Typical <sup>b</sup>             |     |     |     |     |     |      |      |      |

| Interpolation Factor            | Symbol | 1X     | 2X                               | 4X  | 8X  | 16X | 32X | 64X | 128X | 256X | Unit |

| Cycle Error                     | ΔC     | ±5     | ±15                              | ±20 | ±25 | ±30 | ±35 | ±40 | ±57  | ±60  | °е   |

| Pulse Width (Duty) Error        | ΔΡ     | ±5     | ±10                              | ±15 | ±15 | ±20 | ±25 | ±38 | ±45  | ±45  | °е   |

| Phase Error                     | Δφ     | ±2     | ±7                               | ±9  | ±11 | ±15 | ±28 | ±30 | ±33  | ±35  | °е   |

| State Error                     | ΔS     | ±3     | ±7                               | ±9  | ±11 | ±25 | ±28 | ±40 | ±43  | ±45  | °e   |

| Index Pulse Width (Gated 90°)   | Ро     |        | 90                               |     |     |     |     | °е  |      |      |      |

| Index Pulse Width (Gated 180°)  | Ро     | 180    |                                  |     |     |     | °е  |     |      |      |      |

| Index Pulse Width (Gated 360°)  | Po     | NA 360 |                                  |     |     |     | °e  |     |      |      |      |

| Index Pulse Width (Raw Ungated) | Po     | 330 NA |                                  |     |     |     | °е  |     |      |      |      |

a. The optimal performance of the encoder depends on the motor/system setup condition of the individual customer.

#### **Electrical Characteristics**

Characteristics over recommended operating conditions at 25°C.

| Parameter                  | Symbol | Min. | Тур. | Max. | Unit | Notes        |

|----------------------------|--------|------|------|------|------|--------------|

| High Level Output Voltage  | VOH    | 2.4  | _    | _    | V    | IOH = -20mA  |

| Low Level Output Voltage   | VOL    | _    | _    | 0.4  | V    | IOH = +20 mA |

| Output Current Per Channel | lo     | _    | _    | 20   | mA   |              |

| Rise Time                  | tr     | _    | <50  | _    | ns   | CL ≤ 50 pF   |

| Fall Time                  | tf     | _    | <50  | _    | ns   |              |

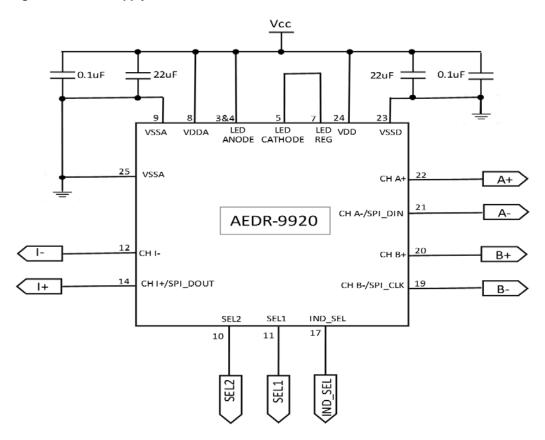

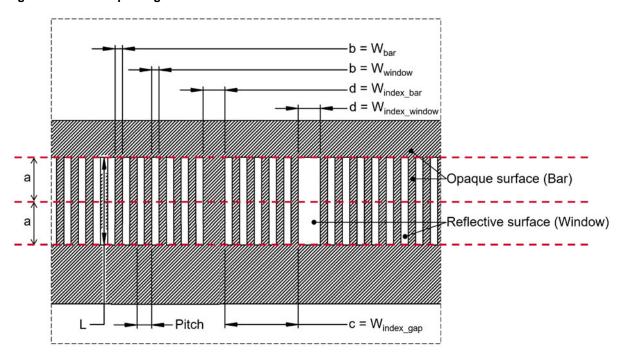

# **Code Wheel Design Guidelines**

- The incremental and index window tracks are reflective surfaces and the window width is denoted by W<sub>window</sub> and W<sub>index window</sub> respectively.

- The incremental and index bar tracks are opaque surfaces and the bar width is denoted by W<sub>bar</sub> and W<sub>index\_bar</sub> respectively.

- There is only one index window track and one index bar track; while the number of incremental window and bar tracks depend on the CPR.

- All incremental window and bar tracks have the same width value, b°.

- Both index window and bar tracks have the same width value, d°.

- There are five pairs of incremental tracks (1 pair = 1 W<sub>window</sub> and 1 W<sub>bar</sub>) between index window and bar track, which denoted by c°.

- The W<sub>window</sub>/W<sub>bar</sub> ratio is recommended to be within a range of 0.95 to 1.05.

- Reflectance of window and bar surface is 60% and 5%, respectively.

b. Typical values represent the average value of the encoder performance based on the factory setup conditions at 2-MHz frequency.

Figure 7: Code Wheel Design

NOTE: Code wheel facing up. Encoder placed on top of Code Wheel in this view.

| Dimension | Formula                          | 225LPI |

|-----------|----------------------------------|--------|

| a (mm)    | $R_O - R_{OP}$ or $R_{OP} - R_i$ | 0.550  |

| b (°)     | (360/CPR)/2                      | _      |

| c (°)     | 10 × b                           | _      |

| d (°)     | 3 × b                            | _      |

# **Code Wheel Design Example**

The following demonstrates a code wheel design for 225LPI at 256 CPR.

Determine  $R_{OP}$ :  $(25.4/225) \times (256/2\pi) = 4.600 \text{ mm}$

Determine  $R_0$ : 4.600 + 0.550 = 5.150 mm

Determine  $R_1$ : 4.600 – 0.550 = 4.050 mm

Determine  $W_{window}$  and  $W_{bar}$ : (360 / 256) / 2 = 0.703°

Determine  $W_{index \ dap}$ :  $10 \times b$  = 7.030°

Determine  $W_{index \ window}$  and  $W_{index \ bar}$ :  $3 \times b$  = 2.109°

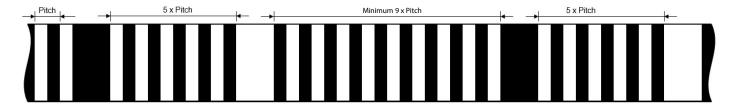

# **Code Strip Design Guideline**

- The incremental and index window tracks are reflective surfaces and the window width is denoted by W<sub>window</sub> and W<sub>index window</sub> respectively.

- The incremental and index bar tracks are opaque surfaces and the bar width is denoted by W<sub>bar</sub> and W<sub>index\_bar</sub> respectively.

- All incremental window and bar tracks have the same width value, b.

- Both index window and bar tracks have the same width value, d.

- There are 5 pairs of incremental tracks (1 pair = 1 W<sub>window</sub> and 1 W<sub>bar</sub>) between index window and bar track, which denoted by c.

Figure 8: Code Strip Design

NOTE: Code wheel facing up. Encoder placed on top of Code Wheel in this view.

| Dimension  | Formula     | 225LPI |

|------------|-------------|--------|

| Pitch (mm) | 25.4/LPI    | 0.113  |

| a (mm)     | L/2         | 0.550  |

| b (mm)     | Pitch/2     | 0.056  |

| c (mm)     | 5 × Pitch   | 0.564  |

| d (mm)     | Pitch × 3/2 | 0.169  |

## **AEDR-9920 Pseudo ABS Recommendation**

#### NOTE:

- 1. Code wheel facing up. Encoder placed on top of Code Wheel in this view.

- 2. Sketch is for illustration purposes only. Not to scale.

| Example 1       |                | Example 2       |                   |

|-----------------|----------------|-----------------|-------------------|

| LPI             | = 225          | CPR             | = 400             |

| Pitch           | = 1 in. / 225  | Pitch           | = 360° / 400      |

|                 | ≈ 113 µm       |                 | = 0.90°           |

| Min Index Pitch | = 9 × 113      | Min Index Pitch | $= 9 \times 0.90$ |

|                 | $= 1017 \mu m$ |                 | = 8.10°           |

### **AEDR-9930 Pseudo ABS Recommendation**

#### NOTE:

- Code wheel facing up. Encoder placed on top of Code Wheel in this view.

- 2. Sketch is for illustration purposes only. Not to scale.

| Example 1       |               | Example 2       |                    |

|-----------------|---------------|-----------------|--------------------|

| LPI             | = 397         | CPR             | = 400              |

| Pitch           | = 1 in. / 397 | Pitch           | = 360° / 400       |

|                 | ≈ 64 µm       |                 | = 0.90°            |

| Min Index Pitch | $=32\times64$ | Min Index Pitch | $= 32 \times 0.90$ |

|                 | = 2048 μm     |                 | = 28.80°           |

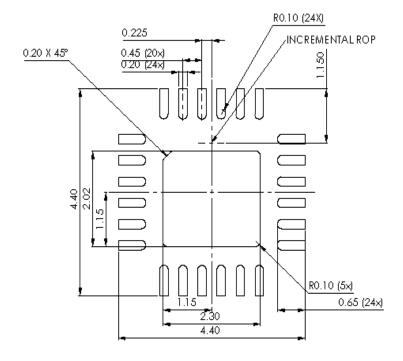

# **Package Outline Drawing**

#### NOTE:

- 1. All dimensions are in millimeters (mm).

- 2. Unless otherwise specified, tolerance is x.xx ± 0.15 mm.

- 3. Package tolerances are not a factor in mechanical misalignment (radial and tangential) stack up.

## **Recommended Land Pattern**

#### NOTE:

- 1. All dimensions are in millimeters (mm).

- 2. Unless otherwise specified, tolerance is  $x.xx \pm 0.05$  mm.

# **Encoder Placement Orientation, Position, and Direction of Movement**

The AEDR-9920 is designed with both the emitter and detector dice placed in parallel to code wheel window/bar orientation. The encoder package mounted on top facing down onto code wheel. When properly aligned, the detector side will be closer to the center of code wheel than the emitter.

The optical center of the encoder package must be aligned tangential to the code wheel's  $R_{OP}$ . The optimal gap setting recommended is 1.00 mm, with the range of 0.50 mm to 1.50 mm.

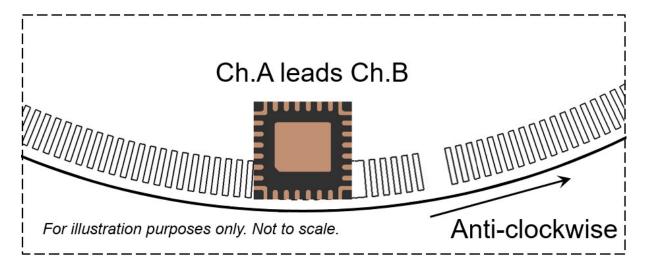

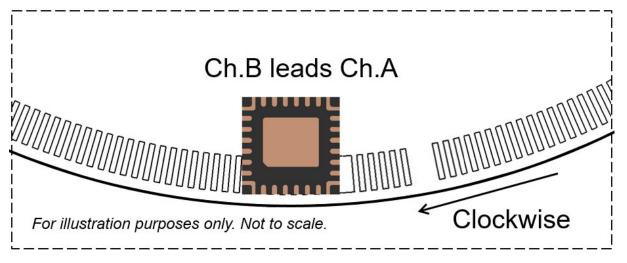

Channel A leads Channel B when the code wheel rotates anti-clockwise and vice versa.

Figure 9: Encoder Placement

Figure 10: Channel A and Channel B

# **Moisture Sensitivity Level**

The AEDR-9920 package is specified to moisture sensitive level 3 (MSL 3). Precaution is required to handle this moisture sensitive product to ensure the reliability of the product.

#### Storage before use:

- Unopened moisture barrier bag (MBB) can be stored at <40°C/90% RH for 12 months.

- Open the MBB just prior to assembly.

#### Control after opening the MBB:

The encoder that will be subjected to reflow solder must be mounted within 168 hours of factory condition <30°C/60% RH.</li>

#### Control for unfinished reel:

Store a sealed MBB with desiccant or desiccators at <5%RH condition.</li>

#### Baking is required if:

- The humidity indicator card (HIC) is >10% when read at  $23 \pm 5$ °C.

- The encoder floor life exceeded 168 hours.

#### Recommended baking condition:

■ 40°C ± 5°C for 22 hours (tape and reel) or 125 ± 10°C for 1 hour (loose units).

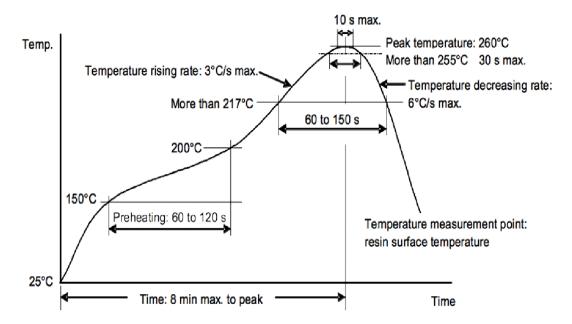

Figure 11: Recommended Lead-Free Solder Reflow Soldering Temperature Profile

**CAUTION!** Use care when handling the encoder ASIC because it is a sensitive optical device. Remove the protective kapton tape only after the reflow process and just before final assembly.

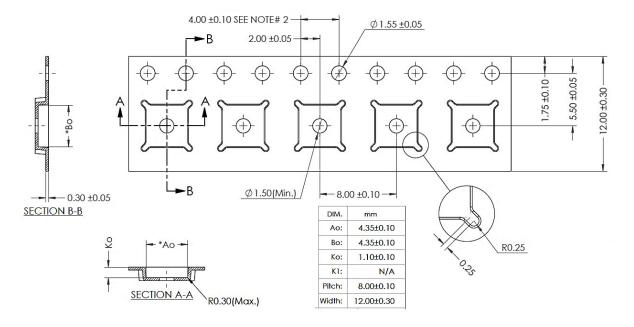

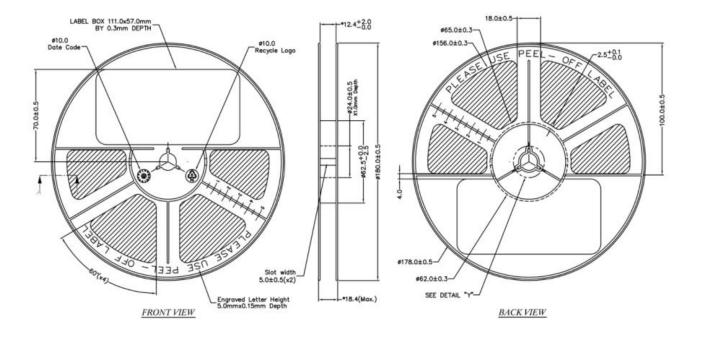

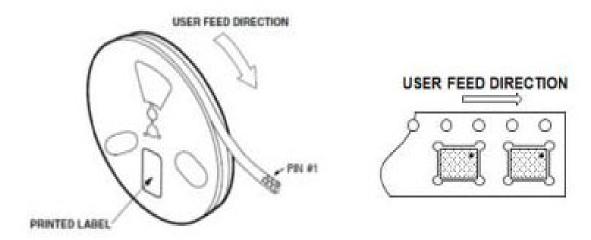

# **Tape and Reel Information**

Figure 12: Tape and Reel

Figure 13: Tape Dimensions

Figure 14: Reel Orientation

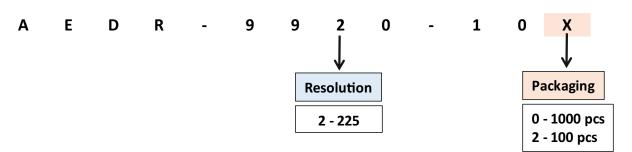

# **Ordering Information**

Copyright © 2020–2022 Broadcom. All Rights Reserved. The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, go to <a href="https://www.broadcom.com">www.broadcom.com</a>. All trademarks, trade names, service marks, and logos referenced herein belong to their respective companies.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.