#### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- Wide operating range: 3.5 to 46  $V_{IN}$ , 50  $V_{IN}$  maximum

- 2.1 MHz PWM switching frequency, avoids AM band

- Selectable outputs: 5.0 V, 3.3 V, 2.5 V

- Minimal external components and extremely small package make the ARG81880 easy to use and save PCB area

- Output voltage accuracy is 53% better than regulators requiring external resistor divider: ±1.8% versus ±3.8%

- Outstanding minimum on-time: typically 20 ns

- PWM frequency dithering and controlled SW node slew rate significantly reduce EMI signature

- Internal loop compensation and internal soft-start lower cost, require less PCB area, and minimize design time

- Compensation automatically adjusts to selected output voltage to maintain high bandwidth and good stability

- Power Good output with rising threshold accuracy (98%) not found in competing regulators

- Selectable current limits allow reduction of output filter component ratings, size, and cost for lower current designs

- Synchronizes to external clock (overrides dithering)

- High-voltage compatible enable input (EN/UV)

- EN/UV input can be used to raise V<sub>IN</sub> UVLO threshold

- Pin-to-pin and pin-to-ground short circuit tolerant at every pin

- Internal 700 m $\Omega$  / 425 m $\Omega$  N-channel MOSFETs

- Operating junction temperature range -40°C to 150°C

#### **APPLICATIONS**

- Underhood

- Infotainment

- · Center Stack

- Clusters

- Telematics

- · ADAS, HUD, AVN

#### **DESCRIPTION**

The ARG81880 is a fixed-frequency synchronous buck regulator complete with control, diagnostics, and protections that efficiently converts automotive battery voltages into tightly regulated output voltages. The ARG81880 does not require an external resistor divider to select  $V_{\rm OUT}$ , which lowers cost, minimizes PCB area, and tightens output voltage tolerance over regulators that must use an external resistor divider to determine  $V_{\rm OUT}$ . The ARG81880 is designed to deliver up to 800 mA of output current, given an adequate thermal solution.

Internal loop compensation and soft-start minimize design effort—saving time, cost, and PCB area. An optional synchronization input allows the ARG81880 to increase or decrease its PWM frequency by  $\pm 10\%$ . The ARG81880 can be enabled by its high-voltage compatible enable input (EN/UV). Also, the EN/UV input can be used to raise the  $V_{IN}$  UV thresholds for higher output voltage systems.

The ARG81880 uses frequency dithering, which has been shown to greatly reduce EMI/EMC. If necessary, frequency dithering may be disabled by applying a synchronization clock at the I<sub>LIM</sub>/SYNC<sub>IN</sub> pin. The ARG81880 includes an open-drain Power Good output (PG) with a relatively short fixed delay.

Protection features include  $V_{\rm IN}$  undervoltage lockout,  $V_{\rm OUT}$  over- and undervoltage protections, PWM pulse-by-pulse current limit, hiccup mode short-circuit protection, SW short-circuit protection, BOOT capacitor protection, and thermal shutdown.

The ARG81880 is supplied in a low-profile 10-lead DFN package (suffix "EJ") with wettable flanks and an exposed power pad.

#### **PACKAGE:**

10-Pin, 3 × 3 mm Wettable Flank DFN with Exposed Thermal Pad (Suffix EJ)

Figure 1: Typical Schematic, 5 V<sub>OUT</sub>, 800 mA Synchronization not used

#### **SELECTION GUIDE**

| Part Number   | Temperature Range | Package                                      | Packing*                    | Lead Frame     |

|---------------|-------------------|----------------------------------------------|-----------------------------|----------------|

| ARG81880KEJTR | –40°C to 150°C    | 10-pin DFN w/ thermal pad and wettable flank | 1500 pieces per 7-inch reel | 100% matte tin |

<sup>\*</sup>Contact Allegro for additional packing options

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic            | Symbol                                         | Notes      | Rating                        | Unit |

|---------------------------|------------------------------------------------|------------|-------------------------------|------|

| VIN, EN/UV                | $V_{\rm IN},V_{\rm EN/UV}$                     |            | −0.3 to 50                    | V    |

|                           |                                                | Continuous | −0.3 to 50                    | V    |

| SW                        | $V_{SW}$                                       | t < 50 ns  | 54                            | V    |

|                           |                                                | t < 250 ns | -1.5                          | V    |

| воот                      | V <sub>BOOT</sub>                              |            | -0.3 to V <sub>IN</sub> + 8 V | V    |

| VOUT, PG                  | $V_{OUT}$ , $V_{PG}$                           |            | -0.3 to 26                    | V    |

| VSET, ILIM/SYNCIN         | V <sub>SET</sub> ,<br>V <sub>ILIM/SYNCIN</sub> |            | −0.3 to 5.5                   | V    |

| Junction Temperature      | $T_J$                                          |            | -40 to 150                    | °C   |

| Storage Temperature Range | T <sub>stg</sub>                               |            | −55 to 150                    | °C   |

<sup>\*</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                          | Symbol          | Test Conditions*                                               | Value | Unit |

|-----------------------------------------|-----------------|----------------------------------------------------------------|-------|------|

| Thermal Resistance, Junction to Ambient | $R_{\theta JA}$ | DFN 10-pin (EJ) package on 4-layer PCB based on JEDEC standard | 45    | °C/W |

<sup>\*</sup> Additional thermal information available on the Allegro website.

#### **Table of Contents**

| Features and Benefits                      | 1 | PWM Frequency and Dithering                      | 9  |

|--------------------------------------------|---|--------------------------------------------------|----|

| Description                                | 1 | Internal Clock and Soft-Starting                 | 10 |

| Package                                    | 1 | Current Limit and Synchronization Input          | 11 |

| Applications                               | 1 | Enable/Undervoltage Function                     | 11 |

| Selection Guide                            | 2 | Power Good Function                              | 12 |

| Absolute Maximum Ratings                   | 2 | Undervoltage Lockout (UVLO)                      |    |

| Thermal Characteristics                    | 2 | Pulse-by-Pulse Current Limit                     | 13 |

| Functional Block Diagram                   | 3 | Output Short-Circuit Protection and Hiccup Mode  |    |

| Pinout Diagrams and Terminal List          |   | SW Pin Protectioon                               | 14 |

| Electrical Characteristics                 |   | BOOT Pin Protections                             | 14 |

| Functional Description                     | 8 | Overvoltage Protection (OVP)                     | 14 |

| Overview                                   |   | Thermal Protection                               |    |

| Output Voltage Accuracy and Selection      | 8 | Pin-to-Ground and Adjacent Pin Short Protections | 15 |

| Adjustable Current Limit                   |   | Component Selections                             | 18 |

| PWM Control and Internal Loop Compensation |   | Package Outline Drawing                          |    |

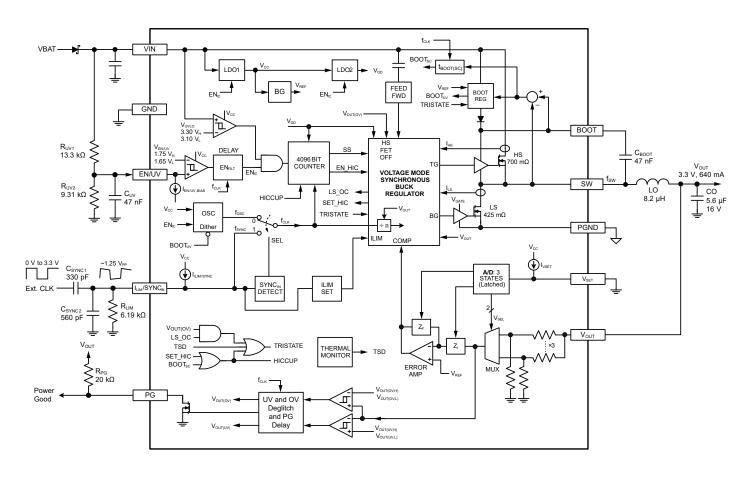

#### **FUNCTIONAL BLOCK DIAGRAM**

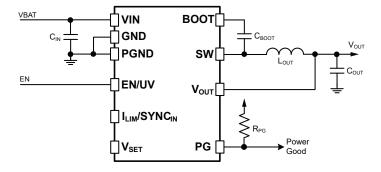

Figure 2: Block Diagram / Typical Schematic

Component values shown are for 12  $V_{IN}$ , 3.3  $V_{OUT}$  at 640 mA. The  $V_{IN}$  Start/Stop thresholds raised to 4.25 V / 4.0 V using a resistor divider at the EN/UV pin

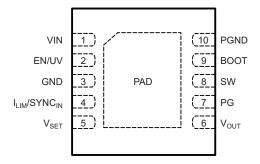

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

Package EJ, 10-Pin DFN Pinout Drawing

#### **Terminal List**

| Pin Number | Pin Name                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VIN                                  | Input voltage to the control circuit and drain of the high-side MOSFET. Connect several high quality ceramic capacitors from this pin directly to PGND. Do not use vias when connecting these capacitors.                                                                                                                                                                                                                                                                                                                     |

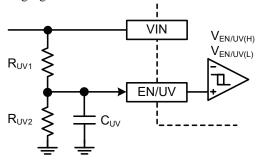

| 2          | EN/UV                                | High-voltage tolerant enable input: HIGH = ON, LOW = OFF. If a resistor divider is placed between this pin and VIN, it will increase the V <sub>IN</sub> UVLO threshold.                                                                                                                                                                                                                                                                                                                                                      |

| 3          | GND                                  | Analog ground for the control circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

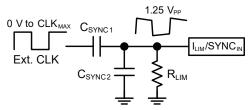

| 4          | I <sub>LIM</sub> /SYNC <sub>IN</sub> | Dual function pin: current limit selection and (optional) external synchronization input. This pin should be either open circuit or connected to ground through a resistor to set the current limit. An external clock may be AC-coupled to this pin via a capacitor-divider to raise or lower the switching frequency by about ±10%. The capacitor divider should be chosen to produce typically 1.25 V <sub>PP</sub> at the I <sub>LIM</sub> /SYNC <sub>IN</sub> pin. The functionality of this pin is detailed in Table 2. |

| 5          | V <sub>SET</sub>                     | Output voltage selection pin. The functionality of this pin is detailed in Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6          | V <sub>OUT</sub>                     | Output voltage sense and feedback pin to the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

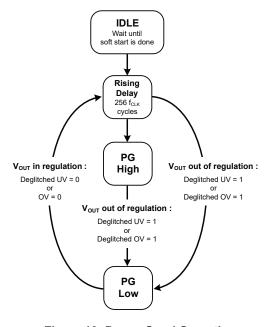

| 7          | PG                                   | Open-drain Power Good (PG) output. An external pull-up resistor must be connected to this pin. This signal will be high if V <sub>OUT</sub> is in regulation. This pin will transition low if V <sub>OUT</sub> is out of regulation—undervoltage or overvoltage. See Figure 13 for a state diagram showing the operation of the PG pin.                                                                                                                                                                                       |

| 8          | SW                                   | Switching node for the synchronous buck regulator. Connect this pin to the output inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9          | воот                                 | Bootstrap supply input for the high-side gate driver. Connect a high quality 47 nF / 16 V <sub>MIN</sub> ceramic capacitor from this pin to the SW node.                                                                                                                                                                                                                                                                                                                                                                      |

| 10         | PGND                                 | Source of the low-side MOSFET and ground for its gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _          | PAD                                  | Exposed thermal pad; tie to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

**ELECTRICAL CHARACTERISTICS** <sup>[1]</sup>: Unless otherwise noted, specifications are valid at 3.5 V ≤ V<sub>IN</sub> ≤ 46 V, −40°C ≤ T<sub>.I</sub> ≤ 150°C

| Characteristics                               | Symbol                 | Test Conditions                                                                            | Min. | Тур.                 | Max. | Unit                  |

|-----------------------------------------------|------------------------|--------------------------------------------------------------------------------------------|------|----------------------|------|-----------------------|

| GENERAL SPECIFICATIONS                        |                        |                                                                                            |      |                      |      |                       |

| Operating Input Voltage                       | V <sub>IN</sub>        | After V <sub>IN</sub> > V <sub>INSTART</sub> , EN/UV = 1                                   | 3.5  | _                    | 46   | V                     |

| V <sub>IN</sub> UVLO Start                    | V <sub>IN(START)</sub> | V <sub>IN</sub> rising                                                                     | 3.15 | 3.30                 | 3.45 | V                     |

| V <sub>IN</sub> UVLO Stop                     | V <sub>IN(STOP)</sub>  | V <sub>IN</sub> falling                                                                    | 2.95 | 3.10                 | 3.25 | V                     |

| Supply Quiescent Current [1]                  | $I_{Q}$                | EN/UV = 1, No PWM or BOOT switching                                                        | -    | 5.7                  | _    | mA                    |

| Supply Quiescent Current 11                   | I <sub>Q(SLEEP)</sub>  | $V_{IN} = 12 \text{ V}, T_J \le 85^{\circ}\text{C}$ [2], EN/UV = 0, $V_{SW} = 0 \text{ V}$ | _    | 2.5                  | 5    | μA                    |

| OUTPUT VOLTAGE                                |                        |                                                                                            |      |                      |      |                       |

| Output Voltage Accuracy [3]                   | V <sub>OUT</sub>       | V <sub>IN</sub> = 12 V                                                                     | -1.8 | ±1.3 [2]             | +1.8 | %                     |

| PULSE WIDTH MODULATION (PW                    | M) TIMING              |                                                                                            |      |                      |      |                       |

| Buck Minimum On-Time [2]                      | t <sub>ON(MIN)</sub>   | V <sub>IN</sub> = 12 V, Measure pulse width from 10% of rising edge to 90% of falling edge | -    | 20                   | 40   | ns                    |

| Buck Minimum Off-Time                         | t <sub>OFF(MIN)</sub>  |                                                                                            | _    | 65                   | 100  | ns                    |

| PWM FREQUENCY AND DITHERIN                    |                        | -                                                                                          |      |                      |      |                       |

| Oscillator Frequency (no SYNC <sub>IN</sub> ) | f <sub>OSC</sub>       | RSET = GND, OPEN, 15.4 kΩ                                                                  | 1.98 | 2.20                 | 2.44 | MHz                   |

| Frequency Dithering Range                     | Δf <sub>OSC</sub>      | No SYNC <sub>IN</sub>                                                                      | _    | ±9                   | _    | % of f <sub>OSC</sub> |

| Dithering Modulation Frequency                | f <sub>MOD</sub>       | No SYNC <sub>IN</sub>                                                                      | _    | 11                   | _    | kHz                   |

| Minimum PWM Frequency                         | f <sub>PWM(MIN)</sub>  | $f_{OSC(MIN)} - \Delta f_{OSC(MAX)}$                                                       | 1.81 | _                    | _    | MHz                   |

| Operational Frequency Foldback                | f <sub>SW(FB)</sub>    | f <sub>OSC</sub> = 2.1 MHz and V <sub>OUT</sub> < 1.1 V                                    | _    | f <sub>CLK</sub> / 4 | _    | _                     |

| MOSFET CHARACTERISTICS                        |                        |                                                                                            |      |                      |      |                       |

| High-Side MOSFET On-Resistance                | Ь                      | $T_J = 25^{\circ}C$ [2], $V_{BOOT} - V_{SW} = 4.5 \text{ V}$ , $I_{DS} = 400 \text{ mA}$   | -    | 700                  | _    | mΩ                    |

| riigii-olde MOOFET Off-Resistance             | $R_{ds(ON,HS)}$        | $T_J = 150$ °C, $V_{BOOT} - V_{SW} = 4.5$ V, $I_{DS} = 400$ mA                             | _    | _                    | 1790 | mΩ                    |

| Low-Side MOSFET On-Resistance                 |                        | $T_J = 25^{\circ}C^{[2]}, V_{IN} > 6 \text{ V}, I_{DS} = 400 \text{ mA}$                   | _    | 425                  | _    | mΩ                    |

| Low-Side MOSFET Off-Resistance                | R <sub>ds(ON,LS)</sub> | $T_J = 150$ °C, $V_{IN} > 6$ V, $I_{DS} = 400$ mA                                          | -    | _                    | 875  | mΩ                    |

| MOSFET Non-Overlap Time [2]                   | t <sub>NO</sub>        |                                                                                            | _    | 8                    | _    | ns                    |

| SW Node Rising Slew Rate [2]                  | SR <sub>SW</sub>       | 12 V < V <sub>IN</sub> < 16 V                                                              | _    | 4.0                  | _    | V/ns                  |

| PWM PULSE-BY-PULSE CURRENT                    | LIMITS                 |                                                                                            |      |                      |      |                       |

|                                               |                        | R <sub>LIM</sub> = OPEN                                                                    | 1275 | 1500                 | 1725 | mA                    |

| High-Side MOSFET Current Limit                | I <sub>LIM(HS)</sub>   | $R_{LIM} = 6.19 \text{ k}\Omega$                                                           | 1010 | 1190                 | 1370 | mA                    |

|                                               |                        | R <sub>LIM</sub> = 17.8 kΩ                                                                 | 770  | 910                  | 1050 | mA                    |

| SW Short Circuit Current Limit                |                        | R <sub>LIM</sub> = OPEN                                                                    | _    | 3.8                  | _    | А                     |

| (hiccup mode after 2 consecutive              | I <sub>LIM(SC)</sub>   | $R_{LIM} = 6.19 \text{ k}\Omega$                                                           | _    | 3.4                  | _    | А                     |

| detections)                                   |                        | R <sub>LIM</sub> = 17.8 kΩ                                                                 | _    | 2.8                  | _    | А                     |

| Low-Side MOSFET Current Limit                 | I <sub>LIM(LS)</sub>   |                                                                                            | 0.5  | 0.7                  | 0.9  | А                     |

Continued on next page...

## **ELECTRICAL CHARACTERISTICS** [1] (continued): Unless otherwise noted, specifications are valid at $3.5 \text{ V} \le \text{V}_{\text{IN}} \le 46 \text{ V}$ , $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$

| Characteristics                                                | Symbol                   | Test Conditions                                | Min. | Тур.                 | Max. | Unit                           |

|----------------------------------------------------------------|--------------------------|------------------------------------------------|------|----------------------|------|--------------------------------|

| HICCUP MODE PROTECTION                                         | •                        |                                                |      |                      |      |                                |

| V <sub>OUT</sub> Hiccup Enable Delay                           | t <sub>HIC(EN)</sub>     |                                                | _    | 512                  | _    | f <sub>CLK</sub> cycles        |

| Hiccup Recovery Time                                           | t <sub>HIC(REC)</sub>    | HICCUP = 1                                     | _    | 4096                 | _    | f <sub>CLK</sub> cycles        |

| DWM Overson Country                                            | +                        | V <sub>OUT</sub> < 25%                         | _    | 30                   | _    | OC Counts<br>@ f <sub>SW</sub> |

| PWM Overcurrent Counts                                         | t <sub>PWM(OC)</sub>     | V <sub>OUT</sub> > 25%                         | _    | 120                  | -    | OC Counts<br>@ f <sub>SW</sub> |

| V <sub>BOOT</sub> Short Circuit Counts                         | t <sub>BOOT(SC)</sub>    |                                                | _    | 64                   | -    | f <sub>CLK</sub> cycles        |

| SOFT-START TIME AND FREQUEN                                    |                          |                                                |      |                      |      |                                |

| Soft-Start Ramp Time                                           | t <sub>SS</sub>          |                                                | _    | 4096                 | _    | f <sub>CLK</sub> cycles        |

|                                                                |                          | $T_J = 150$ °C, $V_{OUT} = 0 V$                | _    | f <sub>CLK</sub> / 8 | _    | _                              |

| Soft-Start Frequency Foldback                                  | f f                      | T <sub>J</sub> = 150°C, V <sub>OUT</sub> = 11% | _    | f <sub>CLK</sub> / 4 | _    | _                              |

| Solt-Start Frequency Foldback                                  | f <sub>SW(SS)</sub>      | $T_J = 150$ °C, $V_{OUT} = 20$ %               | _    | f <sub>CLK</sub> / 2 | _    | _                              |

|                                                                |                          | $T_J = 150$ °C, $V_{OUT} = 35$ %               | _    | f <sub>CLK</sub>     | _    | _                              |

| ENABLE/UNDER-VOLTAGE INPUT                                     | (EN/UV) AN               | D DEGLITCH                                     |      |                      |      |                                |

| EN/UV Thresholds                                               | V <sub>EN/UV(H)</sub>    | V <sub>EN/UV</sub> rising                      | 1.58 | 1.75                 | 1.92 | V                              |

| LIV/OV Tillesholds                                             | V <sub>EN/UV(L)</sub>    | V <sub>EN/UV</sub> falling                     | 1.49 | 1.65                 | 1.81 | V                              |

| EN/UV Hysteresis                                               | V <sub>EN/UV(HYS)</sub>  | $V_{EN/UV(H)} - V_{EN/UV(L)}$                  | _    | 100                  | _    | mV                             |

| EN/UV Bias Current [1]                                         | ī                        | $V_{EN/UV} = 1.4 V$                            | _    | 4.5                  | _    | μΑ                             |

| LIV/OV Blas Guiterit                                           | I <sub>EN/UV(BIAS)</sub> | V <sub>EN/UV</sub> ≥ 12 V                      | _    | 10                   | _    | μΑ                             |

| ENABLE FILTER/DEGLITCH TIME                                    |                          |                                                |      |                      |      |                                |

| Enable Filter/Deglitch Time                                    | EN <sub>FILT</sub>       |                                                | _    | 32                   | _    | f <sub>CLK</sub> cycles        |

| V <sub>SET</sub> AND I <sub>LIM</sub> /SYNC <sub>IN</sub> PINS |                          |                                                |      |                      |      |                                |

| V <sub>SET</sub> Bias Current [1]                              | I <sub>VSET</sub>        | V <sub>SET</sub> = 2 V                         | -94  | -104                 | -114 | μA                             |

| I <sub>LIM</sub> /SYNC <sub>IN</sub> Bias Current [1]          | I <sub>ILIM/SYNC</sub>   | V <sub>ILIM</sub> /V <sub>SYNCIN</sub> = 2 V   | -92  | -104                 | -116 | μA                             |

| SYNCHRONIZATION INPUT                                          |                          |                                                |      |                      |      |                                |

| Synchronization Frequency Range                                | f <sub>SYNC</sub>        |                                                | 1.89 | _                    | 2.4  | MHz                            |

| Synchronization Voltage Sensitivity                            | ΔV <sub>SYNC</sub>       | $V_{SYNC} = 3.0 V_{DC}$                        | 1.0  | 1.25                 | 1.5  | V <sub>PP</sub>                |

| Synchronization Transition Time [2]                            | t <sub>SYNC</sub>        |                                                | _    | 20                   | 100  | μs                             |

| Synchronization CLK Duty Cycle                                 | D <sub>SYNC</sub>        |                                                | 40   | 50                   | 60   | %                              |

| Synchronization CLK Rise and Fall Time [2]                     | t <sub>R/F(SYNC)</sub>   |                                                | _    | _                    | 15   | ns                             |

Continued on next page...

# 50 V, 800 mA, 2.2 MHz, Synchronous Buck Regulator with Internal Compensation, Frequency Dithering, Adjustable Current Limit, Synchronization, and Power Good

## **ELECTRICAL CHARACTERISTICS** [1] (continued): Unless otherwise noted, specifications are valid at $3.5 \text{ V} \le \text{V}_{\text{IN}} \le 46 \text{ V}$ , $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$

| Characteristics                          | Symbol                            | Test Conditions                                               | Min. | Тур. | Max. | Unit                    |

|------------------------------------------|-----------------------------------|---------------------------------------------------------------|------|------|------|-------------------------|

| POWER GOOD (PG) RISING DELAY             | , FILTER/D                        | EGLITCH TIMES, AND UV/OV THRESHOLDS                           |      |      |      |                         |

| PG Rising Delay                          | t <sub>dPG</sub>                  | V <sub>OUT</sub> rising                                       | _    | 256  | _    | f <sub>CLK</sub> cycles |

| UV Filter/Deglitch Times                 | t <sub>dUV</sub>                  | V <sub>OUT</sub> rising or falling                            | _    | 64   | _    | f <sub>CLK</sub> cycles |

| V LIV Throsholds                         | V <sub>OUT(UV,H)</sub>            | V <sub>OUT</sub> rising                                       | _    | 98   | -    | %                       |

| V <sub>OUT</sub> UV Thresholds           | V <sub>OUT(UV,L)</sub>            | V <sub>OUT</sub> falling                                      | 94   | 95   | 96   | %                       |

| V <sub>OUT</sub> UV Hysteresis           | V <sub>OUT(UV,HYS)</sub>          | $V_{OUT(UV,H)} - V_{OUT(UV,L)}$                               | _    | 3    | _    | %                       |

| OV Filter/Deglitch Times                 | t <sub>dOV</sub>                  | V <sub>OUT</sub> rising only                                  | _    | 128  | _    | f <sub>CLK</sub> cycles |

| V OV Three health                        | V <sub>OUT(OV,H)</sub>            | V <sub>OUT</sub> rising                                       | 106  | 107  | 108  | %                       |

| V <sub>OUT</sub> OV Thresholds           | $V_{OUT(OV,L)}$                   | V <sub>OUT</sub> falling                                      | _    | 104  | _    | %                       |

| V <sub>OUT</sub> OV Hysteresis           | V <sub>OUT(OV,HYS)</sub>          | $V_{OUT(OV,H)} - V_{OUT(OV,L)}$                               | _    | 3    | _    | %                       |

| POWER GOOD (PG) INITIALIZATIO            | N AND OUT                         | PUT VOLTAGES                                                  |      |      |      |                         |

| PG Initialization at Low V <sub>IN</sub> | V <sub>PG(INIT)</sub>             | $V_{IN} = 1.5 \text{ V}, I_{PG} = 330 \mu\text{A}, EN/UV = 0$ | _    | -    | 400  | mV                      |

| PG Low Output Voltage                    | V <sub>PG(LOW)</sub>              | EN/UV = 1, V <sub>IN</sub> ≥ 2.5 V, I <sub>PG</sub> = 4 mA    | _    | 150  | 400  | mV                      |

| DC Lookaga Current                       |                                   | V <sub>PG</sub> = 5 V, T <sub>J</sub> ≤ 85°C [2]              | _    | _    | 1    | μA                      |

| PG Leakage Current                       | I <sub>PG,LKG</sub>               | V <sub>PG</sub> = 5 V                                         | _    | _    | 6    | μA                      |

| THERMAL SHUTDOWN PROTECTION              | THERMAL SHUTDOWN PROTECTION (TSD) |                                                               |      |      |      |                         |

| Thermal Shutdown Threshold [2]           | T <sub>TSD</sub>                  | $T_J$ rising                                                  | 160  | 175  | 190  | °C                      |

| Thermal Shutdown Hysteresis [2]          | T <sub>HYS</sub>                  |                                                               | _    | 20   | _    | °C                      |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Typical specification applies from  $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}$ . Min/max specifications apply from  $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ .

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The ARG81880 is a wide input voltage range, high performance synchronous buck regulator designed specifically for demanding automotive and industrial applications. The device requires minimal external components, and combined with its very small footprint, is easy to use, reduces system cost, and saves PCB area.

The ARG81880 provides excellent output voltage accuracy ( $\pm 1.8\%$ ) compared to regulators needing an external resistor divider ( $\pm 3.8\%$ ). The device uses a proprietary voltage mode control algorithm to deliver exceptional minimum on-times, as low as 20 ns, and is capable of jitter-free operation. It employs PWM frequency dithering to reduce its EMI/EMC signature as much as 16 dB, and provides an adjustable current limit, so the rating and size of the output filter components (L and C) can be optimized to each application, saving cost and PCB area. The ARG81880 has internal compensation that automatically adjusts for each output voltage to maintain high bandwidth and good stability. It provides a Power Good output with a typical rising threshold of 98%, an accuracy not found in competing regulators.

The ARG81880 operates at a fixed frequency of 2.1 MHz, above the AM band, and delivers 5.0 V, 3.3 V, or 2.5 V from input voltages as high as 46 V. The ARG81880 can accept an external clock, so multiple regulators can be synchronized in-phase (same clock) or 180° out-of-phase (clock and inverted clock) to reduce input capacitor requirements. The ARG81880 has a high-voltage tolerant enable input and an internally fixed soft-start time.

Protection features of the ARG81880 include  $V_{\rm IN}$  undervoltage lockout, cycle-by-cycle current limit, hiccup mode short-circuit protection, overvoltage protection, and thermal shutdown.

#### **Output Voltage Accuracy and Selection**

The ARG81880 provides a DC output voltage accuracy of  $\pm 1.3\%$  when its junction temperature is 0°C <  $T_J$  < 85°C, and  $\pm 1.8\%$  when -40°C <  $T_J$  < 150°C. It also monitors  $V_{OUT}$  directly so its accuracy is not compromised by an external resistor divider between  $V_{OUT}$  and a feedback pin. Traditional regulators using a  $\pm 1\%$  reference and an external resistor divider created with two  $\pm 1\%$ , 50 ppm resistors can only offer output voltage accuracies of  $\pm 3.8\%$ .

The ARG81880 offers three output voltages: 5.0 V, 3.3 V, and 2.5 V. The output voltage is selected by setting the state of the  $V_{\rm SET}$  pin according to the following table. The  $V_{\rm SET}$  pin is sampled at power-up and the output voltage is internally latched at that time. This means the output voltage cannot change during

operation. This prevents noise or transients from erroneously altering the output voltage.

**Table 1: Output Voltage Selections**

| V <sub>OUT</sub> (V) | V <sub>SET</sub> Pin State |  |

|----------------------|----------------------------|--|

| 5.0                  | OPEN                       |  |

| 3.3                  | GND                        |  |

| 2.5                  | 15.4 kΩ ± 1%               |  |

#### **Adjustable Current Limit**

The ARG81880 supports three possible load currents: 800 mA, 640 mA, or 480 mA. The load current is selected by setting the state of the  $I_{LIM}/SYNC_{IN}$  pin according to the following table. The pulse-by-pulse current limit scales with the load current selected. Providing multiple current settings allows the designer to reduce the saturation current, physical size, and cost of the output inductor for lower current applications.

**Table 2: Current Selection**

| I <sub>OUT</sub> (mA) | High-Side Current<br>Limit, I <sub>LIM(HS)</sub> (mA) | I <sub>LIM</sub> /SYNC <sub>IN</sub> State<br>or R <sub>LIM</sub> Value                        |

|-----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 800                   | 1500                                                  | OPEN                                                                                           |

| 640                   | 1190                                                  | GND if SYNC <sub>IN</sub> is not used; otherwise 6.19 k $\Omega$ , ±1% or 6.2 k $\Omega$ , ±5% |

| 480                   | 910                                                   | 17.8 kΩ, ±1% or<br>18 kΩ, ±5%                                                                  |

Note, for the 640 mA design, if synchronization is not needed, the  $R_{LIM}$  resistor can be omitted and the  $I_{LIM}$ /SYNC $_{IN}$  pin can be connected directly to ground. This reduces the component count by one resistor which saves cost and PCB area.

#### **PWM Control and Internal Loop Compensation**

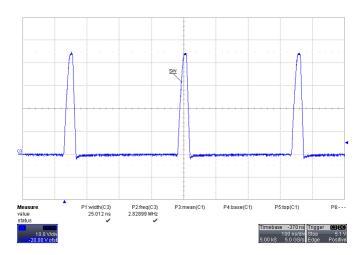

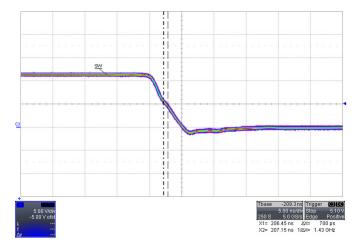

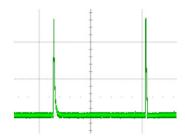

The ARG81880 uses a proprietary voltage mode control algorithm. This control scheme provides excellent noise immunity, incredibly low minimum on-times, and is capable of delivering pulse-widths that are virtually jitter free. Also, the ARG81880 incorporates  $V_{\rm IN}$  feed-forward compensation to supplement the control loop during fast line transients. Figure 2 shows repeatable, closed-loop control producing on-times of only 25 ns—not just a single short pulse during startup or while pulse skipping. Figure 3 shows pulse-width jitter of less than 1 ns while using SYNC<sub>IN</sub>.

Figure 3: Repeatable, Controlled On-Times of only 25 ns.  $46 \, V_{IN}, \, 2.5 \, V_{OUT}, \, 2.8 \, MHz$  at 400 mA load.

Figure 4: Less than 1 ns of Pulse Width Jitter, (5 ns/DIV). Trace captured with infinite oscilloscope persistence.  $12\,V_{IN}$ ,  $5\,V_{OUT}$  at  $800\,\text{mA}$ .

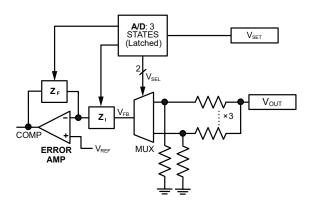

The ARG81880 employs internal compensation. This makes it very easy to use, reduces PCB area, and lowers cost. However, unlike other internally compensated regulators, the ARG81880 stores specific compensation values for each of its output voltage settings. When the output voltage is selected, the ARG81880 compensates itself to maintain high bandwidth, fast transient response, and good gain and phase margins.

Figure 5: The Error Amplifier Compensation  $(Z_F, Z_I)$  is modified when the output voltage is programmed.

#### PWM Frequency and Dithering

The ARG81880 includes two state-of-the-art techniques to help reduce EMI/EMC for demanding automotive applications.

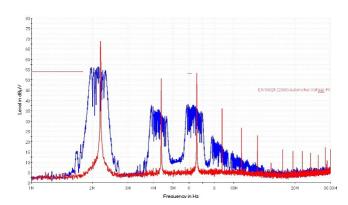

First, the ARG81880 performs dithering of the PWM frequency. Dithering the PWM frequency spreads the energy above and below the nominal frequency. A typical fixed-frequency PWM regulator will create distinct "spikes" of energy at the switching frequency, and at multiples of the switching frequency. Conversely, the ARG81880 spreads the spectrum around the switching frequency, thus creating a lower magnitude at any comparative frequency. Frequency dithering is disabled if an external clock is applied to SYNC<sub>IN</sub>.

Second, the ARG81880 controls the rising slew rate of the SW node to approximately 4 V/ns. A controlled SW rise time reduces high frequency ringing and harmonics of the regulator.

The dithering sweep is internally set at  $\Delta f_{OSC}$  (±9%). This means the PWM switching frequency will ramp from 0.91 to 1.09 times the base frequency ( $f_{OSC}$ ). However, the lowest PWM frequency,  $f_{OSC} - \Delta f_{OSC}$ , is guaranteed not to fall below  $f_{PWM(MIN)}$  (1.81 MHz), thus keeping harmonics out of the AM band. The rate or modulation frequency sweeps a triangular pattern operating at  $f_{MOD}$  (11 kHz).

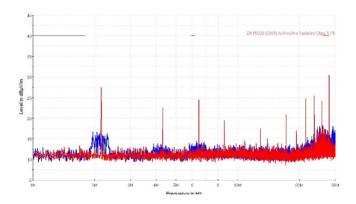

The following two figures compare the conducted and radiated emissions of the ARG81880 with dithering disabled (a trim option) to the ARG81880 employing PWM dithering. The external components, operating conditions, and PCB layouts of the two setups were identical. From these plots, it is clear that PWM dithering significantly reduces the peak levels of energy produced by a traditional, non-dithering regulator.

Figure 6: Comparison with Dithering (blue) and Non-Dithering (red) Conducted Emissions (Peak) in dBµV.

**Table 3: Sample Values from Conducted Emissions Testing**

| Freq.    | Typical PWM | ARG81880 | Improvement |

|----------|-------------|----------|-------------|

| 2.1 MHz  | 69          | 56       | –13 dB      |

| 4.2 MHz  | 51          | 35       | –16 dB      |

| 10.5 MHz | 26          | 12       | -14 dB      |

Figure 7: Comparison with Dithering (blue) and Non-Dithering (red) Radiated Emissions (Peak) in dBµV/m.

**Table 4: Sample Values from Radiated Emissions Testing**

| Freq.   | Typical PWM | ARG81880 | Improvement |

|---------|-------------|----------|-------------|

| 2.1 MHz | 28          | 16       | –12 dB      |

| 4.2 MHz | 23          | 14       | –11 dB      |

| 21 MHz  | 25          | 15       | –10 dB      |

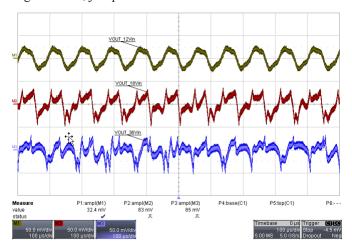

Frequency dithering has obvious benefits, but combined with the control algorithm can produce nontraditional output voltage ripple that increases slightly at higher  $V_{\rm IN}$ . The peak-to-peak ripple is relatively low, but may have a random appearance as shown in the following figure. The output voltage ripple can increase

further if the junction temperature exceeds the absolute maximum rating of 150°C, just prior to TSD.

Figure 8: Output Voltage Ripple at 12 V, 18 V, and 36 V Input. 5 V Output, 800 mA Loading (50 mV/DIV, 100 µs/DIV).

#### Internal Clock and Soft-Starting

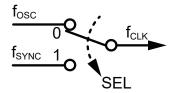

The clock frequency,  $f_{CLK}$ , is derived from either the internal 2.1 MHz oscillator ( $f_{OSC}$ ) or the external clock frequency ( $f_{SYNC}$ ), if one is applied to the  $I_{LIM}/SYNC_{IN}$  pin. Timing functions within the ARG81880 (soft-start, deglitch, delays, etc.) are relative to  $f_{CLK}$ .

Figure 9: The main clock frequency,  $f_{CLK}$ , is derived from either the internal oscillator ( $f_{OSC}$ ) or external clock ( $f_{SYNC}$ ).

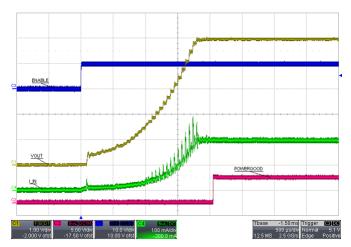

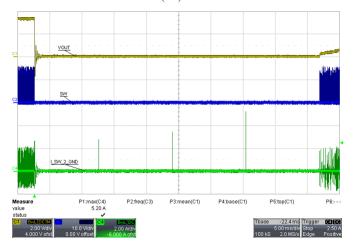

Soft-start of the ARG81880 is internally fixed at 4096 clock cycles ( $f_{CLK}$ ). Based on  $f_{OSC}$  (2.1 MHz), the typical soft-start time is about 1.95 ms. If no faults exist and EN/UV transitions high, the ARG81880 will begin its soft-start routine.

At the beginning of soft-start, the PWM switching frequency  $(f_{SW})$  is temporarily folded back to  $f_{CLK}/8$  while  $V_{OUT}$  is very low. Folding back the frequency extends the PWM off-time which allows the inductor current to decay much further than it would otherwise. Thus, longer off-times significantly limit the peak current in the inductor when the regulator output is shorted to ground. Also, folding back the PWM frequency results in a longer time period which enables the control loop to achieve

much lower duty cycles and better regulation.

As  $V_{OUT}$  rises, the switching frequency ( $f_{SW}$ ) increases to  $f_{CLK}/4$ ,  $f_{CLK}/2$ , and finally  $f_{CLK}$  at about 35% of the steady-state output.

Figure 10: Typical Soft-Start Triggered by the Enable Input. Power Good transitions high only after V<sub>OUT</sub> achieves 100%.

#### **Current Limit and Synchronization Input**

The  $I_{LIM}/SYNC_{IN}$  input provides two functions. First, if this pin is open or has a resistor connected to ground, the current limit can be set to one of the three values shown in Table 2. Second, an external clock can be applied to this pin to synchronize two or more regulators either in phase (same clock) or  $180^{\circ}$  out of phase (clock and inverted clock). The ARG81880 can be synchronized from 1.89 to 2.4 MHz.

The external clock must be AC-coupled to this pin via a capacitor divider, as shown below. The capacitor values must be chosen to produce at least 1.0  $V_{PP}$  but not more than 1.5  $V_{PP}$  at the  $SYNC_{IN}$  pin, given the lowest and highest peak-to-peak voltages of the external clock.

Figure 11: AC-Coupling of an External Clock to SYNC<sub>IN</sub>

The synchronization capacitors should be relatively low value ceramic capacitors (100 to 1000 pF) with tight initial tolerances ( $\pm 5\%$  initial tolerance) and good stability across temperature

(COG/NPO type, 30 ppm). The ratio of the synchronization capacitors can be calculated using the following formula.

Equation 1:

$$\frac{C_{SYNCI}}{C_{SYNC2}} = \frac{1.25 \text{ V}}{CLK_{MAX} - 1.25 \text{ V}}$$

**Table 5: Recommended Synchronization Capacitor Values**

| External Clock | CSYNC1 | CSYNC2 |  |

|----------------|--------|--------|--|

| 0 to 3.3 V     | 330 pF | 560 pF |  |

| 0 to 5.0 V     | 180 pF | 560 pF |  |

#### **Enable/Undervoltage Function**

The enable/undervoltage input (EN/UV) allows the system to selectively enable and disable the ARG81880. Also, the EN/UV pin is rated to 50 V, so the ARG81880 can be automatically controlled from an analog voltage, for example, directly from  $V_{\rm IN}$  or from another regulators output. In addition, the enable input can be used as a programmable UVLO. Connecting a resistor divider from VIN to enable implements this feature as shown in the following figure.

Figure 12: Using EN/UV as a Programmable UVLO.  $C_{UV}$  filters transients on VIN and is strongly recommended.

The programmed UVLO thresholds can be calculated using the following formulas.

Equation 2:

$$V_{IN(START)} = \frac{R_{UVI} + R_{UV2}}{R_{UV2}} \times V_{EN/UV(H)}$$

Equation 3:

$$V_{IN(STOP)} = \frac{R_{UVI} + R_{UV2}}{R_{UV2}} \times V_{EN/UV(L)}$$

If the EN/UV pin is floating, an internal current sink will pull the voltage down and disable the regulator. When the ARG81880 is disabled, it will draw less than 5  $\mu A$  from the input provided  $T_J \leq 85^{\circ} C$ . When EN transitions low, the device waits 32  $f_{CLK}$  cycles (EN\_{FILT}) before shutting down. The shutdown delay prevents the device from prematurely entering Sleep mode due to noisy events like line or load transients.

#### **Power Good Function**

The ARG81880 has a Power Good (PG) output with a fixed delay of 256  $f_{CLK}$  cycles ( $t_{dPG}$ ) on its rising edge. This relatively short delay on the rising edge (122  $\mu s$  at 2.1 MHz) allows the ARG81880 to complete soft-start, so  $V_{OUT}$  can achieve 100% regulation before PG transitions high. The benefit of the rising edge delay on PG is shown in Figure 10. The PG output is an open-drain output, so an external pull-up resistor must be used, as shown in the applications schematic. If Power Good is not used, the PG pin can be left floating or grounded.

Basically, Power Good is high if  $V_{OUT}$  is within regulation and low if  $V_{OUT}$  is out of regulation. The control algorithm in the ARG81880 allows the Power Good function to have a much tighter window of detection than competing regulators: 98% to 107% of the desired value. The Power Good function incorporates hysteresis ( $V_{OUT(UV,HYS)}$ ),  $V_{OUT(OV,HYS)}$ ) to prevent chattering and deglitch filtering ( $t_{dUV}$ ,  $t_{dOV}$ ) to eliminate false triggering. The following flow chart shows the operation of Power Good.

Figure 13: Power Good Operation

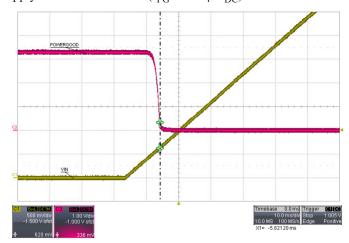

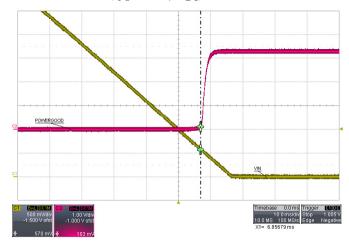

At power-up, Power Good must be initialized (set to a logic low) when  $V_{IN}$  is relatively low. The following figure shows  $V_{IN}$  ramping up and PG being set to a logic low when  $V_{IN}$  is only 620 mV. Most competing regulators cannot initialize PG at this level of  $V_{IN}$ . For this test, PG is pulled up by an external 3.3 V supply via a 10  $k\Omega$  resistor ( $I_{PG}=330~\mu A_{DC}$ ).

Figure 14: Power Good is fully initialized at  $V_{IN}$  = 620 mV during power-up, 10 ms/DIV.

At power-down, Power Good should be held in the logic low state as long as possible. The following figure shows  $V_{IN}$  ramping down and PG being held low until  $V_{IN}$  is only 570 mV. Most competing regulators cannot maintain PG low down to this level of  $V_{IN}.$  For this test, PG is pulled up by an external 3.3 V supply via a 10 k $\Omega$  resistor ( $I_{PG}$  = 330  $\mu A_{DC}$ ).

Figure 15: Power Good maintains a low state until  $V_{\text{IN}}$  = 570 mV at power-down, 10 ms/DIV.

#### **Undervoltage Lockout (UVLO)**

An undervoltage lockout (UVLO) comparator monitors the voltage at the VIN pin and keeps the regulator disabled if the voltage is below the lockout threshold ( $V_{IN(START)}$ ). The UVLO comparator incorporates enough hysteresis, about 200 mV, to prevent on/off cycling of the regulator due to  $I_R$  drops in the  $V_{IN}$  path during heavy loading or during startup.

#### **Pulse-by-Pulse Current Limit**

The current in the high-side MOSFET is monitored on a cycle-by-cycle basis. If the high-side current exceeds  $I_{LIM(HS)}$ , the high-side MOSFET is turned off. This protects the high-side MOSFET from excessive current, overheating, and possible damage. The high-side current limit scales with the load current selection as shown in Table 2.

In a synchronous regulator, the inductor current is allowed to go negative. If the negative current in the low-side MOSFET exceeds  $I_{LIM(LS)}$ , the low-side MOSFET is turned off. This protects the low-side MOSFET from excessive current, overheating, and possible damage. The low-side current limit is fixed at approximately 700 mA ( $I_{LIM(LS)}$ ).

## Output Short-Circuit Protection and Hiccup Mode

An overcurrent (OC) counter and hiccup mode logic protect the regulator when its output is shorted to ground or when the load is too high.

For the first 512 of 4096  $f_{CLK}$  cycles during soft-start, the OC counter and hiccup mode are disabled. However, pulse-by-pulse current limit is always enabled. This approach gives high priority to startup but still protects the regulator. After 512  $f_{CLK}$  cycles, the OC counter and the hiccup mode are enabled. At this instant, given

the level of V<sub>OUT</sub>, the regulator will allow an additional fixed number of overcurrent counts before activating hiccup mode:

- If  $V_{OUT}$  < 25%, allow only 30 consecutive OC counts, or

- If V<sub>OUT</sub> > 25%, allow 120 consecutive OC counts.

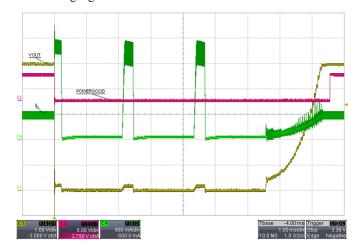

If the OC counter reaches its limit, a hiccup latch is set and PWM switching is suspended for 4096  $f_{CLK}$  cycles (1.95 ms,  $t_{HIC(REC)}$ ). This provides time for the regulator to cool down. After the hiccup timer expires, the hiccup latch is cleared, and a new soft-start routine begins, as described earlier. If the short circuit at the regulator output remains, another hiccup cycle will occur as explained previously. Hiccup cycles repeat until the short circuit is removed or the regulator is disabled. If the short circuit is removed and the 4096  $f_{CLK}$  recovery time expires, the regulator will soft-start normally and the output voltage will automatically recover to the target level. Hiccup mode operation and recovery are shown in the following figure.

Figure 16: Output Short Circuit Transient and Recovery

#### **SW Pin Protection**

Unlike most regulators, the ARG81880 protects itself even when the SW pin is shorted to ground.

If the SW pin is shorted to ground, there will be a very high current in the high-side MOSFET when it is turned on. When the ARG81880 detects this unusually high current ( $I_{LIM(SC)}$ ), it instantly turns off the high-side MOSFET. If the regulator detects two consecutive instances where the current exceeds  $I_{LIM(SC)}$ , it will set the hiccup mode latch and stop switching. After 4096  $f_{CLK}$  cycles ( $t_{HIC(REC)}$ ), the regulator will attempt to restart. If the SW pin remains shorted to ground, another hiccup will occur. If the short to ground is removed, the ARG81880 will automatically recover. Unlike other hiccup mode protections, the SW pin protection does not observe the hiccup mode enable delay of 512  $f_{CLK}$  cycles ( $t_{HIC(EN)}$ ).

Figure 17: SW short-to-ground protection and recovery hiccup mode after two detections.

Figure 18: Each of the SW-to-ground transients shown in the previous figure is actually 2 events.

#### **BOOT Pin Protections**

The ARG81880 monitors the voltage across the BOOT capacitor to detect if the capacitor is missing or short-circuited.

If the BOOT capacitor is missing, the BOOT voltage appears adequate due to stray capacitance between the BOOT and the SW pins (10 to 20 pF). However, there is not enough charge to enhance the high-side MOSFET. Therefore, at the start of every PWM cycle, the BOOT voltage drops the instant the gate driver attempts to turn on the high-side MOSFET. This causes BOOT  $_{\rm UV}$  to occur and the high-side MOSFET is turned off (it never actually turns on). The regulator is unable to raise  $V_{\rm OUT}$  so Power Good remains low. The ARG81880 repeats this process until the BOOT capacitor is replaced.

If the BOOT capacitor is short-circuited, BOOT $_{\rm UV}$  persists during soft-start and the BOOT charger is purposely shut down after only 64 f $_{\rm CLK}$  cycles (t $_{\rm BOOT(SC)}$ ). After the Hiccup Enable Delay (512 f $_{\rm CLK}$  cycles, t $_{\rm HIC(EN)}$ ) plus the minimum OC count (30 f $_{\rm SW}$  cycles or 240 f $_{\rm CLK}$  cycles), the regulator will set the hiccup latch. After waiting 4096 f $_{\rm CLK}$  cycles (t $_{\rm HIC(REC)}$ ), the regulator will clear the hiccup latch and attempt another soft-start. The regulator will continue in hiccup mode until the short circuit is removed from the BOOT capacitor.

#### Overvoltage Protection (OVP)

The ARG81880 provides a fundamental level of overvoltage protection. If  $V_{OUT}$  is above the overvoltage threshold (107%,  $V_{OUT(OV,H)}$ ) for longer than the deglitch time (128  $f_{CLK}$  cycles,  $t_{dOV}$ ), the high-side MOSFET is shut off. Also, to correct the overvoltage condition, the low-side MOSFET is turned on and sinks current from  $V_{OUT}$ . Each PWM cycle, the low-side MOSFET is allowed to be on until the inductor current reaches the low-side MOSFET negative current limit (700 mA,  $I_{LIM(LS)}$ ).

#### **Thermal Protection**

The ARG81880 protects itself from overheating by means of an internal thermal monitoring circuit. If the junction temperature exceeds the thermal shutdown threshold ( $T_{TSD}$ , 175°C typical), both high-side and low-side MOSFETs are shut off, the BOOT charger is shut down, and the internal control circuits are reset. The regulator automatically restarts when the junction temperature decreases more than the thermal shutdown hysteresis ( $T_{HYS}$ , 20°C typical).

50 V, 800 mA, 2.2 MHz, Synchronous Buck Regulator with Internal Compensation, Frequency Dithering, Adjustable Current Limit, Synchronization, and Power Good

#### Pin-to-Ground and Adjacent Pin Short Protections

The ARG81880 is designed to satisfy the most demanding automotive applications. For example, the device is designed to withstand a short circuit to ground at each pin without suffering damage. In addition, care was taken when defining the device pin-out to optimize protection against adjacent pin-to-pin short circuits. For example, logic pins and high-voltage pins are separated as much as possible. Inevitably, some low voltage pins are located adjacent to high voltage pins, but in these instances the low voltage pins are designed to withstand unusually high voltages—with clamps and/or series input resistance to prevent damage to the device.

Table 6 is a comprehensive summary of all fault conditions and the response of the ARG81880 in each case.

**Table 6: Summary Of Fault Mode Operation**

| Fault Condition                                      | Response To Fault                                                                                                                                                                                                                                                                             | V <sub>OUT</sub>                             | Boot<br>Regulator                       | PG                                                                                            | Latched Fault? | Reset Method                                                                 |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------|

| V <sub>OUT</sub> overvoltage (OV)                    | If OV exists for t > t <sub>dOV</sub> , stop PWM switching, turn on the low-side FET, and set PG low. Turn off the low-side FET if it exceeds its current limit.                                                                                                                              | V <sub>OUT</sub> ><br>V <sub>OUT(OV,H)</sub> | Off when<br>MOSFETs are<br>tristated    | Low if OV for t > t <sub>dOV</sub>                                                            | No             | Remove the cause of OV                                                       |

| V <sub>OUT</sub> undervoltage (UV)                   | If UV exists for t > t <sub>dUV</sub> , set PG low.                                                                                                                                                                                                                                           | V <sub>OUT</sub> <<br>V <sub>OUT(UV,L)</sub> | On                                      | Low if UV for t > t <sub>dUV</sub>                                                            | No             | Check V <sub>OUT</sub> for overload or a short to ground.                    |

| V <sub>OUT</sub> pin open circuit                    | If $V_{OUT}$ is open circuit its voltage will be near 0 V. If $V_{OUT}$ is this low, the frequency is limited to $f_{OSC}/8$ and the duty cycle is limited to 1/8.                                                                                                                            | 0 V to V <sub>IN</sub> /8                    | On                                      | Low if V <sub>OUT</sub> < V <sub>OUT(UV,L)</sub>                                              | No             | Connect the V <sub>OUT</sub> pin                                             |

| V <sub>OUT</sub> overcurrent (OC)                    | The high-side MOSFET is shut off when the current is higher than the pulse-by-pulse current limit. Hiccup mode after the Hiccup Enable Delay (512 f <sub>CLK</sub> cycles) and too many consecutive OC counts, 30 or 120, depending on the level of V <sub>OUT</sub> .                        | Depends on<br>V <sub>IN</sub> and load       | On                                      | Low if V <sub>OUT</sub> < V <sub>OUT(UV,L)</sub>                                              | No             | Reduce the load                                                              |

| V <sub>OUT</sub> short to ground                     | High-side MOSFET shuts off when the current is higher than the pulse-by-pulse limit (I <sub>LIM(HS)</sub> ). Enters hiccup mode after 30 consecutive OC counts.                                                                                                                               | 0 V                                          | On                                      | Low                                                                                           | No             | Remove the short circuit at V <sub>OUT</sub>                                 |

| SW pin open circuit                                  | The regulator will be unable to charge the BOOT capacitor so the high-side FET will not switch.                                                                                                                                                                                               | 0 V                                          | On                                      | Low                                                                                           | No             | Connect the SW pin                                                           |

| SW pin short to ground                               | High-side MOSFET shuts off when the current is higher than the SW short-circuit limit (I <sub>LIM(SC)</sub> ). Immediately enters Hiccup mode after 2 consecutive detections—does not wait for the Hiccup Enable delay (t <sub>HIC(EN)</sub> ).                                               | 0 V                                          | On                                      | Low                                                                                           | No             | Remove the short circuit at SW                                               |

| BOOT pin open circuit                                | The voltage at the BOOT pin appear OK due to stray capacitance (10 to 20 pF). However, there is not enough charge to enhance the upper FET, so the BOOT voltage falls below the BOOT <sub>UV</sub> threshold at the start of every PWM cycle.                                                 | 0 V                                          | On                                      | Low                                                                                           | No             | Connect the BOOT pin                                                         |

| BOOT pin short to ground                             | The BOOT regulator cannot charge $C_{BOOT}$ . The BOOT regulator remains on for only $64\ f_{CLK}$ cycles $(t_{BOOT(SC)})$ . Hiccup mode occurs after 752 $f_{CLK}$ cycles $(t_{HIC(EN)} + 30/f_{SW})$ , where $f_{SW} = f_{CLK}/8$ ).                                                        | 0 V                                          | Off after<br>64 f <sub>CLK</sub> cycles | Low                                                                                           | No             | Remove the short circuit from BOOT to ground                                 |

| BOOT pin short to SW                                 | The low-side MOSFET turns on as part of the BOOT charging routine but $C_{BOOT}$ cannot charge. The BOOT regulator remains on for only 64 $f_{CLK}$ cycles ( $t_{BOOT(SC)}$ ). Hiccup mode occurs after 752 $f_{CLK}$ cycles ( $t_{HIC(EN)}$ + 30/ $f_{SW}$ , where $f_{SW}$ = $f_{CLK}/8$ ). | 0 V                                          | Off after<br>64 f <sub>CLK</sub> cycles | Low                                                                                           | No             | Remove the short circuit from BOOT to SW                                     |

| EN/UV pin short to ground                            | The EN/UV voltage is at 0V so the regulator is disabled.                                                                                                                                                                                                                                      | 0V                                           | Off when the IC is disabled             | Low                                                                                           | No             | Remove the short circuit from EN/UV to ground                                |

| EN/UV pin open circuit                               | The EN/UV voltage is pulled low by an internal current sink. The pin is stuck at 0 V and the regulator is disabled.                                                                                                                                                                           | 0 V                                          | Off when the IC is disabled             | Low                                                                                           | No             | Connect the EN/<br>UV pin                                                    |

| I <sub>LIM</sub> /SYNC <sub>IN</sub> short to ground | This is a valid state for this pin resulting in current limits to support 640 mA.                                                                                                                                                                                                             | Set by V <sub>SET</sub> pin status           | On                                      | $\begin{array}{c} \text{High if V}_{\text{OUT}} > \\ \text{V}_{\text{OUT(UV,H)}} \end{array}$ | No             | Remove the short circuit from I <sub>LIM</sub> /SYNC <sub>IN</sub> to ground |

| I <sub>LIM</sub> /SYNC <sub>IN</sub> open circuit    | This is a valid state for this pin resulting in current limits to support 800mA.                                                                                                                                                                                                              | Set by VSET pin status                       | On                                      | High if V <sub>OUT</sub> > V <sub>OUT(UV,H)</sub>                                             | No             | Connect the I <sub>LIM</sub> /<br>SYNC <sub>IN</sub> pin                     |

Continued on next page...

# 50 V, 800 mA, 2.2 MHz, Synchronous Buck Regulator with Internal Compensation, Frequency Dithering, Adjustable Current Limit, Synchronization, and Power Good

**Table 6: Summary Of Fault Mode Operation (continued)**

| Fault Condition                  | Response To Fault                                                                              | V <sub>OUT</sub>                   | Boot<br>Regulator                    | PG                                                | Latched Fault? | Reset Method                                                                   |

|----------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------|---------------------------------------------------|----------------|--------------------------------------------------------------------------------|

| V <sub>SET</sub> short to ground | This is a valid state for this pin resulting in an output voltage of 3.3 V.                    | 3.3 V                              | On                                   | High if V <sub>OUT</sub> > V <sub>OUT(UV,H)</sub> | No             | Remove the short circuit from V <sub>SET</sub> to ground                       |

| V <sub>SET</sub> open circuit    | This is a valid state for this pin resulting in an output voltage of 5.0 V.                    | 5.0 V                              | On                                   | High if V <sub>OUT</sub> > V <sub>OUT(UV,H)</sub> | No             | Connect the V <sub>SET</sub> pin                                               |

| PG open circuit                  | PG pulled high via external pull-up resistor.                                                  | Normal,<br>Set by V <sub>SET</sub> | On                                   | Stuck high                                        | No             | Connect the PG pin                                                             |

| PG short to ground               | PG stuck at 0 V.                                                                               | Normal,<br>Set by V <sub>SET</sub> | On                                   | Stuck low                                         | No             | Remove the short circuit from PG to ground                                     |

| PG short to SW                   | PG unable to show correct state. PG will follow SW, toggling between 0 V and V <sub>IN</sub> . | Normal,<br>Set by V <sub>SET</sub> | On                                   | Follows SW voltage                                | No             | Remove the short circuit from PG to SW                                         |

| Thermal Shutdown (TSD)           | The regulator will shut down when $T_J > T_{TSD}$ .                                            | 0 V                                | Off when<br>MOSFETs are<br>tristated | Low                                               | No             | Automatic, resets<br>after T <sub>J</sub> < T <sub>TSD</sub> -T <sub>HYS</sub> |

50 V, 800 mA, 2.2 MHz, Synchronous Buck Regulator with Internal Compensation, Frequency Dithering, Adjustable Current Limit, Synchronization, and Power Good

#### **COMPONENT SELECTIONS**

Table 7: Recommended Component Values for a 12  $\rm V_{IN}$  System

| V <sub>OUT</sub> R <sub>SET</sub> |        | Recommended Power Components |        |                           |        |                           |        |

|-----------------------------------|--------|------------------------------|--------|---------------------------|--------|---------------------------|--------|

| (V) ±1%                           | ±1%    | I <sub>OUT</sub> = 8         | 300 mA | I <sub>OUT</sub> = 640 mA |        | I <sub>OUT</sub> = 480 mA |        |

| 5.0                               | OPEN   | 8.2 µH                       | 4.7 µF | 10 μH                     | 3.3 µF | 12 µH                     | 2.2 µF |

| 3.3                               | GND    | 6.8 µH                       | 6.8 µF | 8.2 µH                    | 5.6 µF | 10 μH                     | 3.3 µF |

| 2.5                               | 15.4kΩ | 5.6 µH                       | 8.2 µF | 6.8 µH                    | 6.8 µF | 8.2 µH                    | 5.6 µF |

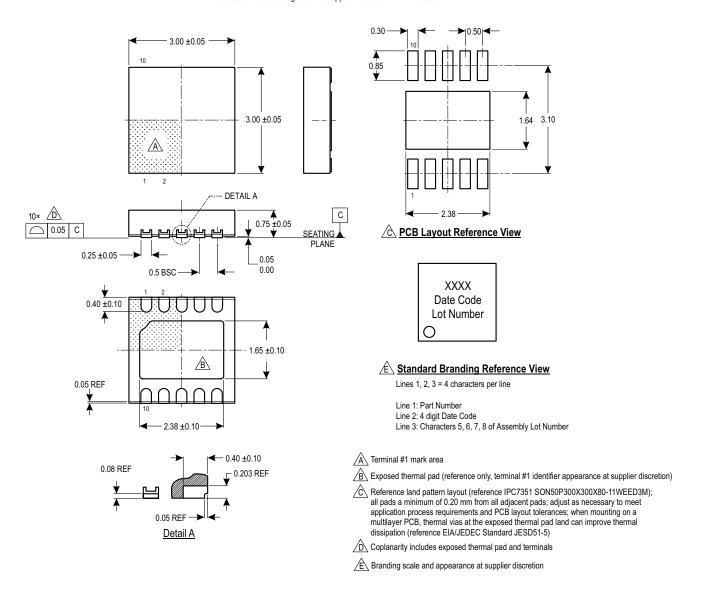

#### PACKAGE OUTLINE DRAWING

### For Reference Only – Not for Tooling Use (Reference JEDEC MO-229)

(Reference JEDEC MO-229)

Dimensions in millimeters – NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

Figure 19: Package EJ, Wettable Flank DFN-10 with Exposed Thermal Pad

# 50 V, 800 mA, 2.2 MHz, Synchronous Buck Regulator with Internal Compensation, Frequency Dithering, Adjustable Current Limit, Synchronization, and Power Good

#### **Revision History**

| Number | Date           | Description                                      |  |  |

|--------|----------------|--------------------------------------------------|--|--|

| _      | March 20, 2018 | Initial release                                  |  |  |

| 1      | June 20, 2018  | Corrected Thermal Characteristics table (page 2) |  |  |

Copyright ©2018, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com