# Fractional-N Clock Multiplier

#### **Features**

- Fractional clock multiplier and jitter reduction using hybrid analog/digital PLL

- Generates low-jitter 6–75 MHz clock (CLK\_OUT), synchronized to a 50 Hz–30 MHz low-quality or intermittent frequency reference (CLK\_IN)

- · Flexible timing reference source

- External clock, external crystal, or built-in oscillator

- · High resolution PLL ratio (1 PPM)

- 18 ps<sub>RMS</sub> period jitter (external timing reference),

18 ps<sub>RMS</sub> period jitter (oscillator reference)

- · Glitchless clock output generated from intermittent input

- I<sup>2</sup>C/SPI control port

- · Configurable auxiliary clock/status output

- · Minimal board space required

- No external analog loop-filter components

- Pin-to-pin, register map, and control compatible with CS2100 and CS2300

- Single-supply operation at 1.8 V or 3.3 V

### **Applications**

- · Automotive audio systems

- · Digital audio systems

- · Network and USB audio interfaces

- · IoT sensor and transducer systems

- · Embedded systems

### **General Description**

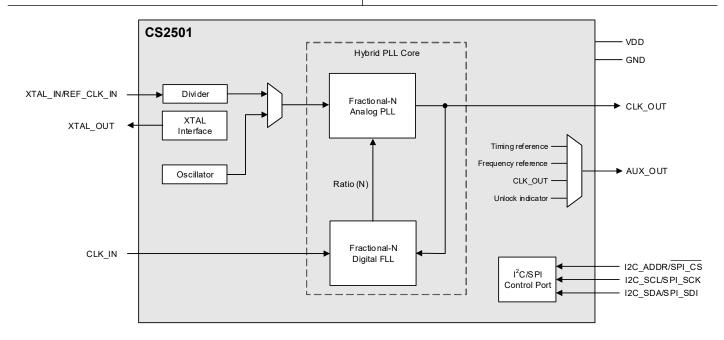

The CS2501 is a system-clocking device incorporating a programmable phase-locked loop (PLL). The hybrid analog/ digital PLL architecture comprises a delta-sigma fractional-N analog PLL and a digital frequency-locked loop (FLL). The CS2501 enables clock generation from a stable timing reference clock. The device can generate low-jitter clocks from a noisy clock reference at frequencies as low as 50 Hz. An internal oscillator can provide the timing reference clock, enabling a reduction in external component requirements. The CS2501 can be configured using a control interface supporting I<sup>2</sup>C and SPI modes of operation.

The CS2501 can be powered from a single 1.8 V or 3.3 V supply. The device combines high performance with low power consumption.

The CS2501 is available in commercial-grade 10-pin TSSOP package for operation from –40°C to +85°C. The device is also available in the AEC-Q100-qualified grade-2 package for operation from –40°C to +105°C. See Section 12 for ordering information.

## **Table of Contents**

| 1 Pin Assignments and Descriptions                                | 4        |

|-------------------------------------------------------------------|----------|

| 1.1 TSSOP Pin Assignments (Top View, Through Package)             |          |

| 1.2 Pin Descriptions                                              | 4        |

| 1.3 Electrostatic Discharge (ESD) Protection Circuitry            | 5        |

| 2 Typical Connections                                             |          |

| 3 Characteristics and Specifications                              |          |

| Table 3-1. Recommended Operating Conditions                       |          |

| Table 3-2. Absolute Maximum Ratings                               | 7        |

| Table 3-3. DC Electrical Characteristics                          | /        |

| Table 3-5. Switching Specifications—I <sup>2</sup> C Control Port | 0        |

| Table 3-6. Switching Specifications—SPI Control Port              | . 10     |

| 4 Functional Description                                          | 11       |

| 4.1 Device Architecture                                           | 11       |

| 4.2 Timing Reference Configuration                                | 11       |

| 4.3 Hybrid PLL Configuration                                      | 12       |

| 4.4 Frequency Reference Configuration                             | 14       |

| 4.6 Auxiliary Output                                              | 17<br>18 |

| 4.7 I <sup>2</sup> C/SPI Control Port                             | 18       |

| 4.8 Device ID                                                     | 21       |

| 5 Applications                                                    |          |

| 5.1 Crystal Component Selection                                   | 22       |

| 6 Register Quick Reference                                        |          |

| 6.1 CONFIG                                                        |          |

| 7 Register Descriptions                                           |          |

| 7.1 CONFIG                                                        | 26       |

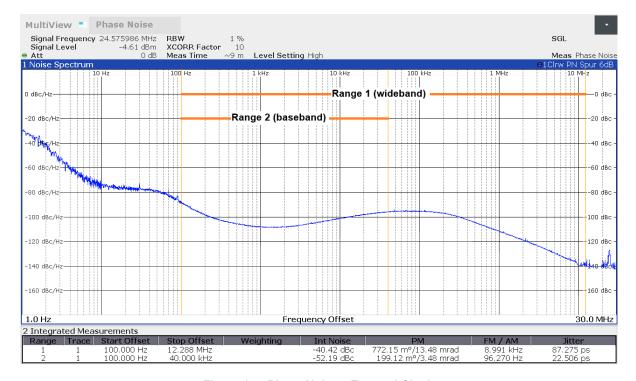

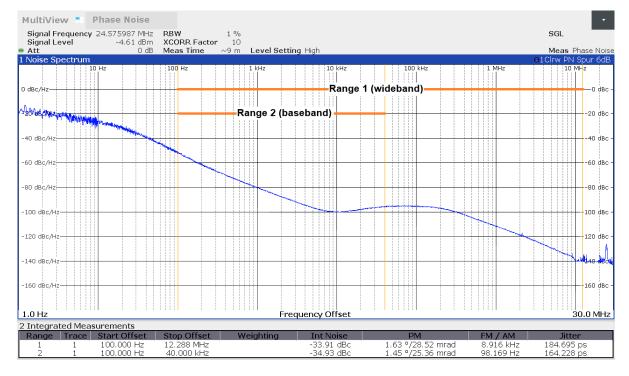

| 8 Performance Plots                                               |          |

| 8.1 Jitter Performance                                            | 31       |

| 8.2 Phase Noise                                                   | 33       |

|                                                                   |          |

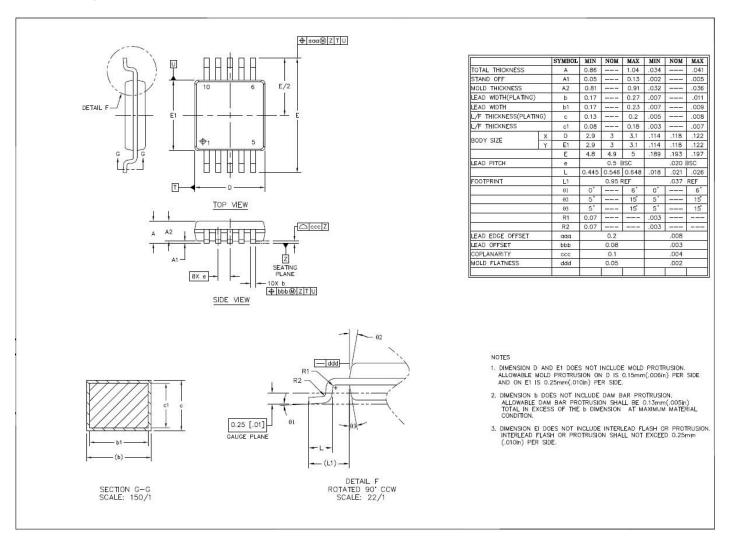

| 10 Package Dimensions                                             |          |

| 11 Package Marking                                                |          |

| 12 Ordering Information                                           |          |

| 13 References                                                     | . 35     |

| 14 Revision History                                               | . 35     |

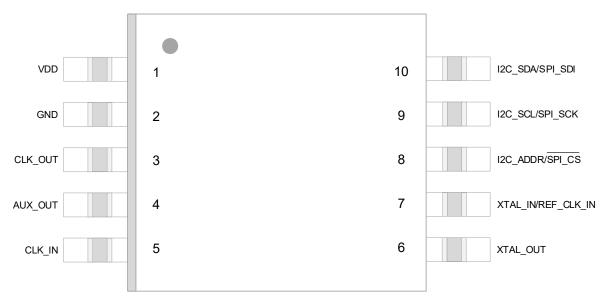

# 1 Pin Assignments and Descriptions

These sections show pin assignments and describe pin functions.

# 1.1 TSSOP Pin Assignments (Top View, Through Package)

Figure 1-1. TSSOP 10-Pin Diagram (Top View, Through-Package)

Note the CS2501 is pin-to-pin compatible with CS2100 and CS2300.

# 1.2 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin Name           | Pin# | Power<br>Supply | I/O | Description                                                                                                                                                                                            |

|--------------------|------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                | 1    | _               | _   | Power Supply. 3.3 V/1.8 V supply for the digital and analog blocks.                                                                                                                                    |

| GND                | 2    | _               | _   | Ground.                                                                                                                                                                                                |

| CLK_OUT            | 3    | VDD             | 0   | Clock Output. PLL clock output.                                                                                                                                                                        |

| AUX_OUT            | 4    | VDD             | 0   | Auxiliary Output. Configurable clock output or status output.                                                                                                                                          |

| CLK_IN             | 5    | VDD             | I   | Clock Input. Frequency reference input for the digital FLL.                                                                                                                                            |

| XTAL_OUT           | 6    | VDD             | 0   | Crystal Connection. Output for an external crystal.  Connect to GND for internal oscillator reference clock. (A capacitor connection is also supported for legacy PCB designs, as shown in Section 2.) |

| XTAL_IN/REF_CLK_IN | 7    | VDD             | I   | Crystal Connection. Input for an external crystal.  Reference Clock. External low-jitter timing reference clock input.  Connect to GND for internal oscillator reference clock.                        |

| I2C_ADDR/SPI_CS    | 8    | VDD             | I   | I <sup>2</sup> C Control-Port Address. Chip address input for the I <sup>2</sup> C interface.  SPI Control-Port Chip Select. Active-low chip select input for the SPI interface.                       |

| I2C_SCL/SPI_SCK    | 9    | VDD             | I   | I <sup>2</sup> C Control-Port Clock. Clock input for the I <sup>2</sup> C interface.  SPI Control-Port Clock. Clock input for the SPI interface.                                                       |

| I2C_SDA/SPI_SDI    | 10   | VDD             | I/O | I <sup>2</sup> C Control-Port Data. Data input/output for the I <sup>2</sup> C interface. SPI Control-Port Serial Data In. SPI data input.                                                             |

# 1.3 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS2501 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to current JEDEC ESD standards.

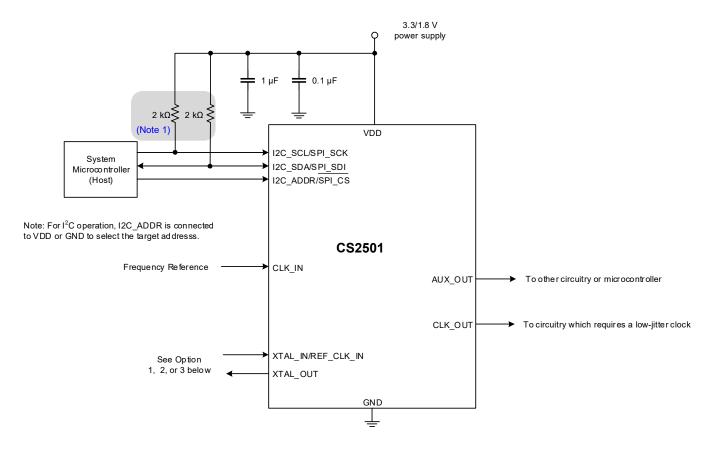

# 2 Typical Connections

Figure 2-1. Typical Connection Diagram

Note referenced in the typical connection diagram:

1. The pull-up resistors are required only for  $I^2C$  operation. The diagram shows 2  $k\Omega$  pull-up, but higher impedance can be supported depending on clock speed and bus capacitance.

# 3 Characteristics and Specifications

#### **Table 3-1. Recommended Operating Conditions**

Test Conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground.

| Par                 | ameters          | Symbol              | Min             | Тур | Max  | Units |

|---------------------|------------------|---------------------|-----------------|-----|------|-------|

| DC power supply     | Nominal 3.3 V    | VDD                 | 3.1             | 3.3 | 3.5  | V     |

|                     | Nominal 1.8 V    |                     | 1.71            | 1.8 | 1.89 | V     |

| Supply ramp up/down |                  | t <sub>PWR_UD</sub> | 0.01            | _   | 10   | ms    |

| Ambient temperature | Commercial Grade | TA                  | -40             | _   | 85   | °C    |

|                     | AEC-Q100 Grade 2 |                     | <del>-4</del> 0 | _   | 105  | °C    |

#### **Table 3-2. Absolute Maximum Ratings**

Test Conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground.

| Parameters                                       | Symbol            | Min  | Max       | Units |

|--------------------------------------------------|-------------------|------|-----------|-------|

| DC power supply                                  | VDD               | -0.3 | 4.32      | V     |

| External voltage applied to digital input/output | V <sub>INDI</sub> | -0.3 | VDD + 0.3 | V     |

| Input current                                    | I <sub>in</sub>   | _    | ±10       | mA    |

| Ambient temperature                              | T <sub>A</sub>    | -55  | 125       | °C    |

| Storage temperature                              | T <sub>STG</sub>  | -65  | 150       | °C    |

#### Table 3-3. DC Electrical Characteristics

Test Conditions (unless specified otherwise): T<sub>A</sub> = 25°C; timing reference = 12 MHz (external clock or crystal).

| Parameters                                    | Symbol           | Min        | Тур          | Max        | Units |

|-----------------------------------------------|------------------|------------|--------------|------------|-------|

| Power supply current—unloaded <sup>1</sup>    | I <sub>VDD</sub> | _          | 4            | _          | mA    |

| Input leakage current (per pin)               | I <sub>IN</sub>  | _          | _            | ±10        | μA    |

| Input capacitance (per pin)                   | I <sub>C</sub>   | _          | _            | 5          | pF    |

| High-level input voltage                      | V <sub>IH</sub>  | 0.70 × VDD | _            | _          | V     |

| Low-level input voltage                       | V <sub>IL</sub>  | _          | _            | 0.30 × VDD | V     |

| High-level output voltage                     | V <sub>OH</sub>  | 0.90 × VDD | _            | _          | V     |

| Low-level output voltage                      | V <sub>OL</sub>  | _          | _            | 0.10 × VDD | V     |

| VDD power-on reset (POR) threshold VDD rising |                  | 1.40       | _            | 1.59       | V     |

| VDD falling                                   |                  | 1.38       | <del>_</del> | 1.55       | V     |

| VDD power-on reset duration <sup>2</sup>      | t <sub>POR</sub> | 100        | _            | _          | ms    |

<sup>1.</sup>To calculate the additional current consumption due to loading (per output pin), multiply clock output frequency by load capacitance (C<sub>L</sub>) and power supply voltage (VDD).

<sup>2.</sup>To trigger a power-on reset, VDD must be held below the reset threshold for longer than this duration. Note that VDD interruption shorter than this duration may result in incorrect device behavior.

#### **Table 3-4. AC Electrical Characteristics**

Test Conditions (unless specified otherwise):  $T_A = -40^{\circ}\text{C}$  to 85°C (commercial grade);  $T_A = -40^{\circ}\text{C}$  to 105°C (AEC-Q100 grade-2); Load capacitance (C<sub>L</sub>) = 15 pF.

| Parameters                                                            | Symbol                          | Min   | Тур  | Max                 | Units             |

|-----------------------------------------------------------------------|---------------------------------|-------|------|---------------------|-------------------|

| Crystal frequency REF_CLK_IN_D                                        |                                 | 8     | _    | 18.75               | MHz               |

| REF_CLK_IN_C                                                          |                                 | 16    | _    | 37.50               | MHz               |

| REF_CLK_IN_C                                                          |                                 | 32    | _    | 50                  | MHz               |

| Crystal interface VDD = 3.3 V, XOSC_GEARn_3V3_E                       |                                 | _     | 13   | _                   | mS                |

| transconductance VDD = 3.3 V, XOSC_GEARn_3V3_[(T <sub>A</sub> = 25°C) | )RV = 1                         | _     | 26   | _                   | mS                |

| \( \) \( \)                                                           | = 1.8 V                         | _     | 43   |                     | mS                |

| Reference clock input frequency REF_CLK_IN_D                          |                                 | 8     | _    | 18.75               | MHz               |

| REF_CLK_IN_C                                                          |                                 | 16    | _    | 37.50               | MHz               |

| REF_CLK_IN_C                                                          |                                 | 32    | _    | 75                  | MHz               |

| Reference clock input duty cycle                                      | D <sub>REF_CLK_IN</sub>         | 45    | _    | 55                  | %                 |

| Clock input frequency                                                 | f <sub>CLK_IN</sub>             | 50    | _    | 30 ×10 <sup>6</sup> | Hz                |

| Clock input pulse width f <sub>CLK IN</sub> < f <sub>SYSCL</sub>      | ( / 96 [1] pw <sub>CLK IN</sub> | 2     | _    |                     | UI <sup>2</sup>   |

| f <sub>CLK_IN</sub> > f <sub>SYSCL</sub>                              | · / 96 [1]                      | 10    | _    | _                   | ns                |

| Clock skipping timeout                                                | t <sub>CS</sub>                 | 20    | _    | _                   | ms                |

| Clock skipping input frequency                                        | f <sub>CLK_SKIP</sub>           | 50    | _    | 80 ×10 <sup>3</sup> | Hz                |

| CLK_OUT frequency range                                               | f <sub>CLK_OUT</sub>            | 6     | _    | 75                  | MHz               |

| Clock output duty cycle measured at '                                 | VDD / 2 t <sub>OD</sub>         | 45    | 50   | 55                  | %                 |

| Clock output rise time 10% to 90%                                     | UIV.                            | _     | 1.8  | _                   | ns                |

| Clock output fall time 90% to 10%                                     | of VDD t <sub>OF</sub>          | _     | 1.8  | _                   | ns                |

| CLK_OUT period jitter 3,4 external timing re                          |                                 | _     | 18   | 25                  | ps <sub>RMS</sub> |

| internal oscillator re                                                | ference                         | _     | 18   | 25                  | ps <sub>RMS</sub> |

| CLK_OUT baseband TIE jitter 3,5 external timing re                    |                                 | _     | 21   | 70                  | ps <sub>RMS</sub> |

| internal oscillator re                                                | ference                         | _     | 170  | 350                 | ps <sub>RMS</sub> |

| CLK_OUT wideband TIE jitter 3,6 external timing re                    |                                 | _     | 90   | 160                 | ps <sub>RMS</sub> |

| internal oscillator re                                                | ference                         | _     | 200  | 380                 | ps <sub>RMS</sub> |

| PLL lock time f <sub>CLK IN</sub> < 2                                 | 200 kHz t <sub>LC</sub>         | _     | 100  | 200                 | UI <sup>7</sup>   |

| f <sub>CLK_IN</sub> ≥ 2                                               |                                 | _     | 1    | 3                   | ms                |

|                                                                       | solution —                      | _     | 1    | _                   | ppm               |

| high multip                                                           |                                 | _     | 244  | _                   | ppm               |

| , · · · · ·                                                           | at 25°C —                       | 11.76 | 12.0 | 12.24               | MHz               |

| , ,                                                                   | at 25°C —                       | _     | 90   | _                   | ppm/°C            |

|                                                                       | to 85°C —                       | -1.0  | _    | 0.8                 | %                 |

|                                                                       | 105°C                           | -1.3  |      | 0.8                 | %                 |

| Clock output frequency deviation CLK_IN stopped, holdover             | enabled —                       | _     | _    | 0.1                 | %                 |

<sup>1.</sup> The internal timing reference clock (SYSCLK) is derived from REF CLK IN (see Section 4.2).

<sup>2.</sup>UI (unit interval) corresponds to  $t_{SYSCLK}$  or 1 /  $f_{SYSCLK}$ .

<sup>3.</sup>REF\_CLK\_IN is a 12 MHz timing reference clock, with phase noise 20 dB lower than the output clock noise. The clock output frequency (f<sub>CLK\_OUT</sub>) is 24.576 MHz.

<sup>4.</sup> Sample size is 10000.

<sup>5.</sup> Using 3rd order 100 Hz–40 kHz bandpass filter as defined in AES-12id-2020 Section 3.4.2.

<sup>6.</sup> Using 3rd order 100 Hz high pass filter as defined in AES-12id-2020 Section 3.4.1.

<sup>7.</sup>UI (unit interval) corresponds to t<sub>CLK IN</sub> or 1 / f<sub>CLK IN</sub>.

<sup>8.</sup> The frequency accuracy of the PLL clock output is directly proportional to the accuracy of the clock input.

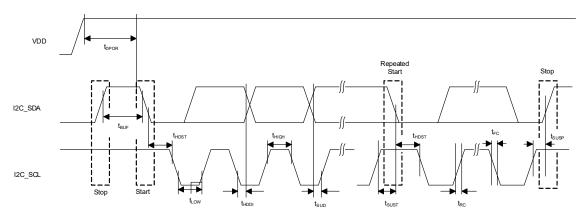

### Table 3-5. Switching Specifications—I<sup>2</sup>C Control Port

Test conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground; input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds, output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds;  $T_A = 25^{\circ}C$ .

| Parameters 1,2                                                                | Symbol            | Min | Max  | Units |

|-------------------------------------------------------------------------------|-------------------|-----|------|-------|

| SCL clock frequency                                                           | f <sub>SCL</sub>  | _   | 400  | kHz   |

| Clock low time                                                                | t <sub>LOW</sub>  | 4.7 | _    | μs    |

| Clock high time                                                               | t <sub>HIGH</sub> | 4.0 | _    | μs    |

| Start condition hold time (before first pulse clock)                          | t <sub>HDST</sub> | 4.0 | _    | μs    |

| Setup time for repeated start                                                 | tsust             | 4.7 | _    | μs    |

| Rise time of SCL and SDA f <sub>SCL</sub> ≤ 100 kHz                           | t <sub>RC</sub>   | _   | 1000 | ns    |

| 100 kHz < f <sub>SCL</sub> ≤ 400 kHz                                          |                   | _   | 300  | ns    |

| Fall time SCL and SDA $f_{SCL} \le 100 \text{ kHz}$                           | t <sub>FC</sub>   | _   | 300  | ns    |

| 100 kHz < f <sub>SCL</sub> ≤ 400 kHz                                          |                   | _   | 300  | ns    |

| Setup time for stop condition                                                 | tsusp             | 4.7 | _    | μs    |

| SDA setup time to SCL rising                                                  | t <sub>SUD</sub>  | 250 | _    | ns    |

| SDA input hold time from SCL falling                                          | t <sub>HDDI</sub> | 0   | _    | ns    |

| Bus free time between transmissions                                           | t <sub>BUF</sub>  | 4.7 | _    | μs    |

| Start-up time from power-up/software reset to control port ready <sup>3</sup> | t <sub>DPOR</sub> | _   | 200  | μs    |

- 1. The I<sup>2</sup>C control port uses a 8-bit register address and 8-bit data words.

- 2.I2C control-port timing.

3. Time from power-up measured from when VDD is within the recommended operating conditions (see Table 3-1).

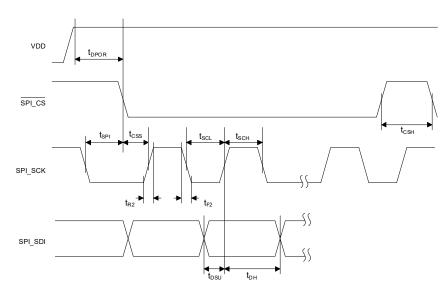

#### Table 3-6. Switching Specifications—SPI Control Port

Test conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground; input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds, output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds;  $T_A = 25^{\circ}C$ .

| Parameters 1,2                                                      | Symbol            | Min | Max | Units |

|---------------------------------------------------------------------|-------------------|-----|-----|-------|

| SCK clock frequency                                                 | f <sub>SCL</sub>  | _   | 6   | MHz   |

| SCK edge to CS falling <sup>3</sup>                                 | t <sub>SPI</sub>  | 500 | _   | ns    |

| CS high time between transmissions                                  | t <sub>CSH</sub>  | 1   | _   | μs    |

| CS falling to SCK rising edge                                       | t <sub>CSS</sub>  | 20  | _   | ns    |

| SCK pulse width low                                                 | t <sub>SCL</sub>  | 66  | _   | ns    |

| SCK pulse width high                                                | tsch              | 66  | _   | ns    |

| SDI to SCK rising setup time                                        | t <sub>DSU</sub>  | 40  | _   | ns    |

| SCK rising to SDI hold time <sup>4</sup>                            | t <sub>DH</sub>   | 15  | _   | ns    |

| Rise time of SCK and SDI <sup>5</sup>                               | t <sub>R2</sub>   | _   | 100 | ns    |

| Fall time of SCK and SDI <sup>5</sup>                               | t <sub>F2</sub>   | _   | 100 | ns    |

| Delay from supply voltage stable to control port ready <sup>6</sup> | t <sub>DPOR</sub> | _   | 200 | μs    |

<sup>1.</sup> The SPI control port uses a 7-bit register address and 8-bit data words.

- $3.t_{SPI}$  is only needed before first falling edge of  $\overline{CS}$  after power is applied;  $t_{SPI}$  is 0 all other times.

- 4. Data must be held for sufficient time to bridge the transition time of SCK.

- 5.For f<sub>SCK</sub> < 1 MHz.

- 6. The supply voltage is considered stable when VDD is within the recommended operating conditions (see Table 3-1).

<sup>2.</sup>SPI control-port timing.

# 4 Functional Description

### 4.1 Device Architecture

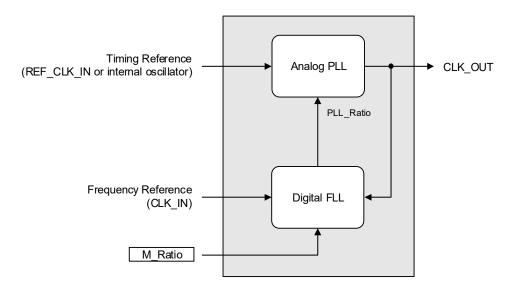

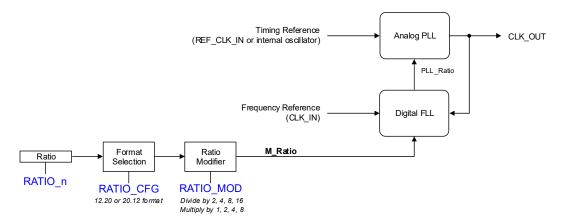

The CS2501 is a highly versatile clock generator. It combines an analog PLL and digital FLL to provide high-resolution clock multiplier capability. The delta-sigma architecture enables low-jitter clock generation across a wide range of fractional operating ratios; it also supports fast transitions between different ratios and output frequencies. Configurable bandwidth of the digital FLL enables optimized behavior under dynamic operating conditions.

The analog PLL generates the main clock output (CLK\_OUT), using the timing reference as its input. The timing reference is a stable low-jitter clock source, derived from the REF\_CLK\_IN input, external crystal, or the internal oscillator. The timing reference is used to ensure the time and phase stability of the PLL output. The PLL frequency ratio determines the multiplier ratio between the timing-reference input and the clock output.

The digital FLL provides input to the analog PLL to configure the frequency ratio. The digital FLL uses the frequency reference (CLK\_IN) as its input and generates the PLL frequency ratio as a control signal to the analog PLL. The capability of the digital FLL is enhanced by its configurable bandwidth; a wide bandwidth is used to achieve lock in a short time, while a narrow bandwidth is used to provide optimal jitter performance.

The user-defined frequency ratio is an input to the digital FLL and defines the CLK\_OUT:CLK\_IN frequency ratio. The FLL monitors the input and output clocks and controls the analog PLL frequency ratio to achieve the required CLK\_OUT frequency. The frequency ratio is dynamically controlled to maintain the required output ratio.

The hybrid analog/digital PLL is illustrated in Fig. 4-1. The user-defined multiplier ratio is defined by the *M\_Ratio* parameter.

Figure 4-1. Hybrid Analog/Digital PLL

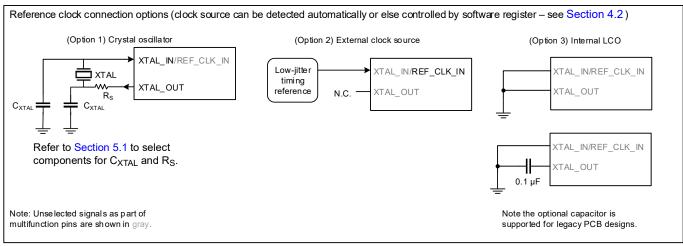

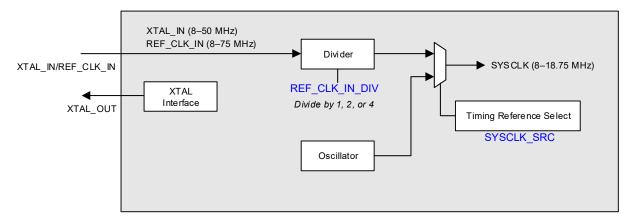

# 4.2 Timing Reference Configuration

The low-jitter timing reference is provided either by an external source (clock input or crystal), or by the internal oscillator. By default, the timing reference is selected automatically depending on the external pin connections, as shown Section 2. It is recommended to use SYSCLK\_SRC to select the internal or external source, as shown in Fig. 4-2.

The frequency range for the external timing reference is described in Table 3-4. Note that the supported frequency range differs depending on the applicable source.

The internal timing reference, SYSCLK, is derived from the selected timing source. A programmable divider is provided for the external timing reference; the divider must be configured using REF\_CLK\_IN\_DIV to bring the reference frequency within the valid SYSCLK range of 8–18.75 MHz.

The timing reference configuration is shown in Fig. 4-2.

Figure 4-2. Timing Reference Configuration

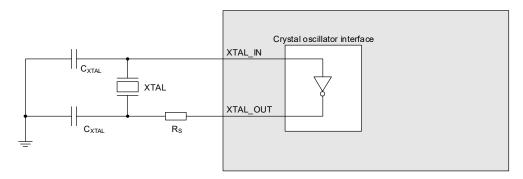

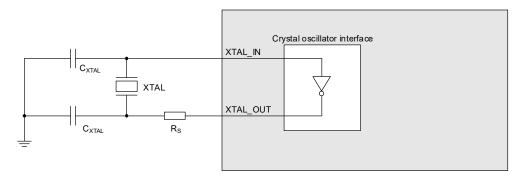

### 4.2.1 Crystal Oscillator

The crystal oscillator uses an external crystal to generate the timing reference. Load capacitors are connected to the crystal as shown in Fig. 4-3. A series resistor (R<sub>S</sub>) may also be required to configure the drive level for the selected crystal.

Figure 4-3. Crystal Oscillator Connection

Guidance on selecting a suitable crystal and associated components is provided in Section 5.1. The suitability of the external crystal is calculated as a function of the operating voltage (VDD) and the transconductance of the crystal interface, as defined in Table 3-4.

Under 3.3 V operating conditions, the transconductance is configurable using the register fields described below. This can be used to optimize the crystal oscillator for the selected external crystal.

- If REF\_CLK\_IN\_DIV = 10 (Divide by 1), the transconductance is configured using XOSC\_GEAR1\_3V3\_DRV

- If REF CLK IN DIV = 01 (Divide by 2), the transconductance is configured using XOSC GEAR2 3V3 DRV

- If REF\_CLK\_IN\_DIV = 00 (Divide by 4), the transconductance is configured using XOSC\_GEAR3\_3V3\_DRV

## 4.3 Hybrid PLL Configuration

The PLL is enabled and configured as described in the following sections.

#### 4.3.1 Enable and Lock Status

The PLL is enabled by setting PLL\_EN1 and PLL\_EN2 (both bits must be set in order to enable the PLL). Note there are no sequencing requirements—the bits may be set or cleared in any order.

**Note:** The device should be fully configured by writing to the applicable control registers before enabling the PLL. When changing the configuration, it is recommended to disable the PLL before updating the register fields; this ensures there is no unexpected transient behavior. See Section 4.7.3 for further details of configuration restrictions.

The PLL lock status is dependent on the clock inputs and the device configuration. Changes in the clock inputs or to the configuration registers can cause the PLL to lose lock. If the PLL loses lock, the quality of the clock output cannot be assured.

The PLL lock status is indicated using UNLOCK. This bit reads 1 if the PLL has unlocked since the last read of the field. This is a read-only bit and is automatically cleared after it has been read.

- If UNLOCK = 0, the PLL is locked and has remained locked since the last read.

- If UNLOCK = 1, one of two possible conditions applies—either (1) the PLL is unlocked, or (2) the PLL is locked, but

had previously unlocked since the last read. In this case, a second read of the UNLOCK bit is required in order to

confirm the current lock status—if the second read indicates 0, the PLL is locked; if the second read indicates 1, the

PLL is unlocked.

The lock status can be indicated on the auxiliary output pin as described in Section 4.6. The lock status can be used to automatically disable the clock outputs—see Section 4.5 for further details.

### 4.3.2 Ratio Configuration

The PLL is configured using a ratio that determines the output frequency as a function of the frequency reference, CLK\_IN.

• The output frequency is defined by the following equation:  $f_{CLK\_OUT} = f_{CLK\_IN} \times PLL$  Ratio For example, to generate a 24.576 MHz output from a 48 kHz frequency reference, a ratio of 512 is required.

The PLL ratio is a 32-bit value, configured using RATIO\_n. The ratio can be defined in high-resolution (12.20) or high-multiplication (20.12) format; the format is selected using RATIO CFG.

- In high-resolution (12.20) format, the 12 MSBs represent the integer portion of the ratio, and the remaining 20 bits represent the fractional portion. This format supports a maximum multiplication factor of ~4096, with a resolution of 0.954 ppm.

- In high-multiplication (20.12) format, the 20 MSBs represent the integer portion of the ratio, and the remaining 12 bits represent the fractional portion. This format supports a maximum multiplication factor of ~1,048,576, with a resolution of 244 ppm.

**Note:** If the desired ratio is less than 4096, the 12.20 format is recommended, to ensure the accuracy of the PLL output.

The PLL ratio is also configured using RATIO\_MOD, allowing additional multiplication/division factors to be applied to the RATIO\_n selection.

The ratio modifier can be used to simplify the selection of related frequency ratios, while using the same RATIO\_n value. It can also be used to support high multiplication ratios in 12.20 format (multiplying by 2, 4, or 8) or to enable greater precision in 20.12 format (dividing by 2, 4, 8, or 16).

Note that, regardless of the ratio format and the ratio modifier, the PLL ratio cannot exceed a multiplication factor of 1,048, 576 or a resolution of 0.954 PPM. If the configured parameters exceed these limits, the effective multiplication or resolution is truncated.

If the selected PLL ratio is invalid, the output clocks are disabled. Normal operation resumes when a valid ratio is detected (either due to register configuration or a change in CLK\_IN frequency).

The ratio configuration is illustrated in Fig. 4-4.

Figure 4-4. PLL Ratio Configuration

## 4.4 Frequency Reference Configuration

The frequency reference (CLK\_IN) is an input to the digital FLL, which is used to generate the dynamic ratio for the analog PLL. The digital FLL monitors the input and output clocks and controls the analog PLL frequency ratio to achieve the required CLK\_OUT frequency. The hybrid PLL/FLL architecture allows the low-jitter timing reference to be used to generate the clock output, while using a separate clock (CLK\_IN) as a frequency reference. The frequency range for CLK\_IN is defined in Table 3-4.

The CS2501 is tolerant of intermittent or unstable characteristics on the CLK\_IN frequency reference. The behavior of the device is configurable as described in the following sections.

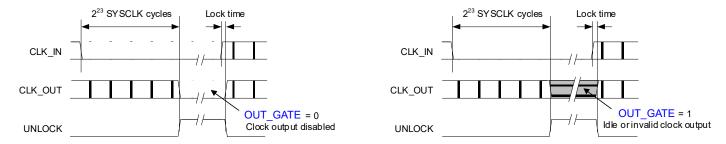

## 4.4.1 Clock Skipping and Intermittent CLK\_IN

The CLK\_IN signal is monitored to confirm the frequency reference is present. If the CLK\_IN signal is not present, the CS2501 responds in a number of ways, depending on the duration of the interruption and on other configurable options. The clock-skipping option allows short interruptions to CLK\_IN to be permitted without affecting the CLK\_OUT signal.

**Note:** Clock skipping is supported for software compatibility with earlier devices; for new designs, it is recommended to configure the CS2501 in Holdover Mode as described in Section 4.4.2.

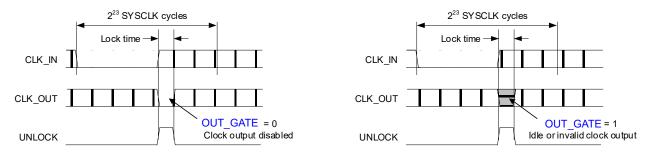

If CLK\_IN is interrupted for longer than 2<sup>23</sup> SYSCLK cycles (447–1048 ms), the PLL unlocks and the PLL output is no longer valid. The PLL remains unlocked indefinitely while CLK\_IN is interrupted. When CLK\_IN resumes, the PLL locks to CLK\_IN and the valid CLK\_OUT signal is restored.

If the PLL is not locked, the PLL output is invalid. To avoid spurious clock generation, the OUT\_GATE bit can be used to disable the clock output whenever the PLL is not locked. If OUT\_GATE = 0, the clock output is disabled whenever the PLL is not locked. See Section 4.5 for other options supported when the PLL is unlocked.

**Note:** If the clock output is disabled as a result of the PLL lock status, the CS2501 controls the CLK\_OUT signal to ensure there is no partial clock period—the output is disabled at the end of a complete clock period.

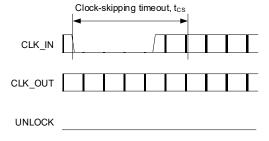

The CLK\_IN interruption longer than 223 SYSCLK cycles is illustrated in Fig. 4-5.

Figure 4-5. CLK\_IN Interruption > 223 SYSCLK Cycles

If CLK\_IN is interrupted for a period shorter than 2<sup>23</sup> SYSCLK cycles, the PLL remains locked for the duration of the interruption. When CLK\_IN resumes, the PLL unlocks temporarily and relocks to CLK\_IN. Note the PLL output is not valid for the period while the PLL is unlocked; the clock output while the PLL is unlocked depends on OUT GATE.

The CLK\_IN interruption shorter than 2<sup>23</sup> SYSCLK cycles is illustrated in Fig. 4-6.

Figure 4-6. CLK IN Interruption < 223 SYSCLK Cycles

The clock-skipping feature allows the CS2501 to tolerate short interruptions to CLK\_IN without causing the PLL to unlock. By maintaining the PLL lock, a valid CLK\_OUT signal can be generated without any glitch or interruption.

Clock skipping is enabled by setting CLK\_IN\_SKIP\_EN. If clock skipping is enabled and CLK\_IN is interrupted for a period shorter than the timeout period (typically ~20 ms), the PLL remains locked and resynchronizes to CLK\_IN.

Note that clock skipping is only supported for CLK\_IN frequencies < 80 kHz. The clock-skipping timeout period (i.e., the maximum permitted CLK\_IN interruption) varies depending on the reference frequency and PLL ratio configuration.

**Note:** Clock skipping is not valid if the holdover function is enabled (see Section 4.4.2). Clock skipping is automatically disabled if the holdover function is enabled.

The clock-skipping behavior is illustrated in Fig. 4-7.

Figure 4-7. Clock Skipping for CLK\_IN Interruption

#### 4.4.2 Holdover Mode

The CLK\_IN signal is monitored to confirm the frequency reference is present and stable. The holdover function enables a valid clock output to be maintained under conditions where the reference is missing or unstable. The holdover function is enabled by setting HOLDOVER\_EN.

If CLK\_IN is missing or unstable, the CS2501 freezes the dynamic PLL ratio at its current setting. The PLL remains locked and the CLK\_OUT signal continues without any glitch or interruption.

When a valid CLK\_IN is detected, the PLL resynchronizes to the frequency reference. If the frequency reference aligns with the previous CLK IN frequency, the PLL remains locked and maintains a glitchless output.

### 4.4.3 Digital FLL Bandwidth

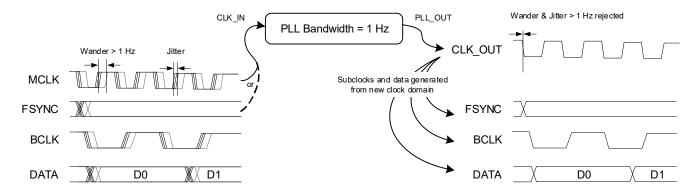

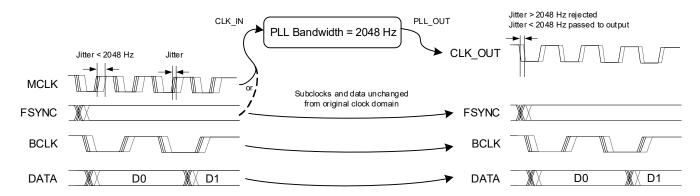

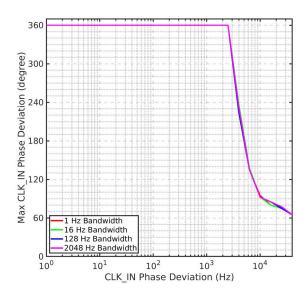

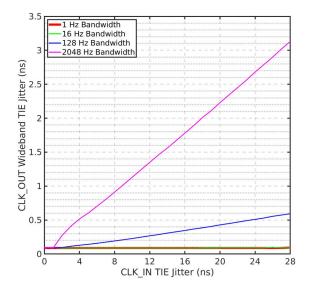

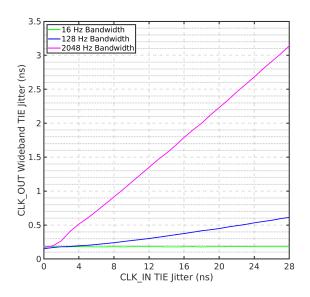

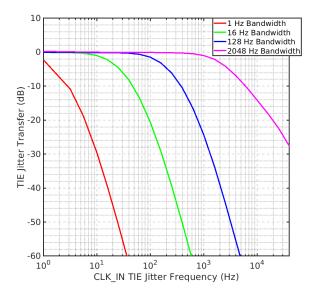

The bandwidth of the digital FLL can be configured to suit different operating conditions. The FLL bandwidth determines the extent to which any jitter on the CLK\_IN signal is attenuated or is passed through to the output clocks. In some applications, it is desirable to reject all jitter as far as possible; in other applications, it may be preferable to preserve the low-frequency variations in the reference clock while attenuating jitter at higher frequencies.

The FLL bandwidth is configured using FLL\_BW and FLL\_BW\_MOD. The FLL\_BW field selects a value 1–128 Hz; the FLL\_BW\_MOD selects multiplication factor of ×1 or ×16. The combination of two fields allows bandwidth selections in the range 1–2048 Hz.

**Notes:** If the internal oscillator is used as the timing reference (see Section 4.2), the FLL bandwidth selection must be 16 Hz or greater.

The CS2501 automatically limits the FLL bandwidth to ensure optimal performance; the bandwidth is limited to a maximum of  $f_{CLK\ IN}$  / 23.4 (rounded down to the nearest valid bandwidth selection).

The FLL bandwidth scales with the SYSCLK frequency; the nominal values selected using FLL\_BW and FLL\_BW\_MOD are valid for 12 MHz SYSCLK.

A narrow bandwidth is typically recommended in applications where the CLK\_OUT signal provides a new clock domain from which all other system clocks are derived. In these circumstances, the system benefits from maximum jitter rejection, as illustrated in Fig. 4-8.

Figure 4-8. Narrow Bandwidth Application

A wide bandwidth is typically recommended in applications where some of the system clocks are referenced to CLK\_OUT, while others are derived from CLK\_IN. In these circumstances, it may be necessary to preserve some of the input reference variation in the clock output, in order to maintain phase alignment.

The FLL bandwidth should be set to the lowest setting that does not cause system-timing errors between the CLK\_IN and CLK\_OUT domains. The wide bandwidth use case is illustrated in Fig. 4-9.

Figure 4-9. Wide Bandwidth Application

## 4.5 Output Configuration

The clock output from the hybrid PLL is provided on the CLK\_OUT pin. The output is enabled by default and is disabled by setting CLK\_OUT\_DIS. If the output is disabled, the driver is configured in a high-impedance (Hi-Z) state.

The CLK\_OUT signal is valid if the PLL is enabled and locked. If the PLL is not locked, the PLL output is invalid. To avoid spurious clock generation, the OUT\_GATE bit can be used to stop the output whenever the PLL is not locked. If OUT\_GATE = 0, the clock output is stopped whenever the PLL is not locked.

If OUT\_GATE = 1 and IDLE\_CLK\_EN = 1, an idle clock output is generated if the PLL is enabled while CLK\_IN is not present. The idle clock is derived from the SYSCLK internal timing reference (see Section 4.2). The frequency of the idle clock is configured using IDLE\_CLK\_FREQ. The idle clock can be used to ensure a CLK\_OUT signal is generated if the PLL is enabled before CLK\_IN is present. When CLK\_IN is provided, the PLL locks to the clock reference and the output transitions to the configured frequency.

If OUT\_GATE = 1 and the PLL is unlocked after previously having been locked, the CLK\_OUT signal is invalid. The invalid output may be a fixed logic level or may be an undefined frequency.

The PLL lock status is indicated using UNLOCK. This bit is set if the PLL is not locked (including if the PLL is disabled).

If the clock output is stopped as a result of the PLL lock status, the CS2501 controls the CLK\_OUT signal to ensure there is no partial clock period—the output is stopped at the end of a complete clock period. The stopped CLK\_OUT signal is Logic 0.

If the PLL is disabled, the CLK\_OUT signal is stopped immediately; the stopped CLK\_OUT signal can be either Logic 0 or Logic 1. Note that the clock output is restored to Logic 0 during PLL enable, prior to starting the clock output; the timing is controlled to ensure there is no partial clock period.

The clock-output logic is described in Table 4-1.

| CLK_OUT_DIS | PLL Enable <sup>1</sup> | UNLOCK | OUT_GATE | IDLE_CLK_EN | CLK_OUT pin                |

|-------------|-------------------------|--------|----------|-------------|----------------------------|

| 1           | _                       | _      | _        | _           | Hi-Z                       |

| 0           | Disabled                | _      | _        | _           | 0 or 1                     |

|             | Enabled                 | 0      | _        | _           | Valid Clock                |

|             |                         | 1      | 0        | _           | 0                          |

|             |                         |        | 1        | 0           | Invalid Clock <sup>2</sup> |

|             |                         |        |          | 1           | Idle or Invalid Clock 3    |

Table 4-1. Clock Output Logic

<sup>1.</sup> The PLL is enabled by setting PLL\_EN1 and PLL\_EN2. See Section 4.3.1 for further details.

<sup>2.</sup> The invalid clock may be a fixed logic level or may be an undefined frequency.

<sup>3.</sup> The idle clock is generated if the PLL is enabled while CLK IN is absent. The output is invalid in other cases where the PLL is not locked.

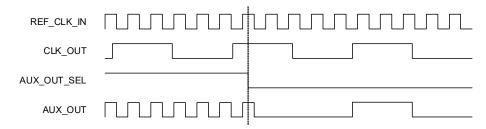

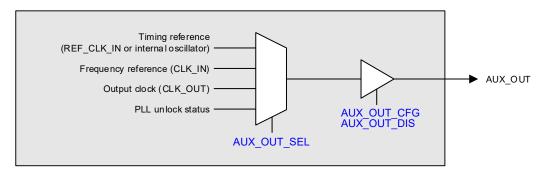

## 4.6 Auxiliary Output

The CS2501 supports an auxiliary output (AUX\_OUT) which can be configured as a clock or status output. The auxiliary output is configured using AUX\_OUT\_SEL. The supported output functions are:

- Timing reference clock (REF CLK IN or internal oscillator)

- Frequency reference clock (CLK IN)

- Output clock (CLK\_OUT)

- · PLL unlock status (asserted if PLL is not locked)

A glitchless transition is provided if the auxiliary output is switched between the timing reference and the output clock, ensuring there are no partial clock periods in the output signal. The glitchless transition is illustrated in Fig. 4-10.

Figure 4-10. Glitchless Transition between Clock Signals

If the auxiliary output is configured as the PLL unlock indication, the output driver can be configured as either CMOS (active high) or open drain (active low). The output driver is configured using AUX\_OUT\_CFG.

Note: If the auxiliary output is configured as a clock output, the output driver is CMOS in all cases.

The output driver can be configured to high impedance by setting AUX OUT DIS.

The auxiliary output is illustrated in Fig. 4-11.

Figure 4-11. Auxiliary Output Configuration

#### 4.7 I<sup>2</sup>C/SPI Control Port

The CS2501 incorporates a control port, supporting I<sup>2</sup>C or SPI modes of operation. In Software Control Mode, the CS2501 is configured by writing to control registers using the control port.

The control port is configured in I<sup>2</sup>C mode or SPI mode using the I<sup>2</sup>C ADDR/ <del>SPI CS</del> pin.

- I<sup>2</sup>C mode is selected by connecting the I<sup>2</sup>C\_ADDR/ <del>SPI\_CS</del> pin to VDD or GND. The pin connection is used to select the target address on the I<sup>2</sup>C bus.

- SPI mode is selected by a high-to-low transition on the I2C ADDR/SPI CS pin after power-on.

### 4.7.1 I<sup>2</sup>C Interface

The I2C control port is supported using the I2C\_SCL and I2C\_SDA pins.

The CS2501 is a target device on the I<sup>2</sup>C bus—SCL is a clock input, SDA is a bidirectional data pin. To allow arbitration of multiple targets (and/or multiple controllers) on the same interface, the CS2501 transmits Logic 1 by tristating the SDA pin, rather than pulling it high. An external pull-up resistor is required to pull the SDA line high so that the Logic 1 can be recognized by the controller.

In order to allow many devices to share a single two-wire control bus, every device on the bus has a unique 8-bit target address (this is not the same as the address of each register in the register map). Note that the LSB of the target address is the read/write bit; this bit is set to Logic 1 for read and Logic 0 for write.

The I<sup>2</sup>C device address is configured using the I<sup>2</sup>C\_ADDR/<del>SPI\_CS</del> pin as described in Table 4-2.

| I2C_ADDR Pin Connection | I <sup>2</sup> C Address  |

|-------------------------|---------------------------|

| Pull-up to VDD          | 0x9E (write), 0x9F (read) |

| Pull-down to GND        | 0x9C (write), 0x9D (read) |

Table 4-2. I<sup>2</sup>C Address Selection

The host device indicates the start of data transfer with a high-to-low transition on SDA while SCL remains high. This indicates that a device address and subsequent address/data bytes follow. The CS2501 responds to the start condition and shifts in the next eight bits on SDA (8-bit target address, including read/write bit, MSB first). If the target address received matches the target address of The CS2501, it responds by pulling SDA low on the next clock pulse (ACK). If the target address is not recognized, the CS2501 returns to the idle condition and waits for a new start condition.

If the target address matches the target address of the CS2501, the data transfer continues. The controller indicates the end of data transfer with a low-to-high transition on SDA while SCL remains high. After receiving a complete address and data sequence, the CS2501 returns to the idle state and waits for another start condition. If a start or stop condition is detected out of sequence at any point during data transfer (i.e., SDA changes while SCL is high), the device returns to the idle condition.

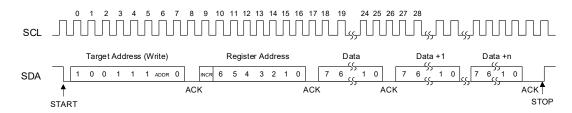

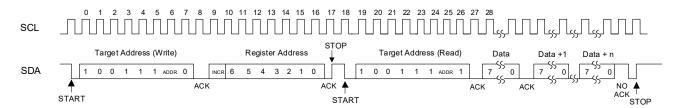

The I<sup>2</sup>C interface uses a 7-bit register address and 8-bit data words. Note that the full I<sup>2</sup>C message protocol also includes a target address, a read/ write bit, and other signaling bits (see Fig. 4-12 and Fig. 4-13).

The CS2501 supports the following read and write operations:

- · Single write

- · Single read

- Multiple write

- Multiple read

Continuous (multiple) read and write modes allow register operations to be scheduled faster than is possible with single register operations. If auto-increment is enabled, the CS2501 automatically increments the register address after each data byte. Successive data bytes can be input/output continuously, separated by the acknowledge (ACK) bit.

The auto-increment option is configured using the MSB of the register-address byte. Setting this bit enables the auto-increment.

The I<sup>2</sup>C register write operation is shown in Fig. 4-12.

Figure 4-12. Control Interface I<sup>2</sup>C Register Write

Copyright © 2023-2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

The I<sup>2</sup>C register read operation is shown in Fig. 4-13.

Figure 4-13. Control Interface I<sup>2</sup>C Register Read

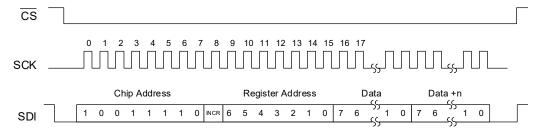

#### 4.7.2 SPI Interface

The SPI interface is supported using the SPI\_CS, SPI\_SCK, and SPI\_SDI pins.

The SPI\_CS pin provides the chip-select input (active low). Data bits (on the SPI\_SDI pin) are clocked in on the rising edge of SPI\_SCK. Note the SPI interface supports write operations only; read operations are not supported.

The SPI write transaction starts with a high-to-low transition on SPI\_CS. The first data byte contains the chip address, which must be 0x9E when writing to the CS2501. The next data byte contains the register address and auto-increment bit. This is followed by the data to be written to the selected register address.

Continuous (multiple) write mode allows register operations to be scheduled faster than is possible with single register writes. If auto-increment is enabled, the CS2501 automatically increments the register address after each data byte. Successive data bytes can be input every 8 clock cycles, allowing block writes of multiple registers.

The auto-increment option is configured using the MSB of the register-address byte. Setting this bit enables the auto-increment.

The SPI register write operation is shown in Fig. 4-14.

Figure 4-14. Control Interface SPI Register Write

### 4.7.3 Device Configuration

The device should be fully configured before enabling the PLL. When changing any register settings, it is recommended to disable the PLL, update the registers, then enable the PLL; this ensures there is no unintended behavior.

See Section 4.3.1 to enable and disable the PLL. Specific restrictions and exceptions on updating register fields are described in Section 4.7.3.2.

#### 4.7.3.1 Freezable Fields

The register map supports a number of freezable fields, as listed in Table 4-3. If FREEZE\_EN is set, these fields are frozen to their current values regardless of any register writes. If a new value is written, the value is buffered and does not become effective until FREEZE\_EN is cleared. When FREEZE\_EN is cleared, all of the frozen fields become active simultaneously.

Table 4-3. Freezable Fields

| Address | Fields                   |

|---------|--------------------------|

| 0x02    | CLK_OUT_DIS, AUX_OUT_DIS |

| 0x03    | AUX_OUT_SEL, RATIO_MOD   |

#### 4.7.3.2 Field Update Restrictions

The fields listed in Table 4-4 can be configured at any time, and do not result in any partial clock period in the outputs.

Table 4-4. Register Fields with No Write Restrictions

| Address | Fields                   |

|---------|--------------------------|

| 0x02    | CLK_OUT_DIS, AUX_OUT_DIS |

| 0x03    | PLL_EN1, AUX_OUT_SEL     |

| 0x05    | PLL_EN2, FREEZE_EN       |

The fields listed in Table 4-5 can be configured at any time, but may cause the PLL to lose lock temporarily.

Table 4-5. Register Fields with Restrictions

| Address   | Fields          |

|-----------|-----------------|

| 0x03      | RATIO_MOD       |

| 0x06-0x09 | RATIO_1-RATIO_4 |

| 0x16      | REF_CLK_IN_DIV  |

| 0x17      | RATIO_CFG       |

Note that, for all other control fields (not listed in Table 4-4 or Table 4-5), the PLL should be disabled before reconfiguring; failure to do so may result in unintended behavior, and may require a software reset to restart the device.

#### 4.7.4 Software Reset

A software reset is triggered by writing 0x5A to the SW\_RST field. A software reset causes all of the CS2501 control registers to be reset to their default states.

#### 4.7.5 Power-On Reset

The power-on reset (POR) sequence is scheduled on initial power-up, and following any interruption to the VDD supply. The POR causes all of the CS2501 control registers to be reset to their default states.

#### 4.8 Device ID

The device ID, and other associated data, can be read from the control fields listed in Table 4-6.

Table 4-6. Device ID

| Label            | Description                 |

|------------------|-----------------------------|

| DEVID_1, DEVID_2 | Device ID                   |

| A_REV_ID         | All-layer device revision   |

| MTL_REV_ID       | Metal-layer device revision |

## 5 Applications

### 5.1 Crystal Component Selection

The crystal oscillator (see Section 4.2.1) uses an external crystal to generate the timing reference. Load capacitors are connected to the crystal as shown in Fig. 5-1. A series resistor (R<sub>S</sub>) may also be required to configure the drive level for the selected crystal.

Figure 5-1. Crystal Oscillator Connection

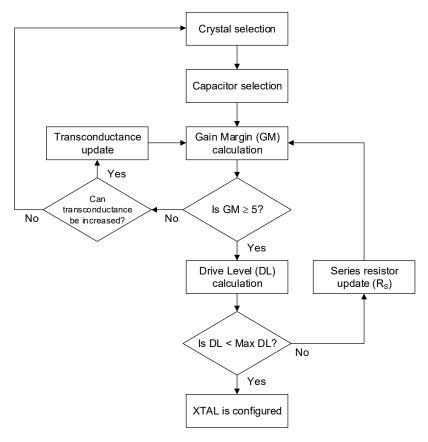

The suitability of the selected crystal is determined by whether the gain margin and drive level are within the valid operating limits of the crystal. The gain margin and drive level can be calculated as a function of the transconductance of the crystal interface.

The transconductance of the crystal interface is dependent on the VDD operating voltage as described in Table 3-4. For 3.3 V use cases, the transconductance is configurable using the XOSC\_GEARn\_3V3\_DRV fields as described in Section 4.2.1.

The recommended sequence for crystal component selection is as follows:

- 1. **Crystal selection.** The CS2501 is compatible with a wide variety of crystal components, including the NX3225SA, NX2016A, ECX-33Q, and ECX-2236Q families.

- 2. **Capacitor selection.** Capacitors should be selected according to the crystal manufacturer's specification for load capacitance ( $C_1$ ). The recommended value for each  $C_{XTAI}$  capacitor is  $2 \times C_1$ .

- 3. **Series resistor.** In the first instance, assume the series resistor Rs is not required (0  $\Omega$ ).

- 4. Gain margin calculation. The gain margin can be calculated from the transconductance of the crystal interface and the series resistor R<sub>S</sub>, together with the crystal characteristics. If the gain margin is less than 5, adjust the transconductance parameter to achieve the required gain margin ≥5. If the required gain margin cannot be achieved, a different crystal selection must be made (Step 1).

$$The \ gain \ margin \ is \ calculated \ as \ follows: \ Gain \ Margin \ = \ \frac{Transconductance}{4 \times \left(\text{ESR} + R_S\right) \times \left(2\pi \times f_{XTAL}\right)^2 \times \left(C_0 + C_L\right)^2}$$

where:

Transconductance = transconductance of the crystal interface (S)

ESR = equivalent series resistance (ESR) of the crystal ( $\Omega$ )

$R_S$  = series resistance ( $\Omega$ )

f<sub>XTAL</sub> = resonant frequency of the crystal (Hz)

C<sub>L</sub> = load capacitance of the crystal (F)

$C_0$  = shunt capacitance of the crystal (F)

5. **Drive level calculation.** The drive level can be calculated using the crystal characteristics and the operating voltage. The operating voltage (peak voltage across the crystal) can be determined using measurement or else by simulation. If the drive level exceeds the maximum level for the crystal, adjust the series resistor R<sub>S</sub> to meet the required specification. Increasing R<sub>S</sub> results in a lower voltage across the crystal and a decrease in drive level.

If the series resistor is adjusted, the gain margin must now be recalculated (Step 4). It is recommended to find the minimum series resistance that meets the required gain margin and drive level.

The drive level (W) is calculated as follows: Drive Level =  $2 \times ESR \times (\pi \times f_{XTAL} \times V \times (C_L + C_0))^2$  where:

ESR = equivalent series resistance (ESR) of the crystal ( $\Omega$ )

f<sub>XTAL</sub> = resonant frequency of the crystal (Hz)

V = Peak voltage across the crystal (V)

C<sub>I</sub> = load capacitance of the crystal (F)

$C_0$  = shunt capacitance of the crystal (F)

The sequence for crystal component selection is illustrated in Fig. 5-2.

Figure 5-2. Crystal Oscillator Component Selection

# 6 Register Quick Reference

This section gives an overview of the control port registers. Refer to the following bit definition tables for bit assignment information.

This register view is for the CS2501.

- A "—" represents a reserved field/access type.

- · The reserved field values must not be modified.

- The registers are 16 bits wide, and only word transactions are allowed.

- · Fields shown in orange are affected by the FREEZE bit.

- All visible fields are read/write except where indicated with the following shading:

|--|

Table 6-1. Block Base Addresses

| Base Address | Block Name | Register Quick<br>Reference | Register<br>Description<br>Reference |

|--------------|------------|-----------------------------|--------------------------------------|

| 0x0000 0000  | CONFIG     | Section 6.1                 | Section 7.1                          |

### 6.1 CONFIG

| Address     | Register         | 7              | 6            | 5      | 4      | 3           | 2     | 1           | 0           |

|-------------|------------------|----------------|--------------|--------|--------|-------------|-------|-------------|-------------|

| 0x0000 0002 | PLL_CFG1         | UNLOCK         |              |        | _      |             |       | AUX_OUT_DIS | CLK_OUT_DIS |

| p. 26       |                  | 1              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0003 | PLL_CFG2         |                | RATIO_MOD    |        | -      | _           | AUX_C | OUT_SEL     | PLL_EN1     |

| p. 26       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0004 | PLL_CFG3         |                | _            | _      | •      | HOLDOVER_EN |       | _           |             |

| p. 27       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0005 | PLL_CFG4         |                | _            | _      |        | FREEZE_EN   | -     | _           | PLL_EN2     |

| p. 27       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0006 | RATIO_REG_1      |                |              |        | RAT    | 10_1        |       |             |             |

| p. 27       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0007 | RATIO_REG_2      |                |              |        | RAT    | 10_2        |       |             |             |

| p. 27       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0008 | RATIO_REG_3      |                |              |        | RAT    | TIO_3       |       |             |             |

| p. 27       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0009 | RATIO_REG_4      |                | RATIO_4      |        |        |             |       |             |             |

| p. 28       |                  | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0016 | DII CECS         | CLK_IN_SKIP_EN | ALIX OUT CEC | _      | DEE CI | K_IN_DIV    | even  | _K_SRC      | _           |

| p. 28       | FLL_CI G3        | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0x0000 0017 | DII CECS         | 0              | _            | 0      |        | RATIO_CFG   |       |             |             |

| p. 28       | FLL_CFG0         | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| μ. 26       |                  |                | 0            |        | 0      | 0           |       | <u> </u>    |             |

| 0x0000 001E | PLL_CFG7         | FLL_BW_MOD     |              | FLL_BW |        |             | -     | _           |             |

| p. 28       |                  | 1              | 0            | 0      | 0      | 0           | 0     | 0           | 0           |

| 0×0000 0054 | DEV_ID_CS250X_0  |                |              |        | DEV    | /ID_2       |       |             |             |

| p. 29       | DLV_ID_00230X_0  | 0              | 0            | 1      | 0      | 0           | 1     | 0           | 1           |

|             | DEV_ID_CS250X_1  | , o            |              |        |        | /ID 1       |       |             |             |

| p. 29       | DE V_ID_G0200X_1 | 0              | 0            | 0      | 0      | 0           | 0     | 0           | 1           |

|             | REV_ID_CS250X_2  | , ,            | A_RE         |        |        |             |       | REV_ID      |             |

| p. 29       |                  | ×              | X            | _      | X      | X           | X     |             | X           |

| P. 20       |                  |                |              |        |        |             |       |             |             |

| 0x0000 0058 | SW_RESET         |                |              |        | SW     | _RST        |       |             |             |

| 1           |                  |                |              |        |        |             |       |             |             |

| Address     | Register                  | 7 | 6        | 5          | 4 | 3           | 2 | 1             | 0 |

|-------------|---------------------------|---|----------|------------|---|-------------|---|---------------|---|

| 0x0000 0068 | YOSC DRV1                 |   |          |            | • |             |   |               |   |

|             | XOSC_DRV1                 |   | _        | R1_3V3_DRV | 0 |             | _ | _             | 4 |

| p. 29       |                           | U | 0        | 0          | U | 1           | 1 | 1             | 1 |

| 0x0000 0069 | XOSC_DRV2                 |   | XOSC_GEA | R2_3V3_DRV |   | _           |   |               |   |

| p. 30       |                           | 0 | 0        | 0          | 0 | 1           | 1 | 1             | 1 |

| 0x0000 006A | XOSC_DRV3                 |   | XOSC_GEA | R3_3V3_DRV |   |             | _ | _             |   |

| p. 30       |                           | 0 | 0        | 0          | 0 | 1           | 1 | 1             | 1 |

| 0x0000 0070 | 000 0070   IDLE_CLK_CFG — |   |          |            |   | IDLE_CLK_EN |   | IDLE_CLK_FREQ |   |

| p. 30       |                           | 0 | 0        | 0          | 0 | 1           | 1 | 0             | 0 |

Address: 0x0000 0003

# 7 Register Descriptions

This section describes each of the control port registers.

This register view is for the CS2501.

- A "—" represents a reserved field/access type.

- · The reserved field values must not be modified.

- The registers are 16 bits wide, and only word transactions are allowed.

- Fields shown in orange are affected by the FREEZE bit.

- All visible fields are read/write except where indicated with the following shading:

|  | Read/write access | Read-only access | Write-only access |

|--|-------------------|------------------|-------------------|

|--|-------------------|------------------|-------------------|

### 7.1 CONFIG

## 7.1.1 PLL\_CFG1

|         | 7      | 6 | 5 | 4 | 3 | 2 | 1           | 0           |

|---------|--------|---|---|---|---|---|-------------|-------------|

|         | UNLOCK |   |   | _ |   |   | AUX_OUT_DIS | CLK_OUT_DIS |

| Access  | RO     |   |   | _ |   |   | RW          | RW          |

| Default | 1      | 0 | 0 | 0 | 0 | 0 | 0           | 0           |

| Bits | Name        | Description                                                                                                            |

|------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 7    | UNLOCK      | PLL frequency unlock indicator                                                                                         |

|      |             | 0 = PLL has not unlocked since last read of this field<br>1 = (Default) PLL has unlocked since last read of this field |

| 6:2  | _           | Reserved                                                                                                               |

| 1    | AUX_OUT_DIS | AUX_OUT disable. If disabled, the output driver is high-impedance (Hi-Z).                                              |

|      |             | 0 = (Default) Output enabled<br>1 = Output disabled (Hi-Z)                                                             |

| 0    | CLK_OUT_DIS | CLK_OUT disable. If disabled, the output driver is high-impedance (Hi-Z).                                              |

|      |             | 0 = (Default) Output enabled<br>1 = Output disabled (Hi-Z)                                                             |

### 7.1.2 PLL\_CFG2

| RW      | 7         | 7 6 5 |   | 4 | 3 | 2     | 1       | 0 |

|---------|-----------|-------|---|---|---|-------|---------|---|

|         | RATIO_MOD |       |   | _ | _ | AUX_O | PLL_EN1 |   |

| Default | 0         | 0     | 0 | 0 | 0 | 0     | 0       | 0 |

| Bits | Name        | Description                                                                                |                                                                           |  |  |  |  |

|------|-------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| 7:5  | RATIO_MOD   | Ratio modifier control. Adjusts the PLL ratio by                                           | the selected multiplier/division factor.                                  |  |  |  |  |

|      |             | 000 = (Default) Multiply x1<br>001 = Multiply x2<br>010 = Multiply x4<br>011 = Multiply x8 | 100 = Divide /2<br>101 = Divide /4<br>110 = Divide /8<br>111 = Divide /16 |  |  |  |  |

| 4:3  | <del></del> | Reserved                                                                                   |                                                                           |  |  |  |  |

| 2:1  | AUX_OUT_SEL | AUX_OUT function select                                                                    |                                                                           |  |  |  |  |

|      |             | 00 = (Default) REF_CLK_IN<br>01 = CLK_IN                                                   | 10 = CLK_OUT<br>11 = PLL unlock (UNLOCK)                                  |  |  |  |  |

| 0    | PLL_EN1     | PLL enable. Note that PLL_EN2 must also be set to enable the PLL.                          |                                                                           |  |  |  |  |

|      |             | 0 = (Default) Disabled<br>1 = Enabled                                                      |                                                                           |  |  |  |  |

|         | Circles     |                                    |                                             |                |                       |        |                   | 7.1 CONFIG      |

|---------|-------------|------------------------------------|---------------------------------------------|----------------|-----------------------|--------|-------------------|-----------------|

| 7.1.3   | PLL_CFG3    |                                    |                                             |                |                       |        | Addre             | ss: 0x0000 0004 |

| RW      | 7           | 6                                  | 5                                           | 4              | 3                     | 2      | 1                 | 0               |

|         |             | -                                  | _                                           |                | HOLDOVER_EN           |        | _                 |                 |

| Default | 0           | 0                                  | 0                                           | 0              | 0                     | 0      | 0                 | 0               |

| Bits    | Name        |                                    |                                             |                | Description           |        |                   |                 |

| 7:4     |             | Reserved                           |                                             |                |                       |        |                   |                 |

| 3       | HOLDOVER_EN | Holdover 6<br>0 = (Def<br>1 = Enal | ault) Disabled                              |                |                       |        |                   |                 |

| 2:0     |             | Reserved                           |                                             |                |                       |        |                   |                 |

| 7.1.4   | PLL_CFG4    |                                    |                                             |                |                       |        | Addre             | ss: 0x0000 0005 |

| RW      | 7           | 6                                  | 5                                           | 4              | 3                     | 2      | 1                 | 0               |

| D-6. "  | ^           |                                    |                                             |                | FREEZE_EN             |        |                   | PLL_EN2         |

| Default | 0           | 0                                  | 0                                           | 0              | 0                     | 0      | 0                 | 0               |

| Bits    | Name        |                                    |                                             |                | Description           |        |                   |                 |

| 7:4     | _           | Reserved                           |                                             |                |                       |        |                   |                 |

| 3       | FREEZE_EN   | buffered u<br>0 = (Def<br>1 = Enal | ntil FREEZE_EN ault) Disabled               | is cleared.    | zable fields hold the |        | s. Any apartes to | These helds are |

| 2:1     | _           | Reserved                           |                                             |                |                       |        |                   |                 |

| 0       | PLL_EN2     |                                    | e. Note that PLL_<br>ault) Disabled<br>bled | _EN1 must also | be set to enable th   | e PLL. |                   |                 |

| 7.1.5   | RATIO_REG   | <b>3_1</b>                         |                                             |                |                       |        | Addre             | ss: 0x0000 0006 |

| RW      | 7           | 6                                  | 5                                           | 4              | 3                     | 2      | 1                 | 0               |

|         |             |                                    |                                             | R/             | ATIO_1                |        |                   |                 |

| Default | 0           | 0                                  | 0                                           | 0              | 0                     | 0      | 0                 | 0               |

| Bits    | Name        |                                    |                                             |                | Description           |        |                   |                 |

| 7:0     | RATIO_1     | PLL ratio,                         | bits [31:24]                                |                |                       |        |                   |                 |

| 7.1.6   | RATIO_REG   | G_2                                |                                             |                |                       |        | Addre             | ss: 0x0000 0007 |

| RW      | 7           | 6                                  | 5                                           | 4              | 3                     | 2      | 1                 | 0               |

|         |             |                                    |                                             | R/             | ATIO_2                |        |                   |                 |

| Default | 0           | 0                                  | 0                                           | 0              | 0                     | 0      | 0                 | 0               |

| Bits    | Name        |                                    |                                             |                | Description           |        |                   |                 |

| 7:0     | RATIO_2     | PLL ratio,                         | bits [23:16]                                |                |                       |        |                   |                 |

| 7.1.7   | RATIO_REG   | <b>3_3</b>                         |                                             |                |                       |        | Addre             | ss: 0x0000 0008 |

| RW      | 7           | 6                                  | 5                                           | 4              | 3                     | 2      | 1                 | 0               |

|         |             |                                    |                                             |                | ATIO_3                |        |                   |                 |

| Default | 0           | 0                                  | 0                                           | 0              | 0                     | 0      | 0                 | 0               |

| Bits | Name    | Description            |

|------|---------|------------------------|

| 7:0  | RATIO_3 | PLL ratio, bits [15:8] |

Address: 0x0000 0016

Address: 0x0000 0017

Address: 0x0000 001E

| 7.1.8 RATIO REG | 7.1.8 | RATIO RE | G | 4 |

|-----------------|-------|----------|---|---|

|-----------------|-------|----------|---|---|

| RW      | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------|---|---|---|---|---|---|---|--|

|         | RATIO_4 |   |   |   |   |   |   |   |  |

| Default | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| Bits | Name    | Description           |

|------|---------|-----------------------|

| 7:0  | RATIO_4 | PLL ratio, bits [7:0] |

## 7.1.9 PLL\_CFG5

| RW      | 7              | 6           | 5 | 4              | 3 | 2     | 1     | 0 |

|---------|----------------|-------------|---|----------------|---|-------|-------|---|

|         | CLK_IN_SKIP_EN | AUX_OUT_CFG | _ | REF_CLK_IN_DIV |   | SYSCL | K_SRC | _ |

| Default | 0              | 0           | 0 | 0              | 0 | 0     | 0     | 0 |

| Bits | Name           | Description                                                                                                                                                                                  |  |  |  |  |  |

|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7    | CLK_IN_SKIP_EN | Clock-skipping enable                                                                                                                                                                        |  |  |  |  |  |

|      |                | 0 = (Default) Disabled<br>1 = Enabled                                                                                                                                                        |  |  |  |  |  |

| 6    | AUX_OUT_CFG    | JX1 and AUX2 driver configuration. Only valid for lock/status output signals; clock outputs are CMOS in all ses.                                                                             |  |  |  |  |  |

|      |                | <ul><li>0 = (Default) CMOS. Active high (Logic 1 indicates unlock or clock-missing status).</li><li>1 = Open Drain. Active low (Logic 0 indicates unlock or clock-missing status).</li></ul> |  |  |  |  |  |

| 5    | _              | Reserved                                                                                                                                                                                     |  |  |  |  |  |

| 4:3  | REF_CLK_IN_DIV | REF_CLK_IN input divider.                                                                                                                                                                    |  |  |  |  |  |