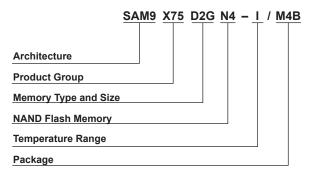

# SAM9X75 MPU, up to 2-Gbit DDR SDRAM, up to 4-Gbit NAND Flash, Gigabit Ethernet PHY, Power Management IC, 64-Mbit Serial Quad I/O Flash

**SAM9X75 SOM Series**

www.microchip.com Product Page Links

## Introduction

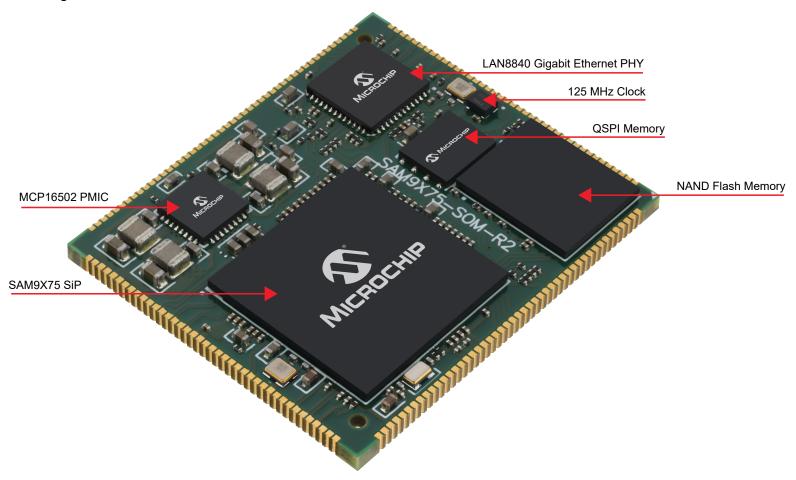

The Microchip SAM9X75 System-On-Module Series is a small single-sided SOM series based on a System-in-Package (SiP) ARM926EJ-S Arm® Thumb® CPU-based embedded microprocessor running up to 800 MHz.

The SAM9X75 SOM Series is built on a common set of proven Microchip components to reduce time to market by simplifying hardware design and software development.

The SOM embeds a SAM9X75 SiP microprocessor with an up to 2-Gbit DDR SDRAM, an up to 4-Gbit NAND Flash memory, a Gigabit Ethernet PHY, a 64-Mbit serial Quad I/O Flash memory and a dedicated Power Management Unit.

The SAM9X75 SOM Series also limits design rules of the main application board, reducing overall PCB complexity and cost. The SAM9X75 SOM Series is supported by a free Linux® distribution and bare metal C examples.

Figure 1. SAM9X75 SOM Series Overview

## 1. Features

- SAM9X75 System-in-Package including:

- ARM926EJ-S Arm Thumb processor-based SAM9X75 MPU running up to 800 MHz

- Up to 2-Gbit DDR3L or 512-Mbit DDR2 SDRAM

- Up to 4-Gbit NAND Flash Memory

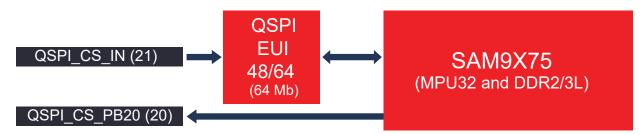

- 64-Mbit Serial Quad I/O Flash Memory (SST26VF064BEUIT-104I/MF) with Embedded EUI-48™ and EUI-64™ MAC Addresses

- On-Board Power Management Unit (MCP16502TAB-E/S8B)

- Gigabit Ethernet Transceiver (LAN8840T-V/PSA)

- 24-MHz Crystal Oscillator for microprocessor main clock generation

- 25-MHz Crystal Oscillator and 125-MHz MEMS Oscillator (DSC1501MI2A-125.0000) for Ethernet clock generation

- 32.768-kHz Crystal Oscillator for slow clock generation

- One High-Speed USB Device, three High-Speed USB Hosts with dedicated on-chip transceivers

- Shutdown and Reset Control Pins

- Up to 67 I/Os

- Independent Power Supplies available for SD Cards, RGB LCD, LVDS Display, Camera Sensor and Backup depending on voltage domains

- Operational Conditions:

- Main operating voltage: 3.3V to 5.5V ±5%

- Module ambient temperature range (T<sub>A</sub>) range: -40°C to +85°C

- · Package:

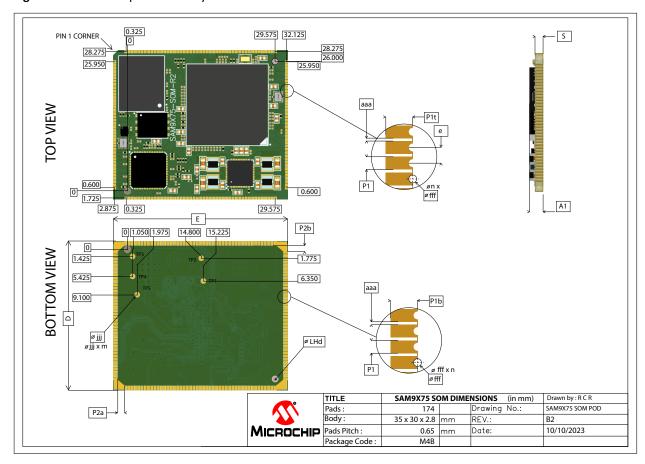

- 35x30 mm 174-pin 0.65 mm Pad Pitch Module, manually solderable for prototyping

# 2. Applications

- Industrial Control and Automation

- Smart Appliances

- Human Machine Interfaces (HMI)

- IoT Gateways

- Access Control Panels

- Security and Alarm Systems

## 3. Design Resources

## 3.1 Hardware Design Resources

As the SAM9X7 Series System-in-Package (SiP) MPU embeds a DDR SDRAM memory chip, most of the design complexity related to high-speed DDR interface routing is avoided when using the SAM9X75 System-On-Module.

For carrier board design, Microchip provides complete SAM9X75 System-On-Module schematics and PCB design files in Altium format (on request and under license agreement), enabling electrical simulations for high-speed interfaces such as MIPI, LVDS and USB, and mechanical evaluation/ simulation. For signal integrity simulation, Microchip provides IBIS models of the SAM9X75 SiP device.

## 3.2 Software Resources

Microchip Technology provides complete embedded Linux solutions for MPUs. For more information, refer to Linux® OS for MPUs.

## 4. Reference Documents

The following reference data sheets are available.

| Document Title                       | Available         | Literature No. |

|--------------------------------------|-------------------|----------------|

| SAM9X75 SiP                          | www.microchip.com | DS60001827     |

| LAN8840                              | www.microchip.com | DS00004727     |

| DSC150X                              | www.microchip.com | DS20006516     |

| SST26VF064BEUI                       | www.microchip.com | DS20006138     |

| MCP16502                             | www.microchip.com | DS20006275     |

| MX30LF2G28AD-XKI <sup>(1)</sup>      | www.mxic.com.tw   | PM2579         |

| MT29F2G08ABAEAH4-IT:G <sup>(1)</sup> | www.micron.com    | -              |

| MX30LF4G28AD-XKI <sup>(2)</sup>      | www.mxic.com.tw   | PM2579         |

| MT29F4G08ABAFAH4-IT:F <sup>(2)</sup> | www.micron.com    | -              |

## **Notes:**

- 1. 2-Gbit NAND Flash memory

- 2. 4-Gbit NAND Flash memory

## 5. Description

The SAM9X75 SOM Series is a high-performance System-On-Module series based on the ultra-low power ARM926EJ-S CPU-based embedded microprocessor (MPU) SAM9X75. The SAM9X75 SOM Series is certified for industrial operating conditions over the [-40°C to 85°C] industrial ambient temperature range.

The SAM9X75 SOM Series operates at a maximum CPU operating frequency of 800 MHz and a maximum bus speed of 266 MHz and offers the following features:

- DDRx SDRAM memory with one of the following configurations:

- 512-Mbit DDR2 SDRAM memory size (SAM9X75D5M-I/4TB)

- 1-Gbit DDR3L SDRAM memory size (SAM9X75D1G-I/4TB)

- 2-Gbit DDR3L SDRAM memory size (SAM9X75D2G-I/4TB)

- 8-bit NAND Flash memory with one of the following configurations:

- 2-Gbit memory size (MX30LF2G28AD-XKI or MT29F2G08ABAEAH4-IT:G)<sup>(1)</sup>

- 4-Gbit memory size (MX30LF4G28AD-XKI or MT29F4G08ABAFAH4-IT:F)<sup>(2)</sup>

**Note:** A version with no NAND Flash memory is also available. (3)

- 64 Mbits of Serial Quad I/O (SQI) Flash memory with EUI (SST26VF064BEUIT-104I/MF)

- A Gigabit Ethernet transceiver (LAN8840T-V/PSA)

The SAM9X75 SOM Series device is a 35x30 mm 174-pin 0.65 mm Pad Pitch Module.

The device offers an extensive peripheral set, system control and up to 67 I/Os featuring:

- Up to 12 Flexible Serial Communication Controllers (FLEXCOM)

- Universal Synchronous Asynchronous Receiver Transceiver (USART)

- Two-Wire Interface (TWI)

- Serial Peripheral Interface (SPI)

- Up to six 12-bit ADC inputs, with a maximum of 1-Msps conversion rate

- Up to two CAN(FD) interfaces compliant with CAN Protocol version 2.0 Part A, B and ISO 11898-1

- Up to two SDMMC interfaces (MultiMedia Card/e.MMC) compliant with Specification V4.51, SD Memory Card Specification V3.0 and SDIO Specification V3.0

- Up to four PWM interfaces

- Serial interfaces such as SSC and I<sup>2</sup>S

- 4-lane LVDS or MIPI DSI<sup>®</sup> interface

- 4-lane CSI-2 camera interface

- Half-bridge class-D stereo

#### Notes:

- 1. Only available with 1-Gbit DDR3L SDRAM memory size (SAM9X75D1G-I/4TB).

- 2. Only available with 2-Gbit DDR3L SDRAM memory size (SAM9X75D2G-I/4TB).

- 3. Only available with 512-Mbit DDR2 SDRAM memory size (SAM9X75D5M-I/4TB).

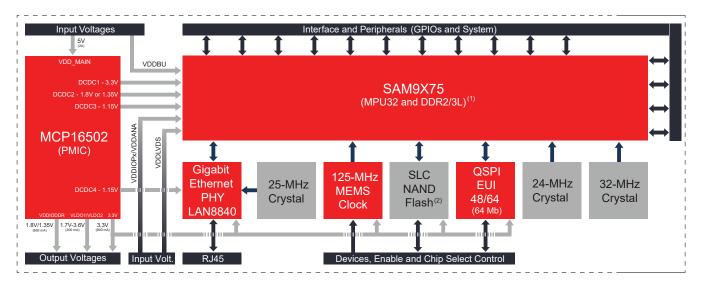

## 6. Block Diagram

Figure 6-1. SAM9X75 SOM Series Block Diagram

#### Notes:

- 1. Several DDRx memory sizes are available depending on the memory configuration.

- 2. Several NAND Flash memory sizes are available depending on the memory configuration.

For more details, see Ordering Information.

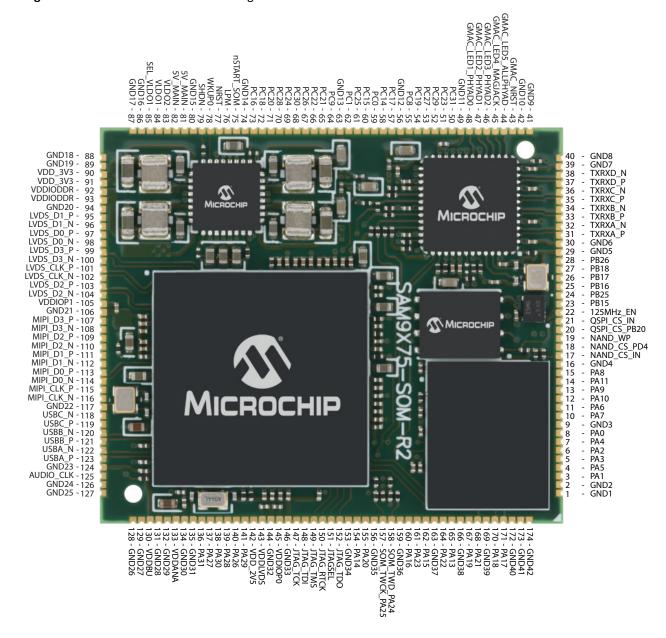

## 7. Pinout

## 7.1 Pinout Overview

Figure 7-1. SAM9X75 SOM Series Pin Assignment

## 7.2 Pin List

The following tables provide the SAM9X75 SOM Series module pin descriptions.

**Important:** Compared to the SAM9X75 SiP device, some PIO features are not listed. These features are used internally on the SAM9X75 SOM Series and cannot have other uses.

The device features several PIO controllers that multiplex the I/O lines of the peripheral set. The following PIOx Pin Description tables define how the I/O lines are multiplexed on the different PIO controllers. The "Reset State" column shows whether the PIO line resets in I/O mode or in Peripheral mode. If I/O is shown, the PIO line resets with the characteristics (input, output, pull-up or pull-down) indicated in this same column, so that the device is configured in a known state as soon as the reset is released. As a result, PIO\_CFGR.FUNC resets to '0'. If a signal name is shown in the "Reset State" column, the PIO line is assigned to this function and PIO\_CFGR.FUNC is not set to '0'. That is the case for pins controlling memories, in particular address lines, which require the pin to be driven as soon as the reset is released.

#### 7.2.1 PIOA Pin List

Table 7-1. PIOA Pin Description

| Dad No  | Power Rail               | I/O Tymo    | Prin   | nary      | Altornata Cignal                |              | PIO Peripheral |              | Reset State <sup>(1)</sup>   | Note                                   |   |

|---------|--------------------------|-------------|--------|-----------|---------------------------------|--------------|----------------|--------------|------------------------------|----------------------------------------|---|

| Pad No. | Power Raii               | I/O Type    | Signal | Туре      | Alternate Signal                | Func         | Signal         | IO Set       | Signal, Dir, PU, PD, HiZ, ST | Note                                   |   |

| 8       | VDDIOP0                  | GPIO        | PA0    | GPIO      | -                               | Α            | SDMMC0_DAT0    | 1            | PIO, I, PU, ST               | _                                      |   |

| 3       | VDDIOP0                  | GPIO        | PA1    | GPIO      | -                               | Α            | SDMMC0_CMD     | 1            | PIO, I, PU, ST               | _                                      |   |

| 6       | VDDIOP0                  | GPIO        | PA2    | GPIO      | WKUP1                           | Α            | SDMMC0_CK      | 1            | PIO, I, PU, ST               | _                                      |   |

| 5       | VDDIOP0                  | GPIO        | PA3    | GPIO      | _                               | Α            | SDMMC0_DAT1    | 1            | PIO, I, PU, ST               | _                                      |   |

| 7       | VDDIOP0                  | GPIO        | PA4    | GPIO      | _                               | Α            | SDMMC0_DAT2    | 1            | PIO, I, PU, ST               | _                                      |   |

| 4       | VDDIOP0                  | GPIO        | PA5    | GPIO      | -                               | Α            | SDMMC0_DAT3    | 1            | PIO, I, PU, ST               | _                                      |   |

| 11      | VDDIOP0                  | GPIO        | PA6    | GPIO      |                                 | Α            | FLEXCOM0_IO4   | 1            | PIO, I, PU, ST               |                                        |   |

| 11      | VDDIOPU                  | GPIO        | PAG    | GPIO      | _                               | В            | SDMMC1_DAT1    | 1            | PIO, 1, PO, 31               | <b>-</b>                               |   |

| 10      | VDDIOP0                  | GPIO        | PA7    | GPIO      | WKUP2                           | Α            | FLEXCOM0_IO3   | 1            | DIO I DII CT                 | _                                      |   |

| 10      | VDDIOPU                  | GPIO        | PA/    | GPIO      | WKUPZ                           | В            | SDMMC1_DAT2    | 1            | PIO, I, PU, ST               |                                        |   |

| 15      | VDDIOP0                  | GPIO        | PA8    | GPIO      | A FLEXCOMO_IO2 1 PIO. I. PU. ST | DIO I DII CT | _              |              |                              |                                        |   |

| 15      | VDDIOPU                  | GPIO        | PAO    | GPIO      | WKUP3                           | В            | SDMMC1_DAT3    | 1            | PIO, I, PU, ST               |                                        |   |

| 13      | VDDIOP0                  | GPIO        | PA9    | GPIO      |                                 | Α            | FLEXCOM4_IO1   | 1,2          | PIO, I, PU, ST               |                                        |   |

| 13      | VDDIOPU                  | GPIO        | PA9    | GPIO      | _                               | В            | SDMMC1_DAT0    | 1            | P10, 1, P0, 31               | -                                      |   |

| 12      | VDDIOP0                  | GPIO        | DA10   | GPIO      |                                 | Α            | FLEXCOM4_IO0   | 1,2          | PIO, I, PU, ST               |                                        |   |

| 12      | VDDIOPU                  | GPIO        | PATO   | GPIO      | _                               | В            | SDMMC1_CMD     | 1            | P10, 1, P0, 31               | _                                      |   |

| 14      | VDDIOP0                  | GPIO        | PA11   | GPIO      |                                 | Α            | FLEXCOM4_IO2   | 1,2          | PIO, I, PU, ST               |                                        |   |

| 14      | VDDIOPU                  | GPIO        | PATT   | GPIO      | _                               | В            | SDMMC1_CK      | 1            | PIO, 1, PO, 31               | <b>-</b>                               |   |

| _       | VDDIOP0                  | GPIO        | PA12   | GPIO      | _                               | _            | -              | -            | PIO, I, PU, ST               | Used for PMIC interrupt <sup>(2)</sup> |   |

| 165     | VDDIODO                  | CDIO        | DA12   | CDIC      |                                 | Α            | FLEXCOM2_IO0   | 1            | DIO I DII CT                 |                                        |   |

| 165     | VDDIOP0                  | GPIO        | PAIS   | GPIO      | _                               | В            | FLEXCOM4_IO4   | 1            | PIO, I, PU, ST               | _                                      |   |

|         | 154 VDDIOPO GPIO PA14 GP |             |        |           | Α                               | FLEXCOM2_IO1 | 1              |              |                              |                                        |   |

| 154     |                          | IOPO GPIO P | GPIO P | GPIO PA14 | PA14 GPIO                       | -            | В              | FLEXCOM5_IO3 | 1,2                          | PIO, I, PU, ST                         | _ |

|         |                          |             |        | 3.13      |                                 | С            | FLEXCOM4_IO5   | 1            |                              |                                        |   |

|         | continued  |          |        |      |                  |      |                |     |                              |                                     |

|---------|------------|----------|--------|------|------------------|------|----------------|-----|------------------------------|-------------------------------------|

|         |            |          | Prin   | nary |                  |      | PIO Peripheral |     | Reset State <sup>(1)</sup>   |                                     |

| Pad No. | Power Rail | I/O Type | Signal |      | Alternate Signal | Func | Signal         |     | Signal, Dir, PU, PD, HiZ, ST | Note                                |

|         |            |          |        |      |                  | Α    | TIOA0          | 1   |                              |                                     |

| 162     | VDDIOP0    | GPIO     | PA15   | GPIO | _                | В    | FLEXCOM5_IO1   | 1,2 | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_R0      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TIOA1          | 1   |                              |                                     |

| 160     | VDDIOP0    | GPIO     | PA16   | GPIO | _                | В    | FLEXCOM5_IO0   | 1,2 | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_R1      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TIOA2          | 1   |                              |                                     |

| 171     | VDDIOP0    | GPIO     | PA17   | GPIO | _                | В    | FLEXCOM5_IO2   | 1,2 | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_R2      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TCLK0          | 1   |                              |                                     |

| 170     | VDDIOP0    | GPIO     | PA18   | GPIO | _                | В    | TK             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_L0      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TCLK1          | 1   |                              |                                     |

| 167     | VDDIOP0    | GPIO     | PA19   | GPIO | _                | В    | TF             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_L1      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TCLK2          | 1   |                              |                                     |

| 155     | VDDIOP0    | GPIO     | PA20   | GPIO | WKUP4            | В    | TD             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_L2      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TIOB0          | 1   |                              |                                     |

| 168     | VDDIOP0    | GPIO     | PA21   | GPIO | _                | В    | RD             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_L3      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TIOB1          | 1   |                              |                                     |

| 164     | VDDIOP0    | GPIO     | PA22   | GPIO | _                | В    | RK             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | CLASSD_R3      | 1   |                              |                                     |

|         |            |          |        |      |                  | Α    | TIOB2          | 1   |                              |                                     |

| 161     | VDDIOP0    | GPIO     | PA23   | GPIO | _                | В    | RF             | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | С    | FLEXCOM2_IO7   | 1   |                              |                                     |

| 158     | VDDANA     | GPIO     | PA24   | GPIO | -                | Α    | FLEXCOM6_IO0   | 1   | PIO, I, PU, ST               | Used for TWI<br>PMIC <sup>(2)</sup> |

| 157     | VDDANA     | GPIO     | PA25   | GPIO | _                | Α    | FLEXCOM6_IO1   | 1   | PIO, I, PU, ST               | Used for TWI                        |

|         |            |          |        |      |                  |      | _              | 1   |                              | PMIC <sup>(2)</sup>                 |

| 140     | VDDANA     | GPIO     | PA26   | GPIO | AD2              | A    | DRXD           | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | В    | CANRX0         | 1   |                              |                                     |

| 136     | VDDANA     | GPIO     | PA27   | GPIO | AD3              | A    | DTXD           | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | В    | CANTX0         | 1   |                              |                                     |

| 139     | VDDANA     | GPIO     | PA28   | GPIO | AD4              | A    | FLEXCOM1_IO0   | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | В    | CANTX1         | 1   |                              |                                     |

| 141     | VDDANA     | GPIO     | PA29   | GPIO | AD5              | A    | FLEXCOM1_IO1   | 1   | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | В    | CANRX1         | 1   |                              |                                     |

| 120     | \\DD       | CDIO     | DAGG   | CDIC | PIO AD6 B        | A    | FLEXCOM0_IO0   | 1   | DIC I DI CT                  |                                     |

| 138     | VDDANA     | GPIO     | PA30   | GPIO |                  | В    | FLEXCOM5_IO4   |     | PIO, I, PU, ST               | _                                   |

|         |            |          |        |      |                  | C    | FLEXCOM4_IO4   | 2   |                              |                                     |

| 136     | VDDANA     | GPIO     | PA31   | GPIO | AD7              | A    | FLEXCOM0_IO1   | 1   | PIO, I, PU, ST               | (3)                                 |

|         |            |          |        |      |                  | В    | FLEXCOM4_IO5   | 2   |                              |                                     |

- 1. Signal = 'PIO' if GPIO; Dir = Direction; PU = Pull-up; PD = Pull-down; HiZ = High impedance; ST = Schmitt Trigger

- 2. This feature is fixed due to the SAM9X75 SOM Series internal connection.

- 3. Compared to SAM9X75 SiP, this feature is limited, as it is partly used for other SAM9X75 SOM Series features, for example GMAC or FLEXCOM.

## 7.2.2 PIOB Pin List

Table 7-2. PIOB Pin Description

|         |            |          | Prin   | nary | Alternation         |        | PIO Peripheral               |        | Reset State <sup>(1)</sup>      |                                             |

|---------|------------|----------|--------|------|---------------------|--------|------------------------------|--------|---------------------------------|---------------------------------------------|

| Pad No. | Power Rail | I/O Type | Signal | Туре | Alternate<br>Signal | Func   | Signal                       | IO Set | Signal, Dir, PU, PD,<br>HiZ, ST | Note                                        |

| -       | VDD_3V3    | GPIO     | PB0    | GPIO | -                   | Α      | GRX2                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB1    | GPIO | -                   | Α      | GRX3                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PB2    | GPIO | _                   | Α      | G125CK                       | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PB3    | GPIO | -                   | Α      | GCRSDV/GRXCTL                | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PB4    | GPIO | -                   | Α      | GTX2                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB5    | GPIO | -                   | Α      | GTX3                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PB6    | GPIO | -                   | Α      | GTXCK/GREFCK                 | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PB7    | GPIO | -                   | Α      | GTXEN/GTXCTL                 | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB8    | GPIO | -                   | Α      | GRXCK                        | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB9    | GPIO | -                   | Α      | GMDIO                        | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB10   | GPIO | -                   | Α      | GMDC                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB11   | GPIO | _                   | Α      | GRX0                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB12   | GPIO | -                   | Α      | GRX1                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB13   | GPIO | -                   | Α      | GTX0                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PB14   | GPIO | -                   | Α      | GTX1                         | 1      | PIO, I, PU, ST                  | Used for Gigabit<br>Ethernet <sup>(2)</sup> |

| 23      | VDD_3V3    | GPIO     | PB15   | GPIO | -                   | C<br>D | FLEXCOM11_IO0 I2SMCC_WS      | 1      | PIO, I, PU, ST                  | (3)                                         |

| 25      | VDD_3V3    | GPIO     | PB16   | GPIO | -                   | С      | FLEXCOM11_IO1<br>I2SMCC_DIN0 | 1      | PIO, I, PU, ST                  | (3)                                         |

|         |            |          |        |      |                     | D<br>C | FLEXCOM12_IO0                | 1      |                                 |                                             |

| 26      | VDD_3V3    | GPIO     | PB17   | GPIO | =                   | D      | I2SMCC_DOUT0                 | 1      | PIO, I, PU, ST                  | (3)                                         |

|         |            |          |        |      |                     | В      | ADTRG                        | 1      |                                 |                                             |

| 27      | VDD_3V3    | GPIO     | PB18   | GPIO | WKUP7               | С      | FLEXCOM12_IO1                | 1      | PIO, I, PU, ST                  | (3)                                         |

|         |            |          |        |      |                     | D      | IRQ                          | 1      |                                 |                                             |

| c       | continued  |          |        |      |           |      |                |        |                                 |                                        |  |

|---------|------------|----------|--------|------|-----------|------|----------------|--------|---------------------------------|----------------------------------------|--|

|         |            |          |        | nary | Alternate |      | PIO Peripheral |        | Reset State <sup>(1)</sup>      |                                        |  |

| Pad No. | Power Rail | I/O Type | Signal | Туре | Signal    | Func | Signal         | IO Set | Signal, Dir, PU, PD,<br>HiZ, ST | Note                                   |  |

| _       | VDD_3V3    | GPIO     | PB19   | GPIO | -         | Α    | QSCK           | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| 20      | VDD_3V3    | GPIO     | PB20   | GPIO | -         | Α    | QCS            | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| _       | VDD_3V3    | GPIO     | PB21   | GPIO | -         | Α    | Q100           | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| _       | VDD_3V3    | GPIO     | PB22   | GPIO | -         | Α    | QIO1           | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| _       | VDD_3V3    | GPIO     | PB23   | GPIO | -         | Α    | QIO2           | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| _       | VDD_3V3    | GPIO     | PB24   | GPIO | -         | Α    | QIO3           | 1      | PIO, I, PU, ST                  | Used for QSPI<br>memory <sup>(2)</sup> |  |

| 24      | VDD_3V3    | GPIO     | PB25   | GPIO | WKUP8     | D    | I2SMCC_MCK     | 1      | PIO, I, PU, ST                  | (3)                                    |  |

| 28      | VDD_3V3    | GPIO     | PB26   | GPIO | _         | D    | I2SMCC_CK      | 1      | PIO, I, PU, ST                  | (3)                                    |  |

- 1. Signal = 'PIO' if GPIO; Dir = Direction; PU = Pull-up; PD = Pull-down; HiZ = High impedance; ST = Schmitt Trigger.

- 2. This feature is fixed due to the SAM9X75 SOM Series internal connection.

- 3. Compared to SAM9X75 SiP, this feature is limited, as it is partly used for other SAM9X75 SOM Series features, for example GMAC or FLEXCOM.

## 7.2.3 PIOC Pin List

**Table 7-3.** PIOC Pin Description

| Dad No  | Dawer Dail            | L/O Tyma    | Prin   | nary                             | Altownsto Cignal |                | PIO Peripheral          |        | Reset State <sup>(1)</sup>   | Note                    |

|---------|-----------------------|-------------|--------|----------------------------------|------------------|----------------|-------------------------|--------|------------------------------|-------------------------|

| Pau No. | Power Rail            | 1/O Type    | Signal | Туре                             | Alternate Signal | Func           | Signal                  | IO Set | Signal, Dir, PU, PD, HiZ, ST | Note                    |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT0               | 1      |                              |                         |

| 59      | VDDIOP1               | GPIO        | PC0    | GPIO                             | -                | В              | ISC_D0                  | 1      | PIO, I, PU, ST               | _                       |

|         |                       |             |        |                                  |                  | С              | FLEXCOM7_IO0            | 1      |                              |                         |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT1               | 1      |                              |                         |

| 62      | VDDIOP1               | GPIO        | PC1    | GPIO - B ISC_D1 1 PIO, I, PU, ST | PIO, I, PU, ST   | _              |                         |        |                              |                         |

|         |                       |             |        |                                  |                  | С              | FLEXCOM7_IO1            | 1      |                              |                         |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT2               | 1      |                              |                         |

| 98      | VDDLVDS               | GPIO        | PC2    | GPIO                             | LVDS_D0_N        | В              | ISC_D2                  | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |

|         |                       |             |        |                                  |                  | С              | TIOA3                   | 1      |                              |                         |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT3               | 1      |                              |                         |

| 97      | VDDLVDS               | GPIO        | PC3    | GPIO                             | LVDS_D0_P        | В              | ISC_D3                  | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |

|         |                       |             |        |                                  |                  | С              | TIOB3                   | 1      |                              |                         |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT4               | 1      |                              |                         |

| 96      | VDDLVDS               | GPIO        | PC4    | GPIO                             | LVDS_D1_N        | В              | ISC_D4                  | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |

|         |                       |             |        |                                  |                  | С              | TCLK3                   | 1      |                              |                         |

|         |                       |             |        |                                  |                  | Α              | LCDC_DAT5               | 1      |                              |                         |

| 95      | VDDLVDS GPIO PC5 GPIO | D LVDS_D1_P | В      | ISC_D5                           | 1                | PIO, I, PU, ST | For LVDS <sup>(2)</sup> |        |                              |                         |

|         |                       |             |        |                                  |                  | С              | TIOA4                   | 1      |                              |                         |

| C       | ontinued            |          |           |       |                  |            |                |        |                              |                         |       |          |          |   |   |      |   |  |

|---------|---------------------|----------|-----------|-------|------------------|------------|----------------|--------|------------------------------|-------------------------|-------|----------|----------|---|---|------|---|--|

| 5 111   |                     | T        | Prim      | nary  | A1:              |            | PIO Peripheral |        | Reset State <sup>(1)</sup>   |                         |       |          |          |   |   |      |   |  |

| Pad No. | Power Rail          | I/O Type | Signal    | Туре  | Alternate Signal | Func       | Signal         | IO Set | Signal, Dir, PU, PD, HiZ, ST | Note                    |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT6      | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 104     | VDDLVDS             | GPIO     | PC6       | GPIO  | LVDS_D2_N        | В          | ISC_D6         | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | TIOB4          | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT7      | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 103     | VDDLVDS             | GPIO     | PC7       | GPIO  | LVDS_D2_P        | В          | ISC_D7         | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | TCLK4          | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT8      | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 55      | VDDIOP1             | GPIO     | PC8       | GPIO  | -                | В          | ISC_D8         | 1      | PIO, I, PU, ST               | _                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | FLEXCOM9_IO0   | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT9      | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 64      | VDDIOP1             | GPIO     | PC9       | GPIO  | _                | В          | ISC_D9         | 1      | PIO, I, PU, ST               | -                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | FLEXCOM9_IO1   | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT10     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 102     | VDDLVDS             | GPIO     | PC10      | GPIO  | LVDS_CLK_N       | В          | ISC_D10        | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | PWM0           | 3      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT11     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 101     | VDDLVDS             | GPIO     | PC11      | GPIO  | LVDS_CLK_P       | В          | ISC_D11        | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | PWM1           | 3      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT12     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 100     | VDDLVDS             | GPIO     | PC12      | GPIO  | LVDS_D3_N        | В          | ISC_PCK        | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | TIOA5          | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT13     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 99      | VDDLVDS             | GPIO     | PC13      | GPIO  | LVDS_D3_P        | В          | ISC_VSYNC      | 1      | PIO, I, PU, ST               | For LVDS <sup>(2)</sup> |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | TIOB5          | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT14     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 58      | VDDIOP1             | GPIO     | PC14      | GPIO  | _                | В          | ISC_HSYNC      | 1      | PIO, I, PU, ST               | -                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | TCLK5          | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT15     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 60      | VDDIOP1             | GPIO     | PC15      | GPIO  | _                | В          | ISC_MCK        | 1      | PIO, I, PU, ST               | _                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | PCK0           | 2      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT16     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 73      | VDDIOP1             | GPIO     | PC16      | GPIO  | _                | В          | ISC_FIELD      | 1      | PIO, I, PU, ST               | _                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | FLEXCOM10_IO0  | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT17     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 57      | VDDIOP1             | GPIO     | PC17      | GPIO  | -                | В          | FLEXCOM1_IO7   | 1      | PIO, I, PU, ST               | _                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | FLEXCOM10_IO1  | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | Α          | LCDC_DAT18     | 1      |                              |                         |       |          |          |   |   |      |   |  |

| 72      | VDDIOP1             | GPIO     | PC18      | GPIO  | -                | В          | FLEXCOM10_IO2  | 1      | PIO, I, PU, ST               | -                       |       |          |          |   |   |      |   |  |

|         |                     |          |           |       |                  | С          | PWM0           | 1      |                              |                         |       |          |          |   |   |      |   |  |

|         | 54 VDDIOP1 GPIO PC1 |          |           |       | Α                | LCDC_DAT19 | 1              |        |                              |                         |       |          |          |   |   |      |   |  |

| 54      |                     | GPIO     | GPIO PC19 | GPIO  |                  | В          | FLEXCOM10_IO3  | 1      | PIO, I, PU, ST               | -                       |       |          |          |   |   |      |   |  |

|         |                     |          | 20        | 2. 70 | 3.10             |            | 30             | 3.10   | G. 10                        | GI 10                   | G. 10 | GIO PC19 | C19 GPIO | - | С | PWM1 | 1 |  |

| c        | ontinued   |          |        |       |                  |      |                |        |                              |      |

|----------|------------|----------|--------|-------|------------------|------|----------------|--------|------------------------------|------|

| Dod No.  | Dawer Bail | L/O Time | Prim   | nary  | Altaurata Cianal |      | PIO Peripheral |        | Reset State <sup>(1)</sup>   | Nata |

| Pad No.  | Power Rail | і/О Туре | Signal | Туре  | Alternate Signal | Func | Signal         | IO Set | Signal, Dir, PU, PD, HiZ, ST | Note |

|          |            |          |        |       |                  | Α    | LCDC_DAT20     | 1      |                              |      |

| 71       | VDDIOP1    | GPIO     | PC20   | GPIO  | _                | В    | FLEXCOM10_IO4  | 1      | PIO, I, PU, ST               | _    |

|          |            |          |        |       |                  | С    | PWM2           | 1      |                              |      |

| 65       | VDDIOP1    | GPIO     | PC21   | GPIO  |                  | Α    | LCDC_DAT21     | 1      | PIO, I, PU, ST               | _    |

| 0.5      | VDDIOFI    | GFIO     | FCZI   | GFIO  | _                | С    | PWM3           | 1      | FIO, I, FO, 31               | _    |

| 66       | VDDIOP1    | GPIO     | PC22   | GPIO  | _                | Α    | LCDC_DAT22     | 1      | PIO, I, PU, ST               | _    |

| 00       | VDDIOI 1   | di io    | 1 (22  | di 10 | _                | В    | FLEXCOM3_IO0   | 1      | 110,1,10,31                  |      |

| 51       | VDDIOP1    | GPIO     | PC23   | GDIO  | WKUP9            | Α    | LCDC_DAT23     | 1      | PIO, I, PU, ST               | _    |

| J1       | VDDIOI 1   | di io    | 1 (23  | di 10 | WKOI 3           | В    | FLEXCOM3_IO1   | 1      | 110,1,10,31                  |      |

| 69       | VDDIOP1    | GPIO     | PC2/I  | GPIO  | WKUP10           | Α    | LCDC_DISP      | 1      | PIO, I, PU, ST               | _    |

| 03       | VDDIOI I   | di io    | 1 024  | di io | WKOI 10          | В    | FLEXCOM3_IO4   | 1      | 110,1,10,31                  |      |

|          |            |          |        |       |                  | Α    | NTRST          | 1      |                              |      |

| 61       | VDDIOP1    | GPIO     | PC25   | GPIO  | WKUP12           | В    | FLEXCOM3_IO3   | 1      | NRST_OUT, O, PD              | -    |

|          |            |          |        |       |                  | С    | NRST_OUT       | 1      |                              |      |

| 67       | VDDIOP1    | GPIO     | PC26   | GPIO  | WKUP13           | Α    | LCDC_PWM       | 1      | PIO, I, PU, ST               | _    |

| <u> </u> | VBBIOTT    | di 10    | 1 020  | di io | WIKOT 15         | В    | FLEXCOM3_IO2   | 1      | 110,1,10,31                  |      |

| 53       | VDDIOP1    | GPIO     | PC27   | GPIO  | _                | Α    | LCDC_VSYNC     | 1      | PIO, I, PU, ST               | _    |

| 33       | VBBIOTT    | di 10    | 1 (2)  | di io |                  | С    | FLEXCOM1_IO4   | 1      | 110,1,10,31                  |      |

| 70       | VDDIOP1    | GPIO     | PC28   | GPIO  | _                | Α    | LCDC_HSYNC     | 1      | PIO, I, PU, ST               | _    |

|          | VBBIOTT    | di 10    | 1 020  | GI 10 |                  | С    | FLEXCOM1_IO3   | 1      | 110,1,10,31                  |      |

| 52       | VDDIOP1    | GPIO     | PC29   | GPIO  | _                | Α    | LCDC_DEN       | 1      | PIO, I, PU, ST               | _    |

|          |            | <u> </u> |        | 55    |                  | С    | FLEXCOM1_IO2   | 1      | ,                            |      |

| 68       | VDDIOP1    | GPIO     | PC30   | GPIO  | _                | Α    | LCDC_PCK       | 1      | PIO, I, PU, ST               | _    |

|          |            | J        |        | 55    |                  | С    | FLEXCOM3_IO7   | 1      | ,                            |      |

| 50       | VDDIOP1    | GPIO     | PC31   | GPIO  | WKUP11           | Α    | FIQ            | 1      | PIO, I, PU, ST               | _    |

|          |            | 0.10     |        | 3, 10 | WKUPTT           | С    | PCK1           | 2      | 1 10,1,1 0,31                |      |

- 1. Signal = 'PIO' if GPIO; Dir = Direction; PU = Pull-up; PD = Pull-down; HiZ = High impedance; ST = Schmitt Trigger.

- 2. The design is optimized for this feature.

## 7.2.4 PIOD Pin List

Table 7-4. PIOD Pin Description

|         |            |          | Pri    | mary | Alternate | PIO Peripheral |             |        | Reset State <sup>(1)</sup>      |                                                |

|---------|------------|----------|--------|------|-----------|----------------|-------------|--------|---------------------------------|------------------------------------------------|

| Pad No. | Power Rail | I/O Type | Signal | Туре | Signal    | Func           | Signal      | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST | Note                                           |

| -       | VDD_3V3    | GPIO     | PD0    | GPIO | _         | Α              | NANDOE      | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup>             |

| -       | VDD_3V3    | GPIO     | PD1    | GPIO | _         | Α              | NANDWE      | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup>             |

| -       | VDD_3V3    | GPIO     | PD2    | GPIO | -         | Α              | A21/NANDALE | 1      | A21, O, PD                      | Used for NAND Flash <sup>(2)</sup>             |

| -       | VDD_3V3    | GPIO     | PD3    | GPIO | _         | Α              | A22/NANDCLE | 1      | A22, O, PD                      | Used for NAND Flash <sup>(2)</sup>             |

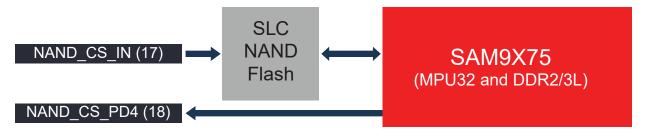

| 18      | VDD_3V3    | GPIO     | PD4    | GPIO | _         | Α              | NCS2/NANDCS | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup>             |

| -       | VDD_3V3    | GPIO     | PD5    | GPIO | _         | -              | _           | _      | PIO, I, PU                      | Used for Ethernet PHY interrupt <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PD6    | GPIO | _         | Α              | NANDDAT0    | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup>             |

| c       | ontinued   |          |        |        |           |      |                   |        |                                 |                                    |

|---------|------------|----------|--------|--------|-----------|------|-------------------|--------|---------------------------------|------------------------------------|

|         |            |          | Pri    | mary   | Alternate |      | PIO Peripheral    |        | Reset State <sup>(1)</sup>      |                                    |

| Pad No. | Power Rail | I/O Type | Signal | Туре   | Signal    | Func | Signal            | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST | Note                               |

| _       | VDD_3V3    | GPIO     | PD7    | GPIO   | -         | Α    | NANDDAT1          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PD8    | GPIO   | -         | Α    | NANDDAT2          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PD9    | GPIO   | -         | Α    | NANDDAT3          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| _       | VDD_3V3    | GPIO     | PD10   | GPIO   | -         | Α    | NANDDAT4          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| -       | VDD_3V3    | GPIO     | PD11   | GPIO   | -         | Α    | NANDDAT5          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| -       | VDD_3V3    | Ground   | PD12   | Ground | -         | Α    | NANDDAT6          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| _       | VDD_3V3    | Ground   | PD13   | Ground | -         | Α    | NANDDAT7          | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

| _       | VDD_3V3    | Ground   | PD14   | Ground | -         | Α    | NWAIT/<br>NANDRDY | 1      | PIO, I, PU                      | Used for NAND Flash <sup>(2)</sup> |

- 1. Signal = 'PIO' if GPIO; Dir = Direction; PU = Pull-up; PD = Pull-down; HiZ = High impedance; ST = Schmitt Trigger.

- 2. This feature is fixed due to the SAM9X75 SOM Series internal connection.

## 7.2.5 System Pin List

Table 7-5. System Pin Description

| Pin No. | Pin Name  | Power Rail | I/O Type | Description                                                 |

|---------|-----------|------------|----------|-------------------------------------------------------------|

| 114     | MIPI_D0_N | VDD_2V5    | DPHYIO   | MIPI DPHY negative differential output data lane 0          |

| 113     | MIPI_D0_P | VDD_2V5    | DPHYIO   | MIPI DPHY positive differential output data lane 0          |

| 112     | MIPI_D1_N | VDD_2V5    | DPHYIO   | MIPI DPHY negative differential output data lane 1          |

| 111     | MIPI_D1_P | VDD_2V5    | DPHYIO   | MIPI DPHY positive differential output data lane 1          |

| 110     | MIPI_D2_N | VDD_2V5    | DPHYIO   | MIPI DPHY negative differential output data lane 2          |

| 109     | MIPI_D2_P | VDD_2V5    | DPHYIO   | MIPI DPHY positive differential output data lane 2          |

| 108     | MIPI_D3_N | VDD_2V5    | DPHYIO   | MIPI DPHY negative differential output data lane 3          |

| 107     | MIPI_D3_P | VDD_2V5    | DPHYIO   | MIPI DPHY positive differential output data lane 3          |

| 116     | MIPI_CK_N | VDD_2V5    | DPHYIO   | MIPI DPHY negative differential output clock lane           |

| 115     | MIPI_CK_P | VDD_2V5    | DPHYIO   | MIPI DPHY positive differential output clock lane           |

| 123     | USBA_P    | VDD_3V3    | USBHS    | USB host port A high-speed data +                           |

| 122     | USBA_N    | VDD_3V3    | USBHS    | USB host port A high-speed data -                           |

| 121     | USBB_P    | VDD_3V3    | USBHS    | USB host port B high-speed data +                           |

| 120     | USBB_N    | VDD_3V3    | USBHS    | USB host port B high-speed data -                           |

| 119     | USBC_P    | VDD_3V3    | USBHS    | USB host port C high-speed data +                           |

| 118     | USBC_N    | VDD_3V3    | USBHS    | USB host port C high-speed data -                           |

| 125     | AUDIO_CLK | VDD_3V3    | CLOCK    | Audio clock output                                          |

| 78      | WKUP0     | VDDBU      | SYSC     | Wake-up input. $100k\Omega$ Internal Pull-Up.               |

| 79      | SHDN      | VDDBU      | SYSC     | Shutdown control                                            |

| 151     | JTAGSEL   | VDDBU      | SYSC     | JTAG selection                                              |

| 147     | JTAG_TCK  | VDD_3V3    | RSTJTAG  | Test clock                                                  |

| 148     | JTAG_TDI  | VDD_3V3    | RSTJTAG  | Test data in                                                |

| 152     | JTAG_TDO  | VDD_3V3    | RSTJTAG  | Test data out                                               |

| 149     | JTAG_TMS  | VDD_3V3    | RSTJTAG  | Test mode select                                            |

| 150     | JTAG_RTCK | VDD_3V3    | RSTJTAG  | Return test clock                                           |

| 77      | nRST      | VDD_3V3    | RSTJTAG  | External nReset input/output. $10k\Omega$ internal pull-up. |

|         | continued          |            |          |                                                                                   |

|---------|--------------------|------------|----------|-----------------------------------------------------------------------------------|

| Pin No. | Pin Name           | Power Rail | I/O Type | Description                                                                       |

| 17      | NAND_CS_IN         | VDD_3V3    | GPIO     | NAND Flash chip select input. $100k\Omega$ internal pull-up.                      |

| 19      | NAND_WP            | VDD_3V3    | GPIO     | NAND Flash write protect. $100k\Omega$ internal pull-up.                          |

| 31      | TXRXA_P            | AVDDL      | Analog   | Physical receive or transmit signal (+ differential)                              |

| 32      | TXRXA_N            | AVDDL      | Analog   | Physical receive or transmit signal (– differential)                              |

| 33      | TXRXB_P            | AVDDL      | Analog   | Physical receive or transmit signal (+ differential)                              |

| 34      | TXRXB_N            | AVDDL      | Analog   | Physical receive or transmit signal (– differential)                              |

| 35      | TXRXC_P            | AVDDL      | Analog   | Physical receive or transmit signal (+ differential)                              |

| 36      | TXRXC_N            | AVDDL      | Analog   | Physical receive or transmit signal (– differential)                              |

| 37      | TXRXD_P            | AVDDL      | Analog   | Physical receive or transmit signal (+ differential)                              |

| 38      | TXRXD_N            | AVDDL      | Analog   | Physical receive or transmit signal (– differential)                              |

| 44      | GMAC_LED5_ALLPHYAD | VDD_3V3    | GPIO     | Programmable LED5 output/PHY address strap pin                                    |

| 45      | GMAC_LED4_MAGJACK  | VDD_3V3    | GPIO     | Programmable LED4 output/MagJack register settings. $10k\Omega$ internal pull-up. |

| 46      | GMAC_LED3_PHYAD2   | VDD_3V3    | GPIO     | Programmable LED3 output/PHYAD2                                                   |

| 47      | GMAC_LED2_PHYAD1   | VDD_3V3    | GPIO     | Programmable LED2 output/PHYAD1                                                   |

| 48      | GMAC_LED1_PHYAD0   | VDD_3V3    | GPIO     | Programmable LED1 output/PHYAD0                                                   |

| 43      | GMAC_NRST          | VDD_3V3    | GPIO     | Gigabit PHY reset line. $10k\Omega$ internal pull-up.                             |

| 21      | QSPI_CS_IN         | VDD_3V3    | GPIO     | NOR Flash chip select input. $10k\Omega$ internal pull-up.                        |

| 22      | 125MHz_EN          | VDD_3V3    | GPIO     | 125-MHz clock generation enable input (Enable high)                               |

## 7.2.6 Power Pin List

Table 7-6. Power Pin Description

| Pin No. | Pin Name   | Power Rail | Type          | Description                                                                                                                                                                                                             |

|---------|------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81      | 5V_MAIN    | 5V_MAIN    | Input power   | 5V main input supply                                                                                                                                                                                                    |

| 90      | VDD_3V3    | VDD_3V3    | Output power  | 3.3V I/Os voltage output                                                                                                                                                                                                |

| 91      | VDD_3V3    | VDD_3V3    | Output power  | 3.3V I/Os voltage output                                                                                                                                                                                                |

| 82      | 5V_MAIN    | 5V_MAIN    | Input power   | 5V main input supply                                                                                                                                                                                                    |

| 92      | VDDIODDR   | VDDIODDR   | Output power  | 1.35V/1.8V memory voltage output                                                                                                                                                                                        |

| 93      | VDDIODDR   | VDDIODDR   | Output power  | 1.35V/1.8V memory voltage output                                                                                                                                                                                        |

| 85      | SELVL1     | 5V_MAIN    | Input         | VLDO1 Default Output Voltage Selection pin. Three-state input.                                                                                                                                                          |

| 84      | VLDO1      | VOUT1      | Output power  | VLDO1 output voltage                                                                                                                                                                                                    |

| 83      | VLDO2      | VOUT2      | Output power  | VLDO2 output voltage                                                                                                                                                                                                    |

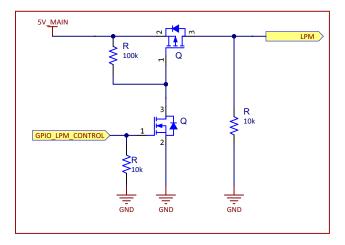

| 76      | LPM        | 5V_MAIN    | Input         | Low-Power Mode Input pin. In combination with PWRHLD and HPM, this pin defines the MCP16502 power mode status.                                                                                                          |

| 75      | nSTART_SOM | 5V_MAIN    | Input/Pull-up | Start event input. Drives nSTART_SOM to low to initiate a start-up sequence. nSTART_SOM is pulled up internally. A capacitor can be connected to automatically initiate a power-up sequence when the main supply rises. |

| 133     | VDDANA     | VDDANA     | Input power   | Analog voltage input                                                                                                                                                                                                    |

| 130     | VDDBU      | VDDBU      | Input power   | Backup voltage input                                                                                                                                                                                                    |

| 145     | VDDIOP0    | VDDIOP0    | Input power   | VDDIOP0 voltage input                                                                                                                                                                                                   |

| 105     | VDDIOP1    | VDDIOP1    | Input power   | VDDIOP1 voltage input                                                                                                                                                                                                   |

| 143     | VDDLVDS    | VDDLVDS    | Input power   | VDDLVDS voltage input                                                                                                                                                                                                   |

| 142     | VDD_2V5    | VDDOUT25   | Output power  | 2.5V output voltage                                                                                                                                                                                                     |

| continued                                                                                                                                                                                 |          |            |        |                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|--------|-------------------|

| Pin No.                                                                                                                                                                                   | Pin Name | Power Rail | Type   | Description       |

| 1, 2, 9, 16, 29, 30, 39, 40, 41, 42, 49, 56, 63, 74, 80, 86, 87, 88, 89, 94, 106, 117, 124, 126, 127, 128, 129, 131, 132, 134, 135, 144, 146, 153, 156, 159, 163, 166, 169, 172, 173, 174 | GND      | GND        | Ground | Ground connection |

## 8. Power Considerations

## 8.1 Power Supplies

Table 8-1. SAM9X75 SOM Series Power Supplies

| Pin No.  | Name             | Power Type | Output Current<br>Capability | Power Domain                                                                          |

|----------|------------------|------------|------------------------------|---------------------------------------------------------------------------------------|

| 130      | VDDBU            | Input      | -                            | Backup supply input                                                                   |

| 145, 105 | VDDIOP0, VDDIOP1 | Input      | -                            | VDDIOPx supplies input                                                                |

| 133      | VDDANA           | Input      | -                            | Analog supply input                                                                   |

| 90, 91   | VDD_3V3          | Output     | 600 mA                       | I/O supply and customer application output                                            |

| 92, 93   | VDDIODDR         | Output     | 600 mA                       | DDR memory supply and customer application output (1.8V for DDR2 and 1.35V for DDR3L) |

| 81, 82   | 5V_MAIN          | Input      | -                            | System power input                                                                    |

| 84       | VLDO1            | Output     | 300 mA                       | Adjustable output depending on application settings                                   |

| 83       | VLDO2            | Output     | 300 mA                       | Adjustable output depending on application settings                                   |

| 142      | VDDOUT25         | Output     | N/A                          | 2.5V output for LVDS interface. Do not use for any other purpose.                     |

| 143      | VDDLVDS          | Input      | -                            | I/O supply<br>LVDS interface supply input                                             |

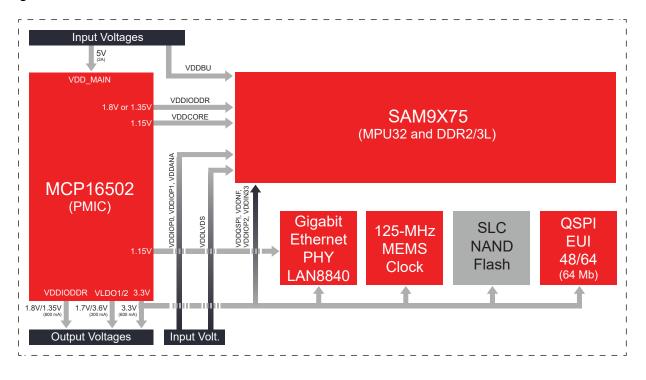

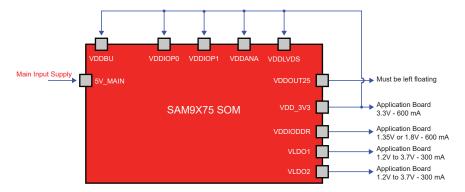

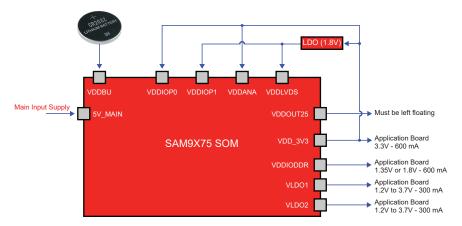

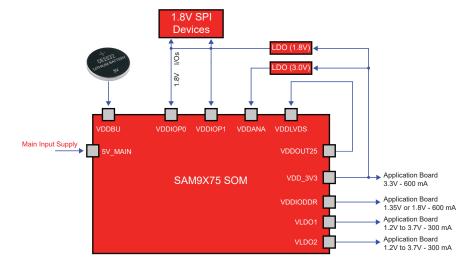

The Microchip SAM9X75 System-On-Module Series is supplied by a unique input (5V\_MAIN) and its internal supplies are delivered by a power management unit (MCP16502), as shown in the following figure.

Figure 8-1. SAM9X75 SOM Series Power Architecture

## 8.2 Power-Up/Power-Down Considerations

#### 8.2.1 System Power-Up

At power-up, from a power supply sequencing perspective, the SAM9X75 SOM Series power supplies are categorized into seven independent groups:

- 5V\_MAIN (main supply)

- VDDBU (backup group)

- VDD\_3V3 (internal periphery group) containing VDDIN33, VDDQSPI, VDDIOP2 and VDDNF inputs

- External VDD\_PERIPH (external periphery group) containing VDDANA, VDDIOP0, and VDDIOP1 inputs

- VDDLVDS and VDDMIPI (video group)

- VDDIODDR (memory group)

- VDDCORE (core group)

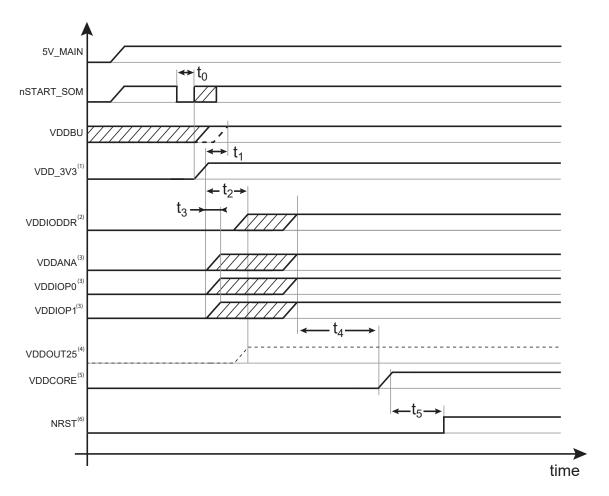

Figure 8-2 shows the recommended power-up sequence.

#### **Notes:**

- VDDBU

- When supplied from a precharged storage element (battery, supercapacitor or microbattery), VDDBU is an always-on supply input and is therefore not part of the power supply sequencing.

- When no storage element is used on VDDBU in the application, VDDBU must be tied to VDD 3V3.

- When a supercapacitor or a micro-battery is used in the application to power VDDBU in Backup mode, this element must be isolated from VDDBU during its (slow) charge, so that VDDBU closely follows VDD\_3V3. In Table 8-2, the parameter t<sub>1</sub> limits the delay to establish VDDBU after VDD 3V3.

- VDDOUT25 is the output of the internal 2.5V regulator, and therefore there is no power supply requirement on this pin.

Figure 8-2. Recommended Power-Up Sequence

- 1. VDD\_3V3 is generated internally by the MCP16502 PMIC and directly supplies the internal periphery group.

- 2. VDDIODDR is generated internally by the MCP16502 PMIC and directly supplies the memory group.

- 3. This group is supplied externally and requires no specific order. Only timing  $t_3$  must be respected.

- 4. VDDOUT25 is generated internally by the SAM9X75 SiP device and can be used to directly supply the internal video group.

- 5. VDDCORE is generated internally by the MCP16502 PMIC and directly supplies the core group.

- 6. The RESET general signal is generated internally by the MCP16502 PMIC and is distributed to the whole system.

Table 8-2. Power-Up Timing Requirements

| Symbo          | Parameter                     | Conditions <sup>(1)</sup>                                 | Min | Typ <sup>(2)</sup> | Max | Unit |

|----------------|-------------------------------|-----------------------------------------------------------|-----|--------------------|-----|------|

| t <sub>0</sub> | nSTRT deglitch time           | nSTRT pin falling edge                                    | -   | 0.5                | -   | ms   |

| t <sub>1</sub> | VDDBU delay                   | Delay from established VDD_3V3 to established VDDBU       | -   | -                  | 0.2 | ms   |

| t <sub>2</sub> | VDD_3V3 to memory group delay | Delay from established VDD_3V3 to VDDIODDR supply turn-on | -   | 8                  | -   | ms   |

|                | continued                                                |                                                                               |     |                    |                |      |  |  |  |  |  |  |

|----------------|----------------------------------------------------------|-------------------------------------------------------------------------------|-----|--------------------|----------------|------|--|--|--|--|--|--|

| Symbol         | Parameter                                                | Conditions <sup>(1)</sup>                                                     | Min | Typ <sup>(2)</sup> | Max            | Unit |  |  |  |  |  |  |

| t <sub>3</sub> | VDD_3V3 to external periphery group delay <sup>(3)</sup> | Delay from established VDD_3V3 to external periphery group established supply | 0   | -                  | t <sub>2</sub> | ms   |  |  |  |  |  |  |

| t <sub>4</sub> | Periphery group to VDDCORE delay                         | Delay from periphery group established supply to VDDCORE supply turn-on       | -   | 4                  | -              | ms   |  |  |  |  |  |  |

| t <sub>5</sub> | Reset delay at power-up                                  | From established VDDCORE to NRST high                                         | -   | 16                 | -              | ms   |  |  |  |  |  |  |

- 1. The term "established" refers to a power supply having reached 90% of its final value.

- 2. Typical timing values can be programmed in MCP16502 registers (RSTDLY[2:0]), but they must follow the timing sequence required by the SAM9X75 SiP device.

- 3. If one of the power inputs of the group is supplied externally, the power must be applied at the same time or after the presence of VDD\_3V3 and before the presence of VDDIODDR.

#### 8.2.2 System Power-Down

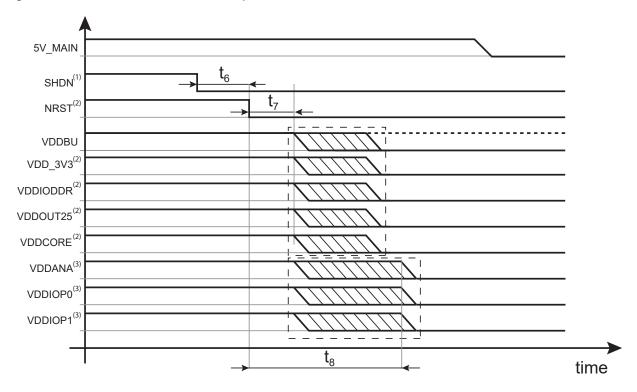

The following figure shows the SAM9X75 SOM Series power-down sequence that starts by asserting the SHDN line to "0".

Once SHDN and NRST are asserted, the supply inputs can be immediately shut down without any specific timing or order. VDDBU may not be shut down if the application uses a backup storage element on this supply input.

Figure 8-3. Recommended Power-Down Sequence

- 1. SHDN is generated internally by a software request from the SAM9X75 SiP device.

- 2. All these signals and power rails are controlled internally by the MCP16502 PMIC and are switched off at the same time.

- 3. This group is supplied externally and requires no specific order. Only timing t<sub>8</sub> must be respected.

Table 8-3. Power-Down Timing Requirements

| Symbol         | Parameter                                  | Conditions                                                      | Min            | Тур | Max | Unit |

|----------------|--------------------------------------------|-----------------------------------------------------------------|----------------|-----|-----|------|

| t <sub>6</sub> | SHDN to NRST<br>delay at power-<br>down    | Delay from<br>asserted SHDN<br>to NRST<br>generation            | 0              | -   | 10  | μs   |

| t <sub>7</sub> | NRST delay at power-down                   | Delay from<br>asserted NRST<br>to first supply<br>turn-off      | 0              | -   | 10  | μs   |

| t <sub>8</sub> | External supply<br>delay at power-<br>down | Delay from<br>asserted NRST<br>to external<br>supplies turn-off | t <sub>7</sub> | -   | 1   | ms   |

#### 8.2.3 Particular Considerations

Using the MCP16502, the system can be configured for automatic start-up (see Power Management Unit). Start-up occurs as soon as 5V\_MAIN voltage is present, provided that an external capacitor is connected on nSTART\_SOM (pin 75).

For this configuration, the external capacitor value must be selected with great care. The recommendations described in the MCP16502 PMIC data sheet under "nSTRT Capacitor for Automatic Turn-On on VIN Ramping" must be followed. For more information, refer to the MCP16502 PMIC data sheet (see Reference Documents).

## 8.3 Power Management Unit

The Microchip SAM9X75 System-On-Module Series is supplied by an external 5V supply (5V\_MAIN) and generates its own internal supplies by interfacing with the Microchip MCP16502 power management unit.

The MCP16502 is a fully-featured Power Management Integrated Circuit (PMIC), cost and size-optimized for Microchip MPU devices such as the SAM9X75 SiP.

The MCP16502 integrates four DC-DC buck regulators used for system supplying and two auxiliary LDOs for customer purpose.

- All buck channels can support loads up to 1A. All bucks are 100% duty cycle capable.

- The DCDC1, set to 3.3V, supplies all pads of the embedded devices. This power rail also offers a 600-mA load to customer applications through VDD\_3V3 pins.

- The DCDC2, set to 1.35V, supplies the DDR3L memory and the DCDC2, set to 1.8V, supplies the DDR2 memory. This power rail also offers a 600-mA load to customer applications through VDDIODDR pins.

- The DCDC3, set to 1.15V, supplies the microprocessor core. It is used internally only.

- The DCDC4, set to 1.15V, supplies the Gigabit Ethernet digital core. It is used internally only.

- One 300-mA LDO is provided so that sensitive analog loads can be supported. The LDO output voltage, named VLDO1 (pin 84), is configured by a three-state pin named SEL\_VLDO1 (pin 85) at power-up and can deliver 1.8V, 2.5V or 3.3V. Other voltage values can be reached after system initialization by an I<sup>2</sup>C interface access.