# swissbit®

**Product Data Sheet** Addendum for 100-ball BGA

**Industrial** e·MMC Memory

EM-36 Series JEDEC e-MMC 5.1 compliant, BGA 100-ball

Industrial and Automotive Temperature Grade

Date: March 11, 2025 Revision: 1.04

# EM-36 Series - Industrial embedded MMC 5.1 5 - 80 GBytes, 100-ball BGA

# 1. Ordering Information

The following Table 1 lists the part number associated with the changes identified in this document.

Table 1: Available Part Numbers

| Capacity         | Part Number                  | Temperatur |

|------------------|------------------------------|------------|

| 5 GBytes (pSLC)  | SFEM005GB1ED1T0-I-5E-31P-STD | Industrial |

| 10 GBytes (pSLC) | SFEM010GB1ED1T0-I-5E-31P-STD | Industrial |

| 20 GBytes (pSLC) | SFEM020GB1ED1T0-I-6F-31P-STD | Industrial |

| 20 GBytes (pSLC) | SFEMo2oGB1ED1TB-I-CE-31P-STD | Industrial |

| 20 GBytes (pSLC) | SFEMo2oGB1ED1TB-A-CE-31P-STD | Automotive |

| 40 GBytes (pSLC) | SFEM040GB1ED1TB-I-EF-31P-STD | Industrial |

| 40 GBytes (pSLC) | SFEM040GB1ED1TB-A-EF-31P-STD | Automotive |

| 80 GBytes (pSLC) | SFEMo8oGB1ED1TB-I-VG-31P-STD | Industrial |

| 80 GBytes (pSLC) | SFEM080GB1ED1TB-A-VG-31P-STD | Automotive |

## 2. Product Changes

The 100-ball Industrial e·MMC 5.1 is identical to the Swissbit standard EM-36 device with the exceptions defined in the following section.

#### 2.1 Mechanical Specifications

Table 2: Physical Dimensions

| Physical Dimensions   |          | Unit |

|-----------------------|----------|------|

| Length                | 14±0.1   |      |

| Width                 | 18±0.1   | mm   |

| Thickness (Max)       | 1.4 max. |      |

| Weight (Max Capacity) | < 1      | g    |

#### 2.2 Physical description

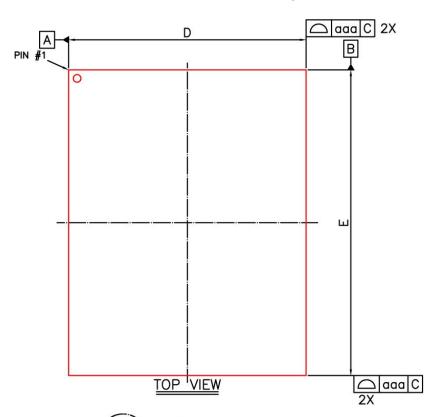

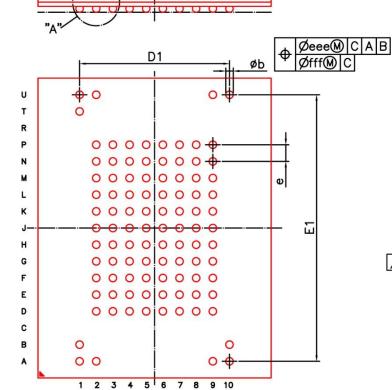

Figure 1: Mechanical dimensions eMMC

Package Mechanical (14 x 18 x 1.4mm)

|        | Dimension in mm |       |       |

|--------|-----------------|-------|-------|

| Symbol | MIN             | NOM   | MAX   |

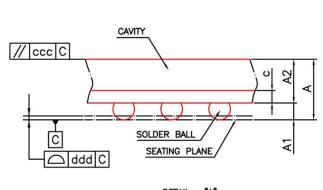

| Α      |                 |       | 1.40  |

| A1     | 0.30            | 0.35  | 0.40  |

| A2     | 0.86            | 0.91  | 0.96  |

| С      | 0.22            | 0.26  | 0.30  |

| D      | 13.90           | 14.00 | 14.10 |

| Е      | 17.90           | 18.00 | 18.10 |

| D1     |                 | 9.00  |       |

| E1     |                 | 16.00 |       |

| е      |                 | 1.00  | e     |

| b      | 0.40            | 0.45  | 0.50  |

| aaa    |                 | 0.15  |       |

| ccc    | 0.15            |       |       |

| ddd    | 0.12            |       |       |

| eee    |                 | 0.15  |       |

| fff    |                 | 0.08  |       |

**BOTTOM VIEW**

DETAIL: "A"

#### 2.3 Pinout

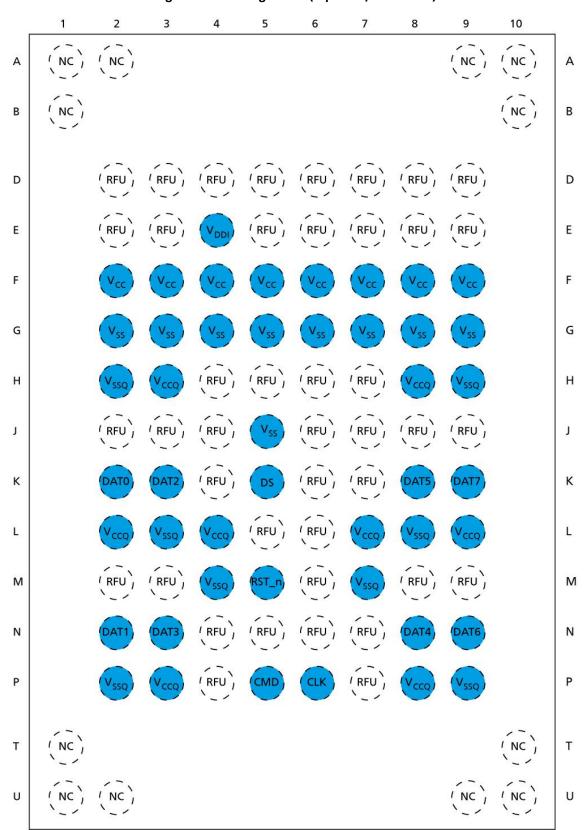

Figure 2: Ball assignment (top view, ball down)

Table 3: Pinout

| Name  | Type      | Ball No.                           | Description                                                                                                                                                                                      |  |

|-------|-----------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK   | 1         | P6                                 | Clock:<br>Each cycle directs a 1-bit transfer on the command and DAT<br>lines.                                                                                                                   |  |

| CMD   | I/O/PP/OD | P5                                 | Command: A bidirectional channel used for device initialization and command transfer. Command has two operating modes: 1) Open-drain for initialization. 2) Push-pull for fast command transfer. |  |

| DATo  | I/O/PP    | К2                                 | Data I/Oo: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT1  | I/O/PP    | N2                                 | Data I/01: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT2  | I/O/PP    | К3                                 | Data I/O2: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT3  | I/O/PP    | N <sub>3</sub>                     | Data I/03: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT4  | I/O/PP    | N8                                 | Data I/O4: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT5  | I/O/PP    | К8                                 | Data I/05: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT6  | I/O/PP    | N9                                 | Data I/06: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| DAT7  | I/O/PP    | К9                                 | Data I/07: Bidirectional channel used for data transfer.                                                                                                                                         |  |

| RST_n | 1         | M5                                 | Reset signal pin                                                                                                                                                                                 |  |

| VCC   | S         | F2, F3, F4, F5, F6, F7, F8, F9     | VCC: Flash memory I/F and Flash memory power supply.                                                                                                                                             |  |

| vccQ  | S         | H3, H8, L2, L4, L7, L9, P3, P8     | VCCQ : Memory controller core and MMC interface I/O power supply.                                                                                                                                |  |

| VSS   | S         | G2, G3, G4, G5, G6, G7, G8, G9, J5 | VSS: Flash memory I/F and Flash memory ground connection.                                                                                                                                        |  |

| VSSQ  | S         | H2, H9, L3, L8, M4, M7, P2, P9     | VSSQ: Memory controller core and MMC I/F ground connection.                                                                                                                                      |  |

| VDDi  |           | E4                                 | VDDi : Connect capacitor Creg from VDDi to GND.                                                                                                                                                  |  |

| DS    | O/PP      | К5                                 | Data Strobe: Newly assigned pin for HS400 mode.                                                                                                                                                  |  |

| NC    |           |                                    | Not connected                                                                                                                                                                                    |  |

| RFU   |           |                                    | Reserved for future use, leave floating                                                                                                                                                          |  |

<sup>1.</sup> I: input; O: output; PP: push-pull; OD: open-drain; NC: Not connected; S: power supply.

#### 2.4 Part Number change

To differentiate, the BGA form factor is encoded in the part number:

SFEMO05GB1ED1TO-I-5E-X1P-STD SFEM010GB1ED1TO-I-5E-X1P-STD SFEM020GB1ED1TO-I-6F-X1P-STD SFEM020GB1ED1TB-I-CE-X1P-STD SFEM020GB1ED1TB-A-CE-X1P-STD SFEM040GB1ED1TB-I-EF-X1P-STD SFEM040GB1ED1TB-A-EF-X1P-STD SFEM080GB1ED1TB-I-VG-X1P-STD SFEM080GB1ED1TB-A-VG-X1P-STD

x = BGA form type

| BGA form type        | Х |

|----------------------|---|

| 11.5 x 13mm, 153ball | 1 |

| 14 x 18mm, 100ball   | 3 |

For further details about our Industrial e·MMC 5.1, see our standard product data sheet or fact sheet of the EM-36 Series (<a href="http://www.swissbit.com">http://www.swissbit.com</a>).

Switzerland

## 3. Revision History

Table 4: Document Revision History

| Date        | Revision | Description                                                                       | Revision Details   |

|-------------|----------|-----------------------------------------------------------------------------------|--------------------|

| 18-Jun-2020 | 0.90     | Preliminary initial release                                                       | Doc. req. no. 3786 |

| 25-Feb-2021 | 1.00     | Initial release                                                                   | Doc. req. no. 4420 |

| 18-Jan-2022 | 1.01     | Added product variants, updated footer (doc. classification), preliminary release | Doc. req. no. 5160 |

| 07-Jul-2022 | 1.02     | Final release                                                                     | Doc. req. no. 5551 |

| 19-Sep-2023 | 1.03     | Added solder ball / SMD ball pad information.                                     | Doc. req. no. 6568 |

| 11-Mar-2025 | 1.04     | Added new variants and adjusted physical description                              | -                  |

#### Disclaimer:

No part of this document may be copied or reproduced in any form or by any means, or transferred to any third party, without the prior written consent of an authorized representative of Swissbit AG ("SWISSBIT"). The information in this document is subject to change without notice. SWISSBIT assumes no responsibility for any errors or omissions that may appear in this document and disclaims responsibility for any consequences resulting from the use of the information set forth herein. SWISSBIT makes no commitments to update or to keep current information contained in this document. The products listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. Moreover, SWISSBIT does not recommend or approve the use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If a customer wishes to use SWISSBIT products in applications not intended by SWISSBIT, said customer must contact an authorized SWISSBIT representative to determine SWISSBIT willingness to support a given application. The information set forth in this document does not convey any license under the copyrights, patent rights, trademarks or other intellectual property rights claimed and owned by SWISSBIT. The information set forth in this document is considered to be "Proprietary" and "Confidential" property owned by SWISSBIT.

ALL PRODUCTS SOLD BY SWISSBIT ARE COVERED BY THE PROVISIONS APPEARING IN SWISSBIT'S TERMS AND CONDITIONS OF SALE ONLY, INCLUDING THE LIMITATIONS OF LIABILITY, WARRANTY AND INFRINGEMENT PROVISIONS. SWISSBIT MAKES NO WARRANTIES OF ANY KIND, EXPRESS, STATUTORY, IMPLIED OR OTHERWISE, REGARDING INFORMATION SET FORTH HEREIN OR REGARDING THE FREEDOM OF THE DESCRIBED PRODUCTS FROM INTELLECTUAL PROPERTY INFRINGEMENT AND EXPRESSLY DISCLAIMS ANY SUCH WARRANTIES INCLUDING WITHOUT LIMITATION ANY EXPRESS, STATUTORY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

© 2025 SWISSBIT AG All rights reserved.

Switzerland