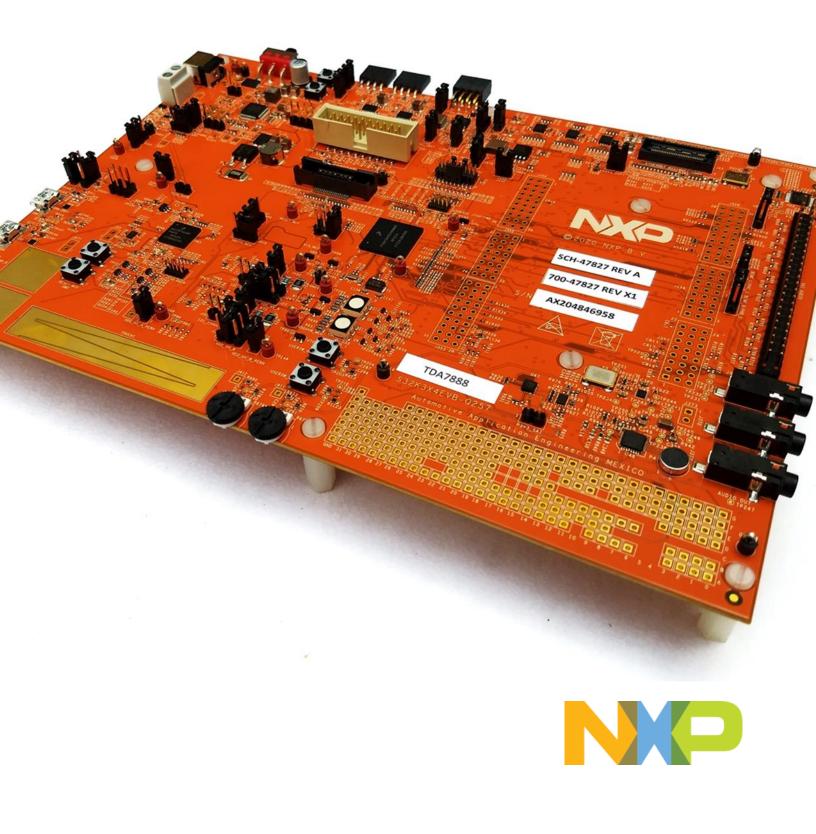

Customer Evaluation Board for S32K3x4 MCUs Hardware User Manual

# **1 Table of contents**

| 1    | Table of contents                              |    |

|------|------------------------------------------------|----|

| 2    | Definitions, Acronyms, and Abbreviations       | 3  |

| 3    | Block Diagram                                  | 4  |

| 4    | Features                                       | 4  |

| 5    | Default Configuration                          |    |

| 6    | S32K3X4EVB-Q257 and S32K3X4EVBQ257ND - Startup | 7  |

| 7    | Power supply                                   |    |

| 7.1  | S32K3X4EVB-Q257 - Main Power Supply            | 9  |

| 7.2  | S32K3X4EVB-Q257 – FS26/Modes Operation         | 10 |

| 7.3  | S32K3X4EVB-Q257 – +5.0 Volts Power Supply      | 11 |

| 7.4  | S32K3X4EVB-Q257 – +3.3 Volts Power Supply      | 12 |

| 7.5  | S32K3X4EVB-Q257 – VDD_HV_A                     | 12 |

| 8    | Programming and Debug Interface                | 17 |

| 8.1  | RESET Switch and LED indicator                 |    |

| 8.2  | On-board S32K3 Debugger                        | 17 |

| 9    | USB to Serial Interface                        | 19 |

| 10   | LIN Interface                                  | 21 |

| 11   | CAN Interface                                  | 23 |

| 12   | Ethernet Interface                             | 25 |

| 13   | Ethernet MII/RMII Connector – Pinout           | -  |

| 14   | QSPI-A Configuration                           | 28 |

| 15   | User Peripherals                               | 29 |

| 15.1 | 1 GPIO Matrix                                  | 29 |

| 15.2 |                                                |    |

| 15.3 |                                                |    |

| 15.4 |                                                |    |

| 16   | Default Jumpers                                |    |

| 17   | Revision history                               | 35 |

| 18   | Legal Information                              |    |

| 18.1 | 1 Definitions                                  | 36 |

| 18.2 |                                                |    |

| 18.3 | 3 Trademarks                                   | 36 |

|      |                                                |    |

# **2** Definitions, Acronyms, and Abbreviations

The following list defines the abbreviations used in this document.

| CD<br>CMOS<br>CPLD<br>CPU<br>CSI<br>CSPI<br>DDR<br>DIP<br>EEPROM<br>GPIO<br>GPO<br>I2C<br>ICE<br>I/O<br>JTAG<br>LAN<br>LCD<br>LED<br>MB<br>MCU<br>MMC<br>MCD<br>MMC<br>MMC<br>MMC<br>MMC<br>MMC<br>MMC<br>MMC<br>MMC | Compact Disk<br>Complementary Metal Oxide Semiconductor<br>Custom Programmed Logic Devices<br>Central Processing Unit<br>Camera Sensor Imaging<br>Serial Peripheral Interface<br>Double Data Rate<br>Dual In-line Package<br>Electrically Erasable Programmable Read Only Memory<br>Erasable Programmable Read Only Memory<br>General Purpose Input/output<br>General Purpose Input/output<br>Inter-Integrated Circuit<br>In-Circuit Emulator<br>Input/output<br>Joint Test Access Group<br>Local Area Network<br>Liquid Crystal Display<br>Light Emitting Diode<br>Megabyte<br>Microcontroller Unit<br>Multi-Media Card<br>Multi-chip product<br>Memory Stick<br>Non-volatile Random-Access Memory<br>Personal Computer<br>Printed Circuit Board<br>Physical interface<br>Power on Reset<br>Pseudo Random Access Memory<br>Power<br>Pulse Width Modulation<br>Graphics Adapter<br>Random Access Memory<br>Synchronous Dynamic Random-Access Memory<br>Synchronous Dynamic Random-Access Memory<br>System International (international system of units and measures)<br>Single In-Line Memory Module<br>Single Pole Single Throw<br>Thin Film Transistor<br>Universal Asynchronous Receiver/Transmitter<br>Universal Asynchronous Receiver/Transmitter<br>Universal Asynchronous Receiver/Transmitter<br>Universal Asynchronous Receiver/Transmitter<br>Universal Serial Bus.<br>Hardware. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB<br>HW<br>POP                                                                                                                                                                                                     | Universal Serial Bus.<br>Hardware.<br>Populate – Component placed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DNP                                                                                                                                                                                                                  | Do not populate – Component removed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

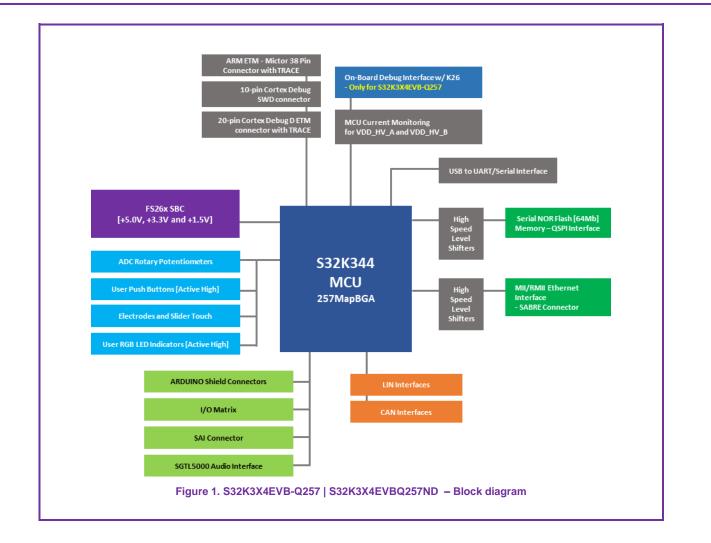

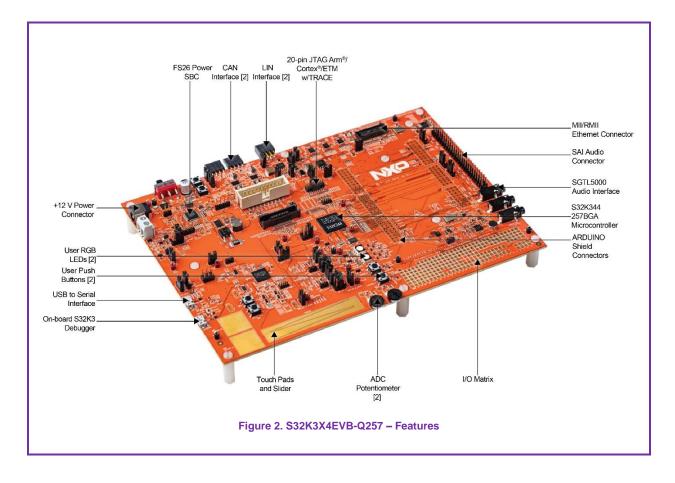

# **3 Block Diagram**

## 4 Features

# **5 Default Configuration**

#### Table 1. S32K3X4EVB-Q257 - Default Configuration

| Interface              | S32K3X4<br>EVB-<br>Q257 | S32K3X4<br>EVBQ257<br>ND | Reference / Signal | Configuration              | Description/Comment                                                    |

|------------------------|-------------------------|--------------------------|--------------------|----------------------------|------------------------------------------------------------------------|

| MCU<br>Power<br>Supply | •                       | •                        | VDD_HV_A_MCU       | +5.0V                      | The VDDA_HV_A domain is connected<br>to +5.0V– Switching Power Supply  |

| Зарріу                 | •                       | •                        | VDD_HV_B_MCU       | +3.3V                      | The VDDA_HV_B domain is connected<br>to +3.3V– Switching Power Supply  |

|                        | •                       | •                        | VDD_REFH_MCU       | [VDD_HV_A]                 | The VDD_REFH domain is connected to VDD_HV_A_MCU                       |

|                        | •                       | •                        | V15_MCU            | External NPN<br>Transistor | The V15_MCU domain is routed to the<br>external NPN Ballast Transistor |

| Ethernet               | •                       | •                        | J63                | MII/RMII<br>Enabled        | Ethernet MII signals are routed to ENET SABRE connector.               |

S32K3X4EVB-Q257 HWUM

| Interface                  | S32K3X4<br>EVB-<br>Q257 | S32K3X4<br>EVBQ257<br>ND | Reference / Signal | Configuration | Description/Comment                                           |

|----------------------------|-------------------------|--------------------------|--------------------|---------------|---------------------------------------------------------------|

| QSPI-A<br>Memory           | •                       | •                        |                    | Enabled       | The MCU signals to the QSPI-A Memory<br>Interface are enabled |

| Open SDA                   | •                       |                          |                    | PTA15         | PTA15/LPUART6_RX is routed to<br>OpenSDA for serial interface |

|                            |                         |                          |                    | PTA16         | PTA16/LPUART6_TX is routed to<br>OpenSDA for serial interface |

| USB to Serial<br>Interface | •                       | •                        |                    | PTC26         | PTC26/LPUART3_RX is routed to the USB2UART Interface          |

|                            |                         |                          |                    | PTC27         | PTC27/LPUART3_TX is routed to the USB2UART Interface          |

| CAN                        | TJA1153                 | TJA1043                  | /CAN0              | PTA6          | CAN0_RX is routed to CAN Phy0                                 |

| Interface                  |                         |                          |                    | PTA7          | CAN0_TX is routed to CAN Phy0                                 |

|                            |                         |                          |                    | PTC23         | CAN0_ERRN is routed to PTC23 for<br>CAN Phy0                  |

|                            |                         |                          |                    | PTC21         | CAN0_EN is routed to PTC21 for CAN<br>Phy0                    |

|                            |                         |                          |                    | PTC20         | CAN0_STB is routed to PTC20 for CAN<br>Phy0                   |

|                            |                         |                          | /CAN1              | PTE14         | CAN4_RX is routed to PTE14 to CAN<br>Phy1                     |

|                            |                         |                          |                    | PTE3          | CAN4_TX is routed to PTE3 to CAN<br>Phy1                      |

|                            |                         |                          |                    | PTE8          | CAN1_ERRN is routed to PTE8 for CAN<br>Phy1                   |

|                            |                         |                          |                    | PTD15         | CAN1_EN is routed to PTD15 for CAN<br>Phy1                    |

|                            |                         |                          |                    | PTD13         | CAN1_STB is routed to PTD13 for CAN<br>Phy1                   |

| LIN                        | •                       | •                        | LIN1               | PTB9          | LPUART9_RX is routed to LIN Phy0                              |

| Interface                  | •                       | •                        |                    | PTB10         | LPUART9_TX is routed to LIN Phy0                              |

|                            |                         |                          | LIN2               | PTB28         | LPUART5_RX is routed to LIN Phy1                              |

|                            |                         |                          |                    | PTB27         | LPUART5_TX is routed to LIN Phy1                              |

| User Push<br>Buttons       | •                       | ●                        | SW4                | PTB26         | Active Low, before PTA0                                       |

|                            | •                       | •                        | SW5                | PTB19         | Active Low, before PTA1                                       |

| User LEDs                  | •                       | •                        | D32                | PTA29         | Red                                                           |

|                            | -                       | -                        |                    | PTA30         | Green                                                         |

|                            |                         |                          |                    | PTA31         | Blue                                                          |

|                            | •                       | •                        | D33                | PTB18         | Red                                                           |

|                            | -                       |                          |                    | PTB25         | Green                                                         |

|                            |                         |                          |                    | PTE12         | Blue                                                          |

| ADC<br>Potentio-           | •                       | ●                        | R672               | PTA11         | ADCPOT0 [R672] is routed to PTA11 -<br>ADC1_S10               |

| meters                     | •                       | •                        | R679               | PTA17         | ADCPOT1 [R679] is routed to PTA17 -<br>ADC2_S19               |

# 6 S32K3X4EVB-Q257 and S32K3X4EVBQ257ND -Startup

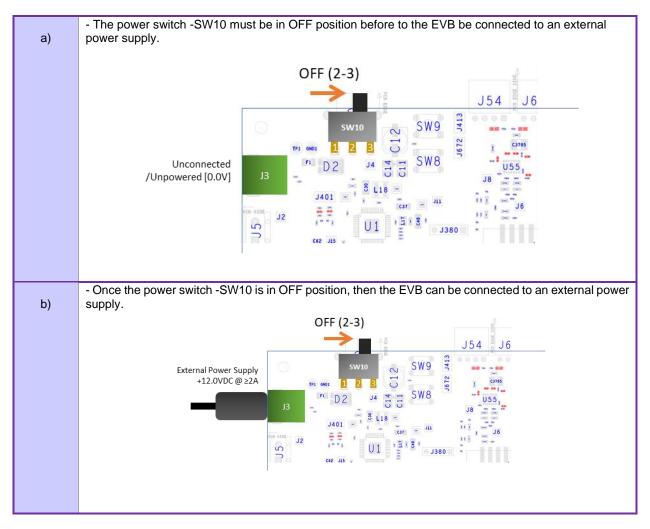

Follow these steps to connect and power on the board

- 1. Carefully unpack the S32K3X4EVB-Q257 and observe ESD preventive measures while handling the K3 development board.

- 2. Connect necessary cables between host PC and EVB board prior to applying power to the EVB.

- 3. The power-ON sequence for the EVB must be as follows:

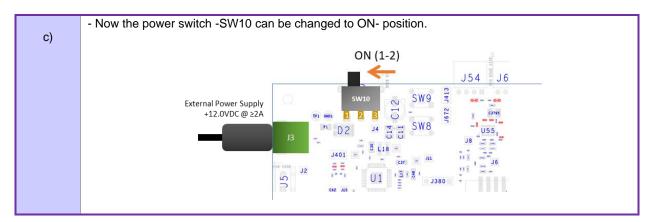

- 4. When power is applied to the EVB, three orange LED's adjacent to the voltage regulators show the presence of the supply voltages as follows:

- LED D34

- Indicates that the 12.0V is connected to the EVB correctly.

- LED D35 Indicates that the 5.0V linear regulator is enabled and working correctly.

- LED D36 Indicates that the +3.3Vlinear regulator is enabled and working correctly.

If no LED's are illuminated when power is applied to the EVB and the regulators are correctly enabled using the appropriate jumpers, it is possible that either power supply is not connected properly, or the voltage level is lower that the specified [+12.0V to ≥2Amps].

Note that the fuse will not protect against one of the EVB regulators being shorted. If this happens, damage is likely to occur to the EVB and / or components.

5. The board is ready to use now.

| 57 HWUM | All Information | provided in this | document is sub | ject to legal disclaimers |

|---------|-----------------|------------------|-----------------|---------------------------|

S32K3X4EVB-Q25

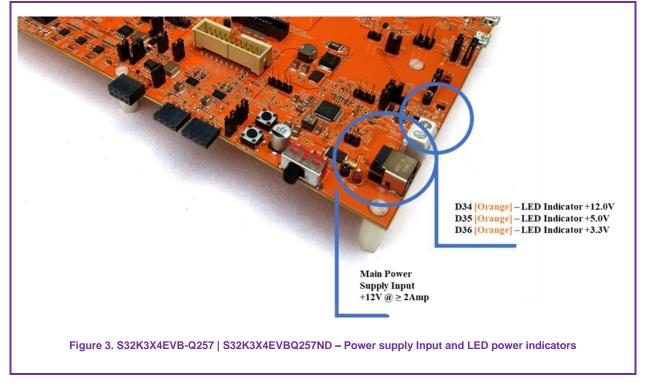

# 7 Power supply

The EVB requires an external power supply voltage of between to +12V/≥2A. This allows the EVB to be easily used in a vehicle if required. The 12v input is on the EVB is used to supply a FS26/SBC – U1, the power management IC controller provides +5.0V, +3.3V and +1.5V, for the different power configurations of VDD\_HV\_A, VDD\_HV\_B, V15 and other interfaces.

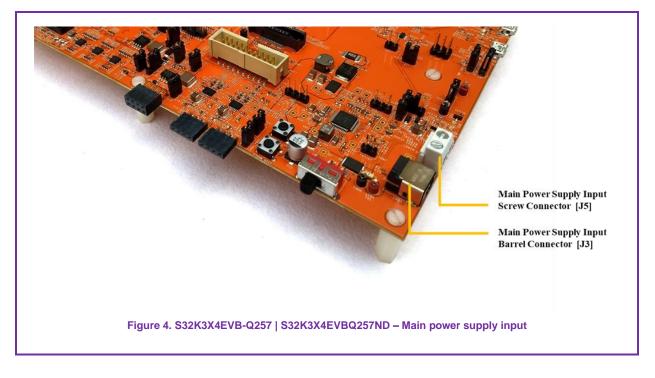

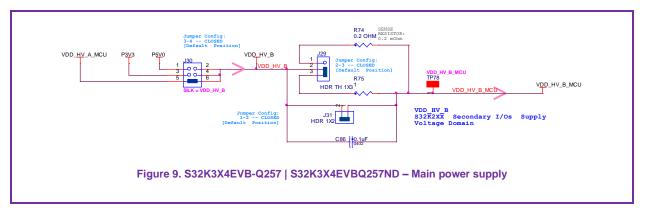

## 7.1 S32K3X4EVB-Q257 - Main Power Supply

#### Table 2. Main power supply connectors

| Connector                | Description                                                                                                                                                                                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground<br>V+ (+12Volts). | <b>2.1mm Barrel Connector – J3</b><br>This connector should be used to connect the supplied wall-plug mains<br>adapter. Note – if a replacement or alternative adapter is used, care must be<br>taken to ensure the 2.1mm plug uses the correct polarization as shown |

| Ground<br>V+ (12Volts).  | <b>2-Way Screw Type Connector – J5</b><br>This can be used to connect a bare wire lead to the EVB, typically from a laboratory power supply. The polarization of the connectors is clearly marked on the EVB. Care must be taken to ensure correct connection.        |

S32K3X4EVB-Q257 HWUM

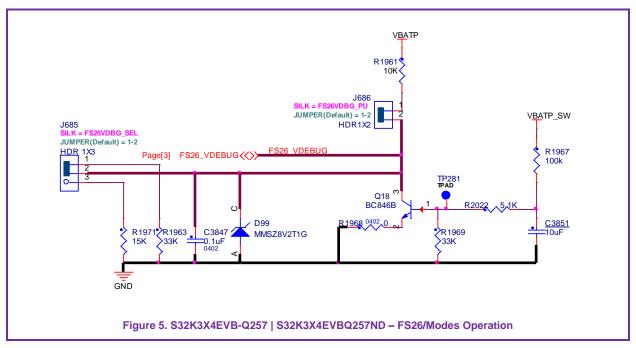

## 7.2 S32K3X4EVB-Q257 – FS26/Modes Operation

Table 3. S32K3X4EVB-Q257 – FS26/Modes Operation

| Reference                                | Jı   | umper Posi | tion       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comments |

|------------------------------------------|------|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Flash Mode<br>[Default<br>configuration] | J686 | 1-2        | 1          | The R1961 resistor to VBATP (VBAT<br>protected +12.0V) is routed as pull-up to the<br>VDEBUG Pin. This is a common pull-up<br>resistor for the 2 voltage divider<br>configurations, with R1971 or R1963.                                                                                                                                                                                                                                                     |          |

|                                          | J685 | 1-2        | 1 2<br>3   | The R1963 is selected for the divider<br>voltage, +8.0V is applied on VDEBUG pin to<br>set the FS26-SBC on MCU Flash Mode. In<br>this mode device power up sequence starts<br>with debug mode enabled and can be used<br>during customer production process to flash<br>MCU without need of WD refresh. After<br>~80ms once the SW10 is in ONposition the<br>VDEBUG pin will be switching to a low<br>voltage (GND) due to the RC delay circuitry<br>and Q18 |          |

| Debug<br>Mode                            | J686 | 1-2        | 1          | The R1961 resistor to VBATP (VBAT<br>protected +12.0V) is routed as pull-up to the<br>VDEBUG Pin. This is a common pull-up<br>resistor for the 2 voltage divider<br>configurations, with R1971 or R1963.                                                                                                                                                                                                                                                     |          |

|                                          | J685 | 2-3        | 1 2<br>3 1 | The R1963 is selected for the divider<br>voltage, +5.0V is applied on VDEBUG pin to<br>set the FS26-SBC on Debug Mode, voltage<br>must be removed from debug pin in order to<br>start power up sequence. In this mode<br>Watchdog refresh is not needed. After                                                                                                                                                                                               |          |

| Reference   | J             | umper Posi   | tion           | Description                                                                                                                                                                            | Comments |

|-------------|---------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             |               |              |                | ~80ms once the SW10 is in ONposition the VDEBUG pin will be switching to a low voltage (GND) due to the RC delay circuitry and Q18.                                                    |          |

| Normal Mode | J686          | OPEN         | 1              | In this mode the FS26 can enter Normal<br>mode by configuring the init fs window and<br>sending properly serviced watchdog refresh<br>by SPI. Please review the FS26<br>documentation. |          |

|             | J685          | OPEN         | 1<br>2<br>3    |                                                                                                                                                                                        |          |

| ŀ           | All change of | f jumpers mu | ust be done or | nce the EVB is unpowered from J3 and J5 as MA                                                                                                                                          | NDATORY  |

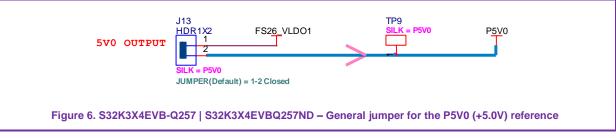

## 7.3 S32K3X4EVB-Q257 - +5.0 Volts Power Supply

#### Table 4. S32K3X4EVB-Q257 - +5.0 Volts Power Supply

| Reference | Jump | er Position | Description                                                                                             | Comments       |

|-----------|------|-------------|---------------------------------------------------------------------------------------------------------|----------------|

| J13       | 1-2  | 1           | The +5.0V output of the FS26x SBC [FS26_VLDO1] is routed to the main P5V0 domain (+5.0V for all board). | Default closed |

|           | OPEN | 1 2         | P5V0 domain (+5.0V for all board) is isolated/disconnected from the FS26x                               |                |

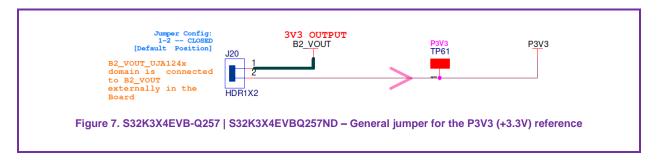

## 7.4 S32K3X4EVB-Q257 - +3.3 Volts Power Supply

### Table 5. S32K3X4EVB-Q257 – +.3.3 Volts Power Supply

| Reference | Jumper Position |      | Description                                                                                  | Comments       |

|-----------|-----------------|------|----------------------------------------------------------------------------------------------|----------------|

| J20       | 1               | 1-2  | The +3.3V Switching power supply is routed to the main P3V3 domain (+3.3V for all board).    | Default closed |

|           | 1               | OPEN | The +3.3V output of the FS26x SBC is isolated to the main P3V3 domain (+3.3V for all board). |                |

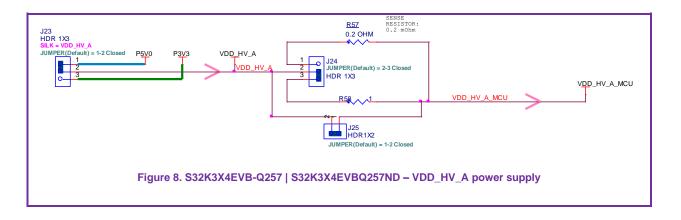

## 7.5 S32K3X4EVB-Q257 – VDD\_HV\_A

#### Table 6. S32K3X4EVB-Q257 – VDD\_HV\_A

| Reference | Jumper P   | osition | Description                                                                                                                                                      | Comments          |

|-----------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| J23       | 1 2 3 1    | 1-2     | P5V0 (+5.0V Switching Power Supply) is selected for the VDD_HV_A_MCU reference                                                                                   | Default<br>closed |

|           | 1 2<br>3 1 | 2-3     | P3V3_DC_SW (+3.3V Switching Power Supply) is selected<br>for the VDD_HV_A_MCU reference                                                                          |                   |

|           | 1 2<br>3   | OPEN    | VDD_HV_A domain is isolated and unpowered                                                                                                                        |                   |

| J24       | 1 2 3      | 1-2     | The shunt resistor R57 [0.2 Ohms] is selected for current measurement proposals on the VDD_HV_A_MCU reference                                                    |                   |

|           | 1 2<br>3   | 2-3     | The shunt resistor R58 [1 Ohms] is selected for current measurement proposals on the VDD_HV_A_MCU reference                                                      | Default<br>closed |

|           | 1 2<br>3 1 | OPEN    | The shunt resistors R57 and R58 are disabled for current measurement proposals on the VDD_HV_A_MCU reference                                                     |                   |

| J25       | 1          | 1-2     | VDD_HV_A is routed to VDD_HV_A_MCU reference. A jumper on this position disables the shunt resistors R57 and R58 are disabled for current measurement proposals. | Default<br>closed |

|           | 1          | OPEN    | This jumper allows a differential measurement to the shunt resistor in series for the VDD_HV_A_MCU domain.                                                       |                   |

## 7.5.1 S32K3X4EVB-Q257 – VDD\_HV\_B

#### Table 7. S32K3X4EVB-Q257 – VDD\_HV\_B

| Reference | Jumper Position                     | Description                                                                                                   | Comments       |

|-----------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------|

| J30       | 1 2 1-2<br>3 4<br>5 6               | P5V0 (+5.0V Switching Power Supply) is selected for the VDD_HV_B_MCU reference                                |                |

|           | 3-4<br>1 2<br>3 4<br>5 6            | P3V3_DC_SW (+3.3V Switching Power Supply) is selected for the VDD_HV_B_MCU reference                          |                |

|           | 1     2       3     4       5     6 | VDD_HV_A_MCU is routed to VDD_HV_B_MCU reference                                                              | Default closed |

|           | 1 2 OPEN<br>3 4 4<br>5 6            | VDD_HV_B domain is isolated and unpowered                                                                     |                |

|           | CAUTION - 2 or n                    | nore connections/jumpers in this header selector is NOT A                                                     | LLOWED         |

| J29       | 1 1-2<br>2 3                        | The shunt resistor R74 [0.2 Ohms] is selected for current measurement proposals on the VDD_HV_B_MCU reference |                |

S32K3X4EVB-Q257 HWUM

|     | 1 2<br>3    | 2-3  | The shunt resistor R75 [1 Ohms] is selected for current measurement proposals on the VDD_HV_B_MCU reference                                                               | Default closed |

|-----|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     | 1<br>2<br>3 | OPEN | The shunt resistors R74 and R75 are disabled for current measurement proposals on the VDD_HV_B_MCU reference                                                              |                |

| J31 | 1           | 1-2  | VDD_HV_B is routed to VDD_HV_B_MCU reference. A<br>jumper on this position disables the shunt resistors R74<br>and R75 are disabled for current measurement<br>proposals. | Default closed |

|     | 1           | OPEN | This jumper allows a differential measurement to the shunt resistor in series for the VDD_HV_B_MCU domain.                                                                |                |

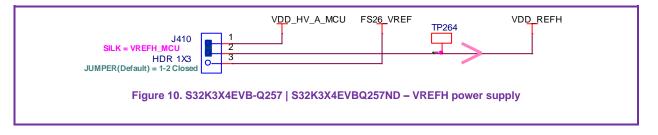

## 7.5.2 S32K3X4EVB-Q257 – VREFH

#### Table 8. S32K3X4EVB-Q257 – VREFH

| Reference | Jumper Po                              | sition | Description                                                               | Comments                                                                                                                             |

|-----------|----------------------------------------|--------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| J410      | 1 <b>1</b><br>2 <b>1</b><br>3 <b>1</b> | 1-2    | The VREFH_MCU reference is routed to the VDD_HV_A_MCU domain.             | Default closed                                                                                                                       |

|           | 1 2 1<br>3 1                           | 2-3    | The VREFH_MCU reference is routed to the FS26_VREF output domain [+5.0V]. | VREH_MCU should not be<br>connected to a higher voltage<br>than VDD_HV_A, therefore<br>J410[1-2] can be placed only<br>when J23[1-2] |

|           | 1 2<br>3 3                             | OPEN   | The VREFH_MCU is floated/unpowered                                        |                                                                                                                                      |

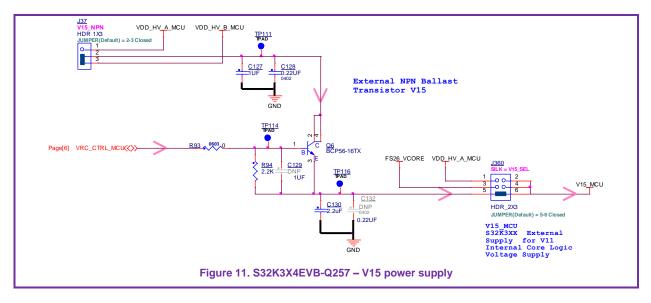

## 7.5.3 S32K3X4EVB-Q257 – V15

#### Table 9. S32K3X4EVB-Q257 - V15 Domain

| Reference | Jumper P | osition | Description                                                                                           | Comments          |

|-----------|----------|---------|-------------------------------------------------------------------------------------------------------|-------------------|

| J37       | 1        | 1-2     | The VDD_HV_A domain is routed to the collector terminal in order to supply the NPN external Ballast   |                   |

|           | 2        |         | transistor for the V15_MCU domain.                                                                    |                   |

|           | 3        |         |                                                                                                       |                   |

|           | 1        | 2-3     | The VDD_HV_B domain is routed to the collector terminal in order to supply the NPN external Ballast   | Default<br>closed |

|           | 2        |         | transistor for the V15_MCU domain.                                                                    |                   |

|           | 3        |         |                                                                                                       |                   |

|           | 1        | OPEN    | The VDD_HV_A and VDD_HV_B domains are isolated to supply the NPN external Ballast transistor for V15. |                   |

|           | 2        |         |                                                                                                       |                   |

|           | 3        |         |                                                                                                       |                   |

| J360      | 1 2      | 1-2     | The VDD_HV_A domain is directly routed the V15_MCU domain.                                            |                   |

|           | 3 4      |         |                                                                                                       |                   |

|           | 5 6      |         |                                                                                                       |                   |

|           | 1 2      | 2-3     | The FS26_VCORE domain [+1.5V] is directly routed the V15_MCU domain.                                  |                   |

|           | 3 4      |         |                                                                                                       |                   |

|           | 5 6      |         |                                                                                                       |                   |

| 1 2 | 5-6  | The NPN external Ballast transistor is selected to supply the V15_MCU domain.     | Default<br>closed |

|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 3 4 |      |                                                                                   |                   |

| 5 6 |      |                                                                                   |                   |

| 1 2 | OPEN | The V15_MCU domain is disconnected and isolated from the local external supplies. |                   |

| 3 4 |      |                                                                                   |                   |

| 5 6 |      |                                                                                   |                   |

# 8 Programming and Debug Interface

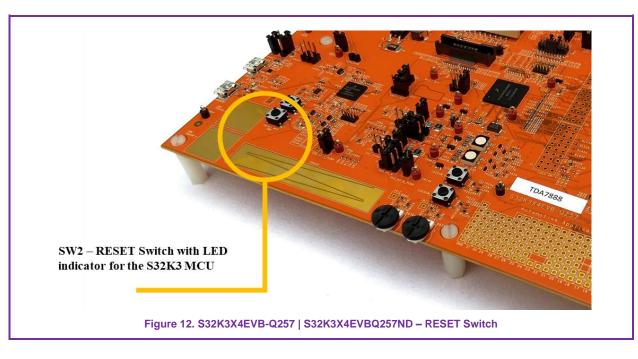

## 8.1 **RESET Switch and LED indicator**

The RESET switch [SW2] provides for manual application of the RESET input signal. The S32K3 MCU will drive the RESET signal to reset the EVB board peripherals. The RESET LED indicator [D22] will be ON for the duration of the RESET signal. This operation indicates the S32K344 MCU is in the Reset state.

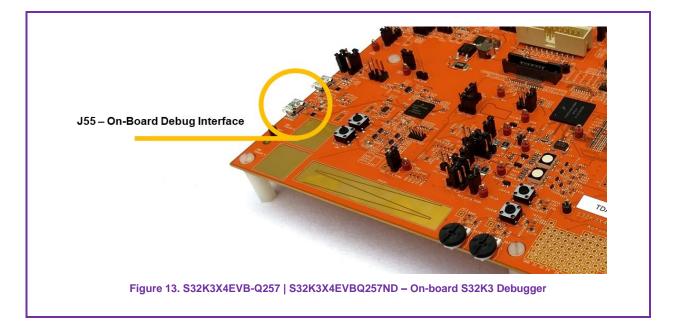

## 8.2 On-board S32K3 Debugger

The S32K3X4EVB-Q257 [only] incorporates an On-Board Debugger embedded well as JTAG connectors. It bridges serial and debug communications between a USB host and an embedded target processor.

S32K3X4EVB-Q257 HWUM

#### Table 10. Programming and Debug Connectors

| с                                         | onnector | S32K3X4EVB-Q257<br>S32K3X4EVBQ257ND |                                                                                                                                                                                                                | Descri                                                                                                          | ption                                                                                                                                                                   |

|-------------------------------------------|----------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Pin Cortex<br>Debug + ETM<br>Connector |          | J50                                 | SWD, SWV, JTAG<br>Cortex-M3/M4/M7<br>A 20-pin header (<br>dimensions:<br>0.50" x 0.188" (12.<br><b>NOTE - JTAG - TI</b><br>Due that the MCU<br>shared with other i<br>signals/interfaces<br><b>connector</b> . | i, and ÉTM<br>device.<br>Samtec FT<br>70 mm x 4.<br><b>RACE Sign</b><br>ports used<br>nterfaces. I<br>for the J | als<br>for the trace signals also are<br>t is important to isolate these<br>I4-Cortex Debug D ETM                                                                       |

|                                           |          |                                     | SIGNAL NAME                                                                                                                                                                                                    | MCU<br>PORT                                                                                                     | COMMENT                                                                                                                                                                 |

|                                           |          |                                     | TRACE_CLK                                                                                                                                                                                                      | PTB9                                                                                                            |                                                                                                                                                                         |

|                                           |          |                                     | TRACE_D0                                                                                                                                                                                                       | PTB8                                                                                                            |                                                                                                                                                                         |

|                                           |          |                                     | TRACE_D1                                                                                                                                                                                                       | PTE2                                                                                                            |                                                                                                                                                                         |

|                                           |          |                                     | TRACE_D2                                                                                                                                                                                                       | PTA14                                                                                                           |                                                                                                                                                                         |

|                                           |          |                                     | TRACE_D3                                                                                                                                                                                                       | PTA13                                                                                                           |                                                                                                                                                                         |

| 10-Pin Cortex<br>Debug<br>Connector       |          | J52                                 | Wire and JTAG in<br>10-pin (0.05") conr<br>access to all SWD<br>Cortex-Mx device.                                                                                                                              | terface mod<br>hector. This<br>, SWV, and<br>Samtec FT                                                          | r provides support for Serial<br>des in a very small, low cost<br>new style connector provides<br>JTAG signals available on a<br>SH-105-01) is specified with<br>8 mm). |

| 38-Pin ARM<br>ETM Mictor<br>Connector       | P1   | The Mictor (Matched Impedance Connector) has been the standard way to connect a trace probe to an ARM target. It supports up to 32-bit ETM trace and is really intended for use with very high-speed ARM processors such as Cortex-R4 and Cortex-A9. Cortex-M7 supports 16-bit data trace using the Mictor connector. This is only available with DS-5 using a DSTREAM debug and trace unit.                                                                                                   |

|---------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Pin ARM<br>Standard<br>JTAG<br>Connector | J365 | The ARM standard JTAG connector has been used for<br>many years in systems with ARM processors.<br>It supports the JTAG interface for accessing ARM7 and<br>ARM9 based devices. For Cortex-Mx devices, it supports<br>Serial Wire and JTAG interfaces for accessing all SWD,<br>SWV, and JTAG signals available on a Cortex-Mx device.<br>The header (e.g. a Samtec: TST-110-01-L-D) is a 20-Pin,<br>0.10" (2.54 mm) pitch connector with these dimensions: 1.3"<br>x 0.365" (33 mm x 9.27mm). |

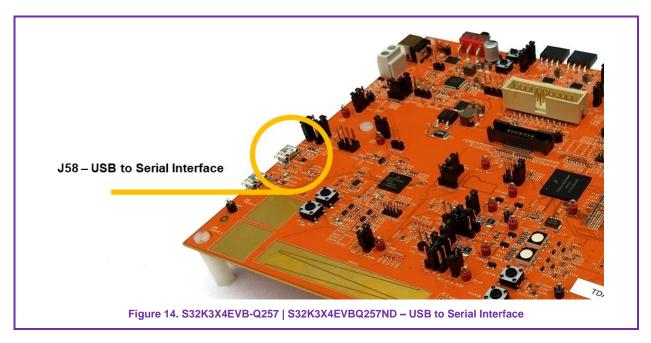

# **9 USB to Serial Interface**

The EVB incorporates an interface providing a serial connectivity via a direct USB connection between the PC and the EVB. The circuit contains an FTDI FT2232D USB to Serial interface which should automatically install the drivers for 2 additional COM ports on your PC. Note that only one of these is used so you will need to try both. For more information on the USB drivers and general fault finding, consult the FTDI website at <a href="http://www.ftdichip.com/">http://www.ftdichip.com/</a>

The PTC27 MCU port (LPUART13\_TX) and PTC26 MCU port (LPUART13\_RX) signals are routed to the FTDI transceiver via zero ohms resistors allowing the transceiver to be isolated from the MCU pin if desired. The default configuration is with the zero ohms resistors, routing the TX and RX signals from the MCU to the FTDI transceiver.

S32K3X4EVB-Q257 HWUM

| Signal MCU<br>/Module Port Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | Reference | Description | Comment                                           |                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|-------------|---------------------------------------------------|-----------------------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |           | R303        | LPUART13_RX signal is routed to FTDI<br>interface | Default configuración |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LPUART13_TX | PTC27     | R309        | LPUART13_TX signal is routed to FTDI<br>interface | Default configuración |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LPUART6_RX  | PTA15     | R302        | LPUART6_RX signal is routed to FTDI interface     |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LPUART6_TX  | PTA16     | R308        | LPUART6_TX signal is routed to FTDI interface     |                       |

| <ol> <li>If the user want use or change to LPUART6 RX/TX, then:         <ul> <li>R303 and R309 must be removed.</li> <li>R302-0603-0ohms and R308-0603-0ohms must be populated</li> </ul> </li> <li>If the user wants to use other LPUARTx RX/TX module of the MCU, the user can have access to the USB to serial interface by the J677 header. For this use case R302, R303, R308 and R309 must be removed.</li> <li>For a LPUARTx RX/TX module under the domain voltage VDD_HV_A, the R293 must be populated and R294 must be removed.</li> <li>For a LPUARTx RX/TX module under the domain voltage VDD_HV_B, the R294 must be populated and R293 must be removed.</li> </ol> |             |           |             |                                                   |                       |

#### Table 11. USB to serial interface - Control Jumpers

The USB to Serial UART interface in the EVB has two options to configure.

- USB Bus powered configuration.

- USB Self powered Configuration.

#### USB Bus Powered Configuration (*Default Configuration*).

The USB Bus Powered device gets its power from the USB bus. Basic rules for USB Bus power devices are as follows:

- On plug-in, the device must draw no more than 100mA

- On USB Suspend the device must draw no more than 500µA.

- A High-Power USB Bus Powered Device (one that draws more than 100mA) should use the PWREN# pin to keep the current below 100mA on plug-in and 500µA on USB suspend.

- A device that consumes more than 100mA cannot be plugged into a USB Bus Powered Hub.

- No device can draw more that 500mA from the USB Bus.

#### USB Self Powered Configuration.

A USB Self Powered configuration gets its power from its own POWER SUPPLY and does not draw current from the USB bus. The basic rules for USB Self power devices are as follows.

- A Self-Powered device should not force current down the USB bus when the USB Host or Hub Controller is powered down.

- A Self Powered Device can take as much current as it likes during normal operation and USB suspend as it has its own POWER SUPPLY.

- A Self Powered Device can be used with any USB Host and both Bus and Self Powered USB Hubs.

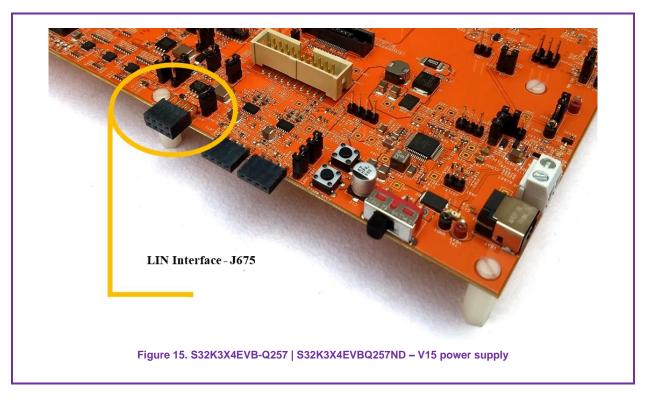

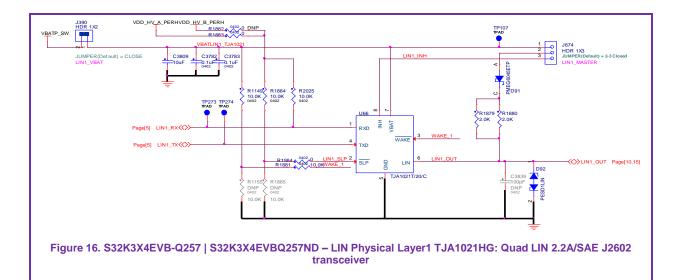

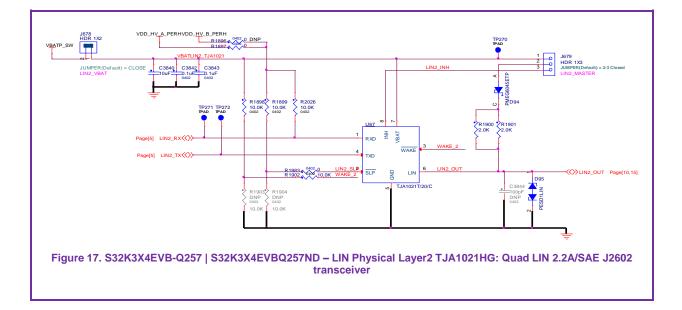

# **10 LIN Interface**

The EVB incorporates two LIN interfaces connected the S32K344 MCU. Using an NXP LIN transceivers the TJA1021T/20/C, supporting both master and slave mode (jumper selectable). The output from the LIN transceivers is connected to J675.

The pinout of these headers is shown below and is also detailed on the PCB silkscreen.

#### Table 12. LIN Connector

| Connector | Reference | Pin<br>Number | Signal/Connection |

|-----------|-----------|---------------|-------------------|

|           | J675      | 1             | GND               |

| 2         |           | 2             | GND               |

| No        |           | 3             | NC                |

|           |           | 4             | NC                |

|           |           | 5             | VBAT              |

| 3 1       |           | 6             | VBAT              |

| 5         |           | 7             | LIN2_OUT          |

|           |           | 8             | LIN1_OUT          |

#### Table 13. LIN Interface – MCU Connections

| LIN<br>Interface | Signal Name | MCU<br>Port | Comment/Description                       |

|------------------|-------------|-------------|-------------------------------------------|

| TJA1021          | LIN1_RX     | PTB9        | LPUART9_RX is routed to LIN Phy1          |

| /LIN1            | LIN1_TX     | PTB10       | LPUART9 is routed to LIN Phy1             |

| TJA1021          | LIN2_RX     | PTB28       | LPUART5_RX is routed to PTE14 to LIN Phy2 |

| /LIN2            | LIN2_TX     | PTB27       | LPUART5_TX is routed to PTE3 to LIN Phy2  |

S32K3X4EVB-Q257 HWUM

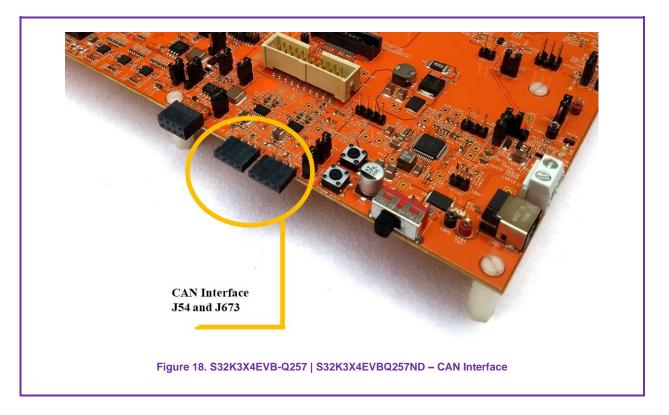

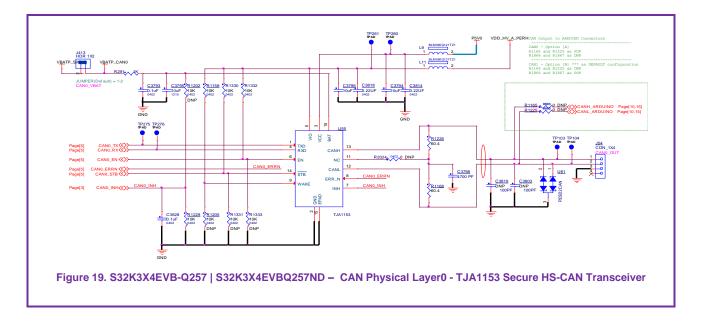

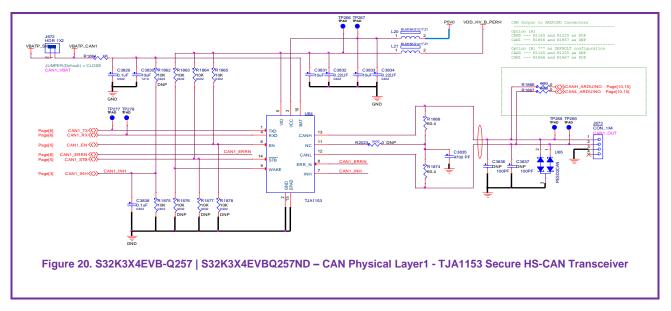

## **11 CAN Interface**

#### Table 14. CAN Interface - Connectors

| Connector | Reference | Circuit/<br>Interface | Pin<br>Number | Signal/Connection |

|-----------|-----------|-----------------------|---------------|-------------------|

|           | J54       | CAN0                  | 1             | CANH0             |

|           |           |                       | 2             | CANL0             |

|           |           |                       | 3             | GND               |

|           |           |                       | 4             | NC                |

| 4         | J673      | CAN1                  | 1             | CANH1             |

| 3         |           |                       | 2             | CANL1             |

| 2         |           |                       | 3             | GND               |

| 1         |           |                       | 4             | NC                |

| Table 15. CAN Interface – MCU Conn |

|------------------------------------|

|------------------------------------|

| CAN<br>Interface | Signal Name | MCU<br>Port | Comment/Description                             |

|------------------|-------------|-------------|-------------------------------------------------|

| TJA1153          | CAN0_RX     | PTA6        | [CAN0_RX Module] is routed to CAN Phy0          |

| /CAN0            | CAN0_TX     | PTA7        | [CAN0_TX Module] is routed to CAN Phy0          |

|                  | CAN0_ERRN   | PTC23       | PTC23 is routed to CAN Phy0 as CAN0_ERRN        |

|                  | CAN0_EN     | PTC21       | PTC21 is routed to CAN Phy0 as CAN0_EN          |

|                  | CAN0_STB    | PTC20       | PTC20 is routed to CAN Phy0 as CAN0_STB         |

| TJA1153          | CAN1_RX     | PTE14       | [CAN4_RX Module] is routed to PTE14 to CAN Phy1 |

| /CAN1            | CAN1_TX     | PTE3        | [CAN4_TX Module] is routed to PTE3 to CAN Phy1  |

|                  | CAN1_ERRN   | PTE8        | PTE8 is routed to CAN Phy1 as CAN1_ERRN         |

S32K3X4EVB-Q257 HWUM

All Information provided in this document is subject to legal disclaimers

© NXP B.V. 2020. All rights reserved

| CAN<br>Interface | Signal Name | MCU<br>Port | Comment/Description                     |

|------------------|-------------|-------------|-----------------------------------------|

|                  | CAN1_EN     | PTD15       | PTD15 is routed to CAN Phy1 as CAN1_EN  |

|                  | CAN1_STB    | PTD13       | PTD13 is routed to CAN Phy1 as CAN1_STB |

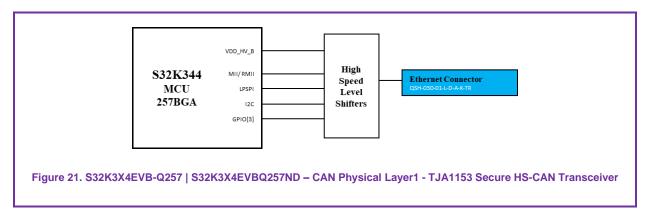

# **12 Ethernet Interface**

The S32K3 EVB incorporates a complete Ethernet interface providing a MII and/or RMII connectivity and LPSPI, I2Cx, GPIOs [3] as digital signals and +3.3V and +12.0V (+5.0V as optional) to the ethernet connector.

**Ethernet Connector** - The *EVB* has a High-Speed Connector that is compatible with some external boards:

- ADTJA1101-RMII

- ETHPHY100BASET

S32K3X4EVB-Q257 HWUM

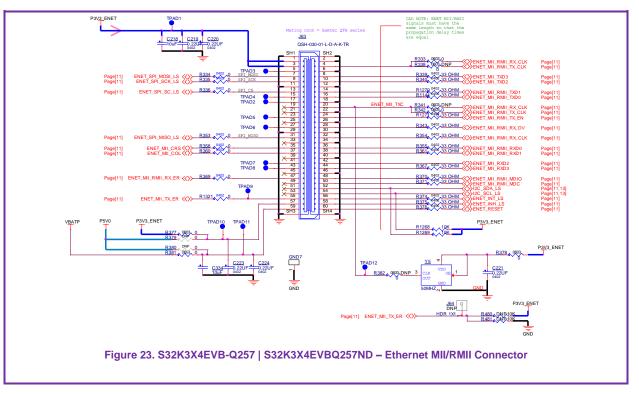

# **13 Ethernet MII/RMII Connector – Pinout**

Table 16. Ethernet MII/RMII Configuration

| MODULE<br>/FUNCTION | SIGNAL               | MCU<br>PORT | DESCRIPTION /COMMENT                             |

|---------------------|----------------------|-------------|--------------------------------------------------|

| MII/RMII            | ENET_MII_RMII_RXD0   | PTD9        | All ports routed to the Ethernet MII/RMII signal |

|                     | ENET_MII_RMII_RXD1   | PTD8        | are not connected to other interface in the EVB  |

|                     | ENET_MII_RXD2        | PTC15       |                                                  |

|                     | ENET_MII_RXD3        | PTC14       |                                                  |

|                     | ENET_MII_RMII_RX_CLK | PTC1        |                                                  |

|                     | ENET_MII_RMII_RX_ER  | PTC16       |                                                  |

|                     | ENET_MII_RMII_RX_DV  | PTC17       |                                                  |

|                     | ENET_MII_RMII_TXD0   | PTB5        |                                                  |

|                     | ENET_MII_RMII_TXD1   | PTB4        |                                                  |

|                     | ENET_MII_TXD2        | PTD6        |                                                  |

|                     | ENET_MII_TXD3        | PTD5        |                                                  |

|                     | ENET_MII_RMII_TX_CLK | PTC0        |                                                  |

|                     | ENET_MII_RMII_TX_EN  | PTE9        |                                                  |

|                     | ENET_MII_RMII_MDC    | PTD17       |                                                  |

|                     | ENET_MII_RMII_MDIO   | PTD16       |                                                  |

|                     | ENET_MII_COL         | PTB23       |                                                  |

|                     | ENET_MII_CRS         | PTB22       |                                                  |

```

S32K3X4EVB-Q257 HWUM

```

| GPIOs  | ENET_INH_LS      | PTA26 |                                                                                                                                                                                                            |

|--------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | ENET_INT_LS      | PTA27 |                                                                                                                                                                                                            |

|        | ENET_RESET       | PTE5  | As optional GPIO for a RESET on the ethernet connector is the PTE21, for this option, R439/0-Ohms must be placed.                                                                                          |

| LPSPIx | ENET_SPI_MISO_LS | PTC9  |                                                                                                                                                                                                            |

|        | ENET_SPI_MOSI_LS | PTB1  |                                                                                                                                                                                                            |

|        | ENET_SPI_SC_LS   | PTC8  |                                                                                                                                                                                                            |

|        | ENET_SPI_SCK_LS  | PTB8  |                                                                                                                                                                                                            |

| I2C    | I2C_SDA_LS       | PTC6  |                                                                                                                                                                                                            |

|        | I2C_SCL_LS       | PTC7  |                                                                                                                                                                                                            |

| PWR    | VBATP            | +12V  | P5V0 [+5.0V] can be routed to the Ethernet<br>connector as optional power supply reference<br>instead the VBATP reference. For this option,<br>R380/0-Ohms must be placed and R381 must<br>be removed.     |

|        | P3V3_ENET        | +3.3V | P5V0 [+5.0V] can be routed to the Ethernet<br>connector as optional power supply reference<br>instead the P3V3_ENET reference. For this<br>option, R380/0-Ohms must be placed and R381<br>must be removed. |

|        |                  | 1     |                                                                                                                                                                                                            |

#### Table 17. Ethernet Interface - Jumpers

|           | Reference                              | Position | Description/Comment                                        |

|-----------|----------------------------------------|----------|------------------------------------------------------------|

| Ethernet  | J32                                    | 1-2      | P3V3 domain is used to supply the Ethernet Interface       |

| Interface |                                        | OPEN     | The Ethernet Interface is disabled                         |

|           | J61 1-2 VDD_HV_B_PERH is routed to VDD |          | VDD_HV_B_PERH is routed to VDD_HV_B_ENET                   |

|           |                                        | OPEN     | The level Shifters for the Ethernet Interface are disabled |

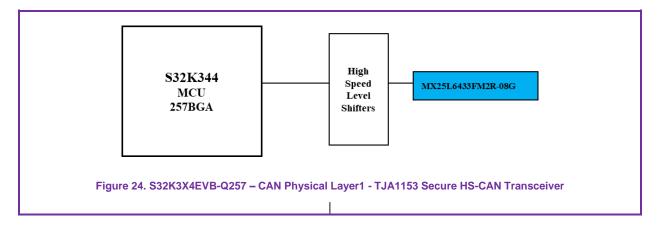

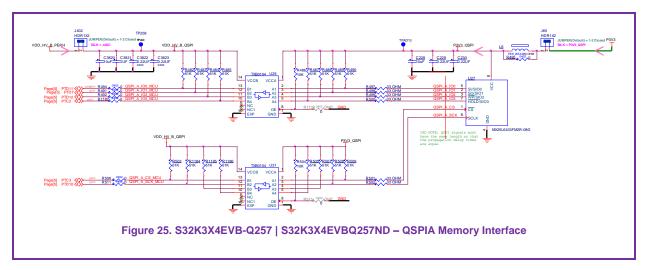

# **14 QSPI-A Configuration**

The S32K3 EVB incorporates a MX25L6433F is 64Mb bits Serial NOR Flash memory, which is connected to the QSPIA Module of the S32K344 MCU.

#### Table 18. QSPIA Memory Interface - Jumpers

|           | Reference | Position | Description/Comment                                        |

|-----------|-----------|----------|------------------------------------------------------------|

| QSPI      | J65       | 1-2      | P3V3 domain is used to supply the QSPIA Memory interface   |

| Interface |           | OPEN     | The QSPIA Memory interface is disabled                     |

|           | J402      | 1-2      | VDD_HV_B_PERH is routed to VDD_HV_B_QSPI                   |

|           |           | OPEN     | The level Shifters for QSPIA Memory interface are disabled |

| Module<br>/Function | Signal               | MCU<br>PORT | DESCRIPTION /COMMENT                                       |

|---------------------|----------------------|-------------|------------------------------------------------------------|

| QSPIA               | QSPI_A_IO0_MCU       | PTD11       | All MCU ports routed to the QSPIA Memory Interface are not |

|                     | QSPI_A_IO1_MCU       | PTD7        | connected to other interface in the EVB.                   |

|                     | QSPI_A_IO2_MCU PTD12 |             |                                                            |

|                     | QSPI_A_IO3_MCU       | PTC2        |                                                            |

|                     | QSPI_A_SCK_MCU       | PTD10       |                                                            |

|                     | QSPI_A_CS_MCU        | PTC3        |                                                            |

The table below details the signals configuration for the QSPI-A.

# **15 User Peripherals**

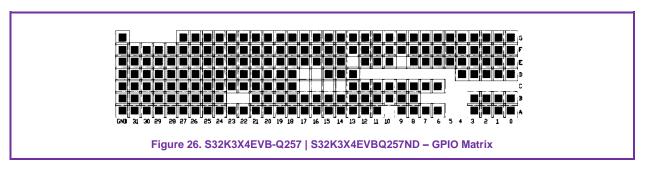

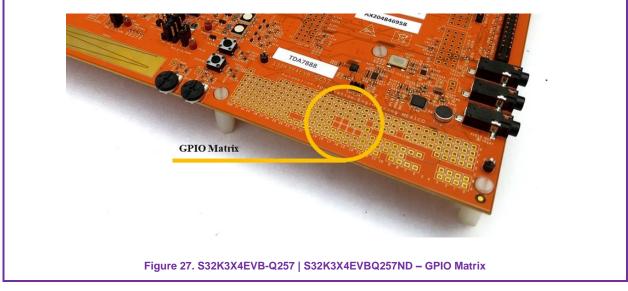

## **15.1 GPIO Matrix**

A subset of available GPIO pins (available pins being those not already routed to the Ethernet connector and the QSPIA-Memory Interface) are available at the GPIO matrix as detailed below. The matrix provides an easy to follow, intuitive, space-saving grid of 0.1" header through-hole pads. Users can solder wires, fit headers, or simply insert a scope probe into the respective pad.

S32K3X4EVB-Q257 HWUM

All Information provided in this document is subject to legal disclaimers

© NXP B.V. 2020. All rights reserved

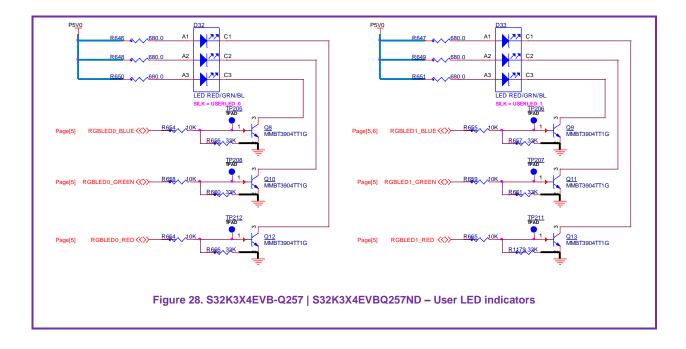

## **15.2 User LED Indicators**

There are 2 active high user RGB LED's are connected by NPN transistors to the MCU ports. The USERLEDs are connected as follows:

### Table 19. User LED Indicators

| Reference   | Signal Name     | MCU Port<br>Default | Color | Comment     |

|-------------|-----------------|---------------------|-------|-------------|

| D32         | RGBLED0_RED     | PTA29               | Red   | Active High |

|             | RGBLED0_GREEN   | PTA30               | Green | Active High |

|             | RGBLED0_BLUE    | PTA31               | Blue  | Active High |

| <b>D</b> 33 | D33 RGBLED1_RED |                     | Red   | Active High |

|             | RGBLED1_GREEN   | PTB25               | Green | Active High |

|             | RGBLED1_BLUE    | PTE12               | Blue  | Active High |

|             |                 | PTB24               |       | Disabled    |

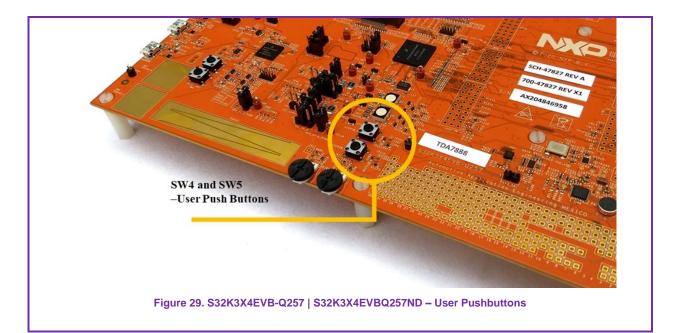

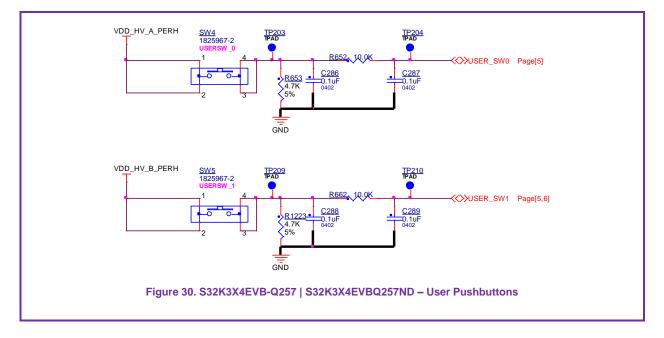

## **15.3 User Pushbuttons**

There are 2 push-buttons active to high (pulled low, driven to VDD\_HV\_A and VDD\_HV\_B), the push button switches (SW4 and SW5) connected to MCU ports. The switches are connected as follows:

## S32K3X4EVB-Q257 | S32K3X4EVBQ257ND HWUM

### Hardware User Manual

All Information provided in this document is subject to legal disclaimers

© NXP B.V. 2020. All rights reserved

Table 20. User Pushbuttons

| Reference | Function | MCU<br>Port | Comments           |

|-----------|----------|-------------|--------------------|

| SW4       | USER_SW0 | PTB26       | Active to HIGH     |

| SW5       | USER_SW1 | PTB19       | Enabled as DEFAULT |

|           |          | PTF31       | Disabled           |

|           |          | PTC18       | Disabled           |

|           |          |             |                    |

There are zero-ohm resistors on the direct connections between each USER\_SWx and the MCU pins. These 1. can be removed if required to isolate or change the User Switch from the default MCU pin.

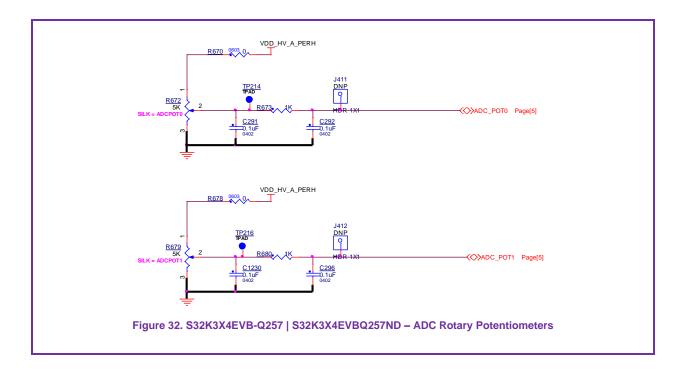

## **15.4 ADC Rotary Potentiometers**

The EVB incorporates a couple of ADC Rotary Potentiometer [which routes a voltage between 0v to VD\_HV\_A] directly connected to ADC Precise Input Chanel of the S32K3XX Microcontroller.

#### **Table 21. ADC Potentiometers**

| Reference | Function | MCU Port | Comments           |

|-----------|----------|----------|--------------------|

| R672      | ADC_POT0 | PTA11    | Enabled as DEFAULT |

|           |          | PTA9     | Disabled           |

| R679      | ADC_POT1 | PTA17    | Enabled as DEFAULT |

| NOTE      |          |          |                    |

There are zero-ohm resistors on the direct connections between each USERSW and the MCU pins. These 1. can be removed if required to isolate or change the User Switch from the default MCU pin.

S32K3X4EVB-Q257 HWUM

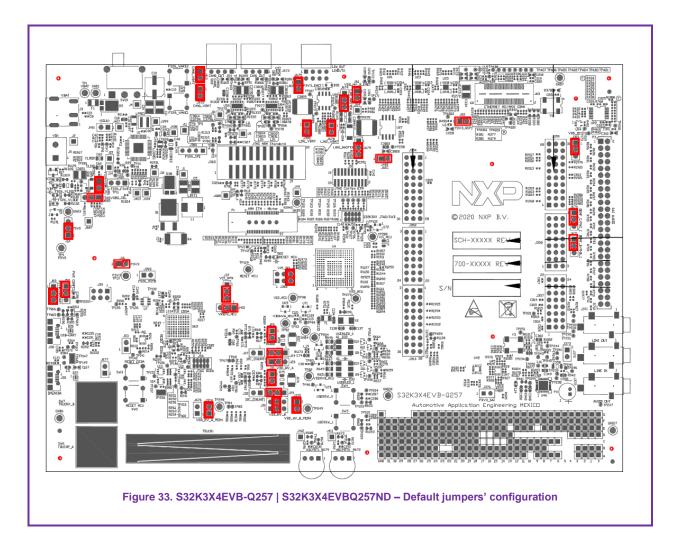

# **16 Default Jumpers**

### Table 22. Default Jumper Configuration

| Interface           | Reference | Position | Description / Comments                                                                                                                                           |  |  |  |

|---------------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FS26x               | J13       | 1-2      | FS26_VLDO1 [+5.0V] is routed to P5V0 domain                                                                                                                      |  |  |  |

| SBC                 | J16       | 1-2      | FS26_VLDO2 [+3.3V] is routed to P3V3 domain                                                                                                                      |  |  |  |

| Power               | J686      | 1-2      | Flash Mode – configuration in the FS26                                                                                                                           |  |  |  |

| Supply              | J685      | 1-2      |                                                                                                                                                                  |  |  |  |

| USB to UART         | J57       | 1-2      | P5V0_USBSER domain is routed to P5V0 for the USB Self Powered Configuration                                                                                      |  |  |  |

| Interface           | J60       | 2-3      | The Reset# pin is routed to the divider resistor for the USB Self Powered Configuration                                                                          |  |  |  |

| Ethernet            | J61       | 1-2      | VDD_HV_B reference is routed for the VDD_HV_B_ENET reference                                                                                                     |  |  |  |

| Interface           | J62       | 1-2      | P3V3 domain is routed to P3V3_ENET                                                                                                                               |  |  |  |

| QSPI                | J65       | 1-2      | P3V3 domain is used to supply the QSPIA interface                                                                                                                |  |  |  |

| Interface           | J402      | 1-2      | VDD_HV_B_PERH is routed to VDD_HV_B_QSPI                                                                                                                         |  |  |  |

| S32K3XX             | J23       | 1-2      | P5V0 (+5.0V from the FS26) is selected for the VDD_HV_A_MCU reference.                                                                                           |  |  |  |

| MCU<br>Power Supply | J24       | 2-3      | The shunt resistor R58 [1 Ohms] is selected for current measurement on the VDD_HV_A_MCU reference.                                                               |  |  |  |

|                     | J25       | 1-2      | VDD_HV_A is routed to VDD_HV_A_MCU reference. A jumper on this position disables the shunt resistors R57 and R58 are disabled for current measurement proposals. |  |  |  |

|                     | J30       | 3-4      | P3V3 (+3.3V from the FS26) is selected for the VDD_HV_B_MCU reference.                                                                                           |  |  |  |

|                     | J29       | 2-3      | The shunt resistor R75 [1 Ohms] is selected for current measurement on the VDD_HV_B_MCU reference.                                                               |  |  |  |

S32K3X4EVB-Q257 HWUM

|             | T    |     |                                                                                |  |  |  |  |

|-------------|------|-----|--------------------------------------------------------------------------------|--|--|--|--|

|             | J31  | 1-2 | VDD_HV_B is routed to VDD_HV_B_MCU reference. A jumper on this position        |  |  |  |  |

|             |      |     | disables the shunt resistors R74 and R75 are disabled for current measurement  |  |  |  |  |

|             |      |     | proposals.                                                                     |  |  |  |  |

|             | J37  | 2-3 | The VDD_HV_B domain is routed to the collector terminal in order to supply the |  |  |  |  |

|             |      |     | NPN external Ballast transistor for V15_MCU domain                             |  |  |  |  |

|             | J360 | 5-6 | The NPN external Ballast transistor is selected to supply the V15_MCU domain.  |  |  |  |  |

|             | J375 | 1-2 | VDD_HV_B is routed to VDD_HV_B_PERH                                            |  |  |  |  |

|             | J374 | 1-2 | VDD_HV_A is routed to VDD_HV_A_PERH                                            |  |  |  |  |

|             | J410 | 1-2 | VDD_HV_A_MCU is routed to VDD_REFH                                             |  |  |  |  |

| User        | J670 | 1-2 | PTE0 is routed to the ARDUINO shield connectors                                |  |  |  |  |

| Peripherals | J671 | 2-3 | PTA9 is routed to the ARDUINO shield connectors                                |  |  |  |  |

|             | J321 | 1-2 | VDD_HV_A_PERH is routed to VDD_IO                                              |  |  |  |  |

| LIN         | J390 | 1-2 | LIN1 Physical layer – LIN1 is enabled                                          |  |  |  |  |

| Interface   | J674 | 3-4 | INH function is routed to LIN1 pullup circuitry for Master configuration       |  |  |  |  |

|             | J678 | 1-2 | LIN2 Physical layer – LIN2 is enabled                                          |  |  |  |  |

|             | J679 | 3-4 | INH function is routed to LIN2 pullup circuitry for Master configuration       |  |  |  |  |

| CAN         | J413 | 1-2 | CAN0 Physical Layer is enabled. VBATP_SW is routed/turning-ON the TJA1153      |  |  |  |  |

| Interface   |      |     | -U55                                                                           |  |  |  |  |

|             | J672 | 1-2 | CAN1 Physical Layer is enabled. VBATP_SW is routed/turning-ON the TJA1153      |  |  |  |  |

|             |      |     | -U64                                                                           |  |  |  |  |

S32K3X4EVB-Q257 HWUM

All Information provided in this document is subject to legal disclaimers

© NXP B.V. 2020. All rights reserved

# **17 Revision history**

#### Table 23. Revision history

| Document<br>Revision | Date    | Board<br>Name    | Schemati<br>c/ Board<br>Number | Schematic/<br>Board<br>Revision | Changes         | Author           |

|----------------------|---------|------------------|--------------------------------|---------------------------------|-----------------|------------------|

| A                    | 08/2021 | S32K3X4EVB-Q257  | 47827                          | A                               | Infernal DRAFT  | Jesús<br>Sánchez |

| В                    | 09/2021 | S32K3X4EVB-Q257  | 47827                          | A                               | Release version |                  |

|                      |         | S32K3X4EVBQ257ND | 53189                          | A                               |                 |                  |

# **18 Legal Information**

## **18.1 Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## **18.2 Disclaimers**

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.