# AFBR-57G5MZ

32GFC SFP28 for Multi-Mode Optical Fiber Digital Diagnostic SFP, 850nm, 32G/16G/8G Low Voltage (3.3V) Fibre Channel Optical Transceiver

# **Data Sheet**

# Description

Avago Technologies' AFBR-57G5MZ optical transceiver supports high speed serial links over multi-mode optical fiber at signalling rates up to 28.05Gb/s (the serial line rate of 32GFC). The product is compliant with Small Form Plug-gable industry agreements SFP and SFP28 for mechanical and low speed electrical specifications. High speed elec-trical and optical specifications are compliant with ANSI Fibre Channel FC-PI-6.

The AFBR-57G5MZ is a multi-rate 850nm transceiver which ensures compliance with FC-PI-6 32GFC, 16GFC and 8GFC specifications. Per the requirements of 32GFC, internal clock and data recovery circuits (CDRs) are present on both electrical input and electrical output of this transceiver. These CDRs will lock at 28.05Gb/s and 14.025Gb/s (32GFC and 16GFC) but must be bypassed for operation at 8.5Gb/s (8GFC), accomplished by using two Rate Select inputs to configure transmit and receive sides. Transmitter and receiver can operate at different data rates, as is often seen during Fibre Channel speed negotiation.

Digital diagnostic monitoring information (DMI) is present in the AFBR-57G5MZ per the requirements of SFF-8472, providing real time monitoring information of transceiver laser, receiver and environment conditions over a SFF-8419 2-wire serial interface.

### **Related Products**

- AFCT-57G5MZ: 1310nm SFP for 32G/16G/8G Fibre Channel

- AFBR-57F5MZ: 850nm SFP for 16G/8G/4G Fibre Channel ٠

- AFCT-57F5AMZ: 1310nm SFP for 16G/8G/4G Fibre Channel

- AFBR-57D9AMZ: 850nm SFP for 8G/4G/2G Fibre Channel

- AFCT-57D5ATPZ: 1310nm SFP for 8G/4G/2G Fibre Channel

- AFCT-57D5ANPZ: 1310nm SFP for 8G/4G/2G Fibre Channel

- AFBR-57R5APZ: 850nm SFP for 4G/2G/1G Fibre Channel

- AFCT-57R5APZ: 1310nm SFP for 4G/2G/1G Fibre Channel

- AFCT-57R5ATPZ: 1310nm SFP for 4G/2G/1G Fibre Channel

- AFCT-57R5ANPZ: 1310nm SFP for 4G/2G/1G Fibre Channel

# **Features**

- 850nm Vertical Cavity Surface Emitting Laser (VCSEL)

- Class 1 eye safe per IEC60825-1 and CDRH •

- ANSI TIA/EIA604-10 (FOCIS 10A)

- Diagnostic features per SFF-8472 "Diagnostic Monitoring Interface for Optical Transceivers"

- Real time monitoring of:

- Transmitter average optical power

- Received average optical power

- Laser bias current

- Temperature

- Supply Voltage

- SFP28 mechanical specifications per SFF-8432

- SFP28 compliant low speed interface per SFF-8419

- Fibre Channel FC-PI-6 compliant high speed interface

- 3200-M5-SN-S, 1600-M5-SN-S, 800-M5-SN-S

- 3200-M5E-SN-I, 1600-M5E-SN-I, 800-M5E-SN-I

- 3200-M5F-SN-I, 1600-M5F-SN-I, 800-M5F-SN-I

- Fibre Channel FC-PI-6 compliant optical link distances

# Applications

- Fibre Channel switches (director, stand alone, blade)

- Fibre Channel Host Bus Adapters

- Fibre Channel RAID controllers

- Fibre Channel tape drive

- Port side connections

- Inter-switch or inter-chassis aggregated links

Patent - www.avagotech.com/patents

- Compliant to RoHS directives

- Wide temperature range (0°C to 70°C)

- LC duplex connector optical interface conforming to

E. .

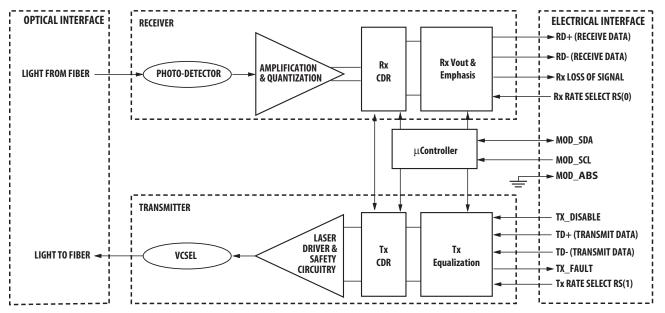

#### **Transmitter Section**

The transmitter section includes a Transmitter Optical SubAssembly (TOSA), laser driver circuit, Clock and Data Recovery circuit (CDR) and an electrical input stage with variable equalization controls. The TOSA contains a 850nm Vertical Cavity Surface Emitting Laser (VCSEL) light source with integral light monitoring function and imaging optics to assure efficient optical coupling to the LC connector in-terface. The TOSA is driven by a laser driver IC, which uses the differential output from an integral Tx CDR stage to modulate and regulate VCSEL optical power. As mandated by FC-PI-6, the integral CDR cleans up any incoming jit-ter accumulated from the host ASIC, PCB traces and SFP electrical connector. Between the SFP electrical connector and Tx CDR is a variable, i2c controlled, equalization cir-cuit to optimize SFP performance with non-ideal incom-ing electrical waveforms. Note the Tx CDR is engaged with Tx RATE=high (32GFC) and auto-configured (engaged or bypassed) with Tx\_RATE=low (16G/8G).

# **Receiver Section:**

The receiver section includes a Receiver Optical SubAssembly (ROSA), pre-amplification and post-amplification circuit, Clock and Data Recovery Circuit and an electrical output stage with variable emphasis controls. The ROSA, containing a high speed PIN detector, pre-amplifier and imaging optics efficiently couple light from the LC connector interface and perform an optical to electrical conversion. The resulting differential electrical

signal passes through a post amplification circuit and into a Clock and Data Recovery circuit (CDR) for cleaning up accumulated jitter. Note the Rx CDR is engaged with Rx\_RATE=high (32GFC) and auto-configured (engaged or bypassed) with Rx\_RATE=low (16G/8G).

# **Digital Diagnostics:**

The AFBR-57G5MZ is compliant to the Diagnostic Monitoring Interface (DMI) defined in document SFF-8472. These features allow the host to access, via i2c, real time diagnostic monitors of transmit optical power, received optical power, temperature, supply voltage and laser operating current.

# **Low Speed Interfaces:**

Conventional low speed interface I/Os are available as defined in documents SFF-8419 to manage coarse and fine functions of the optical transceiver. On the transmit side, a Tx\_DISABLE input is provided for the host to turn on and off the outgoing optical signal. A transmitter rate select control input, Tx\_RATE, is provided to configure the transmitter stages for 32GFC, 16GFC or 8GFC operation (logic HIGH reserved for 32GFC, logic LOW reserved for 16GFC and 8GFC). A transmitter fault indicator output, Tx\_FAULT, is available for the SFP to signal a host of a transmitter operational problem. A receiver rate select control input, Rx\_RATE, is provided to configure receiver stages for 32GFC, 16GFC, or 8GFC operation (logic HIGH reserved for 32GFC, logic LOW reserved for 16GFC and 8GFC). A received optical power loss of signal indicator, RX\_LOS, is available to advise the host of a receiver operational problem.

Figure 1. Transceiver functional diagram.

# Table 1. Regulatory Compliance

| Feature                                                                                                                       | Test Method                                                                                                                                                                                     | Performance                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Contacts                                                                      | JEDEC Human Body Model (HBM)<br>(JESD22-A114-B)                                                                                                                                                 | High speed contacts shall withstand<br>1000V. All other contacts shall withstand<br>2000 V.                                                                                 |

| Electrostatic Discharge (ESD) to the Optical Connector Receptacle                                                             | EN61000-4-2, Criterion B                                                                                                                                                                        | When installed in a properly grounded<br>housing and chassis the units are subject-<br>ed to 15kV air discharges during operatior<br>and 8kV direct discharges to the case. |

| Electromagnetic Interference (EMI)                                                                                            | FCC Part 15 CENELEC EN55022<br>(CISPR 22A) VCCI Class 1                                                                                                                                         | System margins are dependent on cus-<br>tomer board and chassis design.                                                                                                     |

| Immunity                                                                                                                      | Variation of IEC 61000-4-3                                                                                                                                                                      | Typically shows no measurable effect from<br>a 10V/m field swept from 80 MHz to 1 GHz<br>applied to the module without a chassis<br>enclosure                               |

| Laser Eye Safety and Equipment<br>Type Testing<br>BAUART<br>GEPROFT<br>TUV<br>Rheinland<br>Product Safety<br>TYPE<br>APPROVED | US FDA CDRH AEL Class 1<br>US21 CFP, Subchapter J per Paragraphs 1002.10<br>and 1002.12<br>(IEC) EN60825-1:1994 +A11 +A2<br>(IEC) EN60825-2:1994 +A1<br>(IEC) EN60950:1992 +A1 +A2 +A3 +A4 +A11 | CDRH Certification 9720151-155<br>TUV File: R72121699                                                                                                                       |

| Component Recognition                                                                                                         | Underwriters Laboratories (UL) and Canadian<br>Standards Association (CSA) Joint Component<br>Recognition for Information Technology Equip-<br>ment including Electrical Business Equipment     | UL File: E173874                                                                                                                                                            |

| RoHS Compliance                                                                                                               |                                                                                                                                                                                                 | Less than 1000 ppm of cadmium, lead,<br>mercury, hexavalent chromium, polybro-<br>minated biphenyls (PPB) and polybromi-<br>nated biphenyl ethers (PBDE).                   |

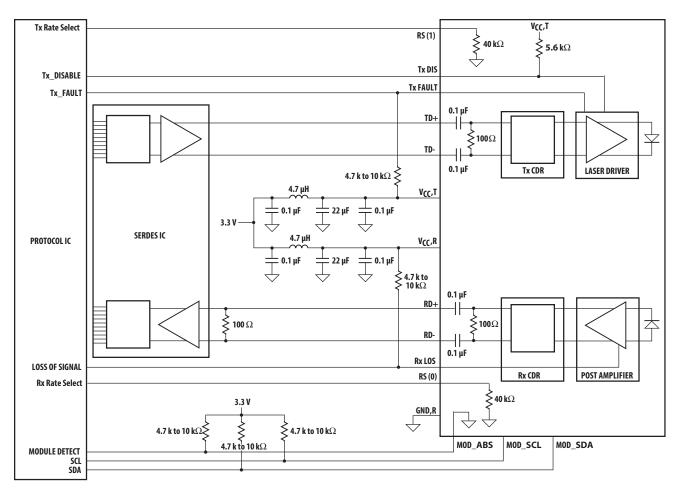

Figure 2. Typical application configuration

NOTE: INDUCTORS MUST HAVE LESS THAN 0.5  $\Omega$  series resistance to limit voltage drop to the SFP module.

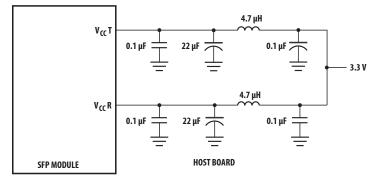

Figure 3. Recommended power supply filter

#### **Table 2. Pin Description**

| Pin | Name                  | Function/Description                                                                | Notes  |

|-----|-----------------------|-------------------------------------------------------------------------------------|--------|

| 1   | VeeT                  | Transmitter Ground                                                                  |        |

| 2   | TX_FAULT              | Transmitter Fault Indication – High indicates a fault condition                     | Note 1 |

| 3   | TX_DISABLE            | Transmitter Disable – Module optical output disables on high or open                | Note 2 |

| 4   | MOD_SDA               | Module Definition 2 – Two wire serial ID interface data line (SDA)                  | Note 3 |

| 5   | MOD_SCL               | Module Definition 1 – Two wire serial ID interface clock line (SCL)                 | Note 3 |

| 6   | MOD_ABS               | Module Definition 0 – Grounded in module (module present indicator)                 | Note 3 |

| 7   | Rx Rate Select, RS(0) | Receiver Rate Select. Logic High = 28.05Gb/s, Logic Low = 14.025Gb/s and 8.5Gb/s    | Note 8 |

| 8   | RX_LOS                | Loss of Signal – High indicates loss of received optical signal                     | Note 4 |

| 9   | Tx Rate Select, RS(1) | Transmitter Rate Select. Logic High = 28.05Gb/s, Logic Low = 14.025Gb/s and 8.5Gb/s | Note 8 |

| 10  | VeeR                  | Receiver Ground                                                                     |        |

| 11  | VeeR                  | Receiver Ground                                                                     |        |

| 12  | RD-                   | Inverse Received Data Out                                                           | Note 5 |

| 13  | RD+                   | Received Data Out                                                                   | Note 5 |

| 14  | VeeR                  | Receiver Ground                                                                     |        |

| 15  | VccR                  | Receiver Power + 3.3 V                                                              | Note 6 |

| 16  | VccT                  | Transmitter Power + 3.3 V                                                           | Note 6 |

| 17  | VeeT                  | Transmitter Ground                                                                  |        |

| 18  | TD+                   | Transmitter Data In                                                                 | Note 7 |

| 19  | TD-                   | Inverse Transmitter Data In                                                         | Note 7 |

| 20  | VeeT                  | Transmitter Ground                                                                  |        |

Notes:

1. TX\_FAULT is an open collector/drain output, which must be pulled up with a 4.7k – 10kΩ resistor on the host board. When high, this output indi-cates a laser fault of some kind. Low indicates normal operation. In the low state, the output will be pulled to < 0.8V.

2. TX\_DISABLE is an input that is used to shut down the transmitter optical output. It is internally pulled up (within the transceiver) with a 5.6 kΩ

resistor.

| 15(0).                        |                      |

|-------------------------------|----------------------|

| Low (0 – 0.8V):               | Transmitter on       |

| Between (0.8V and 2.0V):      | Undefined            |

| High (2.0 – Vcc max) or OPEN: | Transmitter Disabled |

3. The signals Mod\_ABS, SCL, SDA designate the two wire serial interface pins. They must be pulled up with a 4.7k – 10kΩ resistor on the host board. Mod\_ABS is grounded by the module to indicate the module is present

Mod\_SCL is serial clock line (SCL) of two wire serial interface

Mod\_SDA is serial data line (SDA) of two wire serial interface

4. RX\_LOS (Rx Loss of Signal) is an open collector/drain output that must be pulled up with a 4.7k – 10kΩ resistor on the host board. When high, this output indicates the received optical power is below the worst case receiver sensitivity (as defined by the standard in use). Low indicates normal operation. In the low state, the output will be pulled to < 0.8V.</p>

5. RD-/+ designate the differential receiver outputs. They are AC coupled 100Ω differential lines which should be terminated with 100Ω differential at the host SERDES input. AC coupling is done inside the transceiver and is not required on the host board. The voltage swing on these lines will be between 50 and 900 mV differential (25 – 450 mV single ended) when properly terminated.

6. VccR and VccT are the receiver and transmitter power supplies. See SFF-8419 for the details.

TD-/+ designate the differential transmitter inputs. They are AC coupled differential lines with 100Ω differential termination inside the module. The AC coupling is done inside the module and is not required on the host board. The inputs will accept differential swings of 40 – 1200 mV (20 – 600 mV single ended), though it is recommended that values between 50 and 900 mV differential (25 – 450 mV single ended) be used for best EMI performance.

8. RATE\_SELECT is an input used to control transmitter and receiver compliance among multiple rates. It is internally pulled down with a 40kΩ resistor.

| Low (0 - 0.8V) or OPEN:  | Low Bit Rate Compliance (14.025Gb/s and 8.5 Gb/s) |

|--------------------------|---------------------------------------------------|

| Between (0.8V and 2.0V): | Undefined                                         |

| High (2.0 – Vcc max):    | High Bit Rate Compliance (28.05Gb/s)              |

#### **Table 3. Absolute Maximum Ratings**

Stress in excess of any of the individual Absolute Maximum Ratings can cause immediate catastrophic damage to the module even if all other parameters are within Recommended Operating Conditions. It should not be assumed that limiting values of more than one parameter can be applied to the module concurrently. Exposure to any of the Absolute Maximum Ratings for extended periods can adversely affect reliability.

| Parameter                  | Symbol          | Min. | Max.          | Units | Reference |

|----------------------------|-----------------|------|---------------|-------|-----------|

| Storage Temperature        | Ts              | -40  | 85            | °C    | Note 1    |

| Case Operating Temperature | T <sub>C</sub>  | -40  | 85            | °C    |           |

| Relative Humidity          | RH              | 5    | 95            | %     |           |

| Supply Voltage             | V <sub>CC</sub> | -0.5 | 3.63          | V     |           |

| Low Speed Input Voltage    | Vi              | -0.5 | VCC+0.5, 3.63 | V     |           |

#### **Table 4. Recommended Operating Conditions**

Recommended Operating Conditions specify parameters for which the optical and electrical characteristics hold unless otherwise noted. Optical and electrical characteristics are not defined for operation outside the Recommended Operating Conditions, reliability is not implied and damage to the module may occur for such operation over an extended period of time.

| Parameter                                  | Symbol          | Min.  | Тур. | Max.  | Units | Reference |

|--------------------------------------------|-----------------|-------|------|-------|-------|-----------|

| Case Operating Temperature                 | Tc              | 0     |      | 70    | °C    | Note 2    |

| Supply Voltage                             | V <sub>CC</sub> | 3.135 | 3.3  | 3.465 | V     |           |

| Data Rate                                  |                 | 8.5   |      | 28.05 | Gb/s  | Note 3    |

| Two Wire Serial (TWS) Interface Clock Rate |                 |       |      | 400   | kHz   | Note 4    |

# **Table 5. Transceiver Electrical Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                | Symbols         | Min.       | Тур. | Max.      | Units | Reference |

|------------------------------------------|-----------------|------------|------|-----------|-------|-----------|

| Transceiver Power Consumption            |                 |            |      | 1.0       | W     |           |

| Transceiver Power Supply Current         |                 |            |      | 319       | mA    |           |

| Power Supply Noise Tolerance (peak-peak) | PSNR            |            |      | 66        | mVpp  | Note 5    |

| TX_FAULT, RX_LOS                         | I <sub>OH</sub> | -50        |      | 37.5      | μΑ    | Note 6    |

|                                          | V <sub>OL</sub> | -0.3       |      | 0.4       | V     |           |

|                                          | VIH             | 2.0        |      | Vcc+0.3   | V     |           |

| TX_DIS, RS0, RS1                         | V <sub>IL</sub> | -0.3       |      | 0.8       | V     |           |

|                                          | V <sub>OH</sub> | VCC_Hst-0. | 5    | VCC_Hst+0 | ).3 V | Note 7    |

| MOD_SCL, MOD_SDA                         | V <sub>OL</sub> | 0.0        |      | 0.4       | V     |           |

|                                          | V <sub>IH</sub> | VccT*0.7   |      | VccT+0.5  | V     |           |

|                                          | VIL             | -0.3       |      | VccT*0.3  | V     |           |

Notes:

4. With 500us clock stretch per SFF-8419

<sup>1.</sup> Absolute maximum ratings are those values beyond which damage to the device may occur if these limits are exceeded for other than a short period of time. See Reliability Data Sheet for specific reliability performance. Between Absolute Maximum Ratings and the Recommended Operating Conditions functional performance is not intended, device reliability is not implied, and damage to the device may occur over an extended period of time.

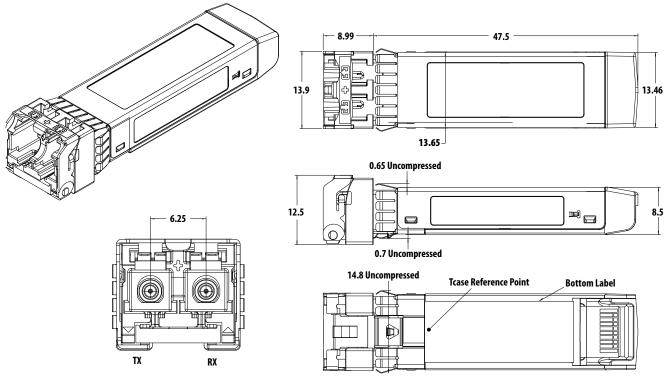

<sup>2.</sup> The position of case temperature measurement is shown in Figure 5. Continuous operation at the maximum Recommended Operating Case Temperature should be avoided in order not to degrade reliability.

<sup>3. 32</sup>GFC requires FEC RS(528,514) encoding per FC-PI-6. 16GFC and 8GFC are not compatible with FEC, per FC-PI-5.

<sup>5.</sup> Filter per SFF-8419 specification is required on the host board.

<sup>6.</sup> Measured with a  $4.7k\Omega$  load pulled up to the host board to 3.3V

<sup>7.</sup> Mod\_SCL and Mod\_SDA must be pulled up externally with a  $4.7k-10k\Omega$  resistor on the host board to host VCC ( $3.14 < VCC_Hst < 3.46V$ ).

#### **Table 6. Transmitter and Receiver Electrical Characteristics**

(Tc = 0°C to 70°C, VccT, VccR =  $3.3V \pm 5\%$ )

| Parameter                                                                     | Symbol | Min. | Max. | Unit   | Notes                                  |

|-------------------------------------------------------------------------------|--------|------|------|--------|----------------------------------------|

| High Speed Data Input Transmitter Differential<br>Input Voltage (TD±)         | VI     | 50   | 900  | mV     | Note 1                                 |

| High Speed Data Output Receiver Differential<br>Output Voltage (RD ±)         | Vo     | 250  | 900  | mV     | Note 2                                 |

| Module Electrical Input, Differential Termination<br>Resistance Mismatch      |        |      | 10   | %      |                                        |

| Module Electrical Input Differential return loss SDD11                        |        |      |      |        | See FC-PI-6 Equation 6-1,<br>Figure 10 |

| Module Electrical Input Common Mode to<br>Differential Conversion, SCD11      |        |      |      |        | See FC-PI-6 Equation 6-2,<br>Figure 12 |

| Module Electrical Input, Differential Mode to<br>Common Conversion, SDC11     |        |      |      |        | See FC-PI-6 Equation 6-2,<br>Figure 12 |

| Module Electrical Input, Stressed Input Random Jitter,<br>p-p, 10E-6 BER      |        |      | 0.09 | UI     |                                        |

| Module Electrical Input, Stressed Input Eye Width<br>at 1E-6 Probability EW6  |        | 0.46 |      | UI     |                                        |

| Module Electrical Input, Stressed Input Eye Height<br>at 1E-6 Probability EH6 |        | 50   |      | mV     |                                        |

| Module Electrical Output, Common Mode Noise rms                               |        |      | 17.5 | mV,rms |                                        |

| Module Electrical Output, Differential termination resistance mismatch        |        |      | 10   | %      |                                        |

| Module Electrical Output, Differential return loss<br>SDD22                   |        |      |      |        | See FC-PI-6 Equation 6-1,<br>Figure 10 |

| Module Electrical Output, Common Mode to<br>Differential Conversion, SCD22    |        |      |      |        | See FC-PI-6 Equation 6-3,<br>Figure 12 |

| Module Electrical Output, Differential Mode to<br>Common Conversion, SDC22    |        |      |      |        | See FC-PI-6 Equation 6-3,<br>Figure 12 |

| Module Electrical Output, Common Mode Return<br>Loss, SCC22                   |        |      | -2   | dB     |                                        |

| Module Electrical Output, Vertical Eye Closure                                |        |      | 4    | dB     |                                        |

| Module Electrical Output, Eye Width at 1E-6<br>Probability EW6                |        | 0.65 |      | UI     |                                        |

| Module Electrical Output, Eye Height at 1E-6<br>Probability EH12              |        | 250  |      | mV     |                                        |

| Receiver Total Jitter (28.05Gb/s)                                             | L      |      |      | UI     | Compliance Test. Note 3, 5             |

| Receiver Total Jitter (14.025Gb/s)                                            | LT     |      | 0.36 | UI     | Note 3,                                |

| Receiver Total Jitter (8.5Gb/s)                                               | LT     |      | 0.71 | UI     | Note 4,                                |

| Receiver Deterministic Jitter (14.025Gb/s)                                    | DJ     |      | 0.22 | UI     | Note 3,                                |

| Receiver Deterministic Jitter (8.5Gb/s)                                       | DJ     |      | 0.42 | UI     | Note 4,                                |

| Receiver Data Dependent Pulse Width Shrinkage<br>(14.025Gb/s)                 | DDPWS  |      | 0.14 | UI     | Note 3,                                |

| Receiver Data Dependent Pulse Width Shrinkage<br>(8.5Gb/s)                    | DDPWS  |      | 0.36 | UI     | Note 4,                                |

Notes:

1. Internally ac coupled and terminated ( $100\Omega$  differential).

2. Internally ac coupled but requires an external load termination ( $100\Omega$  differential).

3. CDR is engaged with 28.05Gb/s and 14.025 Gb/s.

4. CDR is not engaged with 8.5 Gb/s.

5. 32GFC (28.05Gb/s) assumes a FEC encoded RS(528, 514) signal and allows a BER of 1E-6 for receiver and transmitter measurements.

#### **Table 7. Transmitter Optical Characteristics**

(Tc = 0°C to 70°C, VccT, VccR =  $3.3V \pm 5\%$ )

| Parameter                                                         | Symbol | Min. | Тур. | Max. | Unit  | Notes  |

|-------------------------------------------------------------------|--------|------|------|------|-------|--------|

| Modulated Optical Output Power (OMA) (Peak to Peak)<br>28.05Gb/s  | Tx,OMA | 479  |      |      | uW    |        |

| Modulated Optical Output Power (OMA) (Peak to Peak)<br>14.025Gb/s | Tx,OMA | 331  |      |      | uW    |        |

| Modulated Optical Output Power (OMA) (Peak to Peak)<br>8.5Gb/s    | Tx,OMA | 302  |      |      | uW    |        |

| Average Optical Output Power 28.05Gb/s                            | Pout   | -6.2 |      |      | dBm   | Note 1 |

| Average Optical Output Power 14.025Gb/s                           | Pout   | -7.8 |      |      | dBm   | Note 1 |

| Average Optical Output Power 8.5Gb/s                              | Pout   | -8.2 |      |      | dBm   | Note 1 |

| Center Wavelength                                                 | λς     | 840  |      | 860  | nm    |        |

| Spectral Width – rms                                              | σrms   |      |      | 0.57 | nm    |        |

| RIN12 (OMA)                                                       | RIN    |      |      | -129 | dB/Hz |        |

| Optical Return Loss Tolerance                                     |        |      |      | 12   | dB    |        |

| Vertical Eye Closure Penalty, 28.05Gb/s                           | VECP   |      |      | 3.13 | dB    | Note 2 |

| Vertical Eye Closure Penalty, 14.025Gb/s                          | VECP   |      |      | 2.56 | dB    | Note 2 |

| Transmitter Waveform Distortion Penalty, 8.5Gb/s                  | TWDP   |      |      | 4.3  | dB    | Note 3 |

| Pout Tx_DISABLE Asserted                                          | Poff   |      |      | -35  | dBm   |        |

|                                                                   |        |      |      |      |       |        |

Notes:

1. Max Pout is the lesser of Class 1 safety limits (CDRH and EN 60825) or received power, max.

2. CDR is engaged with 28.05Gb/s and 14.025Gb/s.

3. CDR is not engaged with 8.5 Gb/s.

#### **Table 8. Receiver Optical and Electrical Characteristics**

$(Tc = 0^{\circ}C \text{ to } 70^{\circ}C, VccT, VccR = 3.3V \pm 5\%)$

| Parameter                                                                                 | Symbol          | Min | Тур | Мах  | Unit    | Notes     |

|-------------------------------------------------------------------------------------------|-----------------|-----|-----|------|---------|-----------|

| Optical Input Power, 28.05 Gb/s                                                           | P <sub>IN</sub> |     |     | +2   | dBm,avg |           |

| Optical Input Power, 14.025Gb/s and 8.5Gb/s                                               | PIN             |     |     | 0    | dBm,avg |           |

| Input Optical Modulation Amplitude, 28.05Gb/s<br>(Peak to Peak) [Unstressed Sensitivity]  | OMA             | 95  |     |      | uW,OMA  | Note 1, 5 |

| Input Optical Modulation Amplitude, 14.025Gb/s<br>(Peak to Peak) [Unstressed Sensitivity] | OMA             | 89  |     |      | uW,OMA  | Note 1    |

| Input Optical Modulation Amplitude, 8.5Gb/s<br>(Peak to Peak) [Unstressed Sensitivity]    | OMA             | 76  |     |      | uW,OMA  | Note 1    |

| Stressed Receiver Sensitivity (OMA) 28.05Gb/s                                             |                 | 263 |     |      | uW,OMA  | Note 4, 5 |

| Stressed Receiver Sensitivity (OMA) 14.025Gb/s                                            |                 | 170 |     |      | uW,OMA  | Note 2    |

| Stressed Receiver Sensitivity (OMA) 8.5Gb/s                                               |                 | 151 |     |      | uW,OMA  | Note 3    |

| Return Loss                                                                               |                 | 12  |     |      | dB      |           |

| Loss of Signal – Assert                                                                   | Ра              | -30 |     |      | dBm,avg |           |

| Loss of Signal – De-asserted                                                              | PD              |     |     | -9.1 | dBm,avg |           |

| Loss of Signal – Hysteresis                                                               | $P_A - P_D$     | 0.5 |     |      | dB      |           |

Notes:

1. Input Optical Modulation Amplitude (commonly known as sensitivity] requires a valid Fibre Channel encoded input.

2. 14.025 Gb/s stressed received vertical eye closure penalty (ISI) min is 2.5dB.

3. 8.5 Gb/s stressed received vertical eye closure penalty (ISI) min is 3.1dB.

4. 28.05 Gb/s stressed received vertical eye closure penalty (ISI) min is 3.1dB.

5. 32GFC (28.05Gb/s) assumes a FEC encoded RS(528, 514) signal and allows a BER of 1E-6 for receiver and transmitter measurements.

#### **Table 9. Rate Select Definition**

| Function             | State | Operation                                                                                                                                                                                                                                                                                                      |

|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx Rate Select RS(1) | High  | Transmit Rate Select HIGH is defined for 32GFC operation. It configures the Tx CDR to lock on 28.05Gb/s 64b/66b encoded data, sets the Tx optical power and linear bandwidth for 32GFC operation. FEC is expected for 32GFC.                                                                                   |

|                      | Low   | Transmit Rate Select LOW auto configures the internal Tx CDR for 16GFC (CDR locked) or 8GFC (CDR bypassed) operation. Transmit optical power and linear bandwidth are opti-<br>mized accordingly. FEC is not expected for 16GFC or 8GFC. This is intended for use only with 16GFC and 8GFC traffic.            |

| Rx Rate Select RS(0) | High  | Receive Rate Select HIGH is defined for 32GFC operation. It configures the Rx CDR to lock on 28.05Gb/s 64b/66b encoded data, sets the Rx optical sensitivity and bandwidth for 32GFC operation. FEC is expected for 32GFC                                                                                      |

|                      | Low   | Receive Rate Select LOW auto configures the internal Rx CDR for 16GFC (CDR locked) or<br>8GFC (CDR bypassed) operation. Receiver optical sensitivity and linear bandwidth are op-<br>timized accordingly. FEC is not expected for 16GFC or 8GFC. This is intended for use only<br>with 16GFC and 8GFC traffic. |

Note: During Fibre Channel Link Speed Negotiation sequences, the host will control Tx Rate and Rx Rate inputs separately to accomplish link initialization. Once speed negotiation is complete, it is expected both Tx Rate and Rx Rate will be placed in the same state by the host.

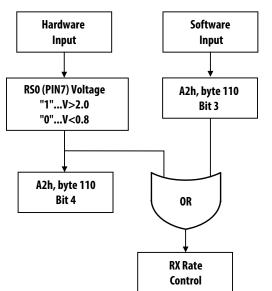

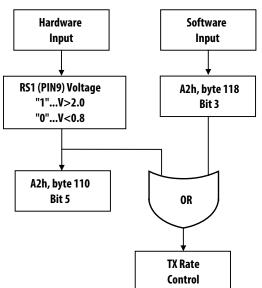

# **Rate Select Control**

RX and TX rates can be independently controlled by either hardware input pins or via register writes. Module electrical input pins 7 and 9 are used to select RX and TX rate respectively. Status of each logic level is reflected to register byte 110 bit 4 and 5 on address A2h as shown in the diagram below. RX and TX rates can also be controlled via register writes to bytes 110 bit 3 and 118 bit 3. Power on default of these bits are logic low. Hardware and software control inputs are OR'd to allow flexible control.

#### **RSO RX Rate Select control flow**

| RS1 TX | Rate | Select | control | flow |

|--------|------|--------|---------|------|

|--------|------|--------|---------|------|

| RS0 Cont | trol Input |           |                    |  |

|----------|------------|-----------|--------------------|--|

| Hardware | Software   | RX        | Operation          |  |

| 0        | 0          | 16G/8G FC | Rx CDR auto detect |  |

| 0        | 1          | 32GFC     | Rx CDR engaged     |  |

| 1        | 0          | 32GFC     | Rx CDR engaged     |  |

| 1        | 1          | 32GFC     | Rx CDR engaged     |  |

| RS1 Control Input |          |                            |                |  |

|-------------------|----------|----------------------------|----------------|--|

| Hardware          | Software | TX Operation               |                |  |

| 0                 | 0        | 16G/8G FC Tx CDR auto dete |                |  |

| 0                 | 1        | 32GFC Tx CDR engaged       |                |  |

| 1                 | 0        | 32GFC                      | Tx CDR engaged |  |

| 1                 | 1        | 32GFC                      | Tx CDR engaged |  |

#### Table 10. Transceiver SOFT DIAGNOSTIC Timing Characteristics

$(T_{C} = 0^{\circ}C \text{ to } 70^{\circ}C, VccT, VccR = 3.3V \pm 5\%)$

| Parameter                                         | Symbol           | Minimum | Maximum | Unit | Notes   |

|---------------------------------------------------|------------------|---------|---------|------|---------|

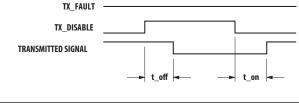

| Hardware TX_DISABLE Assert Time                   | t_off            |         | 100     | μs   | Note 1  |

| Hardware TX_DISABLE Negate Time                   | t_on             |         | 2       | ms   | Note 2  |

| Time to initialize, including reset of TX_FAULT   | t_init           |         | 300     | ms   | Note 3  |

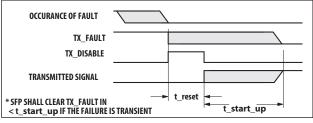

| Hardware TX_FAULT Assert Time                     | t_fault          |         | 1       | ms   | Note 4  |

| Hardware TX_DISABLE to Reset                      | t_reset          | 10      |         | μs   | Note 5  |

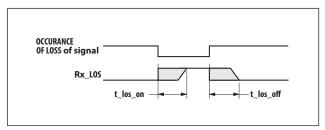

| Hardware RX_LOS DeAssert Time                     | t_loss_on        |         | 100     | μs   | Note 6  |

| Hardware RX_LOS Assert Time                       | t_loss_off       |         | 100     | μs   | Note 7  |

| Hardware RATE_SELECT Assert Time                  | t_rate_high      |         | 2       | ms   | Note 8  |

| Hardware RATE_SELECT DeAssert Time                | t_rate_low       |         | 2       | ms   | Note 8  |

| Software TX_DISABLE Assert Time                   | t_off_soft       |         | 100     | ms   | Note 9  |

| Software TX_DISABLE Negate Time                   | t_on_soft        |         | 100     | ms   | Note 10 |

| Software Tx_FAULT Assert Time                     | t_fault_soft     |         | 100     | ms   | Note 11 |

| Software Rx_LOS Assert Time                       | t_loss_on_soft   |         | 100     | ms   | Note 12 |

| Software Rx_LOS De-Assert Time                    | t_loss_off_soft  |         | 100     | ms   | Note 13 |

| Software RATE_SELECT Assert Time                  | t_rate_soft_high |         | 100     | ms   | Note 14 |

| Software RATE_SELECT DeAssert Time                | t_rate_soft_low  |         | 100     | ms   | Note 15 |

| Analog parameter data ready                       | t_data           |         | 1000    | ms   | Note 16 |

| Serial bus hardware ready                         | t_serial         |         | 300     | ms   | Note 17 |

| Serial bus buffer time                            | t_buf            | 20      |         | μs   | Note 18 |

| Complete Single or Sequential Write up to 4 Byte  | twR              |         | 40      | ms   | Note 19 |

| Complete Sequential Write of 5-8 Byte             | twR              |         | 80      | ms   |         |

| Serial Interface Clock Holdoff "Clock Stretching" | T_clock_hold     |         | 500     | μs   | Note 20 |

| Serial ID Clock Rate                              | f_serial_clock   |         | 400     | kHz  | Note 21 |

Notes

- 1. Time from rising edge of TX\_DISABLE to when the optical output falls below 10% of nominal.

- 2. Time from falling edge of TX\_DISABLE to when the modulated optical output rises above 90% of nominal.

- 3. Time from power on or falling edge of Tx\_Disable to when the modulated optical output rises above 90% of nominal.

- 4. From occurrence of fault to assertion of TX\_FAULT.

- 5. Time TX\_DISABLE must be held high to reset the laser fault shutdown circuitry.

- 6. Time from loss of optical signal to Rx\_LOS Assertion.

- 7. Time from valid optical signal to Rx\_LOS De-Assertion.

- 8. Time from rising or falling edge of Rate\_Select input until transceiver is successfully passing traffic as designated by RS(0) and RS(1). For Rate\_Se-lect going high, the internal CDR will lock on valid 32GFC encoded data within the specified time. For Rate\_Select going low, the internal CDR will attempt to lock on valid 16GFC encoded data for a certain gating period. If valid 16GFC data is not detected in that gating period, the inter-nal CDR will automatically be bypassed for use at 8GFC rates.

- 9. Time from two-wire interface assertion of TX\_DISABLE (A2h, byte 110, bit 6) to when the optical output falls below 10% of nominal. Measured from falling clock edge after stop bit of write transaction.

- 10. Time from two-wire interface de-assertion of TX\_DISABLE (A2h, byte 110, bit 6) to when the optical output rises above 90% of nominal.

- 11. Time from fault to two-wire interface TX\_FAULT (A2h, byte 110, bit 2) asserted.

- 12. Time for two-wire interface assertion of Rx\_LOS (A2h, byte 110, bit 1) from loss of optical signal.

- 13. Time for two-wire interface de-assertion of Rx\_LOS (A2h, byte 110, bit 1) from presence of valid optical signal.

- 14. Time from two-wire interface Assertion of Rate\_Select (either RS(0) in A2h, byte 110, bit 3 or RS(1) in A2h, byte 118, bit 3) to when the respective CDR is engaged at 32GCFC data rate.

- 15. Time from two-wire interface De-Assertion of Rate\_Select (either RS(0) in A2h, byte 110, bit 3 or RS(1) in A2h, byte 118, bit 3) to when the respective CDR is either engaged at 16GFC data rate or bypassed for 8GFC operation.

- 16. From power on to data ready bit asserted (A2h, byte 110, bit 0). Data ready indicates analog monitoring circuitry is functional.

- 17. Time from power on until module is ready for data transmission over the serial bus (reads or writes over A0h and A2h).

- 18. Time between START and STOP commands.

- 19. Time from stop bit to completion of a 1-8 byte write command.

- 20. Maximum time the SFP+ module may hold the SCL line low before continuing with a read or write operation.

- 21. With a maximum Clock Stretch of 500us. A maximum of 100kHz operation can be supported without a Clock Stretch.

### Table 11. Transceiver Digital Diagnostic Monitor (Real Time Sense) Characteristics

(T<sub>C</sub> = 0°C to 70°C, VccT, VccR =  $3.3V \pm 5\%$ )

| Parameter                                            | Symbol           | Min.  | Units | Notes                                                                                                                                                         |

|------------------------------------------------------|------------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver Internal<br>Temperature Accuracy         | T <sub>INT</sub> | ± 3.0 | °C    | Temperature is measured internal to the transceiver.<br>Valid from = $0^{\circ}$ C to 70 °C case temperature.                                                 |

| Transceiver Internal Supply<br>Voltage Accuracy      | V <sub>INT</sub> | ±0.1  | V     | Supply voltage is measured internal to the transceiver and can, with less accuracy, be correlated to voltage at the SFP Vcc pin. Valid over $3.3 V \pm 5\%$ . |

| Transmitter Laser DC Bias<br>Current Accuracy        | I <sub>INT</sub> | ± 10  | %     | $I_{\text{INT}}$ is better than $\pm 10\%$ of the nominal value.                                                                                              |

| Transmitted Average Optical<br>Output Power Accuracy | P <sub>T</sub>   | ± 3.0 | dB    | Coupled into 50um multi-mode fiber. Valid from -8.2dBm to +2dBm avg.                                                                                          |

| Received Optical Input Power<br>Accuracy             | P <sub>R</sub>   | ± 3.0 | dB    | Coupled from 50um multi-mode fiber. Valid from<br>-10.3dBm to +2dBm avg.                                                                                      |

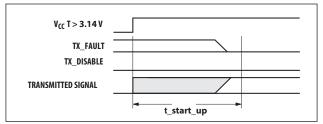

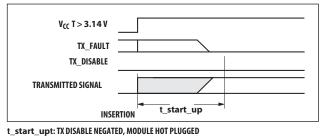

t\_start\_up: TX DISABLE NEGATED

**OCCURANCE OF FAULT**

TRANSMITTED SIGNAL

OCCURANCE OF FAULT

TRANSMITTED SIGNAL

\* SFP SHALL CLEAR TX\_FAULT IN < t\_start\_up IF THE FAILURE IS TRANSIENT

TX\_FAULT

TX\_DISABLE

tx\_fault\_on: TX FAULT ASSERTED, TX SIGNAL NOT RECOVERED

TX\_FAULT

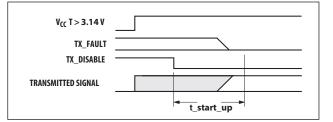

t\_start\_up: TX DISABLE ASSERTED

t\_los\_on & t\_los\_off

tx\_fault\_on: TX DISABLE ASSERTED THEN NEGATED, TX SIGNAL NOT RECOVERED

Figure 4. Transceiver timing diagrams (module installed except where noted)

tx\_fault\_on

t\_reset

tx\_fault\_on

t\_start\_up\*

Avago Technologies Proprietary

| Byte #<br>Decimal | Hex | Description                                                 | Byte #<br>Decimal | Hex | Description                                                            |

|-------------------|-----|-------------------------------------------------------------|-------------------|-----|------------------------------------------------------------------------|

| 0                 | 03  | SFP physical device                                         | 38                | 17  | Hex Byte of Vendor OUI [4]                                             |

| 1                 | 04  | SFP function defined by serial ID only                      | 39                | 6A  | Hex Byte of Vendor OUI [4]                                             |

| 2                 | 07  | LC optical connector                                        | 40                | 41  | "A" - Vendor Part Number ASCII Character                               |

| 3                 | 00  |                                                             | 41                | 46  | "F" - Vendor Part Number ASCII Character                               |

| 4                 | 00  |                                                             | 42                | 42  | "B" - Vendor Part Number ASCII Character                               |

| 5                 | 00  |                                                             | 43                | 52  | "R" - Vendor Part Number ASCII Character                               |

| 6                 | 00  |                                                             | 44                | 2D  | "-" - Vendor Part Number ASCII Character                               |

| 7                 | 60  | Short and Intermediate link distance (per FC-PI-6)          | 45                | 35  | "5" - Vendor Part Number ASCII Character                               |

| 8                 | 40  | Shortwave laser without OFC (open fiber control)            | 46                | 37  | "7" - Vendor Part Number ASCII Character                               |

| 9                 | 04  | Multi-mode 50um optical media                               | 47                | 47  | "G" - Vendor Part Number ASCII Character                               |

| 10                | 68  | 800, 1600 & 3200 MBytes/sec FC-PI-6 speed [1]               | 48                | 35  | "5" - Vendor Part Number ASCII Character                               |

| 11                | 06  | 64B/66B data at 32GFC/16GFC & 8B/10B at 8GFC                | 49                | 4D  | "M" - Vendor Part Number ASCII Character                               |

| 12                | FF  | Greater than 25.5Gb/s (See Address 66)                      | 50                | 5A  | "Z" - Vendor Part Number ASCII Character                               |

| 13                | 0C  | Rate Select (High=32GFC, Low=16GFC, 8GFC)                   | 51                | 20  | " " - Vendor Part Number ASCII Character                               |

| 14                | 00  |                                                             | 52                | 20  | " " - Vendor Part Number ASCII Character                               |

| 15                | 00  |                                                             | 53                | 20  | " " - Vendor Part Number ASCII Character                               |

| 16                | 02  | 20m of OM2 50/125um distance at 32GFC <sup>[2]</sup>        | 54                | 20  | " " - Vendor Part Number ASCII Character                               |

| 17                | 00  | Unspecified OM1 62.5/125um distance at 32GFC <sup>[3]</sup> | 55                | 20  | " " - Vendor Part Number ASCII Character                               |

| 18                | 0A  | 100m of OM4 50/125um fiber at 32GFC <sup>[10]</sup>         | 56                | 20  | " " - Vendor Revision ASCII Character                                  |

| 19                | 07  | 70m of OM3 50/125um fiber at 32GFC <sup>[9]</sup>           | 57                | 20  | " " - Vendor Revision ASCII Character                                  |

| 20                | 41  | "A" - Vendor Name ASCII Character                           | 58                | 20  | " " - Vendor Revision ASCII Character                                  |

| 21                | 56  | "V" - Vendor Name ASCII Character                           | 59                | 20  | " " - Vendor Revision ASCII Character                                  |

| 22                | 41  | "A" - Vendor Name ASCII Character                           | 60                | 03  | Hex Byte of Laser Wavelength [5]                                       |

| 23                | 47  | "G" - Vendor Name ASCII Character                           | 61                | 52  | Hex Byte of Laser Wavelength <sup>[5]</sup>                            |

| 24                | 4F  | "O" - Vendor Name ASCII Character                           | 62                | 00  |                                                                        |

| 25                | 20  | " " - Vendor Name ASCII Character                           | 63                |     | Checksum for Bytes 0-62 <sup>[6]</sup>                                 |

| 26                | 20  | " " - Vendor Name ASCII Character                           | 64                | 08  | CDRs present. 1W power class                                           |

| 27                | 20  | " " - Vendor Name ASCII Character                           | 65                | 3A  | Hardware Tx_Disable, Tx_Fault, Rx_LOS,<br>Rate_Select                  |

| 28                | 20  | " " - Vendor Name ASCII Character                           | 66                | 70  | 28.050 Gbit/sec nominal bit rate (32GFC)                               |

| 29                | 20  | " " - Vendor Name ASCII Character                           | 67                | 00  |                                                                        |

| 30                | 20  | " " - Vendor Name ASCII Character                           | 68 - 83           |     | Vendor Serial Number ASCII characters [7]                              |

| 31                | 20  | " " - Vendor Name ASCII Character                           | 84 - 91           |     | Vendor Date Code ASCII characters [8]                                  |

| 32                | 20  | " " - Vendor Name ASCII Character                           | 92                | 68  | Digital diagnostics, Internal Cal, Rx Pwr Avg                          |

| 33                | 20  | " " - Vendor Name ASCII Character                           | 93                | FA  | Alarms/Warnings, Software Tx_Disable,<br>Tx-Fault, Rx_LOS, Rate_Select |

| 34                | 20  | " " - Vendor Name ASCII Character                           | 94                | 08  | SFF-8472 compliance to revision 12.2                                   |

| 35                | 20  | " " - Vendor Name ASCII Character                           | 95                |     | Checksum for Bytes 62-94 <sup>[6]</sup>                                |

| 36                | 00  |                                                             | 96 – 255          | 00  |                                                                        |

| 37                | 00  | Hex Byte of Vendor OUI <sup>[4]</sup>                       |                   |     |                                                                        |

|                   |     |                                                             |                   |     |                                                                        |

#### Table 12. EEPROM Serial ID Memory Contents – Address A0h

Notes:

1. FC-PI-6 speed 3200 MBytes/sec is a serial bit rate of 28.05Gb/s using FEC encoded data (RS 528/514). FC-PI-5 speed 1600 MBytes/sec is a serial bit rate of 14.025Gb/s. 800 MBytes/sec is a serial bit rate of 8.5Gb/s.

2. Link distance with OM2 50/125um cable at 16GFC is 35m and at 8GFC is 50m.

3. Link distance with OM1 62.5/125um cable at 8.5Gb/s is 25m (and is unspecified at 16GFC).

4. The IEEE Organizationally Unique Identified (OUI) assigned to Avago Technologies is 00-17-6A (3 bytes of hex).

5. Laser Wavelength is represented in 16 unsigned bits. The hex representation of 850nm is 0352.

6. Addresses 63 and 95 are checksums calculated (per SFF-8472 and SFF-8074) and stored prior to product shipment.

7. Address 68-83 specify the AFBR-57G5MZ ASCII serial number and will vary on a per unit basis.

8. Address 84-91 specify the AFBR-57G5MZ ASCII date code and will vary on a per date code basis.

9. Link distance with OM3 50/125um cable at 16GFC is 100m and at 8GFC is 150m.

10. Link distance with OM4 50/125um cable at 16GFC is 125m and at 8GFC is 190m.

| Byte #  |                           | Byte #  |                                    | Byte #  |                                     |

|---------|---------------------------|---------|------------------------------------|---------|-------------------------------------|

| Decimal | Notes                     | Decimal | Notes                              | Decimal | Notes                               |

| 0       | Temp H Alarm MSB [1]      | 26      | Tx Power L Alarm MSB [4]           | 104     | Real Time Rx Power MSB [5]          |

| 1       | Temp H Alarm LSB [1]      | 27      | Tx Power L Alarm LSB [4]           | 105     | Real Time Rx Power LSB [5]          |

| 2       | Temp L Alarm MSB [1]      | 28      | Tx Power H Warning MSB [4]         | 106     | Reserved                            |

| 3       | Temp L Alarm LSB [1]      | 29      | Tx Power H Warning LSB [4]         | 107     | Reserved                            |

| 4       | Temp H Warning MSB [1]    | 30      | Tx Power L Warning MSB [4]         | 108     | Reserved                            |

| 5       | Temp H Warning LSB [1]    | 31      | Tx Power L Warning LSB [4]         | 109     | Reserved                            |

| 6       | Temp L Warning MSB [1]    | 32      | Rx Power H Alarm MSB [5]           | 110     | Status/Control – See Table 14       |

| 7       | Temp L Warning LSB [1]    | 33      | Rx Power H Alarm LSB [5]           | 111     | Status/Control – See Table 15       |

| 8       | Vcc H Alarm MSB [2]       | 34      | Rx Power L Alarm MSB [5]           | 112     | Flag Bits – See Table 16            |

| 9       | Vcc H Alarm LSB [2]       | 35      | Rx Power L Alarm LSB [5]           | 113     | Flag Bits – See Table 16            |

| 10      | Vcc L Alarm MSB [2]       | 36      | Rx Power H Warning MSB [5]         | 114     | Tx Input EQ Control - See Table 19, |

|         |                           |         |                                    |         | 20                                  |

| 11      | Vcc L Alarm LSB [2]       | 37      | Rx Power H Warning LSB [5]         | 115     | Rx Output Emphasis Control - See    |

|         |                           |         |                                    |         | Table 21, 22                        |

| 12      | Vcc H Warning MSB [2]     | 38      | Rx Power L Warning MSB [5]         | 116     | Flag Bits – See Table 16            |

| 13      | Vcc H Warning LSB [2]     | 39      | Rx Power L Warning LSB [5]         | 117     | Flag Bits – See Table 16            |

| 14      | Vcc L Warning MSB [2]     | 40-55   | Control Settings – See Table 18    | 118     | Status/Control – See Table 17       |

| 15      | Vcc L Warning LSB [2]     | 56-94   | External Calibration Constants [6] | 119     | CDR Loss of Lock Status - See Table |

|         |                           |         |                                    |         | 18                                  |

| 16      | Tx Bias H Alarm MSB[3]    | 95      | Checksum for Bytes 0-94 [7]        | 120-126 | Reserved                            |

| 17      | Tx Bias H Alarm LSB[3]    | 96      | Real Time Temperature MSB [1]      | 127     | Page Select Control                 |

| 18      | Tx Bias L Alarm MSB [3]   | 97      | Real Time Temperature LSB [1]      | 128-247 | Customer Writable                   |

| 19      | Tx Bias L Alarm LSB[3]    | 98      | Real Time Vcc MSB [2]              | 248-255 | Vendor Specific                     |

| 20      | Tx Bias H Warning MSB[3]  | 99      | Real Time Vcc LSB [2]              |         |                                     |

| 21      | Tx Bias H Warning LSB[3]  | 100     | Real Time Tx Bias MSB [3]          |         |                                     |

| 22      | Tx Bias L Warning MSB [3] | 101     | Real Time Tx Bias LSB [3]          |         |                                     |

| 23      | Tx Bias L Warning LSB[3]  | 102     | Real Time Tx Power MSB [4]         |         |                                     |

| 24      | Tx Power H Alarm MSB [4]  | 103     | Real Time Tx Power LSB [4]         |         |                                     |

| 25      | Tx Power H Alarm LSB [4]  |         |                                    |         |                                     |

# Table 13. EEPROM Serial ID Memory Contents - Enhanced SFP Memory (Address A2h)

Notes:

1. Temperature (Temp) is decoded as a 16 bit signed two's complement integer in increments of 1/256 °C.

2. Supply Voltage (Vcc) is decoded as a 16 bit unsigned integer in increments of  $100 \,\mu$ V.

3. Tx bias current (Tx Bias) is decoded as a 16 bit unsigned integer in increments of 2  $\mu$ A.

4. Transmitted average optical power (Tx Pwr) is decoded as a 16 bit unsigned integer in increments of 0.1 µW.

5. Received average optical power (Rx Pwr) is decoded as a 16 bit unsigned integer in increments of 0.1 µW.

6. Bytes 56-94 are not intended for use, but have been set to default values per SFF-8472.

7. Byte 95 is a checksum calculated (per SFF-8472) and stored prior to product shipment.

| Bit # | Status/Control Name     | Description                                                                         | Notes     |

|-------|-------------------------|-------------------------------------------------------------------------------------|-----------|

| 7     | TX_DISABLE State        | Digital state of TX_DISABLE Input Pin (1 = TX_DISABLE asserted)                     | Note 1    |

| 6     | Soft TX_DISABLE Control | Read/write bit for changing digital state of TX_DISABLE function                    | Note 1, 2 |

| 5     | RS(1) State             | Digital state of TX Rate_Select Input Pin RS(1) (1 = Rate High asserted)            |           |

| 4     | RS(0) State             | Digital state of RX Rate_Select Input Pin RS(0) (1 = Rate High asserted)            |           |

| 3     | Soft RS(0) Control      | Read/write bit for changing digital state of Rx Rate_Select RS(0) function          | Note 3    |

| 2     | TX_FAULT State          | Digital state of TX_FAULT Output Pin (1 = TX_FAULT asserted)                        | Note 1    |

| 1     | RX_LOS State            | Digital state of SFP RX_LOS Output Pin (1 = RX_LOS asserted)                        | Note 1    |

| 0     | Data Ready (Bar)        | Indicates transceiver is powered and real time sense data is ready (0 = Data Ready) |           |

| lotes |                         |                                                                                     |           |

# Table 14. EEPROM Serial ID Memory Contents – Soft Commands (Address A2h, Byte 110).

Notes:

1. The response time for soft commands of the AFBR-57G5MZ is 100msec as specified by MSA SFF-8472.

2. Bit 6 is logic OR'd with the SFP TX\_DISABLE input pin 3 .... either asserted will disable the SFP transmitter.

3. Bit 3 is logic OR'd with the SFP RS(0) RX Rate\_Select input pin 7 .... either asserted will set receiver to Rate = High.

| Bit # | Status/Control Name          | Description                                                                                                                                                                                                                                                           | Notes |

|-------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3-7   | Reserved                     |                                                                                                                                                                                                                                                                       |       |

| 2     | OWRAP Control Bit            | Logic Low = OWRAP disabled. Logic High = OWRAP enabled. When enabled, OW-<br>RAP routes incoming SFP Rx optical data to the Tx optical output and Rx electrical<br>output. Enabling clears all other bits in byte 111.                                                |       |

| 1     | EWRAP FORWARD<br>Control Bit | Logic Low = FORWARD disabled. Logic High = FORWARD enabled. When used in combination with EWRAP enable, FORWARD routes incoming SFP Tx electrical data to both Rx electrical output and Tx optical output. Enabling sets bit 0 and clears all other bits in byte 111. |       |

| 0     | EWRAP Control Bit            | Logic Low = EWRAP disabled. Logic High = EWRAP enabled. When enabled,<br>EWRAP routes incoming SFP Tx electrical data to the Rx electrical output. Enabling<br>clears all other bits in byte 111.                                                                     |       |

| Byte | Bit | Flag Bit Name         | Description                                                                  |

|------|-----|-----------------------|------------------------------------------------------------------------------|

| 112  | 7   | Temp High Alarm       | Set when transceiver internal temperature exceeds high alarm threshold.      |

|      | 6   | Temp Low Alarm        | Set when transceiver internal temperature exceeds low alarm threshold.       |

|      | 5   | Vcc High Alarm        | Set when transceiver internal supply voltage exceeds high alarm threshold.   |

|      | 4   | Vcc Low Alarm         | Set when transceiver internal supply voltage exceeds low alarm threshold.    |

|      | 3   | Tx Bias High Alarm    | Set when transceiver laser bias current exceeds high alarm threshold.        |

|      | 2   | Tx Bias Low Alarm     | Set when transceiver laser bias current exceeds low alarm threshold.         |

|      | 1   | Tx Power High Alarm   | Set when transmitted average optical power exceeds high alarm threshold.     |

|      | 0   | Tx Power Low Alarm    | Set when transmitted average optical power exceeds low alarm threshold.      |

| 113  | 7   | Rx Power High Alarm   | Set when received average optical power exceeds high alarm threshold.        |

|      | 6   | Rx Power Low Alarm    | Set when received average optical power exceeds low alarm threshold.         |

|      | 0-5 | reserved              |                                                                              |

| 116  | 7   | Temp High Warning     | Set when transceiver internal temperature exceeds high warning threshold.    |

|      | 6   | Temp Low Warning      | Set when transceiver internal temperature exceeds low warning threshold.     |

|      | 5   | Vcc High Warning      | Set when transceiver internal supply voltage exceeds high warning threshold. |

|      | 4   | Vcc Low Warning       | Set when transceiver internal supply voltage exceeds low warning threshold.  |

|      | 3   | Tx Bias High Warning  | Set when transceiver laser bias current exceeds high warning threshold.      |

|      | 2   | Tx Bias Low Warning   | Set when transceiver laser bias current exceeds low warning threshold.       |

|      | 1   | Tx Power High Warning | Set when transmitted average optical power exceeds high warning threshold.   |

|      | 0   | Tx Power Low Warning  | Set when transmitted average optical power exceeds low warning threshold.    |

| 117  | 7   | Rx Power High Warning | Set when received average optical power exceeds high warning threshold.      |

|      | 6   | Rx Power Low Warning  | Set when received average optical power exceeds low warning threshold.       |

|      | 0-5 | reserved              |                                                                              |

# Table 16. EEPROM Serial ID Memory Contents – Alarms and Warnings (Address A2h, Bytes 112, 113, 116, 117)

# Table 17. EEPROM Serial ID Memory Contents – Soft Commands (Address A2h, Byte 118).

| Bit # | Status/Control Name | Description                                                                      | Notes  |

|-------|---------------------|----------------------------------------------------------------------------------|--------|

| 4-7   | Reserved            |                                                                                  |        |

| 3     | Soft RS(1) Control  | Read/write bit for changing digital state of Tx Rate_Select RS(1) function       | Note 1 |

| 2     | Reserved            |                                                                                  | ·      |

| 1     | Power Level State   | Always set to zero. Value of zero indicates Power Level 1 operation (1 Watt max) |        |

| 0     | Power Level Select  | Unused. This device supports power level zero (1 Watt max) only.                 |        |

| Notos |                     |                                                                                  |        |

Notes:

1. Bit 3 is log OR'd with the SFP RS(1) TX Rate\_Select input pin 9 .... either asserted will set transmitter to Rate = High.

#### Table 18. EEPROM Serial ID Memory Contents – CDR Loss of Lock (LOL) Status Indicators (Address A2h, Byte 119).

| Bit # | Status/Control Name | Description                                                                                                                                                              | Notes |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7-2   | Reserved            |                                                                                                                                                                          |       |

| 1     | Tx CDR LOL Flag     | A value of 0 indicates the CDR is locked. A value of 1 indicates CDR loss of lock. If the CDR is operationally bypassed (ie. for 8.5Gb/s operation), value is undefined. |       |

| 0     | Rx CDR LOL Flag     | A value of 0 indicates the CDR is locked. A value of 1 indicates CDR loss of lock. If the CDR is operationally bypassed (ie. for 8.5Gb/s operation), value is undefined. |       |

| Bit # Status/Control Name Description |                   | Description                                                                             |  |

|---------------------------------------|-------------------|-----------------------------------------------------------------------------------------|--|

| 7-4                                   | TX EQ, RS(1)=HIGH | Selects an input equalization value per Table 9-13 of SFF-8472 for high rate operation. |  |

| 3-0                                   | TX EQ, RS(1)=LOW  | Selects an input equalization value per Table 9-13 of SFF-8472 for low rate operation.  |  |

# Table 19. EEPROM Serial ID Memory Contents – Transmitter Input Electrical Equalization Control (Address A2h, Byte 114).

# Table 20. Transmitter Input Equalization Control Values (Address A2h, Byte 114)

From Table 9-13 of SFF-8472

|      | Transmitter Input Equalization |                 |  |

|------|--------------------------------|-----------------|--|

| Code | Nominal                        | Units           |  |

| 11xx | Reserved                       |                 |  |

| 1011 | Reserved                       |                 |  |

| 1010 | 10                             | dB              |  |

| 1001 | 9                              | dB              |  |

| 1000 | 8                              | dB              |  |

| 0111 | 7                              | dB              |  |

| 0110 | 6                              | dB              |  |

| 0101 | 5                              | dB              |  |

| 0100 | 4                              | dB              |  |

| 0011 | 3                              | dB              |  |

| 0010 | 2                              | dB              |  |

| 0001 | 1                              | dB              |  |

| 0000 | 0                              | No Equalization |  |

|      |                                |                 |  |

# Table 21. EEPROM Serial ID Memory Contents – Receiver Output Electrical Emphasis Control (Address A2h, Byte 115).

| Bit # | Status/Control Name | Description                                                                          |  |

|-------|---------------------|--------------------------------------------------------------------------------------|--|

| 7-4   | RX EMPH, RS(0)=HIGH | Selects an output emphasis value per Table 9-14 of SFF-8472 for high rate operation. |  |

| 3-0   | RX EMPH, RS(0)=LOW  | Selects an output emphasis value per Table 9-14 of SFF-8472 for low rate operation.  |  |

# Table 22. Receiver Output Emphasis Control Values (Address A2h, Byte 115)

From Table 9-14 of SFF-8472

|      | Receiver Output Emphasis<br>At nominal Output Amplitude |             |  |

|------|---------------------------------------------------------|-------------|--|

| Code | Nominal                                                 | Units       |  |

| 1xxx | Vendor Specific                                         |             |  |

| 0111 | 7                                                       | dB          |  |

| 0110 | 6                                                       | dB          |  |

| 0101 | 5                                                       | dB          |  |

| 0100 | 4                                                       | dB          |  |

| 0011 | 3                                                       | dB          |  |

| 0010 | 2                                                       | dB          |  |

| 0001 | 1                                                       | dB          |  |

| 0000 | 0                                                       | No Emphasis |  |

Figure 5. Module drawing

Figure 6. Module Label

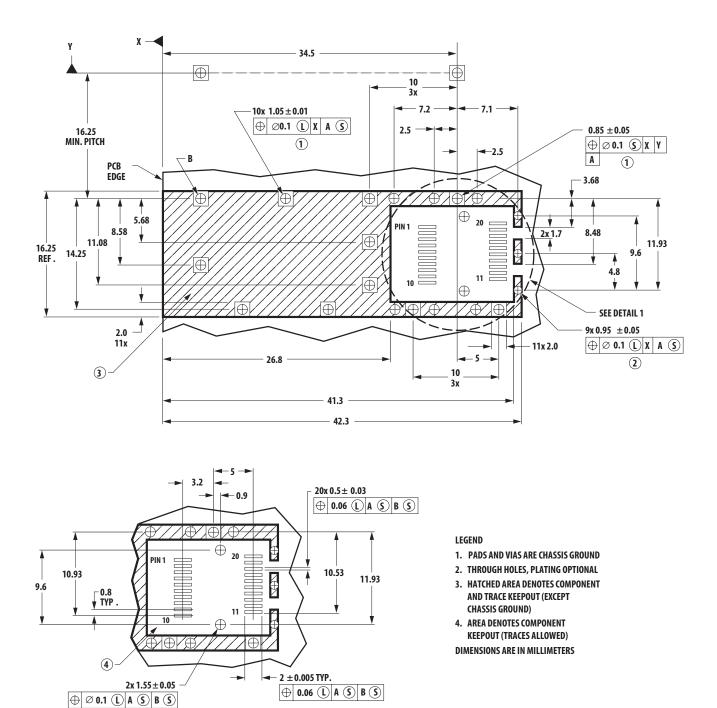

Figure 7. SFP host board mechanical layout

DETAIL 1

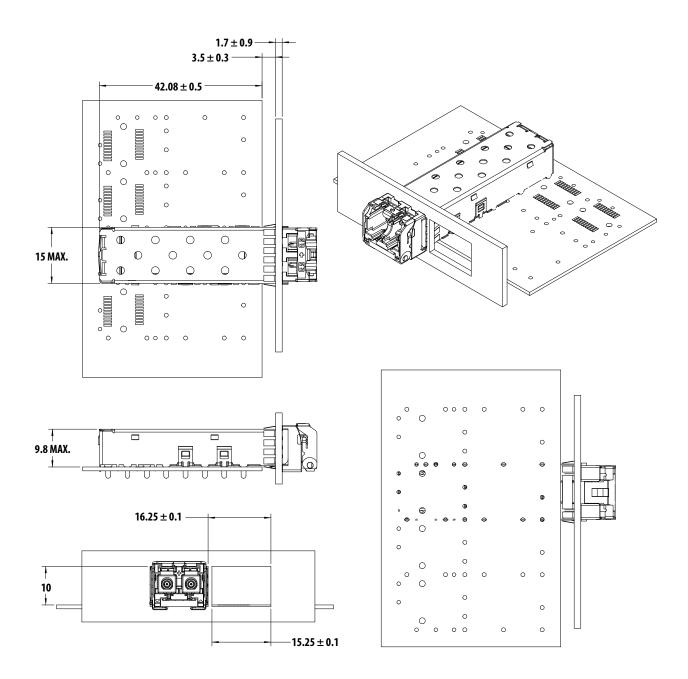

#### Figure 8. SFP Assembly drawing

# **Customer Manufacturing Processes**

This module is pluggable and is not designed for aqueous wash, IR reflow, or wave soldering processes.

For product information and a complete list of distributors, please go to our website: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2015-2016 Avago Technologies. All rights reserved. pub-005170 - October 19,2016

Avago Technologies Proprietary