## Automotive Three Phase Sinusoidal Fan Driver

## **Features and Benefits**

- Full 3-phase sinusoidal drive

- PWM speed input

- · Analog speed input

- FG speed output

- Lock detection

- Current limiting

- Output short circuit protection

- Dynamic lead angle control

## **Applications:**

• Automotive blower

Not to scale

- Air conditioning

- Air movement

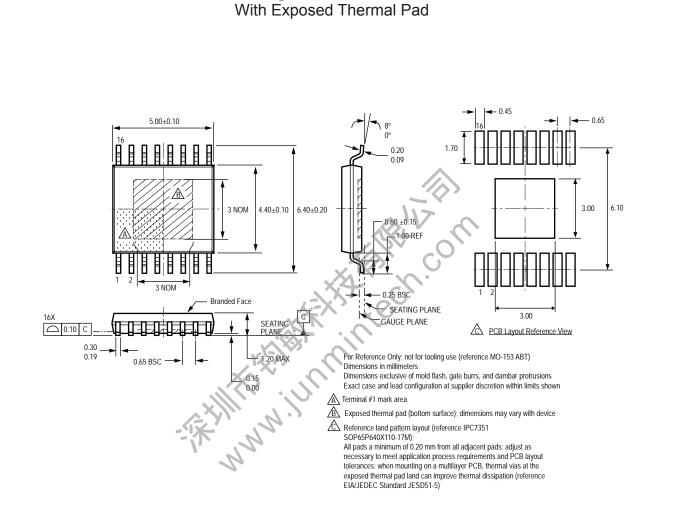

# Package: 16-pin TSSOP with Exposed Thermal Pad (suffix LP)

## Description

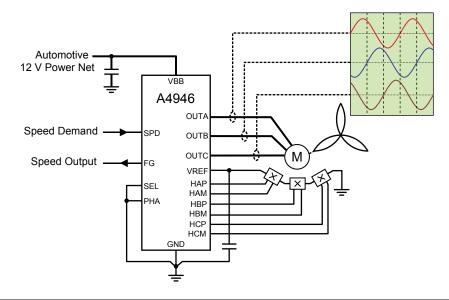

The A4946 is a low noise, three phase motor driver with integrated power bridge suitable for driving small fans and blowers in automotive systems. Motor audible noise and vibration is reduced by driving the phases with sinusoidal PWM excitation. Motor current is controlled using PWM techniques to minimize the power dissipation.

Rotor position is determined by Hall effect elements. These provide direct inputs to the integrated commutation and excitation logic.

In addition to speed control by varying the supply voltage, motor speed can be controlled using a variable duty cycle PWM input or a variable voltage analog input. This allows system cost savings by eliminating the requirement for an external variable power supply. Motor speed is indicated each full commutation cycle by a single digital output.

The A4946 incorporates motor lock detection, current limiting, supply overvoltage and undervoltage detection, short circuit protection, and overtemperature protection.

The A4946 is supplied in a 16-pin TSSOP power package with an exposed thermal pad (package type LP). This package is lead (Pb) free with 100% matte-tin lead frame plating.

## Typical Application Diagram

#### **Selection Guide**

| Part N | umber   | Packing              | Package                                                                       |

|--------|---------|----------------------|-------------------------------------------------------------------------------|

| A49460 | SLPTR-T | 1500 pieces per reel | 4.4 mm x 5 mm, 1.2 mm nominal height<br>16-pin TSSOP with exposed thermal pad |

### Absolute Maximum Ratings with respect to GND

| Characteristic                             | Symbol              | Notes                                             | Rating     | Unit |

|--------------------------------------------|---------------------|---------------------------------------------------|------------|------|

| Drive Supply Voltage                       | V <sub>BB</sub>     |                                                   | -0.3 to 50 | V    |

| Pins SPD, SEL, PHA                         | -                   |                                                   | -0.3 to 6  | V    |

| Pin FG                                     | _                   |                                                   | –0.3 to 6  | V    |

| Pins HAP, HAM, HBP, HBM, HCP,<br>HCM       | -                   | R.V.R                                             | –0.3 to 6  | V    |

| Pin VREF                                   | -                   |                                                   | -0.3 to 6  | V    |

| Ambient Operating Temperature<br>Range     | T <sub>A</sub>      | Temperature Range G, limited by power dissipation | -40 to 105 | °C   |

| Maximum Continuous Junction<br>Temperature | T <sub>J(max)</sub> | AFX' C                                            | 150        | °C   |

| Storage Temperature Range                  | T <sub>stg</sub>    |                                                   | -55 to 150 | °C   |

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol           | Test Conditions*                                                  | Value | Unit |

|----------------------------|------------------|-------------------------------------------------------------------|-------|------|

| Package Thermal Resistance | D                | On 4-layer PCB based on JEDEC standard                            | 34    | °C/W |

| Tackage memainesistance    | K <sub>0JA</sub> | On 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 43    | °C/W |

\*Additional thermal information available on the Allegro website.

| Table of Contents                 |         |                                         |          |  |  |  |  |

|-----------------------------------|---------|-----------------------------------------|----------|--|--|--|--|

| Functional Block Diagram          | 3       | Operation During Start                  | 10       |  |  |  |  |

| Pin-out Diagram and Terminal List | 4       | Transition to Sinusoidal Operating Mode | 11       |  |  |  |  |

| Electrical Characteristics Table  | 5       | Soft Start<br>Lock Detect               | 11<br>12 |  |  |  |  |

| Commutation Timing Diagram        | 7       | Current Limit                           | 12       |  |  |  |  |

| Commutation and Phase Tables      | 8       | Output Short Circuit Protection         | 12       |  |  |  |  |

| Functional Description            | 9       | Phase Advance                           | 12       |  |  |  |  |

| Pin Functions                     | 9       | Application Information                 | 13       |  |  |  |  |

| Operation<br>Speed Control        | 9<br>10 | Package Outline Drawing                 | 14       |  |  |  |  |

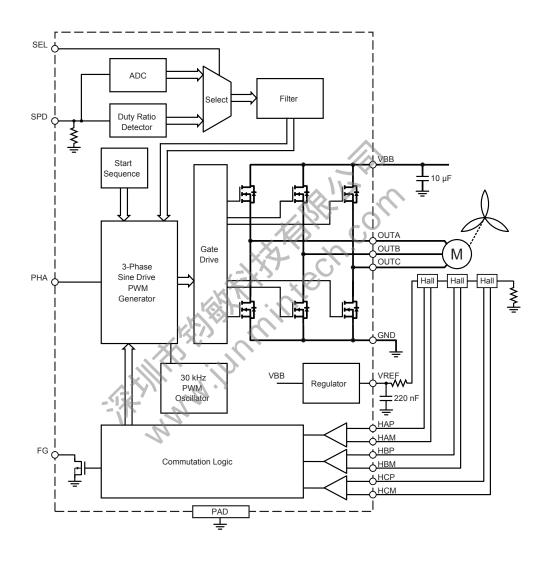

## **Functional Block Diagram**

#### **Pin-out Diagram**

| HAP 1<br>HAM 2<br>HBP 3<br>HBP 4<br>HBP 4<br>HCP 5<br>HCM 6<br>PHA 7<br>VREF 8<br>Terminal List Table |       |                                     |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-------|-------------------------------------|--|--|--|--|--|--|--|

| Number                                                                                                | Name  | Function                            |  |  |  |  |  |  |  |

| 1                                                                                                     | HAP   | Hall element A input                |  |  |  |  |  |  |  |

| 2                                                                                                     | HAM   | Hall element A input                |  |  |  |  |  |  |  |

| 3                                                                                                     | HBP   | Hall element B input                |  |  |  |  |  |  |  |

| 4                                                                                                     | НВМ   | Hall element B input                |  |  |  |  |  |  |  |

| 5                                                                                                     | HCP - | Hall element C Input                |  |  |  |  |  |  |  |

| 6                                                                                                     | НСМ   | Hall element C input                |  |  |  |  |  |  |  |

| 7                                                                                                     | PHA   | Phase advance input                 |  |  |  |  |  |  |  |

| 8                                                                                                     | VREF  | Analog reference voltage            |  |  |  |  |  |  |  |

| 9                                                                                                     | VBB   | Supply voltage                      |  |  |  |  |  |  |  |

| 10                                                                                                    | OUTC  | Motor phase C output                |  |  |  |  |  |  |  |

| 11                                                                                                    | OUTB  | Motor phase B output                |  |  |  |  |  |  |  |

| 12                                                                                                    | GND   | Ground                              |  |  |  |  |  |  |  |

| 13                                                                                                    | OUTA  | Motor phase A output                |  |  |  |  |  |  |  |

| 14                                                                                                    | FG    | Speed output                        |  |  |  |  |  |  |  |

| 15                                                                                                    | SEL   | Speed control mode input            |  |  |  |  |  |  |  |

| 16                                                                                                    | SPD   | Speed demand input                  |  |  |  |  |  |  |  |

| _                                                                                                     | PAD   | Exposed thermal pad, connect to GND |  |  |  |  |  |  |  |

4

### **ELECTRICAL CHARACTERISTICS** Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{BB} = 6.5$ to 28 V; unless otherwise specified

| Characteristic Symbol                            |                     | Test Conditions                                                           | Min.     | Тур.  | Max.              | Unit              |

|--------------------------------------------------|---------------------|---------------------------------------------------------------------------|----------|-------|-------------------|-------------------|

| Supplies                                         | 4                   |                                                                           |          | 1     |                   |                   |

|                                                  |                     | Functional, no unsafe states                                              |          | _     | 50                | V                 |

| Supply Voltage Range <sup>1</sup>                | V <sub>BB</sub>     | Outputs Driving                                                           | 4.8      | _     | V <sub>BBOV</sub> | V                 |

| Supply Quiescent Current                         | I <sub>BBQ</sub>    |                                                                           | _        | _     | 12                | mA                |

| Reference Output Voltage                         | V <sub>REF</sub>    | 0 mA > I <sub>REF</sub> > -30 mA                                          | 4.75     | 5     | 5.25              | V                 |

| Reference Dropout Voltage                        | V <sub>REFDO</sub>  | V <sub>BB</sub> = 4.8 V, I <sub>REF</sub> = -20 mA                        | _        | 500   | _                 | mV                |

| Reference Current Limit                          | I <sub>REFLIM</sub> |                                                                           | _        | 50    | _                 | mA                |

| Motor Bridge Output                              |                     | •                                                                         |          |       |                   |                   |

|                                                  |                     | V <sub>BB</sub> = 12 V, T <sub>J</sub> = 25°C                             | _        | 0.54  | 0.65              | Ω                 |

| Total On-Resistance (High-Side Plus<br>Low-Side) | R <sub>DS(on)</sub> | V <sub>BB</sub> = 12 V, T <sub>J</sub> = 150°C                            | _        | 0.9   | 1.1               | Ω                 |

|                                                  |                     | V <sub>BB</sub> = 7.0 V, T <sub>J</sub> = 25°C                            | <u> </u> | 0.85  | 1                 | Ω                 |

| Output Sense Current <sup>2</sup>                | ISENSE              | V <sub>OUT</sub> = 0 V, outputs not driving                               | -35      | -110  | -185              | μA                |

| Current Control                                  |                     |                                                                           |          |       |                   |                   |

| Dead Time                                        | t <sub>DEAD</sub>   |                                                                           | _        | 400   | _                 | ns                |

| Motor PWM Frequency                              | f <sub>PWM</sub>    | SXT G                                                                     | 28       | 30    | 32                | kHz               |

| Current Limit Threshold                          | I <sub>CL</sub>     | Per phase                                                                 | 1.35     | 1.63  | 1.91              | A                 |

| Overcurrent Off-Time                             | t <sub>OFF</sub>    |                                                                           | _        | 24    | _                 | μs                |

| Motor Control                                    |                     | 15,133                                                                    |          | •     |                   |                   |

| Start Time                                       | t <sub>ST</sub>     |                                                                           | _        | 1     | _                 | s                 |

| Disable Time                                     | t <sub>LD</sub>     |                                                                           | _        | 8     | -                 | s                 |

| Commutation Period <sup>3</sup>                  | t <sub>COMM</sub>   |                                                                           | 100      | -     | -                 | μs                |

| Drive Mode Selection Period                      | t <sub>SINOK</sub>  | Sinusoidal mode selected when $t_{COMM} < t_{SINOK}$                      | 33       | 52    | 58                | ms                |

| SPD Maximum Demand (100%)                        | VSPD <sub>MAX</sub> | SEL = 0; $V_{BB} \ge 6.5$ V and monotonic from 0 V to VSPD <sub>MAX</sub> | 4.15     | 4.25  | 4.35              | V                 |

| SPD On Threshold (25%)                           | VSPD <sub>ON</sub>  | SEL = 0                                                                   | 1.02     | 1.12  | 1.22              | V                 |

| SPD Off Threshold (12.5%)                        | VSPD <sub>OFF</sub> | SEL = 0                                                                   | 480      | 580   | 680               | mV                |

| Duty Cycle On Threshold for SPD                  | D <sub>ON</sub>     | SEL = 1                                                                   | 23.75    | 25    | 26.25             | %                 |

| Duty Cycle Off Threshold for SPD                 | D <sub>OFF</sub>    | SEL = 1                                                                   | 11.88    | 12.5  | 13.12             | %                 |

| Internal Speed Demand Slew Rate                  | t <sub>RR</sub>     |                                                                           | _        | 15.33 | _                 | ms/%FS            |

| Logic Input and Output                           |                     | ·                                                                         |          |       |                   |                   |

| Input Low Voltage (PHA, SEL, SPD)                | V <sub>IL</sub>     |                                                                           | _        | _     | 0.8               | V                 |

| Input High Voltage (PHA, SEL, SPD)               | V <sub>IH</sub>     |                                                                           | 2.0      | _     | _                 | V                 |

| Input Open Voltage Condition (PHA)               | V <sub>IOpen</sub>  |                                                                           | 47.4     | _     | 52.6              | %V <sub>REF</sub> |

| Input Hysteresis (PHA, SEL, SPD)                 | V <sub>lhys</sub>   |                                                                           | 100      | 300   | _                 | mV                |

Continued on the next page...

#### ELECTRICAL CHARACTERISTICS (continued) Valid at T<sub>J</sub> = -40°C to 150°C, V<sub>BB</sub> = 6.5 to 28 V; unless otherwise specified

| Characteristic                                              | Characteristic Symbol Test Conditions |                                                |          |      | Max. | Unit                |

|-------------------------------------------------------------|---------------------------------------|------------------------------------------------|----------|------|------|---------------------|

| Logic Input and Output (continued)                          |                                       |                                                |          |      |      |                     |

|                                                             | Р                                     | SEL pin                                        | _        | 50   | _    | kΩ                  |

| Input Pull-Down Resistor                                    | R <sub>PD</sub>                       | PHA, SPD pins                                  | _        | 100  | _    | kΩ                  |

| Input Pull-Up Resistor (PHA)                                | R <sub>PU</sub>                       |                                                | _        | 100  | _    | kΩ                  |

| Output Low Voltage (FG)                                     | V <sub>OL</sub>                       | I <sub>OL</sub> = 2 mA                         | _        | _    | 0.4  | V                   |

| Output Leakage <sup>2</sup> (FG)                            | Ι <sub>Ο</sub>                        | 0 V < V <sub>O</sub> < 5 V                     | -1       | _    | 1    | μA                  |

| Hall Element Input                                          |                                       |                                                |          |      |      |                     |

| Hall Differential Input Drive Voltage                       | V <sub>HD</sub>                       | •                                              | ±30      | _    | _    | mV <sub>pk-pk</sub> |

| Hall Input Common Mode Range                                | V <sub>HICMR</sub>                    |                                                | 1        | -    | 4    | V                   |

| Hall Input Offset Voltage                                   | V <sub>HO</sub>                       |                                                | _        | ±5   | -    | mV                  |

| Hall Input Hysteresis Voltage                               | V <sub>HDHys</sub>                    |                                                | <u> </u> | ±13  | -    | mV                  |

| Diagnostics And Protection                                  |                                       | SE al                                          |          |      |      |                     |

| VPP Over eltere Threshold                                   | V                                     | V <sub>BB</sub> rising                         | 32       | -    | 36   | V                   |

| VBB Overvoltage Threshold                                   | V <sub>BBOV</sub>                     | V <sub>BB</sub> falling                        | 28       | _    | 31   | V                   |

| VBB Overvoltage Hysteresis                                  | V <sub>BBOVHys</sub>                  |                                                | _        | 3.5  | -    | V                   |

| VBB Undervoltage Threshold                                  | V <sub>BBUV</sub>                     | V <sub>BB</sub> rising                         | 3.6      | -    | 4.1  | V                   |

| VBB Ondervoltage Threshold                                  | ▼BB0V                                 | V <sub>BB</sub> falling                        | 3.35     | 3.55 | 3.7  | V                   |

| VBB Undervoltage Hysteresis                                 | V <sub>BBHys</sub>                    | 1-143                                          | -        | 300  | _    | mV                  |

| VREF Undervoltage Threshold                                 | V                                     | V <sub>REF</sub> rising                        | 3.5      | -    | 4.0  | V                   |

| VICE Ondervoltage Threshold                                 | V <sub>REFUV</sub>                    | V <sub>REF</sub> falling                       | 3.25     | 3.45 | 3.6  | V                   |

| VREF Undervoltage Hysteresis                                | V <sub>REFHys</sub>                   |                                                | _        | 300  | -    | mV                  |

| Short Circuit Current Protection<br>Thresholds <sup>4</sup> | -V <sub>DS</sub>                      |                                                | 1.6      | -    | 5.5  | V                   |

| Overtemperature Shut Down                                   | T <sub>JF</sub>                       | Temperature increasing                         | 155      | 170  | -    | °C                  |

| Overtemperature Hysteresis                                  | T <sub>Jhys</sub>                     | Recovery = T <sub>JF</sub> – T <sub>Jhys</sub> | _        | 15   | -    | °C                  |

<sup>1</sup>The term "functional" indicates correct operation but parameters may not be within specification above or below the general limits

$(6.5 \text{ V} < \text{V}_{BB} < 28 \text{ V})$ , and outputs are not operational above  $\text{V}_{\text{BBOV}}$  or below  $\text{V}_{\text{BBUV}}$ . <sup>2</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

<sup>3</sup>Parameter t<sub>COMM</sub> = 1/ (6 × FG pin frequency) under steady motor speed conditions. <sup>4</sup>Parameter V<sub>DS</sub> = V<sub>OUTx</sub> to GND or V<sub>BB</sub> - V<sub>OUTx</sub>.

## A4946

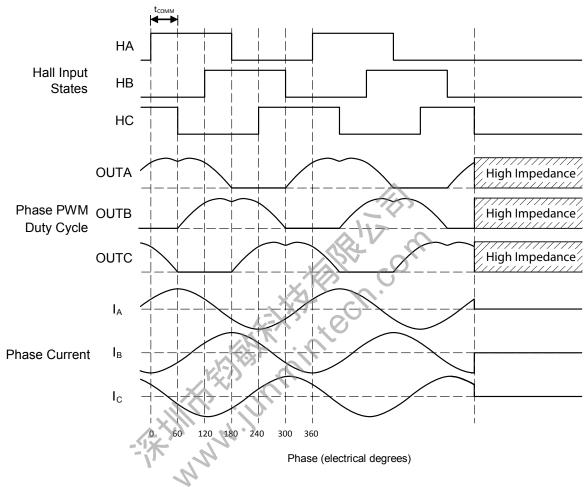

Figure 1. Commutation sequence timing

#### **Table 1. Commutation State Table**

| Commutation Input State* |    |    | Output Mode      |      |      |                 |          |          |  |

|--------------------------|----|----|------------------|------|------|-----------------|----------|----------|--|

| Commutation input State  |    |    | Trapezoidal Mode |      |      | Sinusoidal Mode |          |          |  |

| HA                       | HB | HC | OUTA             | OUTB | OUTC | OUTA            | OUTB     | OUTC     |  |

| Н                        | L  | Н  | High             | Low  | Z    | Sine PWM        | Low      | Sine PWM |  |

| н                        | L  | L  | High             | Z    | Low  | Sine PWM        | Sine PWM | Low      |  |

| н                        | Н  | L  | Z                | High | Low  | Sine PWM        | Sine PWM | Low      |  |

| L                        | Н  | L  | Low              | High | Z    | Low             | Sine PWM | Sine PWM |  |

| L                        | Н  | Н  | Low              | Z    | High | Low             | Sine PWM | Sine PWM |  |

| L                        | L  | Н  | Z                | Low  | High | Sine PWM        | Low      | Sine PWM |  |

| н                        | Н  | Н  | Z                | Z    | Z    | Z               | Z        | Z        |  |

| L                        | L  | L  | Z                | Z    | Z    | Z               | Z        | Z        |  |

| Н                                                                                                                 | Н             | Н      | Z                     | Z  | Z                      | Z    | Z                      | Z      |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|---------------|--------|-----------------------|----|------------------------|------|------------------------|--------|--|--|--|

| L                                                                                                                 | L             | L      | Z                     | Z  | Z                      | Z    | Z                      | Z      |  |  |  |

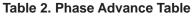

| Note: $Z = high impedance$<br>* $H = V_{HxP} > V_{HxM}$ , $L = V_{HxM} > V_{HxP}$<br>Table 2. Phase Advance Table |               |        |                       |    |                        |      |                        |        |  |  |  |

|                                                                                                                   |               |        | <u> </u>              |    | PHA Input Sta          | ite  |                        |        |  |  |  |

|                                                                                                                   | Dutput<br>Hz) | (Elect | Low<br>rical degrees) | (E | High<br>lectrical degr | ees) | Open<br>(Electrical de | grees) |  |  |  |

|                                                                                                                   | 0             |        | 0                     | 2, | 0                      |      | 5.6                    |        |  |  |  |

|                                                                                                                   | 80            |        | 0                     | 2  | 3.8                    |      | 5.6                    |        |  |  |  |

| 1                                                                                                                 | 00            |        | 0                     |    | 7.5                    |      | 5.6                    |        |  |  |  |

| 1                                                                                                                 | 20            |        | 0                     |    | 9.4                    |      | 5.6                    |        |  |  |  |

| 1                                                                                                                 | 40            |        | 0                     |    | 11.3                   |      | 5.6                    |        |  |  |  |

| 1                                                                                                                 | 60            |        | 0                     |    | 13.1                   |      | 5.6                    |        |  |  |  |

| 1                                                                                                                 | 80            |        | 0                     |    | 13.1                   |      | 5.6                    |        |  |  |  |

| 2                                                                                                                 | 50            |        | 0                     |    | 13.1                   |      | 5.6                    |        |  |  |  |

| 3                                                                                                                 | 00            |        | 0                     |    | 13.1                   |      | 5.6                    |        |  |  |  |

| >3                                                                                                                | 00            |        | 0                     |    | 13.1                   |      | 5.6                    |        |  |  |  |

## **Functional Description**

The A4946 is a three phase motor driver with integrated power bridge suitable for driving small fans and blowers in automotive applications. Typically average continuous motor phase current up to 1.25 A is possible in ambient temperatures up to 80°C, depending on the thermal resistance of the assembly. Peak phase current up to 1.63 A (typ) is controlled by fixed off-time PWM current limiting.

Motor audible noise and vibration is reduced by driving the phases with three 120 degree spaced sinusoidal currents. The motor current is determined by variable duty cycle PWM switching of the three motor phase connections. The PWM duty cycle is generated automatically, depending on the rotor position and the demanded speed.

Rotor position is determined by Hall effect elements. These provide direct inputs to the integrated commutation and excitation logic.

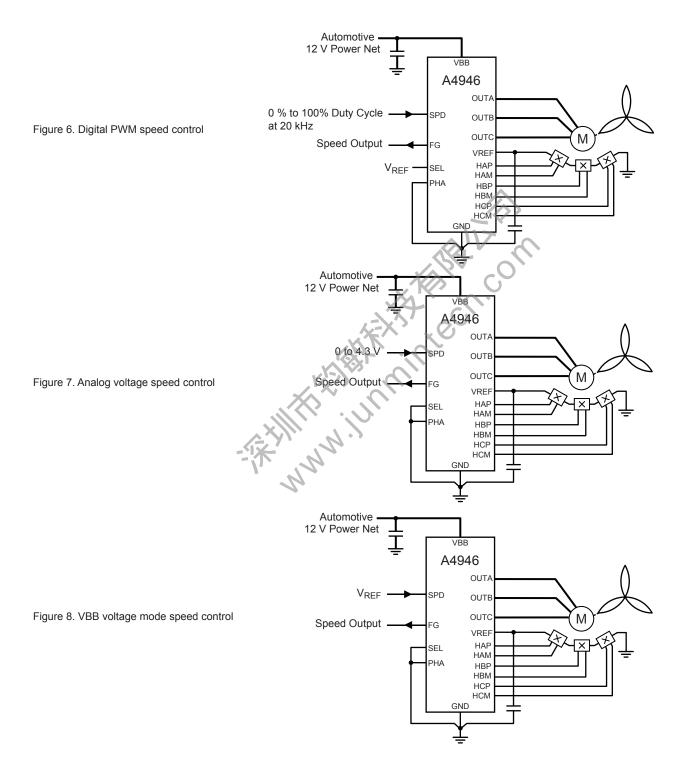

In addition to speed control by varying the supply voltage, motor speed can be controlled using digital PWM or analog voltage inputs, allowing system cost savings by eliminating an external variable power supply. Motor speed is indicated each full electrical commutation cycle by a single digital output

The A4946 incorporates motor lock detection, current limiting, supply overvoltage and undervoltage detection, overcurrent protection, and overtemperature protection.

## **Pin Functions**

**VBB** Main motor supply and chip supply for internal regulators and charge pump. VBB should be decoupled to ground with a low ESR electrolytic capacitor greater than 10  $\mu$ F, and a 100 nF (50 V) X7R ceramic capacitor in parallel.

**VREF** Regulated 5 V output for Hall element supply up to 30 mA. Also used for internal logic and analog supply. Should be decoupled to ground with a 220 nF (10 V minimum) X7R ceramic capacitor.

GND Supply return and analog reference ground.

**HAP, HAM** Hall element A inputs. Hall input A (HA) is defined as high when the voltage at HAP is greater than the voltage at HAM. Low is when HAM voltage is greater than HAP. **HBP, HBM** Hall element B inputs. Hall input B (HB) is defined as high when the voltage at HBP is greater than the voltage at HBM. Low is when HBM voltage is greater than HBP.

*HCP, HCM* Hall element C inputs. Hall input C (HC) is defined as high when the voltage at HCP is greater than the voltage at HCM. Low is when HCM voltage is greater than HCP.

OUTA, OUTB, OUTC Motor phase connections.

**FG** Speed output indicator provides a logical output equivalent of the Hall A (HA) status, one period per electrical revolution of the motor.

**SEL** Selects analog (voltage) or digital (PWM duty cycle) input for the SPD pin.

**SPD** Speed demand input. Analog voltage input or digital PWM duty cycle input selected by the SEL input.

**PHA** Phase advance logical input. When high, or open, phase advance is enabled. When low, phase advance is disabled.

## Operation

The three sinusoidal phase currents in the motor phase windings are generated, using variable duty cycle PWM, by a three-phase MOSFET power bridge. A three phase sine drive PWM generator provides the controlling inputs to the power bridge based on rotor position derived from Hall element inputs and a speed demand input. The PWM duty cycle modulation relative to the Hall signals is shown in figure 1.

The first three waveforms, HA, HB, and HC, in figure 1 show the Hall sequence derived from 120° (electrical) spaced Hall elements. The A4946 incorporates sensitive comparators with a large common mode capability, allowing the Hall elements to be connected in series or in parallel. The Hall inputs provide the commutation points to the sine drive generator. This produces the continuously varying duty cycle for each phase, based on the timing between the commutation points as shown in waveforms OUTA, OUTB, and OUTC in figure 1. Note that figure 1 shows the internal duty cycle value applied to the PWM generator in each phase, not the voltage waveform at the phase output.

The three sine wave phase currents,  $I_A$ ,  $I_B$ , and  $I_C$ , resulting from the three phase PWM outputs are shown in the bottom three waveforms in figure 1.

### **Speed Control**

The speed demand input modulates the range of the three PWM duty cycles to directly control the effective average voltage applied to the motor windings and therefore the current in the motor windings. The speed demand applied to the internal PWM generator is a digital value derived from the speed demand input pin, SPD. This input can be a variable duty cycle PWM signal with a frequency of typically 20 kHz, or a linear voltage input depending on the state of the SEL input.

When SEL is low, a voltage can be applied to the SPD input. This voltage is converted to a digital value by an internal 9-bit A-to-D converter, and then is used as the internal speed demand value. The input voltage range is from 0 V to typically 4.25 V. However when the input is less than 0.5 V, the motor speed demand will be zero. Between 1 and 4.3 V, the motor speed demand increases linearly from 25% to 100%. The relationship between the voltage on SPD,  $V_{SPD}$ , and the motor speed demand is shown in figure 2. The 0.5 V of hysteresis related to the start and stop response of the motor can also be seen in figure 2.

When SEL is high, a variable duty cycle digital signal can be applied to the SPD input. This signal should be at a frequency of

100 Votor Speed Demand (%) 75 50 25 0 (Disabled 75 100 25 50 12.5 0 PWM, D<sub>SPD</sub> (%) 4.3 0 0.5 2.1 3.2 1 Analog, V<sub>SPD</sub> (V) **Control Input**

Figure 2. Control input mapping to speed demand

typically 20 kHz. The signal timing is used to convert the input duty cycle to a 9-bit digital value, which is used as the motor speed demand value. The input duty cycle range is 0% to 100%. However, when the input duty cycle is less than 12.5%, the motor speed demand will be zero. Between 25% and 100% the motor speed demand increases linearly from 25% to 100%.

The relationship between the duty cycle of the PWM signal on the SPD pin, DCSPD, and the motor speed demand is shown in figure 2. The 12.5% of hysteresis related to the start and stop response of the motor is also be shown in figure 2.

#### **Operation During Start**

Note: Parameters used in the following descriptions are listed in the Motor Control section of the Electrical Characteristics table.

As the motor turns, it produces commutation codes that generate a speed related signal,  $t_{COMM}$ , which is used by the internal controller of the A4946 to detect two conditions:

#### Locked rotor

• The transition from trapezoidal drive mode to sinusoidal drive mode

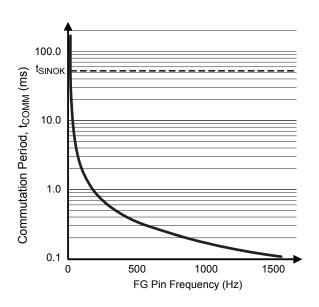

The relationship between  $t_{COMM}$  and the rotational speed of a motor measured at the FG pin is shown in figure 3. The curve is based on electrical cycles of the motor commutation system and

Figure 3. Relationship between  $t_{\mbox{COMM}}$  and FG frequency

this relationship will remain constant irrespective of the number of pole pairs the motor has. The number of poles will modify the relationship between the frequency measured on the FG pin and the actual mechanical rotational speed, in rpm, of the motor.

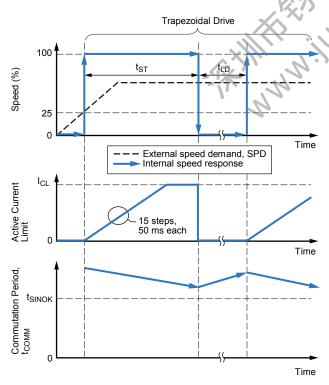

Figure 4 illustrates the conditions during a full start time period,  $t_{ST}$ , if the motor rotor is locked while driving a very high friction or inertia mechanical load. All these conditions will prevent the value of  $t_{COMM}$  reducing to a value less than the  $t_{SINOK}$  period before  $t_{ST}$  times out. After  $t_{ST}$  has timed out, the drive to the motor will be turned off for approximately 8 s, the  $t_{LD}$  period.

It can be seen in figure 4 that a start condition is commanded immediately when the control setting on the SPD pin exceeds the 25% level. If the initial condition on the SPD pin is less than 25% there will be a time delay, based on initial conditions, before a start is commanded (discussed in the Soft Start section).

During the start condition, trapezoidal drive mode is selected, also speed demand and motor current are controlled internally by the A4946. To aid starting the motor, current is incremented in steps every 50 ms in an attempt to increase the torque in the motor and increase rotational speed, thereby reducing the value of  $t_{\mbox{COMM}}.$

#### **Transition to Sinusoidal Operating Mode**

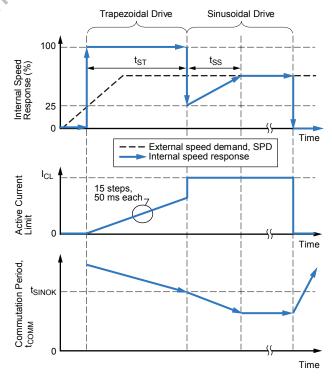

Figure 5 shows a successful transition to sinusoidal mode. Here the starting condition is the same as in figure 4, but now the motor reaches a higher speed during the  $t_{ST}$  period and the value of  $t_{COMM}$  reduces to values less than the  $t_{SINOK}$  threshold . This results in sinusoidal drive mode being selected at the next commutation point.

After sinusoidal drive mode is commanded, the internal current limit is raised to  $I_{CL}$  and the internal speed demand is lowered to 25%. Then controlled by the soft start feature in the A4946, the speed demand will increase during the period  $t_{SS}$ , to the external speed demand setting set on the SPD pin.

## Soft Start

A soft start function is integrated into the 4946. This is achieved by limiting the internal speed response slew rate to a maximum value,  $t_{RR}$ , to slow the rate of change of PWM duty cycle delivered to the motor phases.

Figure 4. Locked rotor case; no transition to sinusoidal mode

Figure 5. Successful start and transition to sinusoidal mode

This results in limiting the acceleration or deceleration of the motor between two speed demand levels input on the SPD pin. The end effect is to lower the average current demand from the power supply.

The speed change time, t<sub>SS</sub>, is defined by:

$$|t_{SS}| = (SPD1 - SPD2) \times t_{RR},$$

where SPDn is the setting on the SPD pin, in % of full scale. This is the time it takes the internally generated PWM duty cycle to change between demand settings, SPD1 and SPD2, input on the SPD pin.

Applying the above equation, the maximum value of  $t_{SS}$  in sinusoidal mode would be when SPD1 = 12.5% and SPD2 = 100%:

$$t_{SS} = 87.5 \ (\%) \times 15.33 \ (ms) = 1.345 \ s$$

,

and the maximum time to a motor start command would be when SPD1 = 0% and SPD2 = 25%:

$$t_{SS} = 25 ~(\%) \times 15.33 ~(ms) = 383 ~ms$$

.

The exception is when the signal on SPD is rapidly reduced to zero. This will cause all three drivers to enter the high impedance condition shown in table 1 immediately. This action is not modified by the state on the SEL pin. The end result is all three half bridges turn off and the motor will coast to a halt.

#### Lock Detect

Rotor lock is a functional state where the motor is turning too slowly to change from trapezoidal to sinusoidal mode. It can occur during two conditions. The first is during initial motor start up and the second is when the motor is running in sinusoidal mode and is forced to slow down by an external force.

Motor speed is continuously sensed by measuring the time between consecutive motor commutation points, and the value is stored as the parameter  $t_{COMM}$ . The relationship between  $t_{COMM}$  and the frequency available in the FG pin is shown in figure 3.

At the end of the start-up time,  $t_{ST}$ , if the value of  $t_{COMM}$  is greater than the drive mode selection parameter,  $t_{SINOK}$ , all phases will be disabled for a disable period,  $t_{LD}$ . An attempt to restart the motor is made when  $t_{LD}$  times out. The typical values of  $t_{ST}$  and  $t_{LD}$  are 1 s and 8 s respectively. Restart attempts based on these times will continue while the speed demand setting on the SPD pin is greater than 12.5%. If the motor is running in sinusoidal mode when an external force causes it to slow down to a speed where  $t_{COMM}$  is greater than  $t_{SI-NOK}$ , the A4946 will initiate a full start up sequence as shown in figure 4. If the force slowing the motor is no longer present, the motor will successfully re-start and switch to sinuisoidal mode as shown in figure 5. If the force is still present, then the start sequence described in figure 4 will result.

## **Current Limit**

Load current on each active output is continuously monitored on the high-side sourcing MOSFET in each half bridge. If the current exceeds  $I_{CL}$ , the source driver is turned off for 24  $\mu$ s. During this fixed off time, the driver operates in slow decay, synchronous rectification, mode.

During start up in trapezoidal mode, the value of  $I_{CL}$  is ramped from zero to aid starting and protect the outputs when the motor is locked. In sinusoidal mode the value of  $I_{CL}$  is fixed. See figures 4 and 5 for more information.

## **Output Short Circuit Protection**

The output short circuit protection feature operates to protect the A4946 if the current through any OUTx pin causes the source to drain voltage,  $V_{DS}$ , across active MOSFETs to exceed safe values. This could be the result of a short to ground, STG, a short to battery, STB, or a shorted load, STL, condition being detected. If any of these conditions occur, the A4946 disables the drives to all three OUTx pins and coasts the motor.

To reset the driver and attempt to restart the motor, the speed demand setting on the SPD pin must be reduced to a value less than 12.5%, and then increased to greater than 25% to initiate an attempt to start the motor. If the STx condition is still present the coast condition will be commanded again.

#### Phase Advance

To improve motor efficiency, the A4946 includes a dynamic phase advance feature. The advance is based on electrical cycle degrees and is enabled by setting PHA input to high or to open (table 2).

As speed increases, the phase excitation sequence advances ahead of the commutation sequence (shown in figure 1) by the values at each speed threshold in table 2. Rapid switching between advance values due to speed jitter is prevented by a hysteresis of about 10 Hz. When PHA is low, no phase advance is introduced.

## Automotive Three Phase Sinusoidal Fan Driver

## **Application Information**

Package LP, 16-Pin TSSOP

WWW. WINNING

Copyright ©2013, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com