# 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### FEATURES AND BENEFITS

- Automotive ASIL B, AEC-Q100 qualified solution for infrared LED driver monitoring system (DMS)

- Ultra-low EMI architecture with integrated EMImitigation capacitors and spread spectrum operation to comply with automotive requirements

- Safety protection against out-of-range PWM on-time and duty cycle with PWM monitoring feature for eye-safe operation

- High integration architecture including high-side and low-side MOSFET switches and 5 V peripheral LDO to reduce solution size and cost

- Safety diagnostics for ASIL B compliance including:

- Low power shutdown (1 μA typical)

- High-side output current sense

- High-side MOSFET current limit protection

- Active-low fault flag output

- Undervoltage lockout (UVLO)

- Thermal shutdown protection

- Robust protection against:

- Adjacent pin-to-pin short

- Pin-to-ground short

- Component open/short faults

### APPLICATIONS:

- Driver monitoring systems

- Advanced driver assistance systems

- Instrument clusters

### DESCRIPTION

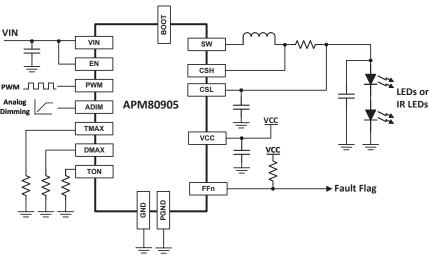

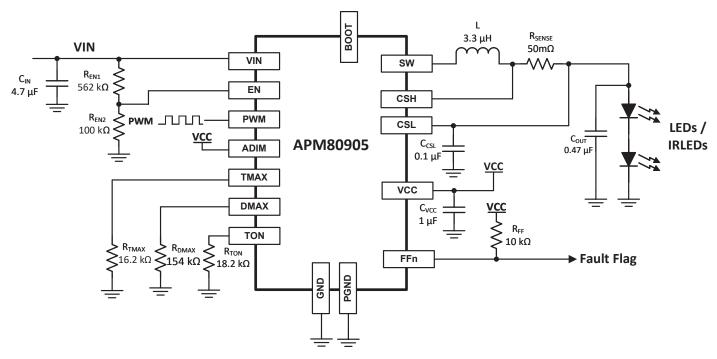

The APM80905 is a 36 V, 4 A, ASIL B, low-EMI, synchronous buck switching regulator module that provides a regulated current output to drive high-power infrared or standard LEDs. The module integrates both the high-side and low-side N-channel MOSFET switches, high-frequency input voltage and boot capacitors. The APM80905 also includes several fault protection features including a PWM dimming signal monitor with configurable LED on-time and duty cycle limits to simplify the design of driver monitoring systems.

The switching frequency is programmable from 400 kHz to 2.2 MHz with an external resistor. Output current is programmable by an external current sense resistor, and the output voltage is automatically adjusted to drive one or multiple LEDs in series, optimizing system efficiency regardless of the number of LEDs in the string. The analog dimming input, ADIM, allows for LED current calibration or thermal foldback with an external NTC thermistor. An open-drain fault flag pin FFn is pulled low to alert the system or controller that a fault was detected.

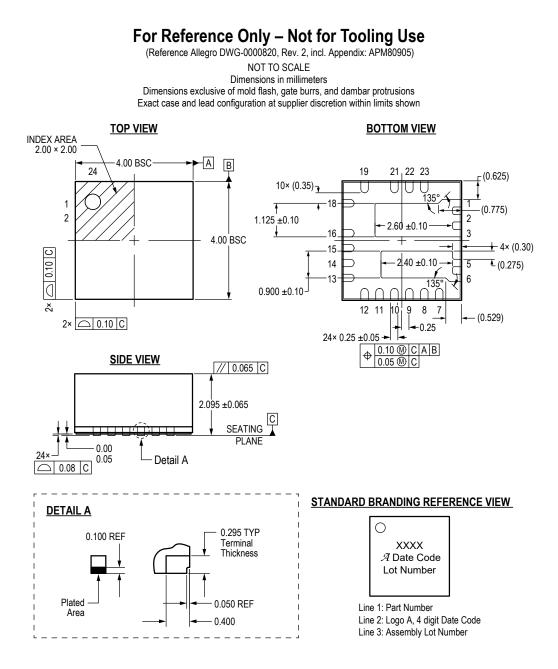

The APM80905 is offered in a compact, thermally enhanced  $4 \text{ mm} \times 4 \text{ mm} \times 2 \text{ mm}$  QFN package with wettable flank.

Not to scale

24-pin QFN 4 mm × 4 mm with wettable flank (suffix NB)

Figure 1: APM80905 Typical Application Circuit

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### **Table of Contents**

| Features and Benefits               |    |

|-------------------------------------|----|

| Description                         | 1  |

| Applications                        | 1  |

| Package                             | 1  |

| Typical Application Circuit         | 1  |

| Selection Guide                     |    |

| Absolute Maximum Ratings            |    |

| Thermal Characteristics             |    |

| Pinout Diagram and Terminal List    |    |

| Functional Block Diagram            |    |

| Electrical Characteristics          | 6  |

| EMI/EMC Performance Characteristics | 8  |

| Functional Description              | 9  |

| Overview                            | 9  |

| LED Current                         | 9  |

| Switching Frequency                 | 9  |

| Frequency Dithering                 | 9  |

| Enable                              | 10 |

| Internal VCC Regulator              | 10 |

| PWM Dimming                         | 10 |

| PWM Monitoring                      | 10 |

| On-Time Limit                       | 10 |

| Duty Cycle Limit                    | 11 |

| Normal Operation                    | 11 |

| lenis                                                  |      |

|--------------------------------------------------------|------|

| TMAX Fault                                             | 11   |

| DMAX Fault                                             | 11   |

| TMAX and DMAX Fault                                    | . 12 |

| Analog Dimming                                         | . 12 |

| Minimum and Maximum Output Voltages                    | . 13 |

| Boot Circuit                                           | . 13 |

| Thermal Budgeting                                      | . 14 |

| Protection Functions                                   |      |

| Built-In Self-Test                                     | . 14 |

| Fault Protection for Extreme Applications              | . 14 |

| LED Faults                                             |      |

| Open LED Fault                                         | . 15 |

| Open Short Fault                                       |      |

| Fault Detection Timers                                 | . 16 |

| Application Information                                | . 18 |

| Power Inductor Selection                               |      |

| Output Filter Capacitor                                | . 18 |

| Use of EN Pin for Input Undervoltage Protection        | . 18 |

| Application Circuit Diagram                            | . 20 |

| Design Procedure                                       |      |

| PCB Layout Guidelines                                  | . 23 |

| Package Outline Drawing and Recommended PCB Footprint. |      |

| Revision History                                       |      |

#### **SELECTION GUIDE**

| Part Number    | Dither  | Description                                        | Packing <sup>[1]</sup>          | Lead Finish |

|----------------|---------|----------------------------------------------------|---------------------------------|-------------|

| APM80905KNBATR | Enabled | 24-pin wettable flank QFN package with thermal pad | 3000 pieces<br>per 13-inch reel | Matte Tin   |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS [1]

| Characteristic                      | Symbol                             | Notes              | Rating                           | Unit |

|-------------------------------------|------------------------------------|--------------------|----------------------------------|------|

| Supply Voltage                      | V <sub>IN</sub>                    |                    | –0.3 to 42                       | V    |

| Switch Pin Voltage                  | V                                  |                    | –0.3 to V <sub>IN</sub> + 0.3    | V    |

| Switch Pin Voltage                  | V <sub>SW</sub>                    | Transient < 100 ns | –1.5 to V <sub>IN</sub> + 0.3    | V    |

| EN, PWM Pin <sup>[2]</sup> Voltages | V <sub>EN</sub>                    |                    | -0.3 to V <sub>IN</sub> + 0.3    | V    |

| Current Sense Voltages              | V <sub>CSH,</sub> V <sub>CSL</sub> |                    | -0.3 to V <sub>IN</sub> + 0.3    | V    |

|                                     | N/                                 | Continuous         | $V_{SW}$ – 0.3 to $V_{SW}$ + 5.5 | V    |

| BOOT Pin Voltage                    | V <sub>BOOT</sub>                  | t < 1 ms           | $V_{SW}$ – 0.3 to $V_{SW}$ + 7   | V    |

| All other pins                      |                                    |                    | –0.3 to 7                        | V    |

| Operating Junction Temperature      | T <sub>J(max)</sub>                |                    | -40 to 150                       | °C   |

| Storage Temperature                 | T <sub>stg</sub>                   |                    | –55 to 150                       | °C   |

<sup>[1]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

[2] PWM pin is high-voltage-rated only for FMEA purpose. User is expected to use it as a logic-level pin only. If user wishes to use it at high voltage, then IC will not be pin-to-pin short protected for PWM pin and DMAX pin, user will have to compromise for DMAX pin protection if PWM pin is used for high voltage. It is recommended to use PWM pin as logic-level pin only.

#### **THERMAL CHARACTERISTICS**<sup>[1]</sup>

| Characteristic                         | Symbol                | Test Conditions                        | Value | Unit |

|----------------------------------------|-----------------------|----------------------------------------|-------|------|

| Junction-to-Ambient Thermal Resistance | $R_{	extsf{	heta}JA}$ | On 4-layer PCB based on JEDEC standard | 43    | °C/W |

<sup>[1]</sup>Additional thermal information available on the Allegro website.

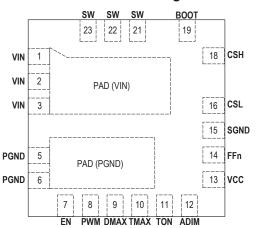

### PINOUT DIAGRAM AND TERMINAL LIST

#### **QFN-24 Pinout Diagram**

#### **Terminal List**

| Number     | Name        | Function                                                                                                                                                                    |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3    | VIN         | Power input for control circuits and power stage. Connect a ceramic capacitor between VIN and PGND close to this pin.                                                       |

| 5, 6       | PGND        | Power ground pins.                                                                                                                                                          |

| 7          | EN          | Enable pin. Pull this pin high to enable the APM80905.                                                                                                                      |

| 8          | PWM         | Logic input for PWM dimming. The LEDs are on while this pin is high, EN is high, and no faults are detected.                                                                |

| 9          | DMAX        | Programming pin for maximum safe output current duty cycle. Connect a resistor between DMAX and GND to set the maximum LED current duty cycle.                              |

| 10         | TMAX        | Programming pin for maximum safe output current on-time. Connect a resistor between TMAX and GNE to set the maximum LED current on-time.                                    |

| 11         | TON         | Programming pin for DC/DC converter high-side power switch on-time. Connect a resistor between TON and GND to set the high-side power switch on-time of the buck converter. |

| 12         | ADIM        | Analog dimming control voltage input.                                                                                                                                       |

| 13         | VCC         | Internal bias regulator output. Connect a 1 $\mu F$ to 4.7 $\mu F$ ceramic capacitor from VCC to PGND close to this pin.                                                    |

| 14         | FFn         | Open-drain, active-low fault signal. Pulled low when a fault is detected. Connect a pull-up resistor to desired logic level.                                                |

| 15         | SGND        | Signal ground pin.                                                                                                                                                          |

| 16         | CSL         | LED current sense low pin. A resistor placed between CSH and CSL sets the current in the LED string. Place a 0.1 $\mu$ F ceramic capacitor very close to the CSL pin.       |

| 18         | CSH         | LED current sense high pin. A resistor placed between CSH and CSL sets the current in the LED string.                                                                       |

| 19         | BOOT        | High-side gate driver bootstrap pin. The boot circuit capacitor is inside the package. This pin is provided for testing purposes and should be left floating.               |

| 21, 22, 23 | SW          | Buck converter power switch output pins. Connect these pins to the power inductor.                                                                                          |

| PAD1       | Exposed Pad | PAD1 is an exposed pad and should be soldered to VIN.                                                                                                                       |

| PAD2       | Exposed Pad | PAD2 is an exposed pad and should be soldered to the PGND plane for enhanced thermal performance                                                                            |

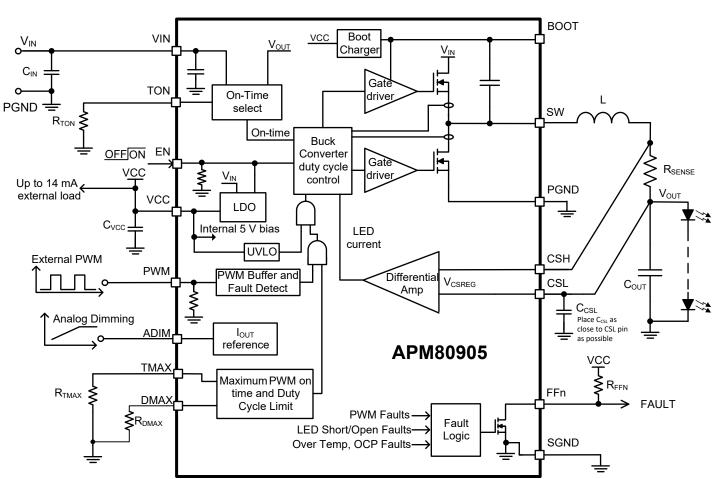

FUNCTIONAL BLOCK DIAGRAM

Figure 2: Functional Block Diagram

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### ELECTRICAL CHARACTERISTICS: Valid at V<sub>IN</sub> $\leq$ 12 V, V<sub>OUT</sub> = 6 V, typical values at T<sub>J</sub> = 25°C, unless otherwise noted

| Characteristics                                             | Symbol                    | Test Conditions                                                                             | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

| INPUT SUPPLY                                                |                           | ·                                                                                           |      | ·    |      |      |

| Input Voltage Range                                         | V <sub>IN</sub>           | V <sub>IN</sub> must first rise above V <sub>UVLO(ON,MAX)</sub>                             | 4.5  | _    | 36   | V    |

| Input Supply Undervoltage Lockout<br>Startup Threshold      | V <sub>UVLO(ON)</sub>     | V <sub>IN</sub> rising                                                                      | -    | _    | 4.31 | V    |

| Input Supply Undervoltage Lockout<br>Hysteresis             | V <sub>UVLO(HYS)</sub>    |                                                                                             | -    | 165  | _    | mV   |

| Input Supply Current <sup>[1]</sup>                         | I <sub>IN</sub>           | $V_{EN} = V_{EN(HI)}, V_{PWM} = V_{IL(PWM)}$                                                | _    | 5    | _    | mA   |

| Input Shutdown Current <sup>[1]</sup>                       | I <sub>IN(SD)</sub>       | V <sub>EN</sub> = 0 V                                                                       | _    | 1    | 10   | μA   |

| POWER SWITCHES                                              | · · ·                     |                                                                                             |      | •    |      |      |

| Buck Switch Current Limit Threshold                         | I <sub>SW(LIM)</sub>      |                                                                                             | 6    | 6.4  | 7    | A    |

| Buck High-Side Switch On-Resistance                         | R <sub>DSON(HS)</sub>     | V <sub>BOOT</sub> = V <sub>IN</sub> + 4.3 V, T <sub>J</sub> = 25°C, I <sub>SW</sub> = 0.5 A | _    | 90   | _    | mΩ   |

| Buck Low-Side Switch On-Resistance                          | R <sub>DSON(LS)</sub>     | V <sub>BOOT</sub> = 4.3 V, T <sub>J</sub> = 25°C, I <sub>SW</sub> = 0.5 A                   | _    | 60   | _    | mΩ   |

| Selected On-Time                                            | t <sub>ON</sub>           | $V_{IN}$ = 12 V, $V_{CSL}$ = 6 V , $R_{TON}$ = 100 k $\Omega$                               | 1.37 | 1.50 | 1.62 | μs   |

| Switching Minimum On-Time                                   | t <sub>ON(MIN)</sub>      |                                                                                             | _    | 108  | 130  | ns   |

| Switching Minimum Off-Time                                  | t <sub>OFF(MIN)</sub>     | $V_{CSH} - V_{CSL} = 0 V$                                                                   | _    | 70   | 90   | ns   |

| On-Time Spread Spectrum Range                               | t <sub>ON(SWEEP)</sub>    |                                                                                             | _    | ±5   | _    | %    |

| On-Time Spread Spectrum Modulation<br>Frequency             | f <sub>SW(MOD)</sub>      |                                                                                             | _    | 10   | _    | kHz  |

| REGULATION COMPARATOR AND                                   | ERROR AMP                 | LIFIER                                                                                      |      |      |      | ·    |

| Output Current Sense Common Mode<br>Voltage [4]             | V <sub>OUT</sub>          | $\rm V_{IN}$ = 36 V, $\rm f_{SW}$ = 500 kHz, $\rm I_{LED}$ = 0.5 A, measured at CSL pin     | 2.65 | -    | 32   | V    |

| Differential Output Current Sense<br>Voltage <sup>[3]</sup> | V <sub>CSREG</sub>        | V <sub>CSH</sub> – V <sub>CSL</sub> Average, ADIM tied to VCC<br>(no analog dimming)        | 189  | 195  | 201  | mV   |

| CSH Input Sense Current <sup>[1]</sup>                      | I <sub>CSH</sub>          | V <sub>CSH</sub> - V <sub>CSL</sub> = 0.195 V                                               | _    | 230  | _    | μA   |

| CSL Input Sense Current <sup>[1]</sup>                      | I <sub>CSL</sub>          | V <sub>CSH</sub> - V <sub>CSL</sub> = 0.195 V                                               | _    | 165  | _    | μA   |

| ANALOG DIMMING INPUT                                        |                           |                                                                                             |      |      |      |      |

| ADIM Voltage for 100% LED Current                           | VADIM(H)                  | $V_{CSH} - V_{CSL} = V_{CSREG}$                                                             | 1.75 | -    | _    | V    |

| Regulation Threshold at 50% Analog<br>Dimming               | V <sub>CSREG(50)</sub>    | V <sub>ADIM</sub> = 0.925 V                                                                 | 97   | 100  | 103  | mV   |

| Regulation Threshold at 20% Analog<br>Dimming               | V <sub>CSREG(20)</sub>    | V <sub>ADIM</sub> = 0.620 V                                                                 | -    | 40   | _    | mV   |

| INTERNAL LINEAR REGULATOR                                   |                           | · · · ·                                                                                     |      |      |      |      |

| VCC Pin Output Voltage                                      | V <sub>CC</sub>           | 0 mA < I <sub>VCC</sub> < 14 mA, V <sub>IN</sub> > 6 V                                      | 4.85 | 5.0  | 5.15 | V    |

| VCC Dropout Voltage                                         | V <sub>CC(DROP)</sub>     | Measure $V_{IN} - V_{CC}$ : $V_{IN}$ = 4.8 V, $I_{VCC}$ = 14 mA                             | _    | 0.35 | 0.75 | V    |

| VCC External Load                                           | I <sub>VCC(EXT)</sub>     | V <sub>IN</sub> > 6 V                                                                       | _    | -    | 14   | mA   |

| VCC Undervoltage Lockout Rising                             | V <sub>CC(UVLO)</sub>     |                                                                                             | 3.60 | 3.9  | 4.15 | V    |

| VCC Undervoltage Lockout Hysteresis                         | V <sub>CC(UVLO,HYS)</sub> |                                                                                             | 180  | 230  | 280  | mV   |

Continued on the next page ...

# ELECTRICAL CHARACTERISTICS (continued): Valid at $V_{IN} \le 12$ V, $V_{OUT} = 6$ V, typical values at $T_J = 25^{\circ}$ C, unless otherwise noted

| PWM INPUT                                                       |                           |                                                                            |       |       |       |    |

|-----------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|-------|-------|-------|----|

| PWM High Voltage                                                | V <sub>IH(PWM)</sub>      | V <sub>PWM</sub> increasing                                                | _     | _     | 1.2   | V  |

| PWM Low Voltage                                                 | V <sub>IL(PWM)</sub>      | V <sub>PWM</sub> decreasing                                                | 0.6   | _     | _     | V  |

| PWM Pin Pulldown Resistance                                     | R <sub>PWM(PD)</sub>      | V <sub>CC</sub> = 5 V, V <sub>PWM</sub> = 3 V                              | _     | 100   | _     | kΩ |

| ENABLE INPUT                                                    |                           | ·                                                                          |       |       |       |    |

| EN High Voltage                                                 | V <sub>EN(HI)</sub>       | V <sub>EN</sub> rising                                                     | 1.14  | 1.2   | 1.26  | V  |

| EN Input Hysteresis                                             | V <sub>EN(HYS)</sub>      | EN/UVHI EN/UVLO                                                            | 38    | 104   | 170   | mV |

| EN Pin Sink Current <sup>[1]</sup>                              | I <sub>EN</sub>           | V <sub>EN</sub> = 1.2 V                                                    | _     | 1     | 5     | μA |

| EN Pin Pulldown Resistance <sup>[2]</sup>                       | R <sub>EN(PD)</sub>       | V <sub>IN</sub> > 3 V                                                      | _     | 2     | _     | MΩ |

| FAULT                                                           |                           | ·                                                                          |       |       |       |    |

| Minimum V <sub>ADIM</sub> for LED Open/Short<br>Fault Detection |                           | V <sub>ADIM</sub> rising                                                   | 475   | 500   | 525   | mV |

| V <sub>OUT</sub> Low Threshold for LED Short<br>Fault Detection |                           | V <sub>OUT</sub> falling                                                   | 1.5   | 1.7   | 1.9   | V  |

| Sense Voltage Threshold for LED<br>Open Fault                   | V <sub>CS(OPEN)</sub>     | $V_{CSREG}$ = 200 mV start falling (PWM duty = max), $V_{ADIM}$ = $V_{CC}$ | 35    | 65    | 95    | mV |

| Sense Voltage Hysteresis for LED<br>Open Fault <sup>[2]</sup>   | V <sub>CS(OPEN,HYS)</sub> | $V_{CSREG}$ = 200 mV start falling (PWM duty = max), $V_{ADIM}$ = $V_{CC}$ | _     | 20    | _     | mV |

| Fault Deglitch Timer                                            | t <sub>FDG</sub>          |                                                                            | 45    | 60    | 75    | μs |

| Fault Mask Timer                                                | t <sub>MASK</sub>         |                                                                            | 90    | 120   | 150   | μs |

| FFn Pull-Down Voltage                                           | V <sub>FAULT(PD)</sub>    | Fault condition asserted, pull-up current = 1 mA                           | _     | -     | 0.4   | V  |

| FFn Pin Leakage Current <sup>[1]</sup>                          | I <sub>FAULT(LKG)</sub>   | Fault condition cleared, pull-up to 5 V                                    | _     | -     | 1     | μA |

| FFn Rising Delay Timer <sup>[2]</sup>                           | t <sub>RISE</sub>         | Low to High transition time for FFn pin                                    |       |       | 10    | μs |

| FFn Falling Delay Timer <sup>[2]</sup>                          | t <sub>FALL</sub>         | High to Low transition time for FFn pin                                    |       |       | 10    | μs |

| Cool Down Timer for Fault Retry                                 | t <sub>RETRY</sub>        |                                                                            | _     | 1     | _     | ms |

| THERMAL SHUTDOWN                                                |                           |                                                                            |       |       |       |    |

| Thermal Shutdown Threshold <sup>[2]</sup>                       | T <sub>SD</sub>           |                                                                            | 150   | 165   | 180   | °C |

| Thermal Shutdown Hysteresis [2]                                 | T <sub>SDHYS</sub>        |                                                                            | _     | 25    | -     | °C |

| PWM MONITORING                                                  |                           |                                                                            |       |       |       |    |

| Minimum PWM On-Time Safety Limit Setting                        | t <sub>PWMON(MIN)</sub>   | R <sub>TMAX</sub> = 6.65 kΩ                                                | 0.218 | 0.250 | 0.282 | ms |

| Maximum PWM On-Time Safety Limit Setting                        | t <sub>PWMON(MAX)</sub>   | R <sub>TMAX</sub> = 191 kΩ                                                 | 4.37  | 5.00  | 5.63  | ms |

| Minimum PWM Off-Time Safety Limit Setting                       | t <sub>BLANK(MIN)</sub>   | R <sub>DMAX</sub> = 5.36 kΩ                                                | 0.71  | 0.82  | 0.93  | ms |

| Maximum PWM Off-Time Safety Limit Setting                       | t <sub>BLANK(MAX)</sub>   | R <sub>DMAX</sub> = 178 kΩ                                                 | 16.6  | 19    | 21.4  | ms |

<sup>[1]</sup> Negative current is defined as coming out of (sourcing) the specified device pin or node.

<sup>[2]</sup> Determined by design and characterization. Not production tested.

<sup>[3]</sup> In test mode, a ramp signal is applied between CSH and CSL pins to determine the  $V_{CSH} - V_{CSL}$  regulation threshold voltage. In actual application, the average  $V_{CSH} - V_{CSL}$  voltage is regulated at  $V_{CSREG}$  regardless of ripple voltage.

[4] Determined by design and characterization. Production tested from 2.65 to 30 V.

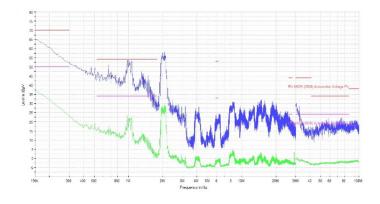

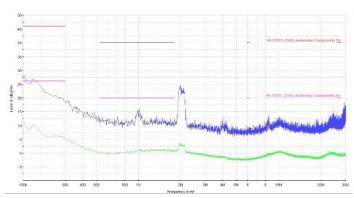

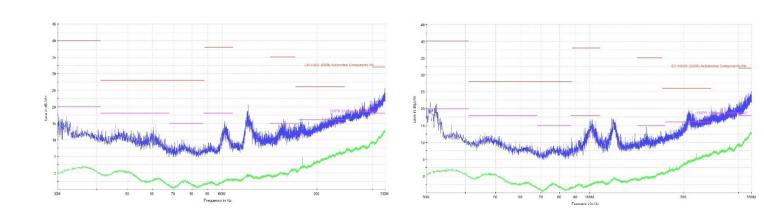

### **EMI/EMC PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 12 V,  $V_{OUT}$  = 5 V,  $f_{SW}$  = 2.15 MHz

Conducted Emissions (150 kHz to 30 MHz)

Radiated Emissions (150 kHz to 30 MHz) (Monopole)

Radiated Emissions (30 MHz to 330 MHz) (Vertical Biconical)

NOTE: Allegro is not an accredited EMC laboratory. The information presented here is for reference only. APM80905 is operating at a switching frequency of 2.2 MHz for all tests with combined nominal input capacitance of 47  $\mu$ F using ceramic surface mount capacitors.

### FUNCTIONAL DESCRIPTION

#### Overview

The APM80905 is a synchronous buck regulator module designed for driving a high-current LED or IR LED string. It employs average current-mode control to maintain constant LED current and consistent brightness.

### LED Current

The LED current level is easily programmable by selection of an external current sense resistor with a value determined by:

Equation 1:

$$_{\text{SENSE}} = \frac{V_{\text{CSREG}}}{I_{\text{LED}}}$$

where  $V_{CSREG} = V_{CSH} - V_{CSL} = 195 \text{ mV}$  typical.

R

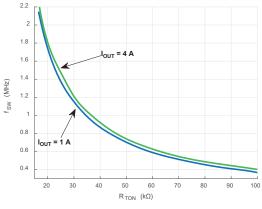

### **Switching Frequency**

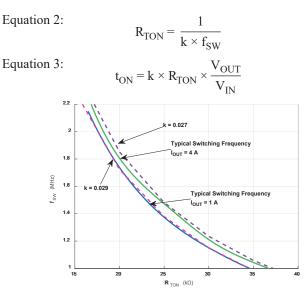

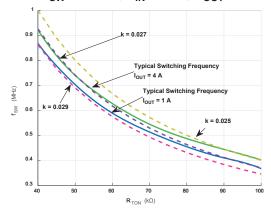

The APM80905 operates in fixed adaptive on-time mode. The ontime is programmed using an external resistor connected between the TON pin and ground. The switching frequency is dependent on several application specific factors including input voltage, output voltage, and output current. Figure 3 shows the relationship between R<sub>TON</sub> and switching frequency for a typical application with two different output currents. Since most applications are designed to target a switching frequency, such as above or below the AM radio band in automotive applications, Equation 2 can be used to approximate the value of the R<sub>TON</sub> resistor value for a given switching frequency. Use Figure 4 and Figure 5 to find the constant k for applications with a similar input to output voltage ratio. For other applications or for more help selecting R<sub>TON</sub>, consult the APM80905 Design Tool. If switching frequency is critical to the application, the APM80905 application should be validated across all system parameters as the switching frequency will vary with the system state due to the constant on-time control architecture.

Figure 3: Switching Frequency vs. R<sub>TON</sub>

Figure 4: Switching Frequency vs.  $R_{TON}$ for f<sub>SW</sub> > 1 MHz, V<sub>IN</sub> = 12 V, V<sub>OUT</sub> ≈ 6 V

Figure 5: Switching Frequency vs.  $R_{TON}$ for  $f_{SW}$  < 1 MHz,  $V_{IN}$  = 12 V,  $V_{OUT} \approx 6$  V

#### **Frequency Dithering**

The APM80905 uses spread spectrum clocking to minimize EMI at the fundamental switching frequency and its harmonics, generated by the switch node. The frequency dithering range is fixed at  $\pm$ 5% with a modulation frequency of 10 kHz. The switching frequency dither is a triangle wave, sweeping linearly between 0.95 × t<sub>ON</sub> and 1.05 × t<sub>ON</sub>, where t<sub>ON</sub> is the programmed on-time.

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### Enable

A voltage on EN above the nominal 1.2 V threshold enables the APM80905. The EN comparator has a typical hysteresis of 100 mV. Once enabled, if EN decreases below the 1.1 V (typ) disable threshold, then the APM80905 enters the shutdown state, stops switching, and draws only 1  $\mu$ A (typ) from V<sub>IN</sub>.

The EN pin is high-voltage tolerant and can be directly connected to VIN for always-on applications. However, if EN is higher than the VIN voltage at any time, a series  $10 \text{ k}\Omega$  resistor is required to limit the current flowing into the EN pin. The series EN pin resistor is not necessary if EN is driven from a logic input.

There is an internal 2 M $\Omega$  (typ) pulldown on the EN pin that is active once the voltage on the VIN pin is greater than approximately 3 V, preventing a leakage current path to GND through the APM80905 if the VIN supply is disabled but the EN pin is still driven high from a different supply.

### Internal VCC Regulator

The VCC regulator is used as the power supply for the internal control circuitry and can supply up to 14 mA to an external load. A 1  $\mu$ F to 4.7  $\mu$ F ceramic capacitor placed close to the VCC pin, with a low-impedance connection to VCC and GND, is recommended.

### **PWM Dimming**

The LED brightness is controlled by the pulse-width-modulated signal applied to the PWM pin. The APM80905 drives the LED current to the target level set by  $R_{\rm SENSE}$  when the PWM pin is high and drives the LED current off when the PWM pin is low.

The dimming ratio is the ratio of the on-time to the period of the PWM signal. For example, by selecting a PWM period of 5 ms (200 Hz) and a PWM on-time of 5  $\mu$ s, a dimming ratio of 0.1% can be achieved. This is sometimes referred to as 1000:1 dimming. In an actual application, the minimum dimming ratio is determined by various system parameters including: V<sub>IN</sub>, V<sub>OUT</sub>, inductance of the power inductor, LED current, switching frequency, and PWM frequency. The device is capable of PWM on-time as short as 5  $\mu$ s; however, if fault flag operation for open or short LED detection is required, the PWM on-time must be greater than the maximum fault mask timer, t<sub>MASK</sub>.

The PWM pin is a logic input pin and is internally pulled to GND through a 100 k $\Omega$  (typ) resistor. The EN and PWM pins function as illustrated in Table 1.

#### Table 1: EN and PWM Pin States

| EN Pin | PWM Pin  | FFn  | VCC | LEDs |

|--------|----------|------|-----|------|

| Low    | х        | Х    | OFF | OFF  |

| High   | Low/Open | Х    | ON  | OFF  |

| High   | High     | High | ON  | ON   |

| High   | High     | Low  | ON  | OFF  |

### **PWM Monitoring**

The APM80905 continuously monitors the on-time and duty cycle of the incoming PWM signal and drives the FFn pin low and disables the LED current if a fault is detected.

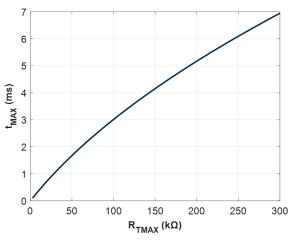

### On-Time Limit

The first PWM monitor is a maximum on-time limit. A TMAX fault is detected when the incoming PWM signal on-time exceeds the maximum on-time set by  $R_{TMAX}$ . A TMAX fault drives the FFn pin low and disables the LED current for the remainder of the PWM cycle. The TMAX fault is cleared on the next PWM rising edge. Use Equation 4 to calculate  $R_{TMAX}$  and refer to Figure 6.

Equation 4:

$$R_{TMAX} = 2.5413(t_{MAX})^2 + 25.527 t_{MAX}$$

where  $t_{\text{MAX}}$  is in milliseconds and  $R_{\text{TMAX}}$  is in k $\Omega.$

Figure 6: t<sub>MAX</sub> vs. R<sub>TMAX</sub>

# 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

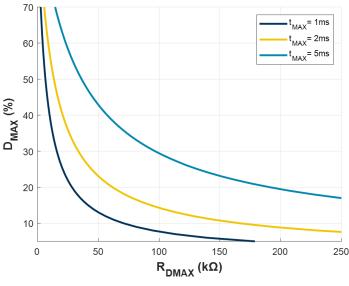

### **Duty Cycle Limit**

The second PWM monitor circuit is a maximum duty cycle limit set by a resistor from the DMAX pin to GND,  $R_{DMAX}$ . The DMAX fault monitors the incoming PWM signal off-time, and determines duty cycle with respect to the on-time limit TMAX set with  $R_{TMAX}$ . A DMAX fault is triggered at a PWM rising edge when the PWM off-time is less than the minimum blanking time,  $t_{BLANK}$ , set by  $R_{DMAX}$ . A DMAX fault disables the LED current for at least  $t_{BLANK}$  and can be cleared on the next PWM rising edge after waiting  $t_{BLANK}$ . Calculate  $R_{DMAX}$  by first calculating the off-time,  $t_{BLANK}$ , at  $t_{MAX}$  using Equation 5.

Equation 5:

$$t_{\rm BLANK} = t_{\rm MAX} \left( \frac{1}{D_{\rm MAX}} - 1 \right)$$

where  $D_{\mbox{MAX}}$  is the maximum duty cycle percentage normalized from 0-1.

Then solve for the resistor value of  $R_{DMAX}$  using the blanking time in Equation 6 and refer to Figure 7.

Equation 6:

$$\label{eq:RDMAX} \begin{split} R_{DMAX} = 0.1529 \times t_{BLANK}^{}^2 + 6.5112 \times t_{BLANK}^{} - 0.1486 \end{split}$$

where  $t_{BLANK}$  is in milliseconds and  $R_{DMAX}$  is in k $\Omega$ .

Figure 7: D<sub>MAX</sub> vs. R<sub>DMAX</sub>

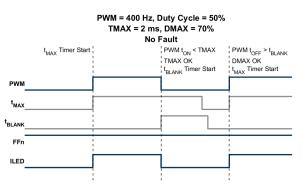

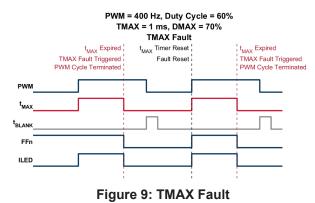

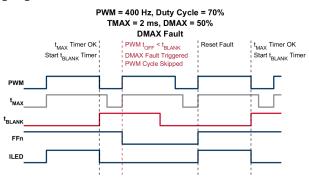

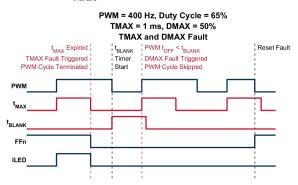

The TMAX and DMAX fault scenarios are presented in Figure 8 to Figure 11. A dark blue line represents a signal external to the APM80905, a gray line represents an internal signal not responsible for triggering a fault, and a red line represents an internal signal responsible for triggering a fault.

### **Normal Operation**

When the PWM signal on-time is less than the configured TMAX value and duty cycle is less than the configured DMAX value, there is no reported fault and the LED current follows the PWM signal and the FFn pin remains high, as shown in Figure 8. The PWM on-time is less than the  $t_{MAX}$  timer and the PWM off-time is greater than the  $t_{BLANK}$  timer.

Figure 8: No TMAX or DMAX Fault

### TMAX Fault

When the PWM signal on-time exceeds the configured TMAX value set by  $R_{TMAX}$ , the LED current is shut off and the FFn pin is pulled low. The fault is cleared on the next PWM rising edge. If the fault occurs again the same process repeats, as shown in Figure 9.

### DMAX Fault

A DMAX fault occurs when the duty cycle exceeds the configured duty cycle limit set by  $R_{DMAX}$ . In Figure 10, the PWM on-time is less than the maximum set by the internal  $t_{MAX}$  timer so there is no TMAX fault, but the PWM off-time is less than the minimum required off-time of  $t_{BLANK}$ , which triggers a DMAX fault. The DMAX fault drives the FFn pin low and prevents the

# 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

LED current from turning on for that PWM cycle. After waiting for at least the  $t_{BLANK}$  timer, the fault is reset on the next PWM rising edge.

### TMAX and DMAX Fault

Even if the LED cycle is terminated early due to a TMAX fault, the incoming PWM signal off-time must still be greater than  $t_{BLANK}$ . If a DMAX fault is triggered following a TMAX fault the LED current remains off and the PWM cycle is skipped similar to the DMAX fault in Figure 11. When a DMAX fault follows a TMAX fault, the faults are reset by the falling edge of the next PWM pulse after the  $t_{BLANK}$  timer expires and the PWM pulse does not exceed  $t_{MAX}$ .

Figure 11: TMAX and DMAX Fault

### **Analog Dimming**

The APM80905 includes an analog dimming feature that can be used for multiple applications including LED binning, extending the dimming ratio, or LED current foldback with increased LED temperature. Analog dimming adjusts the regulation voltage,  $V_{CS-REG}$ , maintained across  $R_{SENSE}$ . The voltage on the ADIM pin,  $V_{ADIM}$ , determines the level of dimming applied. If analog dimming is not used, ADIM should be tied to VCC. The APM80905 does not detect an ADIM shorted to VCC fault because it is a

valid operating state, where the LED current is not derated.

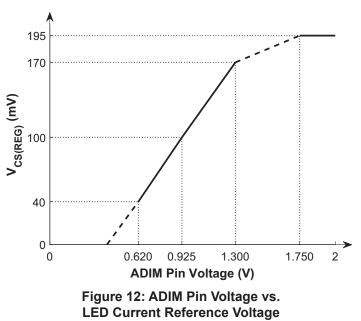

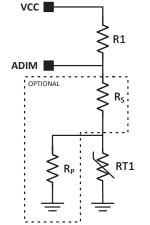

No dimming is applied when  $V_{ADIM}$  exceeds 1.75 V. When  $V_{ADIM}$  is between 0.62 and 1.3 V, the LED current varies linearly with  $V_{ADIM}$  from 20% to 90%. The LED current regulation voltage,  $V_{CSREG}$ , can be calculated by Equation 7 or the dimming ratio by Equation 8, and is shown in Figure 12.

Equation 7:

$$V_{\text{CSREG}} = (V_{\text{ADIM}} - 0.42) \times 0.195$$

Equation 8:

$$DimPct = (V_{CSREG} / V_{CSNOM}) \times 100\%$$

where DimPct is the analog dimming percentage and  $V_{CSNOM}$ , the  $V_{CSREG}$  value with no dimming, is 0.195 V.

The voltage across the sense resistor must always be greater than 0 V, including at the valley of the inductor current ripple.

Temperature-based LED current foldback can be implemented as a voltage divider with an NTC thermistor on the ADIM pin, as shown in Figure 13. The resistors  $R_S$  and  $R_P$  can be added or removed as needed to tune the NTC voltage divider response.

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

Figure 13: NTC thermistor circuit for temperaturebased output current foldback

### Minimum and Maximum Output Voltages

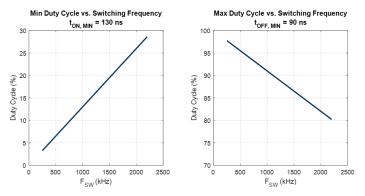

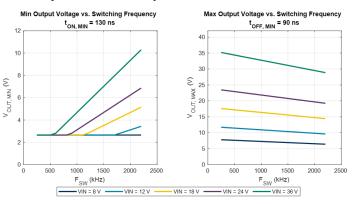

The maximum output voltage is limited by the input voltage and the duty cycle of the power stage at the minimum off-time,  $t_{OFF(MIN)}$ . At higher switching frequencies the minimum off-time becomes a larger percentage of the switching period, limiting the maximum duty cycle in the switching period. The same principal applies to the minimum output voltage at the minimum on-time,  $t_{ON(MIN)}$ . See Figure 14 for the minimum and maximum duty cycle for a given switching frequency. The output voltage range is a function of the input voltage and duty cycle range.

For example, with a minimum off-time of 90 ns at  $f_{SW} = 2$  MHz, the maximum duty cycle is 82%, and for an input voltage of 18 V the maximum output voltage is approximately 14.76 V (based on the simplified equation of  $V_{OUT} = V_{IN} \times D$ , where D is the switching converter duty cycle). The maximum output voltage is also slightly reduced by the power loss and thermal condition of the IC.

Similarly, at a minimum on-time of 130 ns and  $f_{SW} = 2$  MHz, the minimum duty cycle is 26%, so with an input voltage of 9 V the minimum V<sub>OUT</sub> is 2.34 V. However, the internal current sense amplifier is designed to operate accurately down to V<sub>OUT</sub> = 2.65 V. Therefore, the output voltage should not go below 2.65 V or the output current accuracy will be reduced.

Figure 15: Minimum and Maximum Output Voltage

If the required output voltage is lower than that permitted by the minimum on-time, the controller will automatically extend the off-time to maintain the correct duty cycle. The result is that the switching frequency will drop lower when necessary to keep the LED current in regulation.

If the LED string is completely shorted and  $V_{OUT} = 0$  V, the controller enters hiccup mode and switches at the minimum on-time.

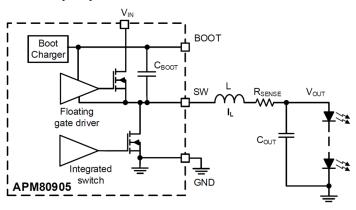

#### **Boot Circuit**

The APM80905 includes a bootstrap charging circuit with internal capacitor,  $C_{BOOT}$ . The internal boot capacitor is charged every switch cycle to ensure normal operation of the LED driver. Leave the BOOT pin open.

Figure 16: Boot Circuit

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### **Thermal Budgeting**

The APM80905 can supply up to 4 A of output current, but system designers must ensure the total internal power dissipation does not induce thermal shutdown. The maximum power dissipation of the device is:

Equation 9:

$$P_{DISS(MAX)} = \frac{\Delta T}{\Theta_{JA}} = \frac{T_{J(MAX)} - T_{AMB}}{\Theta_{JA}}$$

For example, on a standard 4-layer JEDEC board with 29°C/W thermal resistance, if the maximum ambient temperature is 100°C at the device case surface, then the maximum internal power dissipation is 1.7 W.

### **Protection Functions**

The APM80905 is designed to handle the following faults:

- Any pin-to-ground short

- Any pin-to-neighboring-pin short

- Any pin open

- External component open or short (inductor, resistors, capacitors, LEDs)

- Output-to-ground short

- LED PWM dimming signal on-time and duty cycle limits

### **Built-In Self-Test**

The APM80905 includes a built-in self-test (BIST) that checks the internal monitoring circuits for correct operation. If the BIST fails, then the APM80905 will not start and the FFn flag will assert low.

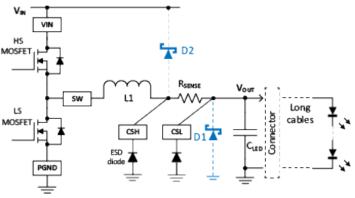

### **Fault Protection for Extreme Applications**

In some applications, such as those with long cables harnesses or inductive loads, additional protection diodes as shown in Figure 13 may be necessary to prevent the voltage at the CSH and CSL pins from exceeding the absolute maximum ratings of the pins. Diode D1 adds protection during output short-to-ground and diode D2 adds protection during an output open fault. It is up to the application designer to determine if the output faults could present voltage beyond the absolute maximum ratings and add D1 and D2 if necessary.

Figure 17: Optional Clamp Diodes

### LED Faults

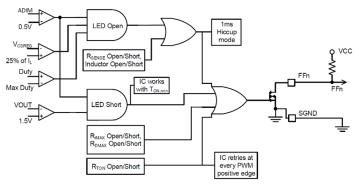

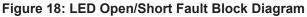

The APM80905 can detect open and short-to-ground LED strings. The diagram in Figure 18 shows the logic tree to report an open or short LED fault, as well as  $R_{TMAX}$ ,  $R_{DMAX}$ , and  $R_{TON}$  open or short-to-ground.

### Open LED Fault

The APM80905 can detect when the LED string connection is opened. The fault must be present longer than the fault deglitch timer, t<sub>FDG</sub>, and exist after PWM dimming mask timer at the start of each PWM cycle, t<sub>MASK</sub>, expires to be detected. If the PWM on-time is less than t<sub>MASK</sub> the open LED fault will not be detected. If the ADIM pin is less than 500 mV the open LED fault is masked. To detect an open LED fault, ADIM must be greater than 500 mV, the regulation voltage V<sub>CSREG</sub> must be less than 25% of the inductor current, and the converter duty cycle is switching at its maximum duty cycle.

Upon open LED fault detection, the APM80905 will assert the fault flag by driving the FFn pin low and enter hiccup mode. When the fault condition is removed the device recovers one hiccup period after the next PWM cycle by releasing the FFn pin to clear the fault flag and resumes normal regulation.

If the device is in a fault state and then ADIM goes below 500 mV the fault will remain asserted. When PWM goes low, the fault flag is latched and maintains its state until the next PWM rising edge. See Figure 19.

| ADIM | FFn <sup>n</sup> | LED Open<br>Fault? | Next PWM<br>Rising<br>Edge | FFn <sup>n+</sup> |  |  |  |  |

|------|------------------|--------------------|----------------------------|-------------------|--|--|--|--|

| High | х                | No                 | Ŀ                          | High              |  |  |  |  |

| High | х                | Yes                | Ţ                          | Low               |  |  |  |  |

| Low  | Low              | No                 | Ţ                          | High              |  |  |  |  |

#### Table 2: LED Open Fault Truth Table

Low

1

Low

I ow

х ADIM High means V<sub>ADIM</sub> > 500 mV; ADIM Low means V<sub>ADIM</sub> < 500 mV

Yes

### Output Short Fault

An output short condition such as LED shorted to GND or output capacitor shorted to GND is detected when  $V_{OUT} < 1.5$  V. The fault must be present longer than the fault deglitch timer, t<sub>FDG</sub>, and exist after PWM dimming mask timer at the start of each PWM cycle,  $t_{MASK}$ , to be detected. If the PWM on-time is less than  $t_{MASK}$  the output short fault will not be detected. During an output short fault condition, the regulator will not enter hiccup mode, but only switches the power stage at the minimum on-time and the fault flag is asserted by driving FFn low. When the fault condition is removed the device resumes normal regulation and clears the fault flag by releasing the FFn pin. If  $V_{ADIM} < 500$  mV the output short fault is masked. When PWM goes low, the fault flag is latched and maintains its state until the next PWM rising edge. See Figure 19.

Low

1

х

х

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### **Fault Detection Timers**

The APM80905 has a fault deglitch timer,  $t_{FDG}$ , and a fault mask timer,  $t_{MASK}$ , which work together to prevent fault reporting for short, transient system events. The mask timer is typically twice as long as the deglitch timer.

Both timers are disabled when the PWM pin is low. The mask timer starts on the PWM rising edge and prevents fault reporting for the beginning of each PWM pulse. The deglitch timer starts when PWM is high and a fault is detected. The two timers are independent and can overlap if a fault is detected while the mask timer is active. The FFn pin will assert low if a fault is present after both timers have expired.

The basic timing configurations are detailed in Figure 19. For each case, the TMAX and DMAX conditions are satisfied with no faults, and ADIM is greater than 500 mV.

Figure 19: LED Short and Open Fault Timing Diagrams

\*Current to regulation timer is 256 (Typical) switching cycles.

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

#### Table 3: System Failure Mode Table

| Failure Mode                                                                                     | Symptom Observed       | FAULT flag asserted? | APM80905 Response                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inductor open                                                                                    | No light from LEDs     | Yes <sup>[1]</sup>   | Enter hiccup mode with 1 ms retry period.                                                                                                                              |

| Inductor shorted                                                                                 | Dim light from LEDs    | Yes                  | Current through high-side MOSFET exceeds<br>power switch current limit causing overcurrent<br>fault. Switching stops and hiccup mode starts with<br>1 ms retry period. |

| Sense resistor open                                                                              | Dim light from LEDs    | Yes                  | Device switches with small switching duty cycle.                                                                                                                       |

| Sense resistor shorted                                                                           | Dim light from LEDs    | Yes                  | Triggers SW OCP fault, entering hiccup mode with 1 ms retry period.                                                                                                    |

| LED string open                                                                                  | No light from LEDs     | Yes <sup>[1]</sup>   | Enters hiccup mode with 1 ms retry period.                                                                                                                             |

| LED strings shorted<br>(Either LED shorted to GND or output<br>capacitor shorted to GND) < 1.5 V | No light from LEDs     | Yes [2]              | Continues switching at minimum $t_{ON}$ ; regulator will not enter hiccup mode.                                                                                        |

| Output/CSL capacitor open                                                                        | Normal light from LEDs | No                   | Possible decreased performance.                                                                                                                                        |

| TON resistor open or short                                                                       | Dim light from LEDs    | Yes                  | Part will retry and recover on fault removal.                                                                                                                          |

| TMAX pin open or shorted to GND                                                                  | No light from LEDs     | Yes                  | LEDs remain off while pin is open or shorted to GND, will recover when fault is removed.                                                                               |

| DMAX pin open or shorted to VCC or GND                                                           | No light from LEDs     | Yes                  | LEDs remain off while pin is open or shorted to GND, will recover when fault is removed.                                                                               |

| VCC shorted to GND IC does not operate                                                           |                        | [2]                  | Device cannot operate without $V_{CC}.$ $V_{CC}$ is internal protected against short to GND.                                                                           |

| Undervoltage lockout                                                                             | No light from LEDs     | [3]                  | Device is in shutdown.                                                                                                                                                 |

<sup>[1]</sup> For LED open or output short faults, fault flag will not be asserted when  $V_{ADIM} < 500 \text{ mV}$  or PWM dimming pulse width is less than fault mask timer. <sup>[2]</sup> For VCC short-to-GND Fault, internal logic circuit will not operate. FFn pin will be floating.

<sup>[3]</sup> For UVLO, APM80905 enters shutdown mode, FFn pin will be floating.

#### APPLICATION INFORMATION

#### **Power Inductor Selection**

To ensure stable operation while the LED current is on, the APM80905 should have a ripple voltage across the current sense resistor of at least 5 mV peak-to-peak. The voltage across the sense resistor must always be greater than 0 V, including at the valley of the inductor current ripple.

The recommended maximum inductor value can be calculated with Equation 10 at the minimum input voltage and maximum output voltage.

Equation 10:

$$L_{MAX} = \frac{V_{OUT}}{V_{IN}} \times \frac{(V_{IN} - V_{OUT})}{f_{SW} \times \Delta I_{L(pp)}}$$

where  $\Delta I_{L(pp)}$  is set to 10% of  $I_{OUT}$ .

The minimum recommended inductance by application is shown in Table 4. If the calculate  $L_{MAX} < L_{MIN}$ , use  $L_{MIN}$  from Table 4. The inductor current ripple,  $\Delta I_{L(pp)}$  can be calculated with Equation 11:

Equation 11:

$$\Delta I_{L(pp)} = \frac{(V_{IN} - V_{OUT}) t_{ON}}{L}$$

The inductor values in Table 4 represent suggested inductor values when  $V_{SENSE} \ge 100 \text{ mV}$ , where  $V_{SENSE} = V_{CSH} - V_{CSL}$ .

#### Table 4: Minimum Inductor Value by Application

| f <sub>SW</sub> (kHz) | L <sub>MIN</sub> (µH) | I <sub>OUT</sub> (A) | V <sub>IN</sub> -V <sub>OUT</sub><br>Minimum<br>Headroom<br>(V) | V <sub>OUT</sub> (V) |

|-----------------------|-----------------------|----------------------|-----------------------------------------------------------------|----------------------|

|                       |                       |                      | 4                                                               | 2.65 to 5            |

|                       | 3.3                   | 4                    | 3                                                               | 5 to 12              |

| 2250                  |                       |                      | 3                                                               | 12 to 32             |

| 2250                  |                       | 3.3                  | 3                                                               | 3.5                  |

|                       |                       | 2                    | 2                                                               | 2.65 to 32           |

|                       |                       | 1                    | 2                                                               |                      |

| 1500                  | 3.6                   | 1-4                  | 3                                                               | 2.65 to 32           |

| 1000                  | 3.9                   | 1-4                  | 3                                                               | 2.65 to 32           |

| 750                   | 6.8                   | 1-4                  | 3                                                               | 2.65 to 32           |

| 400                   | 10                    | 1-4                  | 3                                                               | 2.65 to 32           |

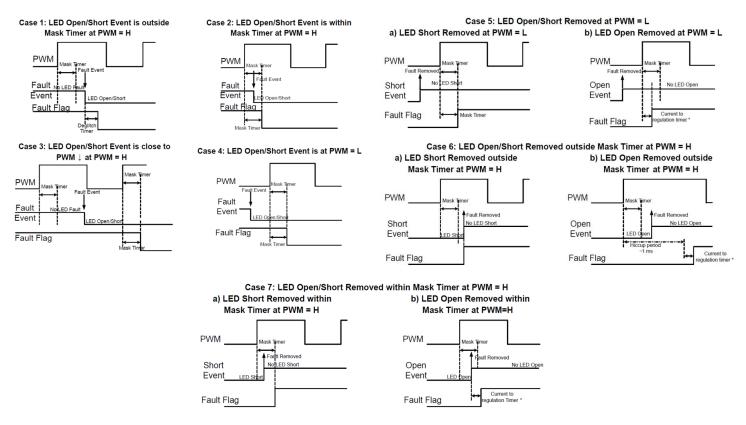

#### Output Filter Capacitor

The APM80905 is designed to operate in current regulation mode. Therefore, it does not require a large output capacitor to stabilize the output voltage. This results in lower solution cost and reduced PCB area requirements. The use of a large output capacitor is not recommended. In most applications, however, it is beneficial to add a small filter capacitor, about 0.47  $\mu$ F, across the LED string to serve as a filter and eliminate any switching spikes that may be seen by the LED string, helping to reduce EMI. Avoid placing a capacitor at the CSH node of the current sense resistor to maintain higher ripple across the current sense resistor. A 0.1  $\mu$ F ceramic capacitor placed very close to the CSL pin is also recommended.

#### Figure 20: Recommended Output Capacitor Placement

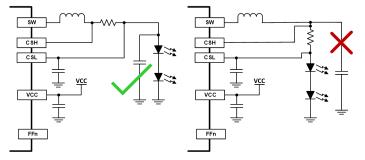

#### Use of EN Pin for Input Undervoltage Protection

The EN pin is an input to a hysteretic comparator with 1.2 V (typ) threshold to enable the device. Once enabled the EN comparator has a typical hysteresis of 100 mV and if EN is lowered below the 1.1 V (typ) turn-off threshold, the APM80905 enters shutdown.

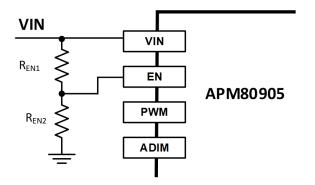

The EN pin can be used with a voltage divider from VIN to create a configurable undervoltage lockout threshold, as shown in Figure 21.

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

Figure 21: Input Undervoltage Lockout with EN pin

Select a convenient value for  $R_{\rm EN2}$  and use Equation 12 to calculate  $R_{\rm EN1}$  to estimate the rising enable threshold level. Use Equa-

tion 13 to estimate the falling input voltage threshold level once both resistors are known. Refer to the Electrical Characteristics section for  $V_{EN(HI)}$ ,  $V_{EN(HYS)}$ , and  $I_{EN}$ .

Equation 12:

$$R_{EN1} = \frac{V_{INTH(RISE)} - V_{EN(HI)}}{I_{EN} + \frac{V_{EN(HI)}}{R_{EN2}}}$$

where  $V_{INTH(RISE)}$  is the desired threshold of rising input voltage to enable the device and  $I_{EN}$  is the EN pin input current.

Equation 13:

$$V_{\text{INTH(FALL)}} = (V_{\text{EN(HI)}} - V_{\text{EN(HYS)}}) \times \left(\frac{R_{\text{EN1}} + R_{\text{EN2}}}{R_{\text{EN2}}}\right) + I_{\text{EN}} R_{\text{EN1}}$$

### **APPLICATION CIRCUIT DIAGRAM**

Figure 22: Application Circuit Diagram

#### **Table 5: Design Requirements**

| Requirement                       |         | Symbol                | Value | Unit |

|-----------------------------------|---------|-----------------------|-------|------|

| Input Voltage                     | Min     | V <sub>IN(MIN)</sub>  | 8     | V    |

|                                   | Nominal | V <sub>IN(NOM)</sub>  | 12    | V    |

|                                   | Max     | V <sub>IN(MAX)</sub>  | 24    | V    |

| UVLO Power On                     |         | V <sub>UVLO(ON)</sub> | 8.5   | V    |

| Switching Frequency               |         | f <sub>SW</sub>       | 2.15  | MHz  |

| Output Current                    |         | I <sub>LED</sub>      | 4     | A    |

| Infrared LED Forward Voltage Drop |         | V <sub>LEDF</sub>     | 2.3   | V    |

| Number of IR LEDs                 |         | -                     | 2     | _    |

| Analog Dimming                    |         | -                     | 100   | %    |

| PWM LED Dimming Frequency         |         | f <sub>PWM</sub>      | 60    | Hz   |

| PWM LED Dimming Duty Cycle        |         | D <sub>PWM</sub>      | 10    | %    |

| PWM Max On-Time Protection        |         | t <sub>PWM(MAX)</sub> | 3     | ms   |

| PWM Max Duty Cycle Protection     |         | D <sub>PWM(MAX)</sub> | 15    | %    |

### 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

### **DESIGN PROCEDURE**

This design procedure works through the component selection process for the two infrared LEDs with 60 Hz PWM application shown in the Application Circuit Diagram (Figure 22).

#### **Output Current Sense Resistor**

Use Equation 1 to calculate the sense resistor.

$$R_{SENSE} = \frac{195 \text{ mV}}{I_{LED}} = \frac{195 \text{ mV}}{4 \text{ A}} = 0.0488 \Omega$$

Select a standard value of 50 m  $\!\Omega.$

### **Power Stage Switching Frequency**

Use Equation 4 to calculate R<sub>TON</sub>.

$$R_{\text{TON}} = \frac{1}{0.028 \times f_{\text{SW(MHz)}}} = 16.6 \text{ k}\Omega$$

Select a 1% standard value that is lower than calculated to keep the switching frequency slightly higher and away from the AM radio band, 16.2 k $\Omega$ .

### **Power Inductor**

Use Equation 10 to calculate the inductor value at nominal  $V_{\rm IN}$  with 10% output current ripple.

$$L_{MAX} = \frac{V_{OUT}}{V_{IN}} \times \frac{(V_{IN} - V_{OUT})}{f_{SW} \times \Delta I_{L(pp)}} = \frac{4.6}{12} \times \frac{(12 - 4.6)}{2.15 \text{ MHz} \times 0.4} = 3.3 \text{ } \mu\text{H}$$

Referring to Table 4, the minimum inductance for applications switching at 2 MHz is 3.3  $\mu$ H. Since  $L_{MIN} = L_{MAX}$ , continue with the value of 3.3  $\mu$ H.

Using the same equation again at the minimum  $V_{IN}$  yields  $L_{MAX} = 2.2 \mu$ H; however, the  $L_{MIN}$  requirement from Table 4 must be met first, so the selected inductor value remains 3.3  $\mu$ H.

Use Equation 12 to calculate the output current ripple at each  $V_{\rm IN}$  level for the selected inductor value.

#### Table 6: Output Ripple for Selected Inductor Value

| V <sub>IN</sub> | Inductor Value | Output Current Ripple | R <sub>sense</sub> | Output<br>Voltage<br>Rippe |

|-----------------|----------------|-----------------------|--------------------|----------------------------|

| 8 V             | 3.3 µH         | 278 mA (6.96 %)       | 50 mΩ              | 14 mV                      |

| 12 V            | 3.3 µH         | 404 mA (10.1 %)       | 50 mΩ              | 20 mV                      |

| 24 V            | 3.3 µH         | 529 mA (13.2 %)       | 50 mΩ              | 26 mV                      |

This design meets the output voltage ripple requirement of greater than 5 mV peak-to-peak at all input voltages.

### **PWM Protections**

Use Equation 4 to calculate R<sub>TMAX</sub>.

$$R_{TMAX} = 2.5413(t_{MAX})^2 + 25.527 t_{MAX} = 99.5 k\Omega$$

Select a 1% standard value of 100 k $\Omega$ .

Use Equation 5 and Equation 6 to calculate  $R_{DMAX}$ .

$$t_{BLANK} = t_{MAX} \left(\frac{1}{D_{MAX}} - 1\right) = 0.017$$

seconds

$$\begin{split} R_{DMAX} = 0.1529 \times t_{BLANK}{}^2 + 6.5112 \times t_{BLANK} - 0.1486 = 155 \text{ k}\Omega \end{split}$$

Select a standard 1% value of 154 k $\Omega$ .

#### **Analog Dimming**

To disable analog dimming and regulate to 100% of the nominal output current tie the ADIM pin to VCC.

#### Undervoltage Lockout

Use a voltage divider on the EN pin from VIN to customize the undervoltage lockout thresholds. Use Equation 12 to calculate the top resistor of the voltage divider. Set the bottom resistor,  $R_{EN2}$ , to 100 k $\Omega$ .

$$R_{EN1} = \frac{V_{INTH(RISE)} - 1.2 \text{ V}}{I_{EN} + \frac{1.2 \text{ V}}{R_{EN2}}} = \frac{8.5 \text{ V} - 1.2 \text{ V}}{1 \mu \text{A} + \frac{1.2 \text{ V}}{100 \text{ k}\Omega}} = 561.5 \text{ k}\Omega$$

Select a standard 1% tolerance value of 562 k $\Omega.$

Use  $R_{\rm EN1}, R_{\rm EN2},$  and Equation 13 to calculate the UVLO turn-off threshold.

$$V_{\text{INTH(FALL)}} = (1.2 \text{ V} - 100 \text{ mV}) \times \left(\frac{R_{\text{EN1}} + R_{\text{EN2}}}{R_{\text{EN2}}}\right) + I_{\text{EN}} R_{\text{EN1}}$$

$$= 1.1 \text{ V} \times \left(\frac{662 \text{ k}\Omega}{100 \text{ k}\Omega}\right) + (1 \text{ }\mu\text{A} \times 562 \text{ }\text{k}\Omega) = 7.85 \text{ V}$$

With  $R_{EN1}$  of 60.4 k $\Omega$  and  $R_{EN2}$  of 10 k $\Omega$ , the device will be enabled at an input voltage of 8.5 V and disabled at an input voltage of approximately 7.85 V (typical). At the nominal input voltage, 12 V, the resistor divider will consume approximately 18  $\mu A$ .

### **Output Capacitor**

Add the recommended output filter capacitor of 0.47  $\mu F$  after the sense resistor, across the LED string.

Additionally, a 0.1  $\mu$ F ceramic capacitor close to the CSL pin is recommended for control loop stability. A diode from CSL to ground can optionally be added.

#### **Table 7: Application Component Values**

| Parameter                                       | Symbol             | Value | Unit |

|-------------------------------------------------|--------------------|-------|------|

| Output Current Sense Resistor                   | R <sub>SENSE</sub> | 50    | mΩ   |

| Power Stage On-Time Selection<br>Resistor       | R <sub>TON</sub>   | 16.2  | kΩ   |

| Power Inductor                                  | L                  | 3.3   | μH   |

| PWM On-Time Protection Selection<br>Resistor    | R <sub>TMAX</sub>  | 100   | kΩ   |

| PWM Duty Cycle Protection<br>Selection Resistor | R <sub>DMAX</sub>  | 154   | kΩ   |

| Undervoltage Lockout Top Resistor               | R <sub>EN1</sub>   | 562   | kΩ   |

| Undervoltage Lockout Bottom<br>Resistor         | R <sub>EN2</sub>   | 100   | kΩ   |

| Output Capacitor                                | C <sub>OUT</sub>   | 0.47  | μF   |

| CSL Stability Capacitor                         | C <sub>CSL</sub>   | 0.1   | μF   |

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

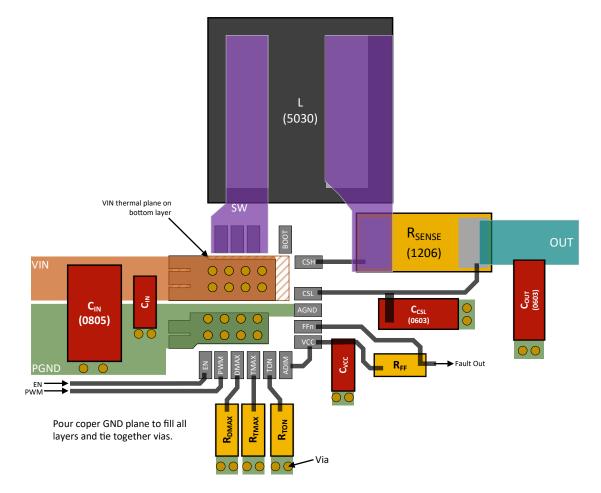

### PCB LAYOUT GUIDELINES

The APM80905 is designed to minimize electromagnetic (EM) emissions when proper PCB layout techniques are adopted. A good PCB layout is also critical for the APM80905 to provide clean and stable output voltages and current. Design guidelines for EMI/EMC-aware PCB layout and minimum  $R_{\theta JA}$  are presented below. Figure 23 shows a sample PCB layout for the APM80905.

- Place the ceramic input capacitors as close as possible to the VIN pin and PGND pins to minimize the loop area, and the traces of the input capacitors to VIN pin should be short and wide to minimize the inductance. A bulk/electrolytic input capacitor can be located further away from the VIN pin. The APM809805, input capacitors, and VIN traces should be on the same side of the board.

- The loop from the input supply and capacitors, through the high-side MOSFET and output inductor, to the output capacitors and back to ground, should be minimized and use relatively wide traces.

- Place the output capacitor(s) across the LED load, after the sense resistor, to maintain ripple current through the sense resistor for the control loop. The output capacitor(s) must use a ground plane to make a very low-inductance connection to the PCB GND.

- The output inductor, current sense resistor, and the APM80905 should be on the same board layer. Connect the output inductor and the current sense resistor with a wide trace.

- The current sense resistor should be placed close to the APM80905 CSH and CSL pins to minimize offset and gain error due to PCB parasitics. A ceramic capacitor, C<sub>CSL</sub>, must be placed close to the CSL pin.

- Place the output inductor as close as possible to the SW pin with short and wide traces. The voltage at SW node transitions

from 0 V to  $V_{IN}$  with a high dv/dt rate. This node is the root cause of many noise issues. It is suggested to minimize the SW copper area to minimize the coupling capacitance between SW node and other noise-sensitive nodes; however, the SW node area must be large enough to conduct high current. A copper ground area can be placed underneath the SW node to provide additional shielding.

- Place R<sub>TON</sub>, R<sub>TMAX</sub>, and R<sub>DMAX</sub> as close as possible to their respective pins and avoid tying them to GND where large currents will flow.

- Allegro recommends a 4-layer PCB (TOP, L2, L3, BOT). Heavier copper layers, reduced material between layers and a good amount of thermal vias are the keys to improved thermal performance. Use TOP layer for routing high-current traces, L2 for a solid GND plane, L3 for most other routing, and BOT layer for solid GND plane or optionally other components without low-impedance traces constraints—the FFn pull-up resistor could be on the BOT plane if desired.

- If two-layer only (TOP and BOT) PCB is mandatory, place all the components on the TOP layer and limit the routing only to the top layer. Use BOT layer as GND plane.

- When connecting the input and output ceramic capacitors, use multiple vias to GND planes and place the vias as close as possible to the pads of the components. Do not use thermal reliefs around the pads for the input and output ceramic capacitors.

- To minimize thermal resistance  $(R_{\theta JA})$ , extend ground planes on TOP layer as much as possible and use plenty of thermal vias to connect them to GND plane in BOT layer.

- To minimize PCB losses and improve system efficiency, the power traces should be as wide as reasonably possible.

Figure 23: Sample PCB Layout

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

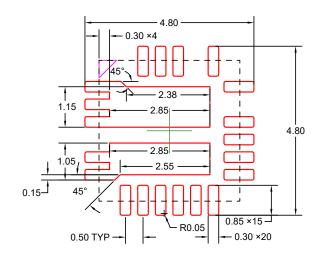

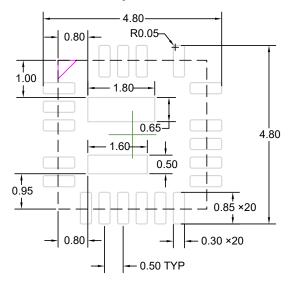

### PACKAGE OUTLINE DRAWING AND RECOMMENDED PCB FOOTPRINT

Figure 24: 24-Lead 4 mm × 4mm QFN (Suffix NB)

# 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

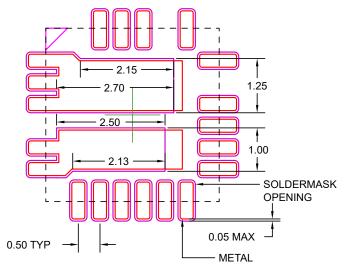

**PCB** Footprint – Copper

#### PCB Footprint – Paste

PCB Footprint – Soldermask

#### Figure 25: Recommended PCB Footprint

Altium and Cadence schematic and layout library files for the APM80905 are provided on the APM80905 product page on Allegromicro.com.

## 36 V, 4 A, Low-EMI, Synchronous Buck LED Driver Module with PWM Monitor

#### **Revision History**

| Number | Date               | Description                                                |

|--------|--------------------|------------------------------------------------------------|

| -      | August 9, 2023     | Initial release                                            |

| 1      | September 19, 2023 | Updated VCC to PGND pin capacitor ratings (pages 4 and 10) |

Copyright 2023, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com