## Isolated Amplifier with Adjustable Gain and Single-Ended Output

#### **FEATURES**

- ▶ High-Impedance input for isolated voltage measurement

- ► Low offset error and drift (output offset voltage): ±6 mV (Max) at 25°C and −22 µV/°C (Typ)

- ▶ Low gain error and drift: ±0.5% (max) and ±27 ppm/°C (max)

- ► Voltage-supply range

- ▶ V<sub>DD1</sub>: 4.5 V to 5.5 V

- ▶ V<sub>DD2</sub>: 4.5 V to 5.5 V

- ▶ Bandwidth: 210 kHz

- ▶ Isolation voltage: 3000 V rms for ADuM3195

- Safety and regulatory approvals (pending)

- UL recognition (pending): 3000 V rms for 1 minute per UL 1577

- CSA (pending)

- VDE certificate of conformity (pending)

- ▶ ▶ DIN VDE V 0884-11:2017-01

- V<sub>IORM</sub> = 636 V peak (reinforced)

- ▶ Wide temperature range

- ► -40°C to +125°C ambient operation

- ▶ 150°C maximum junction temperature

- ► AEC-Q100 qualified for automotive applications

#### **APPLICATIONS**

- Inverters

- DC to DC converters

- On-board chargers

#### **GENERAL DESCRIPTION**

The ADuM3195<sup>1</sup> are isolation amplifiers based on Analog Devices, Inc., *i*Coupler<sup>®</sup> technology. The ADuM3195 have very low offset and gain error, making them ideal for many isolated voltage sensing applications.

Unlike optocoupler-based solutions, which have an uncertain current transfer ratio over lifetime and at high temperatures, the ADuM3195 transfer functions do not change over lifetime, and are stable over a wide temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Included in the ADuM3195 are wideband operational amplifiers useful for a variety of commonly used applications. Included in the ADuM3195 are two high accuracy 2.5 V references outputs.

The ADuM3195 is packaged in a 16-lead quarter small outline package (QSOP) for a 3000 V rms isolation voltage rating.

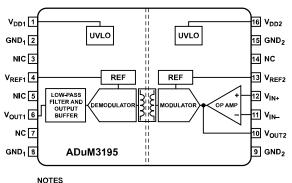

#### FUNCTIONAL BLOCK DIAGRAM

1. NIC = NOT INTERNALLY CONNECTED. THIS PIN IS NOT CONNECTED INTERNALLY. 2. NC = NO CONNECT.

Figure 1.

60

<sup>1</sup> Protected by U.S. Patents 5,952,849, 6,873,065 and 7,075,329. Other patents pending.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 | 1 |

| General Description                          | 1 |

| Functional Block Diagram                     | 1 |

| Specifications                               | 3 |

| Package Characteristics                      | 4 |

| Regulatory Information                       | 5 |

| Insulation and Safety Related Specifications | 5 |

| Recommended Operating Conditions             | 5 |

| DIN VDE V 0884-11:2017-01 Insulation         |   |

| Characteristics (Pending)                    | 6 |

| Absolute Maximum Ratings                     | 7 |

| ESD Caution                                  |   |

|                                              |   |

**REVISION HISTORY**

4/2023—Revision 0: Initial Version

| Pin Configuration and Function Descriptions | 8  |

|---------------------------------------------|----|

| Typical Performance Characteristics         | 9  |

| Theory of Operation                         | 15 |

| Applications Information                    | 16 |

| Application Block Diagram                   | 16 |

| Design Example                              | 17 |

| DC Correctness and Magnetic Field           |    |

| Immunity                                    | 17 |

| Layout Considerations                       | 18 |

| Outline Dimensions                          | 19 |

| Ordering Guide                              | 19 |

| Evaluation Board                            |    |

| Automotive Products                         | 19 |

|                                             |    |

$V_{DD1} = V_{DD2} = 4.5$  V to 5.5 V for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All typical specifications are at  $T_A = 25^{\circ}C$  and  $V_{DD1} = V_{DD2} = 5$  V, unless otherwise noted.

| Parameter                                             | Min  | Тур       | Max                    | Unit   | Test Conditions/Comment                                                        |

|-------------------------------------------------------|------|-----------|------------------------|--------|--------------------------------------------------------------------------------|

| OPERATIONAL AMPLIFIER (OP AMP)                        |      | 71        |                        |        |                                                                                |

| Input Offset Voltage (V <sub>OS</sub> )               | -0.5 |           | +1.5                   | mV     |                                                                                |

| Input Offset Voltage (VOS)                            | -11  | +11 µV/°C |                        |        |                                                                                |

| Input Op Amp Gain                                     | 85   |           | • • •                  | dB     |                                                                                |

| Input Common-Mode Range <sup>1</sup>                  | 0.25 |           | V <sub>DD2</sub> - 0.7 | V      |                                                                                |

| Gain-Bandwidth Product                                | 0.23 | 15        | V <sub>DD2</sub> = 0.7 | MHz    |                                                                                |

|                                                       |      | -85       |                        | dB     |                                                                                |

| Common-Mode Rejection                                 |      |           |                        |        |                                                                                |

| Input Resistance                                      |      | 10<br>5   |                        | GΩ     |                                                                                |

| Input Capacitance                                     | 0.0  | 5         | .0.0                   | pF     | T 0500                                                                         |

| Input-Bias Current <sup>2</sup>                       | -0.2 |           | +0.2                   | nA     | T <sub>A</sub> = 25°C                                                          |

|                                                       |      |           |                        |        | $V_{IN+}$ or $V_{IN-}$ = 2.5 V                                                 |

| Input-Bias Current Drift                              | -25  |           | +75                    | pA/°C  |                                                                                |

| Op Amp Output Voltage Range <sup>1</sup>              | 0.1  |           | V <sub>DD2</sub>       | V      |                                                                                |

| REFERENCE                                             |      |           |                        |        |                                                                                |

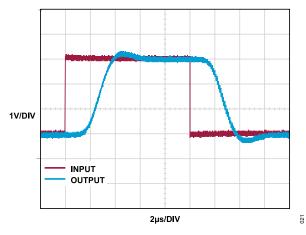

| Output Voltage, V <sub>REF1</sub> , V <sub>REF2</sub> |      |           |                        |        | 0 mA to 1 mA load                                                              |

|                                                       | 2.49 | 2.50      | 2.51                   | V      | T <sub>A</sub> = 25°C                                                          |

|                                                       | 2.47 | 2.50      | 2.53                   | V      | $T_A = T_{MIN}$ to $T_{MAX}$                                                   |

| Reference Temperature Coefficient (Tempco)            |      | ±25       |                        | ppm/°C |                                                                                |

| Output Current                                        | 1.0  |           |                        | mA     |                                                                                |

| OUTPUT CHARACTERISTICS                                |      |           |                        |        |                                                                                |

| Linear Output Voltage Range <sup>1</sup>              | 0.25 |           | V <sub>DD2</sub> - 0.7 | V      |                                                                                |

| Output Offset Voltage                                 | -6.0 |           | +6.0                   | mV     | V <sub>OUT1</sub> – V <sub>IN+</sub> (op amp in buffer                         |

|                                                       |      |           |                        |        | configuration), $V_{IN+} = 2.5 \text{ V}-$ , $T_A = 25^{\circ}\text{C}$        |

| Output Offset Drift                                   |      | -22       |                        | µV/°C  | $V_{IN+} = 2.5 \text{ V}, \text{ T}_{A} = -40 \text{ to } 125^{\circ}\text{C}$ |

| Output Gain <sup>3</sup>                              |      | 1         |                        |        | V <sub>OUT1</sub> /V <sub>IN+</sub> (op amp in buffer configuration)           |

| Output Gain Error                                     | -0.5 |           | +0.5                   | %      |                                                                                |

| Output Gain Error Drift                               | -27  |           | +27                    | ppm/°C |                                                                                |

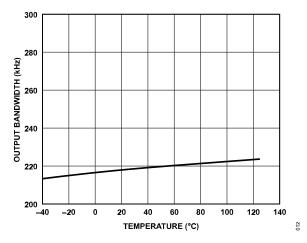

| Output −3 dB Bandwidth                                |      | 210       |                        | kHz    | From V <sub>OUT1</sub> to V <sub>IN+</sub>                                     |

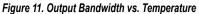

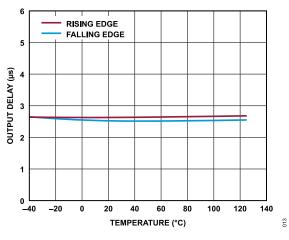

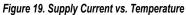

| Output Delay                                          |      | 3         |                        | μs     | 50% input to 50% output within $V_{IN+} = 1$<br>V to 4 V                       |

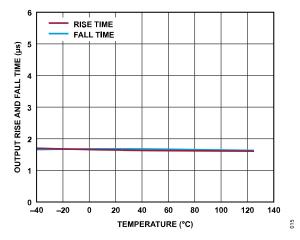

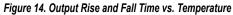

| Output Rise and Fall time                             |      | 2         |                        | μs     | 10% to 90% within $V_{IN+}$ = 1 V to 4 V                                       |

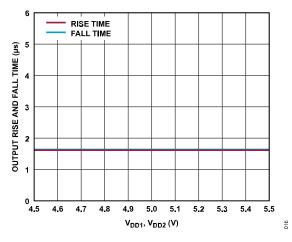

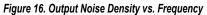

| Output Noise                                          |      | 540       |                        | μV rms | f <sub>IN</sub> = 1 kHz, bandwidth = 100 kHz                                   |

|                                                       |      | 1         |                        | mV rms | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 200 kHz                                 |

| SNR                                                   |      | 69        |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 100 kHz                                 |

|                                                       |      | 64        |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 200 kHz                                 |

| Total Harmonic Distortion Plus Noise (THD + N)        |      | -54       |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 100 kHz                                 |

| Ratio                                                 |      | -56       |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 200 kHz                                 |

| Signal-to-Noise-and-Distortion (SINAD) Ratio          |      | -30<br>57 |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 100 kHz                                 |

| Signal-to-Noise-and-Distontion (SiNAD) Ratio          |      |           |                        |        |                                                                                |

| Dower Cumby Delection Datia (DCDD)                    |      | 56        |                        | dB     | $f_{IN} = 1 \text{ kHz}$ , bandwidth = 200 kHz                                 |

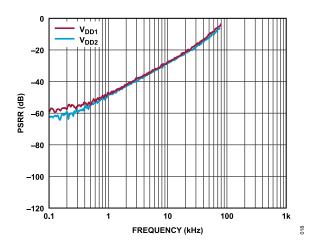

| Power-Supply Rejection Ratio (PSRR)                   | 10   | -60       |                        | dB     | DC, $V_{DD1} = V_{DD2} = 4.5 V$ to 5.5 V                                       |

| Output Resistive Load                                 | 10   |           |                        | kΩ     |                                                                                |

| Output Capacitive Load                                |      |           | 100                    | pF     |                                                                                |

| Common-Mode Transient Immunity (CMTI) <sup>2, 4</sup> | 100  | 150       |                        | kV/µs  | $ GND_1 - GND_2  = 1.5 \text{ kV}$                                             |

| POWER SUPPLY                                          |      |           |                        |        |                                                                                |

| Operating Range, Side 1                               | 4.5  | 5.0       | 5.5                    | V      | V <sub>DD1</sub>                                                               |

#### Table 1. Specifications (Continued)

| Parameter                                               | Min | Тур | Max | Unit | Test Conditions/Comment                                   |

|---------------------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------|

| Undervoltage Lockout (UVLO) Positive Going<br>Threshold |     | 4.2 |     | V    |                                                           |

| UVLO Negative Going Threshold                           |     | 4.0 |     | V    |                                                           |

| Operating Range, Side 2                                 | 4.5 | 5.0 | 5.5 | V    | V <sub>DD2</sub>                                          |

| UVLO Positive Going Threshold                           |     | 4.2 |     | V    |                                                           |

| UVLO Negative Going Threshold                           |     | 4.0 |     | V    |                                                           |

| V <sub>OUT1</sub> Impedance                             |     | 35  |     | Ω    | V <sub>DD1</sub> = 5 V, V <sub>DD2</sub> < UVLO threshold |

|                                                         |     | 3.7 |     | kΩ   | V <sub>DD1</sub> < UVLO threshold                         |

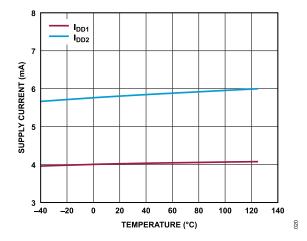

| Supply Current                                          |     |     |     |      |                                                           |

| I <sub>DD1</sub>                                        |     | 4.1 | 4.9 | mA   |                                                           |

| I <sub>DD2</sub>                                        |     | 5.9 | 7.3 | mA   |                                                           |

<sup>1</sup> For a maximum deviation of ±1.25% from the best-fit line over the specified input range of 1 V to 3.5 V. Op amp in buffer configuration.

<sup>2</sup> Guaranteed by design and characterization. Not production tested.

<sup>3</sup> Output gain defined as the slope of the best-fit line over the specified input range, with the offset error adjusted out.

$^4$  CMTI error is an output disturbance greater than 100 mV lasting more than 2  $\mu$ s.

#### PACKAGE CHARACTERISTICS

#### Table 2. Package Characteristics

| Parameter                                    | Symbol           | Min | Тур              | Max | Unit | Test Conditions/Comments                            |

|----------------------------------------------|------------------|-----|------------------|-----|------|-----------------------------------------------------|

| RESISTANCE                                   |                  |     |                  |     |      |                                                     |

| Input-to-Output <sup>1</sup>                 | R <sub>I-O</sub> |     | 10 <sup>13</sup> |     | Ω    |                                                     |

| CAPACITANCE                                  |                  |     |                  |     |      |                                                     |

| Input-to-Output <sup>1</sup>                 | CI-O             |     | 2.2              |     | pF   | f = 1 MHz                                           |

| Input Capacitance <sup>2</sup>               | CI               |     | 4.0              |     | pF   |                                                     |

| IC JUNCTION-TO-AMBIENT THERMAL<br>RESISTANCE |                  |     |                  |     |      |                                                     |

| 16-Lead QSOP                                 | θ <sub>JA</sub>  |     | 83               |     | °C/W | Thermocouple located at center of package underside |

<sup>1</sup> The device is considered a 2-terminal device; Pins 1 through Pin 8 are shorted together, and Pin 9 through Pin 16 are shorted together.

<sup>2</sup> Input capacitance is from any input data pin to ground.

#### **REGULATORY INFORMATION**

#### Table 3. ADuM3195 Regulatory Information (Pending)

| UL                                                                  | CSA <sup>1</sup>                                                                                         | VDE <sup>2</sup>                                                                               |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Recognized Under 1577 Component Recognition<br>Program <sup>3</sup> |                                                                                                          | Certified according to DIN VDE V 0884-11:2017-01                                               |

| Single Protection, 3000 V rms Isolation Voltage, 16-<br>Lead QSOP   | Basic insulation per CSA 62638-1-03 and IEC 62638-1, 350 V rms (495 V peak) maximum working voltage      | Reinforced insulation, 636 V peak V <sub>IOTM</sub> = 4200 V pk, V <sub>IOSM</sub> = 6250 V pk |

|                                                                     | Reinforced insulation per CSA 62638-1-03 and IEC 62638-1, 175 V rms (247 V peak) maximum working voltage |                                                                                                |

| File E214100 (pending)                                              | File (pending)                                                                                           | (pending)                                                                                      |

<sup>1</sup> Working voltages are quoted for Pollution Degree 2, Material Group III.

<sup>2</sup> In accordance with DIN VDE V 0884-11:2017-01, each ADuM3195 is proof tested by applying an insulation test voltage ≥ 1192 V peak for 1 sec (partial discharge detection limit = 5 pC). The \* marking branded on the component designates DIN VDE V 0884-11:2017-01 approval.

<sup>3</sup> In accordance with UL 1577, each ADuM3195 is proof tested by applying an insulation test voltage ≥ 3600 V rms for 1 sec (current leakage detection limit = 5 μA).

## INSULATION AND SAFETY RELATED SPECIFICATIONS

#### Table 4. Insulation and Safety Related Specifications

| Parameter                                                                   | Symbol  | Value | Unit  | Test Conditions/Comments                                                                                                                           |

|-----------------------------------------------------------------------------|---------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 3000  | V rms | 1 minute duration                                                                                                                                  |

| Minimum External Air Gap (Clearance)                                        | L (I01) | 3.2   | mm    | Measured from input terminals to output terminals, shortest distance through air                                                                   |

| Minimum External Tracking (Creepage)                                        | L (102) | 3.2   | mm    | Measured from input terminals to output terminals, shortest distance path along body                                                               |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 3.8   | mm    | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the printed circuit board (PCB) mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 0.041 | mm    | Insulation distance through insulation                                                                                                             |

| Tracking Resistance (Comparative Tracking Index)                            | CTI     | >400  | V     | DIN IEC 112/VDE 0303, Part 1                                                                                                                       |

| Material Group                                                              |         | П     |       | Material Group DIN VDE 0110, 1/89, Table 1                                                                                                         |

#### **RECOMMENDED OPERATING CONDITIONS**

#### Table 5. Recommended Operating Conditions

| Parameter                    | Symbol                              | Min | Max  | Unit |

|------------------------------|-------------------------------------|-----|------|------|

| OPERATING TEMPERATURE        | T <sub>A</sub>                      | -40 | +125 | °C   |

| SUPPLY VOLTAGES <sup>1</sup> | V <sub>DD1</sub> , V <sub>DD2</sub> | 4.5 | 5.5  | V    |

<sup>1</sup> All voltages are relative to their respective grounds.

#### DIN VDE V 0884-11:2017-01 INSULATION CHARACTERISTICS (PENDING)

These isolators are suitable for reinforced isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data. The asterisk (\*) marking branded on the package denotes DIN VDE V 0884-11:2017-01 approval (pending).

#### Table 6. ADuM3195 VDE V 0884-11 Insulation Characteristics

| Description                                          | Test Conditions/Comments                                                                                                          | Symbol              | Characteristic <sup>1</sup> | Unit              |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-------------------|

| Installation Classification per DIN VDE 0110         |                                                                                                                                   |                     |                             |                   |

| For Rated Mains Voltage ≤ 150 V rms                  |                                                                                                                                   |                     | I to IV                     |                   |

| For Rated Mains Voltage ≤ 300 V rms                  |                                                                                                                                   |                     | I to III                    |                   |

| For Rated Mains Voltage ≤ 400 V rms                  |                                                                                                                                   |                     | I to II                     |                   |

| Climatic Classification                              |                                                                                                                                   |                     | 40/125/21                   |                   |

| Pollution Degree per DIN VDE 0110, Table 1           |                                                                                                                                   |                     | 2                           |                   |

| Maximum Working Insulation Voltage                   |                                                                                                                                   | VIORM               | 636                         | VPEAK             |

| Input to Output Test Voltage, Method B1              | $V_{IORM}$ × 1.875 = $V_{PD\ (M)},$ 100% production test, $t_{INI}$ = $t_M$ = 1 sec, partial discharge < 5 pC                     | V <sub>PD (M)</sub> | 1192                        | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method A               |                                                                                                                                   |                     |                             |                   |

| After Environmental Tests Subgroup 1                 | $V_{\rm IORM}$ × 1.5 = $V_{PD~(M)},$ $t_{\rm INI}$ = 60 sec, $t_{\rm M}$ = 10 sec, partial discharge < 5 pC                       | V <sub>PD (M)</sub> | 954                         | V <sub>PEAK</sub> |

| After Input or Safety Test Subgroup 2 and Subgroup 3 | $V_{\text{IORM}}$ × 1.2 = $V_{\text{PD}(\text{M})},$ $t_{\text{INI}}$ = 60 sec, $t_{\text{M}}$ = 10 sec, partial discharge < 5 pC | V <sub>PD (M)</sub> | 763                         | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                        |                                                                                                                                   | V <sub>IOTM</sub>   | 4200                        | VPEAK             |

| Surge Isolation Voltage                              | V <sub>PEAK</sub> = 10 kV, 1.2 µs rise time, 50 µs, 50% fall time                                                                 | VIOSM               | 6250                        | VPEAK             |

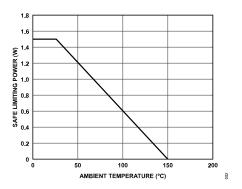

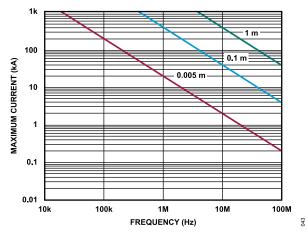

| Safety Limiting Values                               | Maximum value allowed in the event of a failure (see Figure 2)                                                                    |                     |                             |                   |

| Case Temperature                                     |                                                                                                                                   | T <sub>S</sub>      | 150                         | °C                |

| Safety Total Dissipated Power                        |                                                                                                                                   | Ps                  | 1.51                        | W                 |

| Insulation Resistance at T <sub>S</sub>              | V <sub>IO</sub> = 500 V                                                                                                           | R <sub>S</sub>      | >10 <sup>9</sup>            | Ω                 |

$^1\,$  For information about  $t_M,\,t_{INI},$  and  $V_{IO},$  see DIN VDE V 0884-11:2017-01.

Figure 2. Thermal Derating Curve for the ADuM3195, Dependence of Safety Limiting Values on Case Temperature, Per DIN VDE V 0884-11:2017-01

### **ABSOLUTE MAXIMUM RATINGS**

#### $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 7. Absolute Maximum Ratings

| Parameter                                                | Rating                                                               |

|----------------------------------------------------------|----------------------------------------------------------------------|

| Storage Temperature (T <sub>ST</sub> ) Range             | −65°C to +150°C                                                      |

| Ambient Operating Temperature (T <sub>A</sub> )<br>Range | -40°C to +125°C                                                      |

| Junction Temperature (T <sub>J</sub> )                   | -40°C to +150°C                                                      |

| Supply Voltages                                          |                                                                      |

| V <sub>DD1</sub> , V <sub>DD2</sub> <sup>1</sup>         | -0.5 V to +7.0 V                                                     |

| Input Voltages                                           |                                                                      |

| V <sub>IN+</sub> , V <sub>IN-</sub>                      | -0.5 V to V <sub>DD2</sub> +0.5 V                                    |

| Output Voltages                                          |                                                                      |

| $V_{REF1}, V_{OUT1}, V_{REF2}, V_{OUT2}$                 | -0.5 V to V <sub>DD1</sub> +0.5 V, -0.5 V to V <sub>DD2</sub> +0.5 V |

| Output Current per Output Pin                            | -11 mA to +11 mA                                                     |

| Common-Mode Transients <sup>2</sup>                      | -200 kV/µs to +200 kV/µs                                             |

<sup>1</sup> All voltages are relative to their respective grounds.

<sup>2</sup> Refers to the common-mode transients across the insulation barrier. The common-mode transients exceeding the absolute maximum ratings may cause latchup or permanent damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Table 8. Maximum Continuous Working Voltage for the RQ-16 (QSOP)

Package

| Parameter <sup>1</sup>         | Rating               | Constraint                                                                                                                |

|--------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| AC Voltage Bipolar<br>Waveform |                      |                                                                                                                           |

| Basic Insulation               | 450 V <sub>rms</sub> | Basic insulation rating per IEC<br>60747-17. Accumulative failure rate<br>over lifetime (FROL) ≤ 1000 ppm at<br>20 years. |

| Reinforced Insulation          | 225 V <sub>rms</sub> | Rating limited by package creepage<br>per IEC 60664-1:2020 in Pollution<br>Degree 2 environment.                          |

| DC Voltage                     |                      |                                                                                                                           |

| Basic Insulation               | 450 V DC             | Rating limited by package creepage<br>per IEC 60664-1:2020 in Pollution<br>Degree 2 environment.                          |

| Reinforced Insulation          | 225 V DC             | Rating limited by package creepage<br>per IEC 60664-1:2020 in Pollution<br>Degree 2 environment.                          |

<sup>1</sup> Refers to the continuous voltage magnitude imposed across the isolation barrier in a Pollution Degree 2 environment.

### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

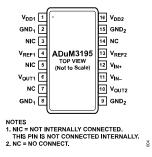

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

#### Table 9. Pin Function Descriptions

| Pin No. | Mnemonic          | Description                                                                                                                                       |

|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD1</sub>  | Supply Voltage for Side 1, Pin 1 to Pin 8 (4.5 V to 5.5 V). Connect a 0.1 µF and a 1 µF capacitor between V <sub>DD1</sub> and GND <sub>1</sub> . |

| 2       | GND <sub>1</sub>  | Ground Reference for Side 1.                                                                                                                      |

| 3       | NIC               | Not Internally Connected. This pin is not connected internally. Connect this pin to V <sub>DD1</sub> , GND <sub>1</sub> , or leave floating.      |

| 4       | V <sub>REF1</sub> | Reference Output Voltage for Side 1. The maximum capacitance for this pin (CREFOUT1) must not exceed 15 pF.                                       |

| 5       | NIC               | Not Internally Connected. This pin is not connected internally. Connect this pin to V <sub>DD1</sub> , GND <sub>1</sub> , or leave floating.      |

| 6       | V <sub>OUT1</sub> | Isolated Output Voltage.                                                                                                                          |

| 7       | NC                | No Connect. Connect this pin to GND <sub>1</sub> . Do not leave it floating.                                                                      |

| 8       | GND <sub>1</sub>  | Ground Reference for Side 1.                                                                                                                      |

| 9       | GND <sub>2</sub>  | Ground Reference for Side 2 (Pin 9 to Pin 16).                                                                                                    |

| 10      | V <sub>OUT2</sub> | Output of the Op Amp.                                                                                                                             |

| 11      | V <sub>IN</sub> - | Inverting Op Amp Input.                                                                                                                           |

| 12      | V <sub>IN+</sub>  | Noninverting Op Amp Input.                                                                                                                        |

| 13      | V <sub>REF2</sub> | Reference Output Voltage for Side 2. The maximum capacitance for this pin (CREFOUT) must not exceed 22 nF.                                        |

| 14      | NC                | No Connect. Connect this pin to GND <sub>2</sub> . Do not leave it floating.                                                                      |

| 15      | GND <sub>2</sub>  | Ground Reference for Side 2.                                                                                                                      |

| 16      | V <sub>DD2</sub>  | Supply Voltage for Side 2 (4.5 V to 5.5 V). Connect a 0.1 $\mu$ F and a 1 $\mu$ F capacitor between V <sub>DD1</sub> and GND <sub>1</sub> .       |

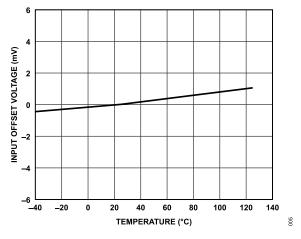

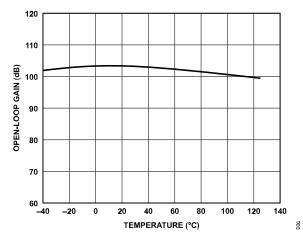

Figure 4. Op Amp Input Offset Voltage vs. Temperature

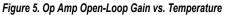

Figure 6. V<sub>REF</sub> vs. Temperature

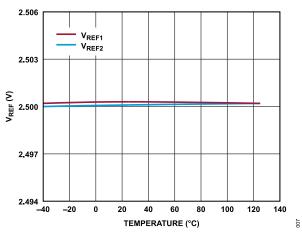

Figure 7. V<sub>OUT1</sub> Offset Voltage vs. Temperature

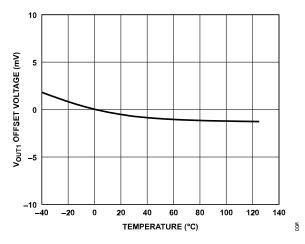

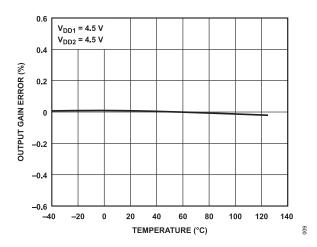

Figure 8. Output Gain Error vs. Temperature

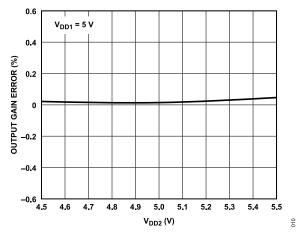

Figure 9. Output Gain Error vs. V<sub>DD2</sub>

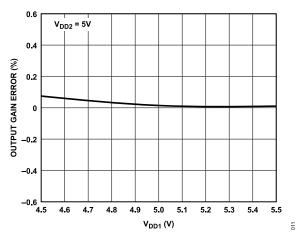

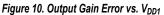

Figure 12. Output Delay vs. Temperature

Figure 13. Output Delay vs. Supply Voltage

Figure 15. Output Rise and Fall Time vs. Supply Voltage

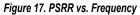

Figure 18. Normalized V<sub>OUT1</sub> vs. Load

Figure 20. Output Square-Wave Response

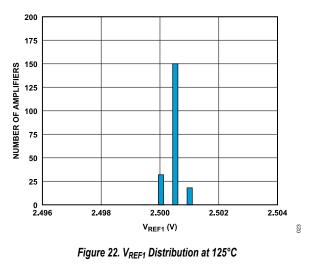

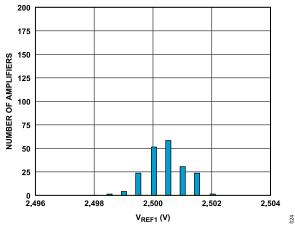

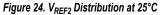

Figure 21. V<sub>REF1</sub> Distribution at 25°C

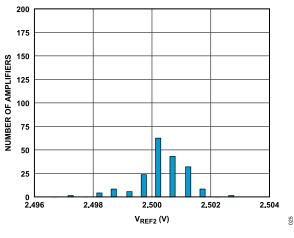

2.500

V<sub>REF2</sub> (V)

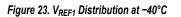

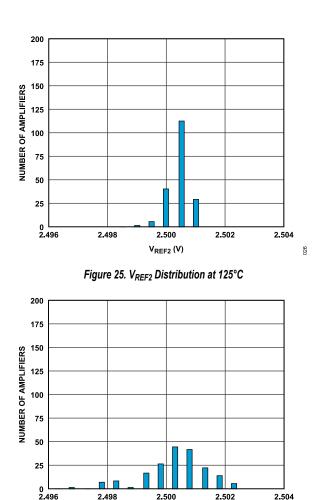

Figure 26. V<sub>REF2</sub> Distribution at -40°C

1.000

VIN+ TO VOUT1 GAIN (V/V)

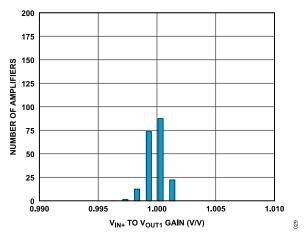

Figure 27. V<sub>IN+</sub> to V<sub>OUT1</sub> Gain Distribution at 25°C

2.502

1.005

2.504

027

2.498

0.995

200

175

50

25

0.990

1.010

028

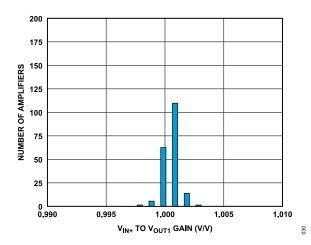

Figure 28. VIN+ to VOUT1 Gain Distribution at 125°C

Figure 29. V<sub>IN+</sub> to V<sub>OUT1</sub> Gain Distribution at -40°C

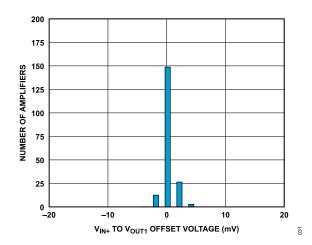

Figure 30.  $V_{IN+}$  to  $V_{OUT1}$  Offset-Voltage Distribution at 25°C, Output Offset Voltage for  $V_{IN+}$  = 2.5 V Op Amp in Buffer Configuration

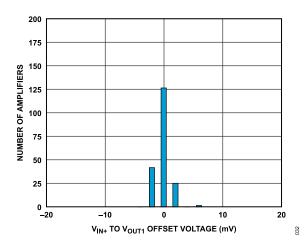

Figure 31. VIN+ to VOUT1 Offset-Voltage Distribution at 125°C

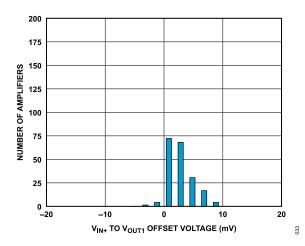

Figure 32. V<sub>IN+</sub> to V<sub>OUT1</sub> Offset-Voltage Distribution at -40°C

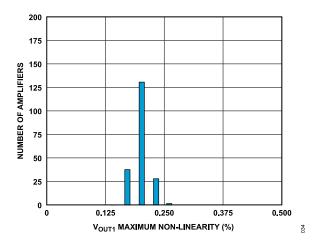

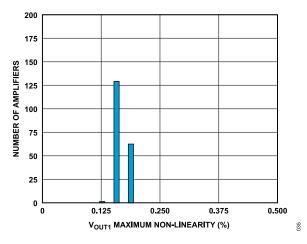

Figure 33. V<sub>OUT1</sub> Maximum Non-Linearity Distribution at 25°C, Maximum Non-Linearity Defined Within V<sub>IN+</sub> Input Range: 1 V to 3.5 V, as an Absolute Value

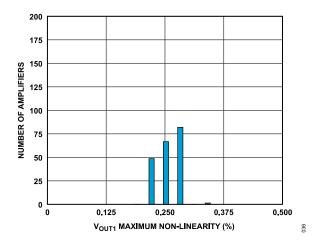

Figure 34. V<sub>OUT1</sub> Maximum Non-Linearity Distribution at 125°C

Figure 35. V<sub>OUT1</sub> Maximum Non-Linearity Distribution at ~40°C, Maximum Non-Linearity Defined Within V<sub>IN+</sub> Input Range: 1 V to 3.5 V, as an Absolute Value

## ADuM3195

## THEORY OF OPERATION

The ADuM3195 is an isolated amplifier (IA) based on Analog Devices, Inc., iCoupler<sup>®</sup> technology. The input side of the IA consists of an operational amplifier with input pins V<sub>IN+</sub> and V<sub>IN-</sub>, and output pin V<sub>OUT2</sub>. The V<sub>IN+</sub>, V<sub>IN-</sub>, and V<sub>OUT2</sub> pins can be used to configure the IA for a wide range of applications such as IA with configurable gain, inverting IA, or as a voltage controller in isolated feedback loops for power supplies. A highly linear pulse width modulation (PWM) compares the output of the operational amplifier to the internal voltage reference V<sub>REF2</sub> and sends the duty cycle (ratio) information to the demodulator through a coreless transformer. On the output side of the IA, the demodulator uses the ratio information and the reference voltage V<sub>REF1</sub> to reconstruct the output voltage, which is then low-pass filtered, buffered, and presented at output pin V<sub>OUT1</sub>. Thus, with the input operational amplifier configured as a voltage follower, the overall signal gain of the IA defaults to 1.

### **APPLICATIONS INFORMATION**

#### **APPLICATION BLOCK DIAGRAM**

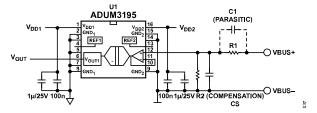

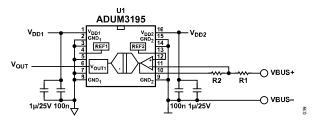

Figure 36 shows a typical application for the ADuM3195 as an isolated voltage monitor. The ADuM3195 offers unique linearity, high common-mode noise immunity, low gain errors, and temperature drift. These features make it a robust and high performance isolated amplifier for industrial applications with high-voltage sensing required. The high-voltage bus is sensed by the R1 voltage divider and the R2 voltage divider. As the input op amp of the IA is configured as a unity-gain amplifier, the voltage on the  $V_{OUT2}$  is equal to the sensed bus voltage multiplied by the voltage-divider ratio. Due to the very high input impedance of the V<sub>IN+</sub> pin, the current through the resistive divider can be kept low without sacrificing accuracy, therefore allowing for a low-power dissipation on the resistors. For very high voltages on the VBUS however, possible pollution on the PCB must also be taken into consideration when planning to design for the low input currents. Also, protective elements (such as diodes or Zener-diodes) in parallel with the R2 voltage divider may negatively affect the accuracy of the voltage divider and must be selected for the lowest reverse leakage currents over the desired temperature range. In such a case, a capacitive protection method as shown in Figure 36 may be a more viable approach.

Figure 36. DC Bus Voltage Monitoring Using ADuM3195

The high-voltage bus is sensed by a voltage divider, which consists of the R1 and the R2. As described in the previous section, the  $V_{OUT1}$  voltage follows the  $V_{IN+}$  with a typical gain of 1.

When monitoring very high bus voltages, the parasitic capacitances of the R1 can impose a risk of overvoltage spikes on the  $V_{IN+}$  during switching events on the VBUS. The recommendation is to connect a compensation capacitor C2 in parallel to the R2. Proper compensation is achieved by selecting C2 such that

$$C2 = R1 \times C1/R2$$

(1)

The value of C2 is not critical but must be selected slightly higher than the calculated value to suppress any overshoot on the V<sub>IN+</sub> during the switching events on the VBUS. For example, if VBUSmax = 1 kV DC and V<sub>OUT</sub> = 4.3 V, the required divider ratio is approximately 1/233, where R1 = 2 M $\Omega$  and R2 = 8.62 k $\Omega$ . With an estimated parasitic capacitance C1 of approximately 10 pF, the compensation capacitance becomes C2 ≥ 2.3 nF.

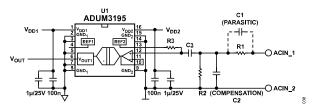

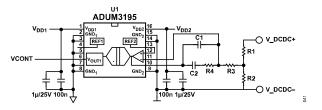

Figure 37 shows an AC voltage monitoring application. In Figure 37, the  $V_{REF2}$  (Pin 13) is used to create a 2.5 V bias voltage for the input op amp. The bias resistor R3 with the coupling capacitor C3, form the AC coupling circuit and high-pass filter to the AC input divider of the circuit. With R3 at least an order of magnitude larger

than R2, a compensation capacitor in parallel with R2 provides a flat, high-frequency response when tuned to R1 × C1 = R2 × C2. The low-frequency roll-off is then defined by R3 and C3.

With the supplies  $V_{DD2}$  and  $V_{DD1}$  = 5 V DC, the acceptable AC input voltage range across R2 is approximately  $V_{R2}$  = 3.6 V (peak-to-peak) or 1.27 V (rms).

Note that in this configuration  $V_{OUT1}$  is also biased to  $V_{REF}$ , therefore an upstream analog-to-digital converter (ADC) can be fed directly without further biasing.

Figure 37. AC Voltage Monitoring Using ADuM3195

On occasions, it may be necessary to invert the monitored bus voltage. In such a case, the input stage of the ADuM3195 can be configured as an inverting amplifier as shown in Figure 38.

Figure 38. ADuM3195 Configured as Inverting Amplifier

With the  $V_{\text{REF2}}$  directly wired to the  $V_{\text{IN+}}$  the  $V_{\text{OUT2}}$  can be calculated as

$$V_{OUT2} = V_{REF2} - R2/R1 \times (VBUS - V_{REF2})$$

<sup>(2)</sup>

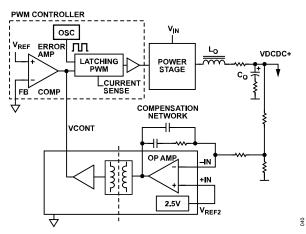

Figure 39 shows another typical application for the ADuM3195 as an isolated error amplifier in a DC to DC power converter.

Figure 39. Isolated DC to DC Converter Application Diagram

### **APPLICATIONS INFORMATION**

The output voltage of the converter is sensed though a voltage divider and then connected to the V<sub>IN</sub>- to compare with the V<sub>REF2</sub> (see Figure 40). The error between the sensed voltage and the V<sub>REF2</sub> is accumulated by the compensation network and transmitted to the voltage on V<sub>OUT1</sub>. V<sub>OUT1</sub> is then used to generate the PWM signals in a PWM controller. The PWM signals drive the power switches in the converter's power stage to regulate the output voltage.

Figure 40. DC to DC Converter V<sub>OUT</sub> Setting

The output of the DC to DC power converter,  $V_{DCDC}$ , can be determined by the following equation, where  $V_{REF2}$  = 2.5 V:

$V_{DCDC} = V_{REF2} \times (R_1 + R_2)/R_2$

#### DESIGN EXAMPLE

For a typical DC bus voltage monitoring application, as shown in Figure 37, the following design procedure can be used:

#### Table 10. Example Design Parameters

| Parameter              | Value     | Comment                              |

|------------------------|-----------|--------------------------------------|

| V <sub>DD2</sub> (min) | 5.0 V DC  | Lowest V <sub>DD2</sub> supply       |

| VBUS (max)             | 1000 V DC | Highest expected bus<br>voltage      |

| I <sub>DIV</sub>       | 500 µA    | Limit power loss in divider to 0.5 W |

Determine the minimum  $V_{\text{DD2}}$  in your system. This in turn determines the maximum  $V_{\text{IN}}$  that can be linearly transmitted across the isolation barrier.

$$V_{IN}$$

(max) =  $V_{DD2}$  (min) – 0.7 V = 5.0 V – 0.7 V = 4.3 V (4)

Determine the ratio 1/K of the voltage divider R1 and R2 for a given maximum of VBUS (max), so that 1/K is about 0 to 10% larger than the VBUS (max)/ $V_{IN}$  (max).

$$1/K = (R1 + R2)/R2 = VBUS (max)/V_{IN} (max),$$

(5)

$$1/K = 1 \dots 1.1 \times (1000 \text{ V}/4.3 \text{ V}) = 232.558 \dots 255.814$$

(6)

For the given  $I_{DIV}$ , the minimum divider input resistance ( $R_{IN}$ ) must meet as follows:

$$R_{IN}$$

= (R1 + R2) > VBUS (max)/I<sub>DIV</sub> = 1 kV DC/500 μA = 2 (7)

Also, the ratio of R1/R2 can be expressed as

$$R1/R2 = (1/K) - 1 = 231.558 \dots 254.814$$

(8)

Thus, when selecting R1 as two 1  $M\Omega$  high-voltage resistors in a series, R2 can be calculated as

R2 = 2 M

$$\Omega$$

× K = 8.6k  $\Omega$  ... 7.82 k $\Omega$  (9)

The divider's output resistance,  $R_{OUT}$ , with the input bias current,  $I_{BIAS}$ , defines the amount of bias error, which adds to the total error of the system. Bias error can be avoided by selecting R1 and R2 so that

$$R_{OUT} = R1 ||R2 < 100 k\Omega,$$

(10)

with above calculated resistors R1 and R2,

$$R_{OUT} = 2 M\Omega ||7.82 k\Omega = 7.8 k\Omega,$$

(11)

which is well below the limit for ROUT.

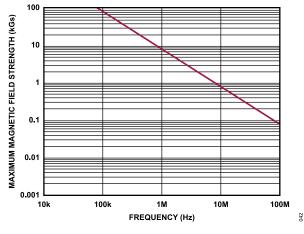

# DC CORRECTNESS AND MAGNETIC FIELD IMMUNITY

The ADuM3195 is highly immune to the external magnetic fields. The limitation on the ADuM3195 magnetic field immunity is set by the condition whereby the induced voltage in the transformer receiving coil is sufficiently large to either falsely set or reset the decoder. The following analysis defines the conditions under which this can occur. The 4.5 V operating condition of the ADuM3195 is examined because it represents the most susceptible mode of operation. The decoder can tolerate up to a 1.6 V noise induced by an external magnetic field. Assuming that there is a 50% margin, the decoder can safely operate with up to a 0.8 V induced noise. The voltage induced across the receiving coil is given by

$$V = (-d\beta/dt) \Sigma \pi \ rn^2, \ n = 1, 2, ..., N$$

(12)

where:

(3)

$\beta$  is the magnetic field strength (Gs). *m* is the radius of the nth turn in the receiving coil (cm). *N* is the number of turns in the receiving coil.

Given the geometry of the receiving coil in the ADuM3195 and an imposed requirement that the induced voltage be, at most, 50% of the 1.6 V threshold at the decoder, a maximum allowable magnetic field is calculated, as shown in Figure 41.

## **APPLICATIONS INFORMATION**

Figure 41. Maximum Allowable External Magnetic Field Strength

For example, at a magnetic field frequency of 1 MHz, the maximum allowable magnetic field of 8 kGs induces a voltage of 0.8 V at the receiving coil. This is approximately 50% of the decoder threshold and does not cause a faulty output transition. The preceding magnetic field strength values correspond to the specific current magnitudes at given distances away from the ADuM3195 transformers. Figure 42 shows these allowable current magnitudes as a function of frequency for selected distances. As shown in Figure 43, the ADuM3195 is immune and can be affected only by extremely large currents operating at a high frequency very close to the component. For the 1 MHz example, a 20 kA current must be placed 5 mm away from the ADuM3195 to affect the operation of the device.

Figure 42. Maximum Allowable Current for Various Current-to-ADuM3195 Spacings

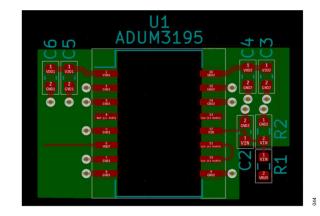

## LAYOUT CONSIDERATIONS

VDD<sub>1</sub> and VDD<sub>2</sub> must be decoupled to their respective GND<sub>1</sub> and GND<sub>2</sub> with capacitors of at least 1  $\mu$ F in parallel with 100 nF. In applications involving fast common-mode transients, ensure that the board coupling across the isolation barrier is minimized. To fully use the specified isolation properties of the ADuM3195, the top and

bottom copper layers of the PCB must not reach underneath the package, but must instead only reach as far as the solder-pad area. Place any decoupling used as close to the supply pins as possible. See Figure 43 for component placement suggestion.

Figure 43. Placement of Decoupling Capacitors and Ground Planes GND1

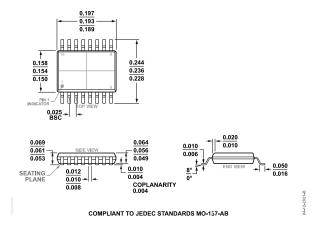

## **OUTLINE DIMENSIONS**

Figure 44. 16-Lead Shrink Small Outline Package [QSOP] (RQ-16) Dimensions shown in inches

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description | Package Option |

|-----------------------|-------------------|---------------------|----------------|

| ADuM3195BRQZ          | -40°C to +125°C   | 16-Lead QSOP        | RQ-16          |

| ADuM3195BRQZ-RL7      | -40°C to +125°C   | 16-Lead QSOP        | RQ-16          |

| ADuM3195WBRQZ         | -40°C to +125°C   | 16-Lead QSOP        | RQ-16          |

| ADuM3195WBRQZ-RL7     | -40°C to +125°C   | 16-Lead QSOP        | RQ-16          |

<sup>1</sup> Z = RoHS Compliant Part.

<sup>2</sup> W = Qualified for Automotive Applications.

#### **EVALUATION BOARD**

| Model <sup>1</sup> | Description               |

|--------------------|---------------------------|

| EVAL-ADUM3195EBZ   | ADuM3195 Evaluation Board |

<sup>1</sup> Z = RoHS Compliant Part.

#### **AUTOMOTIVE PRODUCTS**

The ADuM3195 models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.