# **QSFP-DD 400G Loopback Module**

### **Features**

- Industry's highest rated mating cycles for 2000 and above

- ◆ Built-in surge current mitigation technology

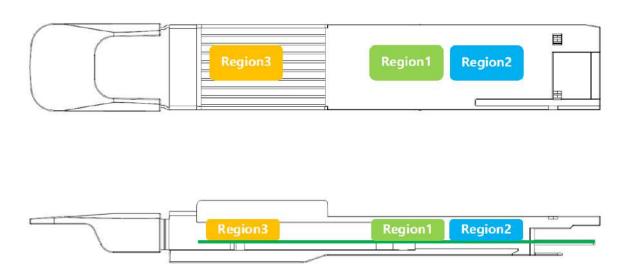

- Adjustable power consumption up to evenly distributed to the 3 regions, each region is individually

- ◆ Operating temperature: -40 °C to 85 °C

- ♦ +3.3V power supply

- ◆ Supports 8\*10G/25G/56G PAM4data rates

- ◆ 2-wire interface for integrated Digital Diagnostic Monitoring

- ◆ Signal integrity performance meets IEEE 802.3ba, 802.3bj , 802.3cd standards respectively

- ◆ Enhanced heat dissipation technology for high power testing

- ◆ Custom EEPROM available

- ◆ A multi-color LED indicator for high/low power modes

- Hot-pluggable

- ◆ RoHS 2.0 compliant

## **Application**

- ◆ QSFP-DD port/system testing

- ◆ Ethernet IEEE 802.3 (Gigabit, 10 Gigabit and 25 Gigabit Ethernet)

- SONET, SDH, GBE, Fiber Channel Support

#### **Standard**

- Common Management Interface Specification, Rev 4.0

- ◆ QSFP-DD/QSFP-DD800/QSFP112 Hardware Specification, Rev 6.01

- ◆ IEEE Std 802.3cd

- ◆ IEEE 802.3bj

- ◆ SFF-8024, SFF Cross Reference to Industry Products, Rev 4.7

## **Description**

Designed and engineered to accommodate customers high usage 2000 cycles at -40°C to 85°C, the loopback module series are the most reliable products in the market to enable the quickest customers systems production and deployment. Software defined multiple power consumption may emulate the optical module power, and the embedded insertion loss characteristics emulates the real-world cabling for

200G/400G Ethernet/Infiniband/FC. The built-in surge current mitigation technology mitigates the DUT risks from being damaged. The broad operating temperature range accommodates the enterprise, datacom and telecom applications. The loopback module may be used for ports testing, field deployment testing and equipment troubleshooting.

## **Specification**

| Absolute Maximum Ratings      |        |      |       |      |  |  |  |  |  |

|-------------------------------|--------|------|-------|------|--|--|--|--|--|

| Parameter                     | Symbol | Min  | Max   | Unit |  |  |  |  |  |

| Storage Temperature           | Ts     | -40  | +85   | °C   |  |  |  |  |  |

| Ambient Operating Temperature | Та     | -40  | +85   | °C   |  |  |  |  |  |

| Storage Relative Humidity     | RHs    | 0    | 95    | %    |  |  |  |  |  |

| Operating Relative Humidity   | RHo    | 0    | 85    | %    |  |  |  |  |  |

| Power Supply Voltage          | Vcc    | 2.97 | +3.63 | V    |  |  |  |  |  |

| Recommended Operating Conditions |          |      |         |      |            |  |  |  |

|----------------------------------|----------|------|---------|------|------------|--|--|--|

| Parameter                        | Symbol   | Min  | Typical | Max  | Unit       |  |  |  |

| Ambient Operating Temperature    | Ta       | -40  | -       | +85  | $^{\circ}$ |  |  |  |

| Power Supply Voltage             | $V_{CC}$ | 2.97 | 3.3     | 3.63 | V          |  |  |  |

| Data Rate                        | BRate    | 0.1  | -       | 400  | Gbps       |  |  |  |

| Durability Cycles                |          | -    | 2000    | 2250 | Times      |  |  |  |

|                             | High Speed Characteristics |                         |         |       |      |                                                   |  |  |  |

|-----------------------------|----------------------------|-------------------------|---------|-------|------|---------------------------------------------------|--|--|--|

| Parameter                   | Symbol                     | Min                     | Typical | Max   | Unit | Notes                                             |  |  |  |

| Input/Output<br>Impedance   | Zd                         | 90                      | 100     | 110   | Ohm  | Differential<br>Impedance                         |  |  |  |

| Return Loss                 | SDD11/22                   | IEEE 802.3bj CL92.10.3. |         |       |      | At Nyquist<br>Frequency                           |  |  |  |

| Insertion Loss              | SDD21                      | 0.845                   | -       | 6.615 | dB   | Exclude the<br>MCB insertion<br>loss, at<br>13GHz |  |  |  |

| Insertion Loss<br>Deviation | ILD                        | -1                      |         | 1     |      | At Nyquist<br>Frequency                           |  |  |  |

| Skew between lanes          | SKEW                       |                         |         | 200   | ps   |                                                   |  |  |  |

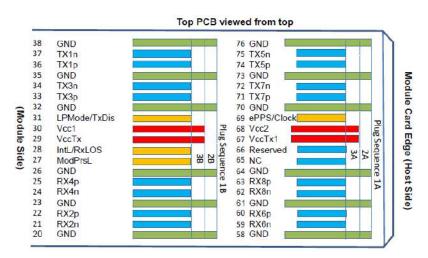

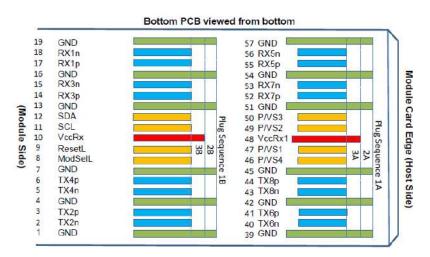

### **Pin Definition**

**Table 1- Pad Function Definition**

| Б.  |              |              | ble 1- Pad Function Definition      | T DI              |          |

|-----|--------------|--------------|-------------------------------------|-------------------|----------|

| Pad | Logic        | Symbol       | Description                         | Plug<br>Sequence⁴ | Notes    |

| 1   |              | GND          | Ground                              | 1B                | 1        |

| 2   | CML-I        | Tx2n         | Transmitter Inverted Data Input     | 3B                | <u> </u> |

| 3   | CML-I        | Tx2p         | Transmitter Non-Inverted Data Input | 3B                |          |

| 4   | OIIIE I      | GND          | Ground                              | 1B                | 1        |

| 5   | CML-I        | Tx4n         | Transmitter Inverted Data Input     | 3B                | '        |

| 6   | CML-I        | Tx4p         | Transmitter Non-Inverted Data Input | 3B                |          |

| 7   | OIVIL-1      | GND          | Ground                              | 1B                | 1        |

| 8   | LVTTL-I      | ModSelL      | Module Select                       | 3B                | '        |

| 9   | LVTTL-I      | ResetL       | Module Reset                        | 3B                |          |

| 10  | LVIIL-I      | VccRx        | +3.3V Power Supply Receiver         | 2B                | 2        |

| 11  | LVCMOS-I/O   | SCL          | TWI serial interface clock          | 3B                |          |

| 12  | LVCMOS-I/O   | SDA          | TWI serial interface data           | 3B                |          |

| 13  | LVCIVIOS-I/O | GND          | Ground                              | 1B                | 1        |

| 14  | CML-O        | Rx3p         | Receiver Non-Inverted Data Output   | 3B                | 1        |

| 15  | CML-O        | Rx3n         | Receiver Inverted Data Output       | 3B                |          |

| 16  | CIVIL-U      | GND          | Ground Ground                       | 1B                | 1        |

| 17  | CML-O        |              |                                     | 3B                | 1        |

| 18  | CML-O        | Rx1p         | Receiver Non-Inverted Data Output   | 3B                |          |

|     | CIVIL-U      | Rx1n         | Receiver Inverted Data Output       |                   | 4        |

| 19  |              | GND          | Ground                              | 1B                | 1        |

| 20  | 0141.0       | GND          | Ground                              | 1B                | 1        |

| 21  | CML-O        | Rx2n         | Receiver Inverted Data Output       | 3B                |          |

| 22  | CML-O        | Rx2p         | Receiver Non-Inverted Data Output   | 3B                | 4        |

| 23  | OMI O        | GND          | Ground                              | 1B                | 1        |

| 24  | CML-O        | Rx4n         | Receiver Inverted Data Output       | 3B                |          |

| 25  | CML-O        | Rx4p         | Receiver Non-Inverted Data Output   | 3B                |          |

| 26  | LV/TTL O     | GND          | Ground                              | 1B                | 1        |

| 27  | LVTTL-0      | ModPrsL      | Module Present                      | 3B                |          |

| 28  | LVTTL-O      | IntL/RxLOS   | Interrupt/optional RxLOS            | 3B                |          |

| 29  |              | VccTx        | +3.3V Power supply transmitter      | 2B                | 2        |

| 30  |              | Vcc1         | +3.3V Power supply                  | 2B                | 2        |

| 31  | LVTTL-I      | LPMode/TxDis | Low Power mode/optional TX Disable  | 3B                |          |

| 32  |              | GND          | Ground                              | 1B                | 1        |

| 33  | CML-I        | Tx3p         | Transmitter Non-Inverted Data Input | 3B                |          |

| 34  | CML-I        | Tx3n         | Transmitter Inverted Data Input     | 3B                |          |

| 35  |              | GND          | Ground                              | 1B                | 1        |

| 36  | CML-I        | Tx1p         | Transmitter Non-Inverted Data Input | 3B                |          |

| 37  | CML-I        | Tx1n         | Transmitter Inverted Data Input     | 3B                |          |

| 38  |              | GND          | Ground                              | 1B                | 1        |

| 39  |              | GND          | Ground                              | 1A                | 1        |

| 40  | CML-I        | Tx6n         | Transmitter Inverted Data Input     | 3A                |          |

| 41  | CML-I        | Tx6p         | Transmitter Non-Inverted Data Input | 3A                |          |

| 42  |              | GND          | Ground                              | 1A                | 1        |

| 43  | CML-I        | Tx8n         | Transmitter Inverted Data Input     | 3A                |          |

| 44  | CML-I        | Tx8p         | Transmitter Non-Inverted Data Input | 3A                |          |

| 45  |              | GND          | Ground                              | 1A                | 1        |

| Pad  | Logic               | Symbol         | Description                                         | Plug<br>Sequence <sup>4</sup> | Notes |

|------|---------------------|----------------|-----------------------------------------------------|-------------------------------|-------|

| 46   | LVCMOS/CML-I        | P/VS4          | Programmable/Module Vendor Specific 4               | 3A                            | 5     |

| 47   | LVCMOS/CML-I        | P/VS1          | Programmable/Module Vendor Specific 1               | 3A                            | 5     |

| 48   |                     | VccRx1         | 3.3V Power Supply                                   | 2A                            | 2     |

| 49   | LVCMOS/CML-O        | P/VS2          | Programmable/Module Vendor Specific 2               | 3A                            | 5     |

| 50   | LVCMOS/CML-O        | P/VS3          | Programmable/Module Vendor Specific 3               | 3A                            | 5     |

| 51   |                     | GND            | Ground                                              | 1A                            | 1     |

| 52   | CML-O               | Rx7p           | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 53   | CML-O               | Rx7n           | Receiver Inverted Data Output                       | 3A                            |       |

| 54   |                     | GND            | Ground                                              | 1A                            | 1     |

| 55   | CML-O               | Rx5p           | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 56   | CML-O               | Rx5n           | Receiver Inverted Data Output                       | 3A                            |       |

| 57   |                     | GND            | Ground                                              | 1A                            | 1     |

| 58   |                     | GND            | Ground                                              | 1A                            | 1     |

| 59   | CML-O               | Rx6n           | Receiver Inverted Data Output                       | 3A                            |       |

| 60   | CML-O               | Rx6p           | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 61   |                     | GND            | Ground                                              | 1A                            | 1     |

| 62   | CML-O               | Rx8n           | Receiver Inverted Data Output                       | 3A                            |       |

| 63   | CML-O               | Rx8p           | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 64   |                     | GND            | Ground                                              | 1A                            | 1     |

| 65   |                     | NC             | No Connect                                          | 3A                            | 3     |

| 66   |                     | Reserved       | For future use                                      | 3A                            | 3     |

| 67   |                     | VccTx1         | 3.3V Power Supply                                   | 2A                            | 2     |

| 68   |                     | Vcc2           | 3.3V Power Supply                                   | 2A                            | 2     |

| 69   | LVCMOS-I            | ePPS/Clock     | 1PPS PTP clock or reference clock input             | 3A                            | 6     |

| 70   |                     | GND            | Ground                                              | 1A                            | 1     |

| 71   | CML-I               | Tx7p           | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 72   | CML-I               | Tx7n           | Transmitter Inverted Data Input                     | 3A                            |       |

| 73   |                     | GND            | Ground                                              | 1A                            | 1     |

| 74   | CML-I               | Tx5p           | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 75   | CML-I               | Tx5n           | Transmitter Inverted Data Input                     | 3A                            |       |

| 76   |                     | GND            | Ground                                              | 1A                            | 1     |

| Noto | 1: OCED DD upon con | mon ground (Ch | VD) for all cignals and cupply (nower). All are com | man within the C              | OED   |

Note 1: QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. Each connector Gnd contact is rated for a steady state current of 500 mA

Note 2: VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Supply requirements defined for the host side of the Host Card Edge Connector are listed in Table 13. For power classes 4 and above the module differential loading of input voltage pads must not result in exceeding contact current limits. Each connector Vcc contact is rated for a steady state current of 1500 mA.

Note 3: Reserved pad recommended to be terminated with 10 k $\Omega$  to ground on the host. Pad 65 (No Connect) Shall be left unconnected within the module, optionally pad 65 may get terminated with 10 k $\Omega$  to ground on the host.

Note 4: Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (See Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A and 1B will then occur simultaneously, followed by 2A and 2B, followed by 3A and 3B.

Note 5: Full definitions of the P/VSx signals currently under development. For module designs using programmable/vendor specific inputs P/VS1 and P/VS4 signals it is recommended each to be terminated in the module with 10 k $\Omega$ . For host designs using programmable/vendor specific outputs P/VS2 and P/VS3 signals it is recommended each to be terminated on the host with 10 k $\Omega$ .

Note 6: for host not implementing ePPS/Clock, it is not necessary to parallel terminate the ePPS/Clock signal to ground on the host. ePPS/Clock already has parallel termination in the module see 4.2.6.

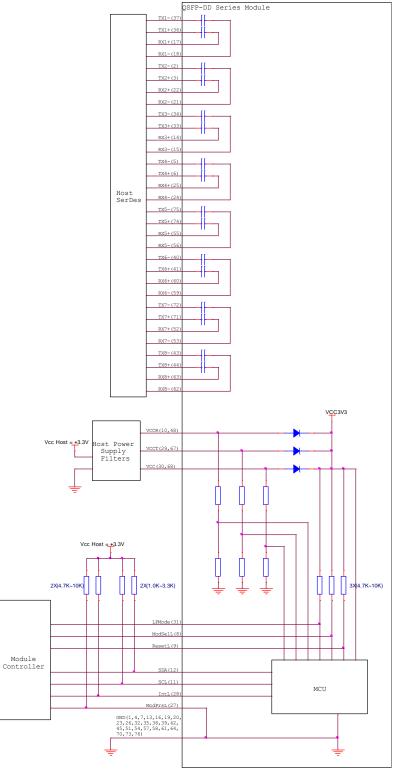

## **Typical application Circuit**

The 16 lanes are connected as following with match polarity:

- TX1 and RX1

- TX2 and RX2

- TX3 and RX3

- TX4 and RX4

- TX5 and RX5

- TX6 and RX6

- TX7 and RX7

- TX8 and RX8

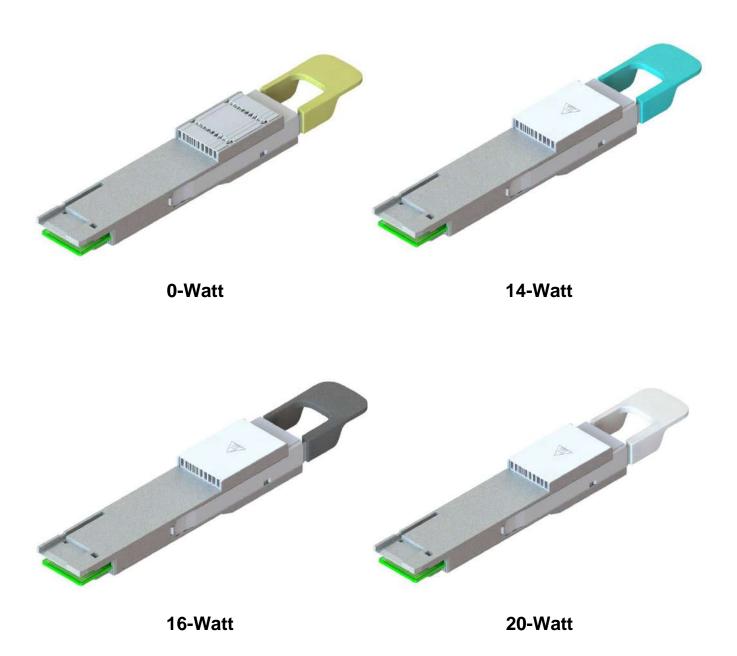

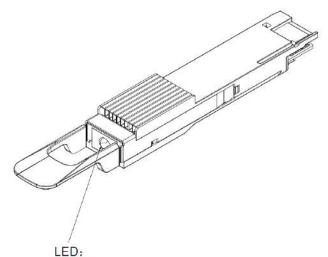

### **Status LED**

A multi-color LED must be viewed from the front of the module in order to signify high/low power modes, as well as interrupts. Low-power mode is defined as device address A0h.00.200.7:4 = 0000b or The InitMode is High.

· Solid green: low-power mode

Solid red: high-power mode

· Blinking green: low-power mode with any of the interrupt flag is set

· Blinking red: high-power mode with any of the interrupt flag is set

### **I2C** interface

Upon the completion of the MgmtInit state, the I2C interface on the module must support Fastmode as defined in the UM10204, I2 C-bus specification and user manual, Rev. 6-4 April 2014 in order to handle the SCL clock frequency between 0kHz and 400KHz. In addition, the module may only clock stretching the SCL less than 100 µsec in any frequency.

### **QSFP-DD** Identification:

Table 1: The module must provide the ID in the following registers

| Page | Address | Size           | Name                                         | Description                                                  |  |

|------|---------|----------------|----------------------------------------------|--------------------------------------------------------------|--|

|      | 0       | 1              | Identifier                                   | 18h: Identifier Type of QSFP-DD                              |  |

|      | 3       | 1              | Module state                                 | b0000_001x: Module LowPwr state                              |  |

|      | 85      | 1              | Module Type Encodings                        | 03h: Passive Cu                                              |  |

|      | 86      | 1              | ApSelCode 1:<br>Host Electrical Interface ID | 11h: 400GAUI-8 C2M                                           |  |

| N/A  | 87      | 1              | ApSelCode 1: Module<br>Media Interface ID    | BFh: Passive Loopback Module                                 |  |

|      | 88      | 1              | ApSel Code 1: Host &<br>Media Lane Count     | 80h: 8 host lanes and 0 media lanes                          |  |

|      | 89      | 1              | ApSel Code 1: Host Lane Assignment Options   | 01h: Begin on Host Lane 1                                    |  |

|      | 128     | 8 1 Identifier |                                              | 18h: Identifier Type of QSFP-DD                              |  |

|      | 129-144 | 16             | Vendor name                                  | Vendor name (ASCII)                                          |  |

|      | 148-163 | 16             | Vendor PN                                    | Part number (ASCII)                                          |  |

| 00h  | 164-165 | 2              | Vendor rev                                   | Revision (ASCII)                                             |  |

|      | 166-181 | 16             | Vendor SN                                    | Vendor Serial Number (ASCII)                                 |  |

|      | 200 1   |                | Maximum Power identifier                     | bxxxx_001x: 14-Watt loopback<br>bxxxx_00xx: 16-Watt loopback |  |

|  |     |   |           | bxxxx_10xx: 20-Watt loopback        |

|--|-----|---|-----------|-------------------------------------|

|  |     |   |           | bxxxx_11xx: 0-Watt loopback         |

|  |     |   |           | Refer to address 201                |

|  | 201 | 1 |           | 0x50 (20W/0.25W = 80)               |

|  |     |   |           | 0x40 (16W/0.25W = 64)               |

|  |     |   | Max Power | 0x38 (14W/0.25W = 56)               |

|  |     |   |           | 0x00 (0W,Without Power burner. Only |

|  |     |   |           | EEPROM)                             |

## **Case temperature monitor**

The case temperature is presented as a 16-bit signed two's complement value in increment of 1/256°C at I2C registers 14(MSB) and 15(LSB) for the top case .

**Table 2: Temperature DOM**

| Page | Address | Size | Name                   | Description                               |

|------|---------|------|------------------------|-------------------------------------------|

|      | 14      | 1    | Module Monitor 1:      |                                           |

| N/A  | 14      | ı    | Temperature 1 MSB      | Internally measured temperature, top case |

| IN/A | 15      | 1    | Module Monitor 1:      | internally measured temperature, top case |

|      | 13      | I    | Temperature 1 LSB      |                                           |

| Page | Address | Bits | Name                   | Description                               |

|      |         | 3    | TempMonLowWamingFlag   | Latched Flag for low temperature warning  |

| N/A  | 0       | 2    | TempMonHighWarningFlag | Latched Flag for high temperature warning |

| IN/A | 9       | 1    | TempMonLowAlarmFlag    | Latched Flag for low temperature alarm    |

|      |         | 0    | TempMonHighAlarmFlag   | Latched Flag for high temperature alarm   |

## Power rail voltage monitor

The 3 VCC power rails, VccRx, VccTx and Vcc are monitored individually.

**Table 3: VCC voltage DOM**

| Page | Address | Size | Name                | Description                            |

|------|---------|------|---------------------|----------------------------------------|

|      | 16      | 1    | Module Monitor 2:   | Internally measured 3.3 volt input     |

|      | 10      | •    | Supply 3.3-volt MSB | supply voltage VccRx* gold-fingers: in |

|      | 17      | 1    | Module Monitor 2:   | 100µV increments                       |

| N/A  |         |      | Supply 3.3-volt LSB | 100μ v increments                      |

|      | 18      | 1    | Module Monitor 3:   | Internally measured 3.3 volt input     |

|      | 10      | '    | Supply 3.3-volt MSB | supply voltage VccTx* gold-fingers: in |

|      | 19      | 1    | Module Monitor 3:   | 100μV increments                       |

|      |         |      | Supply 3.3-volt LSB                  |                                                       |

|------|---------|------|--------------------------------------|-------------------------------------------------------|

|      | 22      | 1    | Module Monitor 5: TEC current MSB    | Internally measured 3.3 volt input                    |

|      | 23      |      | Module Monitor 5:<br>TEC current MSB | supply voltage Vcc* gold-fingers: in 100µV increments |

| Page | Address | Bits | Name                                 | Description                                           |

|      |         | 7    | VccRx MonLowWarningFlag              | Latched Flag for low supply VccRx voltage warning     |

|      | 9       | 6    | VccRx MonHighWarningFlag             | Latched Flag for high supply VccRx voltage warning    |

|      | מ       | 5    | VccRx MonLowAlarmFlag                | Latched Flag for low supply VccRx voltage alarm       |

|      |         | 4    | VccRx MonHighAlarmFlag               | Latched Flag for high supply VccRx voltage alarm      |

|      |         | 3    | VccTx MonLowWarningFlag              | Latched Flag for low supply VccTx voltage warning     |

| N/A  | 40      | 2    | VccTx MonHighWarningFlag             | Latched Flag for high supply VccTx voltage warning    |

| IN/A | 10      | 1    | VccTx MonLowAlarmFlag                | Latched Flag for low supply VccTx voltage alarm       |

|      |         | 0    | VccTx MonHighAlarmFlag               | Latched Flag for high supply VccTx voltage alarm      |

|      |         | 3    | Vcc MonLowWarningFlag                | Latched Flag for low supply Vcc voltage warning       |

|      | 11      | 2    | Vcc MonHighWarningFlag               | Latched Flag for high supply Vcc voltage warning      |

|      | 11      | 1    | Vcc MonLowAlarmFlag                  | Latched Flag for low supply Vcc voltage alarm         |

|      |         | 0    | Vcc MonHighAlarmFlag                 | Latched Flag for high supply Vcc voltage alarm        |

## **Reset requirement**

There should be 3 different type of reset in the module, power-up-reset, hard-reset and softreset. All the 3 resets should cause the module to consume default power: less than or equal to 1.5W

#### Power-up-reset

The power-up-reset should cause all the active components, including the microcontroller, in the module reset to default state and then start the normal operation. It should also reset the power burner in the module to consume the default power, 1.5W.

### Hard-reset(ResetL)

The hard-reset should cause the microcontroller to reset, and then reset all the other active components and reset the power burner to consume the default power, 1.5W. Afterward, the microcontroller will start the normal operation.

#### Soft-reset

The soft-reset should cause the microcontroller to reset, and then reset all the other active components and reset the power burner to consume the default power, 1.5W. Afterward, the microcontroller will start the normal operation. The soft-reset is set by host through the I2C register 26 bit 3.

Table 4: Soft-reset register

| Page | Address | Bits | Name           | Description    | Туре           |

|------|---------|------|----------------|----------------|----------------|

| N/A  | 26      | 3    | Software Reset | Software reset | RW, Self-Clear |

### Programmable power consumption/burner

During power-up of the module, the power burner in the module should burn maximum 1.5W power as default. Afterward, host can set the module to consume more power through a I2C register 200.

Table 5: power burner registers

| Page | Address | bits | Name       | Description                                | Туре |

|------|---------|------|------------|--------------------------------------------|------|

|      |         |      |            | 000b: Power consumption: 1.5W (default)    | RW   |

|      |         |      |            | 001b: Power consumption: 3.5W              |      |

|      |         |      |            | 010b: Power consumption: 5.0W              |      |

|      |         |      |            | 011b: Power consumption: 7.0W              |      |

|      |         |      |            | 100b: Power consumption: 10.0W             |      |

|      |         |      | Module     | 101b: Power consumption: 12.0W             |      |

|      |         | 7-5  | Card Power | 110b: Power consumption: 14.0W             |      |

|      |         | 7-3  | Class      | 111b: Power consumption: 16.0W             |      |

|      |         |      |            | The tolerance of power consumption must    |      |

| 00h  | 200     |      |            | meet the following criteria                |      |

| OON  | 200     |      |            | +/-5% @ VCC = 3.3V +/-2%                   |      |

|      |         |      |            | +/-11% @ VCC = 3.3V +/-5%                  |      |

|      |         |      |            | +/-20% @ VCC = 3.3v +/-10%                 |      |

|      |         |      | Reserved / |                                            | RO   |

|      |         |      | Maximum    | 0b: Power consumption is set by the Module |      |

|      |         | 4    | Module     | Card Power Class register (default)        |      |

|      |         |      | Card Power | 1b: Power consumption: 20.0W               |      |

|      |         |      | Class      |                                            |      |

|      |         |      | Maximum    | bxxxx_001x: 14-Watt loopback               | RO   |

|      |         | 3-0  | Power      | bxxxx_00xx: 16-Watt loopback               |      |

|      |         |      | Identifier | bxxxx_10xx: 20-Watt loopback               |      |

|  |  | bxxxx_11xx: 0-Watt loopback |  |

|--|--|-----------------------------|--|

|  |  | Refer to address 201        |  |

|  |  | (or Customizable power)     |  |

### **Power distribution**

The power burner will be placed on the top side of paddle PCB with all the heat be dissipated at the top of the case. The power burner is separated into 3 regions (0W loopback without burner):

**Table 6: Burner Power distribution registers**

| Page | Address | Bits | Value | Power consumption |          |          |          |

|------|---------|------|-------|-------------------|----------|----------|----------|

| Page |         |      |       | Module            | Region 1 | Region 2 | Region 3 |

|      | 200     | 7-4  | 0000b | 1.5W              | 1.5W     | OW       | 0W       |

|      |         |      | 0010b | 3.5W              | 3.5W     | OW       | 0W       |

|      |         |      | 0100b | 5.0W              | 5.0W     | OW       | 0W       |

|      |         |      | 0110b | 7.0W              | 5.0W     | 2.0W     | 0W       |

| 00h  |         |      | 1000b | 10.0W             | 5.0W     | 5.0W     | 0W       |

|      |         |      | 1010b | 12.0W             | 5.0W     | 7.0W     | 0W       |

|      |         |      | 1100b | 14.0W             | 5.0W     | 9.0W     | 0W       |

|      |         |      | 1110b | 16.0W             | 5.0W     | 11.0W    | 0W       |

|      |         |      | xxx1b | 20.0W             | 5.0W     | 11.0W    | 4.0W     |

**Table 7: Low-Speed Signal status registers**

| Page | Address | bits                      | Name                                                         | Description                                                 | Type |

|------|---------|---------------------------|--------------------------------------------------------------|-------------------------------------------------------------|------|

| FFh  | 225     | 225 signal status 1b: log | ModSelL                                                      | 0b: logical 0, V <sub>ModSelL</sub> < V <sub>il</sub> (max) | RO   |

|      |         |                           | signal status                                                | 1b: logical 1, V <sub>ModSelL</sub> > V <sub>ih</sub> (min) |      |

|      |         |                           | 0b: logical 0, V <sub>InitMode</sub> < V <sub>il</sub> (max) | RO                                                          |      |

| signa | al status | <sub>h</sub> (min) |

|-------|-----------|--------------------|

|-------|-----------|--------------------|

Table 8: Low-Speed Signal state transaction registers

| Page | Address | bits | Name       | Description                                      | Type |

|------|---------|------|------------|--------------------------------------------------|------|

|      | 225 -   | 5    |            | Read 0b: No edge detected                        | RW   |

|      |         |      | ModSelL    | Read 1b: Either rising or falling edges detected |      |

|      |         |      | transition | Write 0b: No effect                              |      |

| FFh  |         |      |            | Write 1b: Clear the register                     |      |

| FFN  |         | 4    |            | Read 0b: No edge detected                        | RW   |

|      |         |      | InitMode   | Read 1b: Either rising or falling edges detected |      |

|      |         |      | transition | Write 0b: No effect                              |      |

|      |         |      |            | Write 1b: Clear the register                     |      |

#### ModSelL

The ModSelL is Low, the module responds to TWI serial communication commands.

The ModSelL is High, the module shall not respond to or acknowledge any TWI interface communication.

#### InitMode

The InitMode is Low, the power burner in the module to consume the setting power.

The InitMode is High, the module enter low power mode.

#### **ModPrsL**

The ModPrsL is pulled towards ground in the module.

#### IntL

The IntL signal is asserted Low with any of Alarm and Warning flag is set and deasserted High after all of Alarm and Warning flags are read.

## Contact pads insertion requirement and module reliability

The contacts pads on the paddle card is wished to handle 2000 physical insertions while maintain the lane insertion loss at the end of the 2000th physical insertion. The value of guaranteed maximum insertion/temperature cycle is saved in I2C registers in upper page 0Xff

Table 9: Contact pads insertion cycle registers

| Page | Address | Size | Name                  | Description                         | Type |

|------|---------|------|-----------------------|-------------------------------------|------|

| FFh  | 252     | 1    | Guaranteed maximum    | Guaranteed maximum                  | RO   |

|      |         | I    | insertion/temperature | insertion/temperature cycle in hex. |      |

|     |   | cycle, MSB                                          | The goal is 2000 (07D0h) |    |

|-----|---|-----------------------------------------------------|--------------------------|----|

| 253 | 1 | Guaranteed maximum insertion/temperature cycle, LSB | insertions.              | RO |

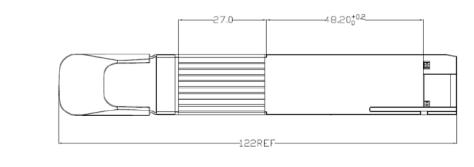

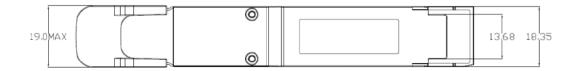

## **Package Outline**

Dimensions are in millimeters. (Unit: mm)

Solid green: low-power mode Solid red: high-power mode

Blinking green: low-power mode with any of the interrupt flag is set Blinking red: high-power mode with any of the interrupt flag is set