| MDT1010D1IH-MIPI            | 1024 x 600 | MIPI Interface | TFT Module |  |  |  |  |

|-----------------------------|------------|----------------|------------|--|--|--|--|

| Specification               |            |                |            |  |  |  |  |

| Version: 1 Date: 27/08/2021 |            |                |            |  |  |  |  |

|                             |            | Revision       |            |  |  |  |  |

| 1 2                         | 6/08/2021  | First issue    |            |  |  |  |  |

|                             |            |                |            |  |  |  |  |

|                             |            |                |            |  |  |  |  |

|                             |            |                |            |  |  |  |  |

| Display F             | eatures                  |              |                  |

|-----------------------|--------------------------|--------------|------------------|

| Display Size          | 10.10"                   |              |                  |

| Resolution            | 1024 x 600               |              |                  |

| Orientation           | Landscape                |              |                  |

| Appearance            | RGB                      |              |                  |

| Logic Voltage         | 1.8V                     |              | <b>oHS</b>       |

| Interface             | MIPI                     |              |                  |

| Brightness            | 1100 cd/m <sup>2</sup>   |              | moliont          |

| Touchscreen           | SPLA                     |              | mpnant           |

| Module Size           | 235.00 x 143.00 x 5.05mm |              | 1,51             |

| Operating Temperature | -20°C ~ +70°C            |              |                  |

| Pinout                | 30 way FFC               | Box Quantity | Weight / Display |

| Pitch                 | 0.5mm                    |              |                  |

\* - For full design functionality, please use this **ACTURE** • **SUPPLY** specification in conjunction with the EK79007AD3 + EK73217BCGA specification. (Provided Separately)

| Disp        | Display Accessories                                     |  |  |  |  |  |  |

|-------------|---------------------------------------------------------|--|--|--|--|--|--|

| Part Number | Description                                             |  |  |  |  |  |  |

| MPBV7       | 30-way FFC 0.5mm,<br>crimp-wire conect.<br>SHDR-30V-S-B |  |  |  |  |  |  |

|             |                                                         |  |  |  |  |  |  |

|             |                                                         |  |  |  |  |  |  |

| Optional Variants |         |  |  |  |  |  |

|-------------------|---------|--|--|--|--|--|

| Appearances       | Voltage |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

|                   |         |  |  |  |  |  |

Page 1 of 29

## Summary

TFT 10.1" is a color active matrix thin film transistor (TFT) liquid crystal display without polarizer. This model is composed of amorphous silicon TFT as a switching device. This TFT LCD has a 10.1" wide (16:9) diagonally measured active display area with WVGA (1024 horizontal by 600 vertical pixel) resolution. Each pixel is divided into Red, Green, Blue dots which are arranged in vertical stripes.

## **General Specifications**

- Size: 10.1 inch

- Dot Matrix: 1024 RGB X 600 dots

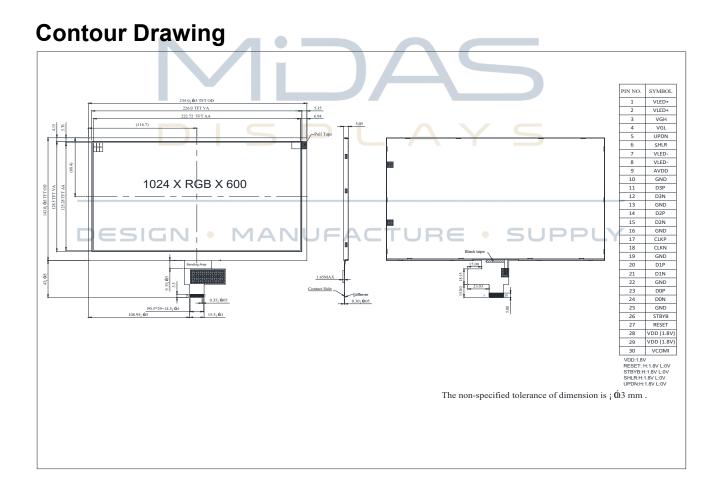

- Module dimension: 235(W) x143(H) x 5.05(D) mm

- Active area: 222.72 (H) x 125.28(V) mm

- Pixel pitch: 0.2175(W) x 0.2088(H) mm

- LCD type: TFT, Normally Black, Transmissive

- TFT Interface: 4-Lanes MIPIANUFACTURE . SUPPLY

- Driver IC: EK79007AD3 + EK73217BCGA or equivalent

- Viewing Angle: 85/85/85/85

- Aspect Ratio: 16:9

- Backlight Type: LED,Normally White

- With /Without TP: Without TP

- Surface: Anti-Glare

\*Color tone slight changed by temperature and driving voltage.

# Interface

## 1. TFT LCD MODULE

| Pin No. | Symbol | Description                                                                                                                                                                                                                                                           |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VLED+  | LED Anode                                                                                                                                                                                                                                                             |

| 2       | VLED+  | LED Anode                                                                                                                                                                                                                                                             |

| 3       | VGH    | Positive power for TFT                                                                                                                                                                                                                                                |

| 4       | VGL    | Negative power for TFT                                                                                                                                                                                                                                                |

| 5       | UPDN   | Gate up or down scan control.<br>UPDN = "L", STV2 output vertical start pulse and UD pin output<br>logical "L" to Gate driver. (default)<br>UPDN = "H", STV1 output vertical start pulse and UD pin output<br>logical "H" to Gate driver                              |

| 6       | SHLR   | Source right or left sequence control.<br>SHLR = "L", shift left: last data = $S1 \leftarrow S2 \leftarrow S3$ $\leftarrow S1536$ = first data.<br>SHLR = "H", shift right: first data = $S1 \rightarrow S2 \rightarrow S3$ $\rightarrow S1536$ = last data.(default) |

| 7       | VLED-  | LED Cathode                                                                                                                                                                                                                                                           |

| 8       | VLED-  | LED Cathode                                                                                                                                                                                                                                                           |

| 9       | AVDD   | Analog power                                                                                                                                                                                                                                                          |

| 10      | GND    | Digital ground                                                                                                                                                                                                                                                        |

| 11      | D3P    | MIPI data input.                                                                                                                                                                                                                                                      |

| 12      | D3N    | MIPI data input.                                                                                                                                                                                                                                                      |

| 13      |        |                                                                                                                                                                                                                                                                       |

| 14      | D2P    | MIPI data input.                                                                                                                                                                                                                                                      |

| 15      | D2N    | MIPI data input.                                                                                                                                                                                                                                                      |

| 16      | GND    | Digital ground                                                                                                                                                                                                                                                        |

| 17      | CLKP   | MIPI clock input                                                                                                                                                                                                                                                      |

| 18      | CLKN   | MIPI clock input                                                                                                                                                                                                                                                      |

| 19      | GND    | Digital ground                                                                                                                                                                                                                                                        |

| 20      | D1P    | MIPI data input.                                                                                                                                                                                                                                                      |

| 21      | D1N    | MIPI data input.                                                                                                                                                                                                                                                      |

| 22      | GND    | Digital ground                                                                                                                                                                                                                                                        |

| 23      | D0P    | MIPI data input.                                                                                                                                                                                                                                                      |

| 24      | D0N    | MIPI data input.                                                                                                                                                                                                                                                      |

| 25      | GND    | Digital ground                                                                                                                                                                                                                                                        |

| 26      | STBYB  | Standby mode.                                                                                                                                                                                                                                                         |

|    |            | STBYB = "H",normal operation(default)<br>STBYB = "L", timing controller, source driver will turn off, all output<br>are GND. |

|----|------------|------------------------------------------------------------------------------------------------------------------------------|

| 27 | RESET      | Global reset pin. Active Low to enter Reset State. Normally pull high. Connecting with an RC reset circuit for stability.    |

| 28 | VDD (1.8V) | Digital power                                                                                                                |

| 29 | VDD (1.8V) | Digital power                                                                                                                |

| 30 | VCOMI      | Common voltage                                                                                                               |

# **Absolute Maximum Ratings**

| ltem                  | Symbol | Min | Тур | Мах | Unit |

|-----------------------|--------|-----|-----|-----|------|

| Operating Temperature | TOP    | -20 |     | +70 | °C   |

| Storage Temperature   | TST    | -30 | _   | +80 | °C   |

Note: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above

## **Electrical Characteristics**

#### 1. Typical Operation Conditions (At Ta = 25 °C,)

| Item                                 | Symbol | Min.  | Тур.  | Max. | Unit | Note  |

|--------------------------------------|--------|-------|-------|------|------|-------|

| Digital Power Supply Voltage For LCD | VDD    | 1.71  | 1.8   | 1.89 | V    | Note1 |

| Analog Power Supply Voltage          | AVDD   | 9.89  | 10.2  | 10.5 | V    | -     |

| Gate On Power Supply Voltage         | VGH    | 19.4  | 20.0  | 20.6 | V    | -     |

| Gate Off Power Supply Voltage        | VGL    | -10.3 | -10.0 | -9.7 | V    | -     |

| Common Power Supply Voltage          | VCOMI  | 4.0   | 4.3   | 4.6  | V    | Note2 |

Note1:VDD setting should match the signals output voltage (refer to Note 3) of customer's system board. **SUPPLY** Note 2.Please adjust VCOMI to make the flicker level be minimum. Note 3:RESET,STBYB,U/D,L/R,SELB

#### 2. Current Consumption

| ltom               | Symbol           |      | Values |      | l In:t | Domork       |  |

|--------------------|------------------|------|--------|------|--------|--------------|--|

| ltem               | Symbol           | Min. | Тур.   | Max. | Unit   | Remark       |  |

|                    | I <sub>VGH</sub> | -    | 0.5    | 1.0  | mA     | VGH =20.0V   |  |

|                    | Ivgl             | -    | 1.4    | 2.1  | mA     | VGL = -10.0V |  |

| Current for Driver | Ivdd             | -    | 16     | 24   | mA     | VDD =1.8V    |  |

|                    | lavdd            | -    | 19     | 28.5 | mA     | AVDD =10.2V  |  |

|                    | I vcomin         | -    | 0      | -    | mA     | VCOMIN=4.3V  |  |

<sup>1.</sup> Temp. ≦60°C, 90% RH MAX. Temp. >60°C, Absolute humidity shall be less than 90% RH at 60°C

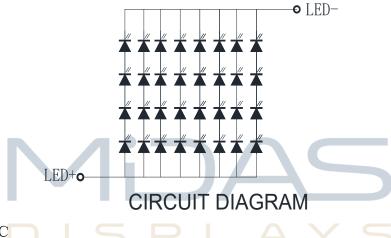

#### 3. Backlight Driving Conditions

| Parameter                             | Symbol | Min.   | Тур. | Max. | Unit | Note   |

|---------------------------------------|--------|--------|------|------|------|--------|

| Supply voltage of white LED backlight | VL     | 10.8   | 12.4 | 14.0 | V    | Note 1 |

| Current for LED backlight             | IL     | -      | 480  | -    | mA   |        |

| LED life time                         | -      | 50,000 | -    | -    | Hr   | Note2  |

Note 1 : There are 1 Groups LED

Note 2 : Ta = 25 ℃

Note 3 : Brightness to be decreased to 50% of the initial value

Note 4 : The single LED lamp case

# DC Electrical Characteristics

| 9.4. Deremeter           | Sympol |        | Rating | llmit  | Condition |           |  |

|--------------------------|--------|--------|--------|--------|-----------|-----------|--|

| 8.1. Parameter           | Symbol | Min    | Тур    | Мах    | Unit      | Condition |  |

| Low level input voltage  | VIL    | 0      | -      | 0.3VDD | V         | Note 1    |  |

| High level input voltage | VIH    | 0.7VDD | -      | VDD    | V         | Note 1    |  |

Note 1:RESET,STBYB, UPDN, SHLR

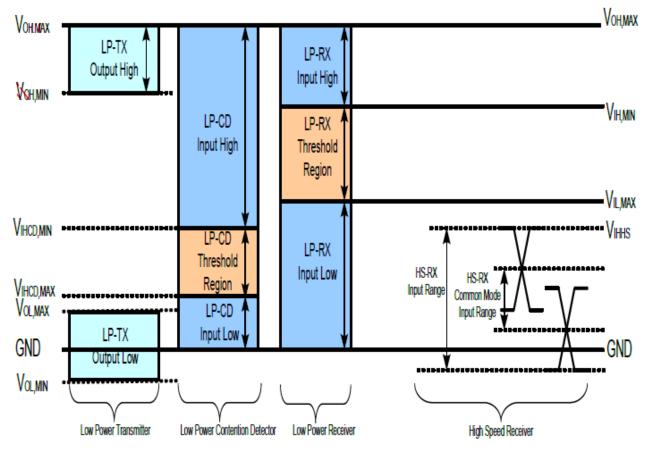

#### 2. MIPI Interface DC Characteristic

| Parameter                      | Symbol      | Min.                 | Тур.          | Max. | Unit |  |  |  |  |

|--------------------------------|-------------|----------------------|---------------|------|------|--|--|--|--|

|                                | MIPI Charac | teristics for High S | peed Receiver |      |      |  |  |  |  |

| Single-ended input low voltage | VILHS       | -40                  | -             | -    | mV   |  |  |  |  |

| Single-ended input high        | VIHHS       | -                    | -             | 460  | mV   |  |  |  |  |

| voltage                        |             |                      |               |      |      |  |  |  |  |

| Common-mode voltage            | VCDRXDC     | 70                   | -             | 330  | mV   |  |  |  |  |

| Differential input impedance   | ZID         |                      | 100           |      | ohm  |  |  |  |  |

| HS transmit differential       | VOD         | 140                  | 200           | 250  | mV   |  |  |  |  |

| voltage(VOD=VDP-VDN)           |             |                      |               |      |      |  |  |  |  |

|                                | MIPI Chara  | acteristics for Low  | Power Mode    |      |      |  |  |  |  |

| Pad signal voltage range       | Vi          | -50                  | -             | 1350 | mV   |  |  |  |  |

| Ground shift                   | VGNDSH      | -50                  | -             | 50   | mV   |  |  |  |  |

| Logic 0 input threshold        | VIL         | 0                    | -             | 550  | mV   |  |  |  |  |

| Logic 1 input threshold        | VIH         | 880                  | -             | 1350 | mV   |  |  |  |  |

| Input hysteresis               | VHYST       | 25                   | -             | -    | mV   |  |  |  |  |

| Output low level               | Vol         | -50                  | -             | 50   | mV   |  |  |  |  |

| Output high level              | Voн         | 1.1                  | 1.2           | 1.3  | V    |  |  |  |  |

| Output impedance of Low        | ZOLP        | 80                   | 100           | 125  | ohm  |  |  |  |  |

| Power Transmitter              |             |                      |               |      |      |  |  |  |  |

| Logic 0 contention threshold   | VILCD,MAX   | -                    | -             | 200  | mV   |  |  |  |  |

| Logic 0 contention threshold   | VIHCD,Man   | 450                  | -             | -    | mV   |  |  |  |  |

# **AC Electrical Characteristics**

## 1. Basic AC Characteristic

#### VDD/RESET AC characteristic

| Parameter               | Symbol             | Min. | Typ  | Max. | Unit | Condition         |

|-------------------------|--------------------|------|------|------|------|-------------------|

|                         |                    |      | Тур. |      |      |                   |

| VDD power slew rate     | TPOR               | -    | -    | 20   | ms   | From 0 to 90% VDD |

| RESETactive pulse width | T <sub>RESET</sub> | 1    | -    | -    | ms   | VDD=1.8V          |

| VDD resettle time       | TRES               | 1    | -    | -    | s    |                   |

| VDD<br>RESET            | TRESET             | 0%   | 0.17 | Thes |      | 0.1V              |

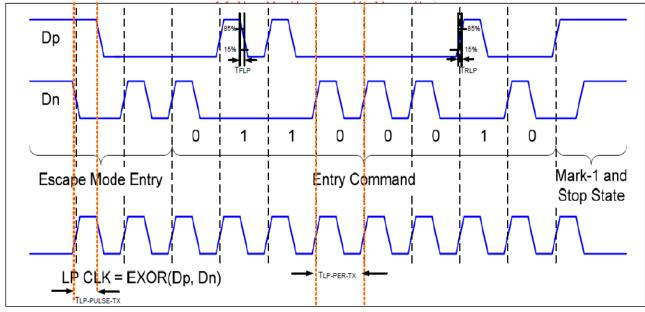

#### 2. MIPI AC Characteristic 1.Transmitter AC Specification

| Parameter       |                           | Symbol       | Min | Тур | Max | Units | Notes |

|-----------------|---------------------------|--------------|-----|-----|-----|-------|-------|

| 15%~85% risir   | ng time and falling time  | TRLP / TFLP  | -   | -   | 25  | ns    | -     |

| 30%~85% risir   | ng time and falling time  | TREOT        | -   | -   | 35  | ns    | -     |

| Pulse width     | First LP EXOR clock       |              |     |     |     |       | -     |

| of LP           | pulse after STOP state or |              |     |     |     |       |       |

| exclusive-OR    | Last pulse before stop    | TLP-PULSE-TX | 40  | -   | -   | ns    |       |

| clock           | state                     |              |     |     |     |       |       |

|                 | All other pulses          |              | 20  | -   | -   | ns    | -     |

| Period of the L | P EXOR clock              | TLP-PER-TX   | 90  | -   | -   | mV/ns | -     |

| Slew Rate @C    | LOAD =0pF                 |              | 30  | -   | 500 | mV/ns | -     |

| Slew Rate @C    | LOAD =5pF                 | δ V/δ tsr    | 30  | -   | 200 | mV/ns | -     |

| Slew Rate @C    | LOAD =20pF                | ] [          | 30  | -   | 150 | mV/ns | -     |

| Slew Rate @C    | LOAD =70pF                |              | 30  | -   | 100 | mV/ns | -     |

| Load Capacita   | nce                       | TRLP         | -   | -   | 70  | pF    | -     |

DP:MIPI\_D1P / MIPI\_D0P DN: MIPI\_D1N / MIPI\_D0N

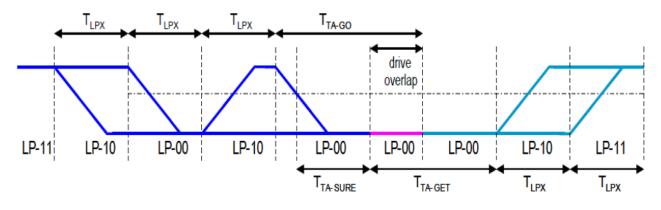

#### **Turnaround Procedure**

**Turnaround Procedure Operation Timing Parameters**

| Parameter                                          | Symbol   | Min  | Тур   | Max   | Units |

|----------------------------------------------------|----------|------|-------|-------|-------|

| Length of any Low-Power state period: Master side  | TLPX     | 50   | -     | 75    | ns    |

| Length of any Low-Power state period: Slave side   | TLPX     | 50   | 55.56 | 58.34 | ns    |

| Ratio of TLPX(Master)/ TLPX (Slave) between Master | Ratio    | 2/3  | -     | 3/2   |       |

| and Slave side                                     | TLPX     |      |       |       |       |

|                                                    |          |      |       |       |       |

| Time-out before new TX side start driving          | TTA-Sure | TLPX | -     | 2Tlpx | ns    |

| Time to drive LP-00 by new TX                      | TTA-GET  | -    | 5TLPX | -     | ns    |

| Time to drive LP-00 after Turnaround Request       | TTA-GO   | -    | 4Tlpx | -     | ns    |

|                                                    |          |      |       |       |       |

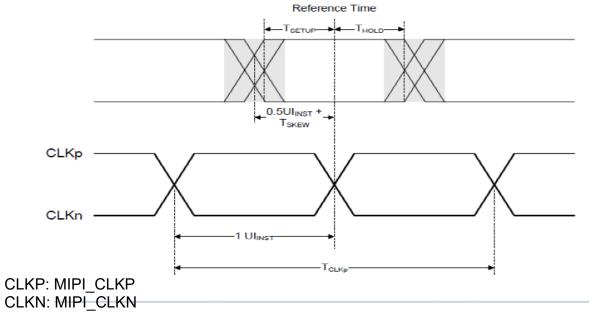

## 3. High speed transmission

| Parameter                  | Symbol     | Min   | Тур | Max  | Units  |

|----------------------------|------------|-------|-----|------|--------|

| UI instantaneous           | UIINST     | 2     | -   | 12.5 | ns     |

| Data to Clock              | TSKEW(TX)  | -0.15 | -   | 0.15 | UIINST |

| Skew(measured at           |            |       |     |      |        |

| transmitter)               |            |       |     |      |        |

| Data to Clock Setup        | TSETUP(RX) | 0.15  | -   | -    | UIINST |

| time(measured at receiver) |            |       |     |      |        |

| Data to Clock Hold         | THOLD(RX)  | 0.15  | -   | -    | UIINST |

| time(measured at receiver) |            |       |     |      |        |

| 20%~80% rise time and fall | Tr, Tf     | 150   | -   | -    | ps     |

| time                       |            | -     | -   | 0.3  | UIINST |

DESIGN • MANUFACTURE • SUPPLY

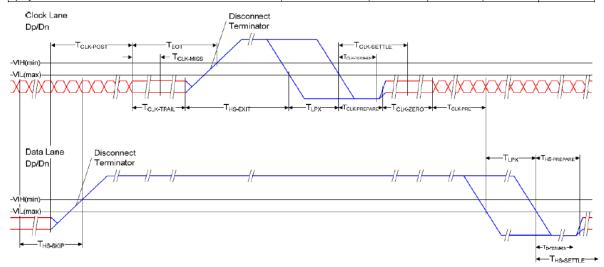

#### 4.High Speed Clock Transmission DP:MIPI\_D1P / MIPI\_D0P DN: MIPI\_D1N / MIPI\_D0N CLKP: MIPI\_CLKP CLKN: MIPI\_CLKN

| Parameter                                                                                                                       | Symbol                      | Min     | Тур | Max | Units |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|-----|-----|-------|

| Time that the transmitter shall continue sending<br>HS clock after the last associated Data Lane has<br>transitioned to LP mode | TCLK-POST                   | 60+52UI | -   | -   | ns    |

| Detection time that the clock has stopped toggling                                                                              | TCLK-MISS                   | -       | -   | 60  | ns    |

| Time to drive LP-00 to prepare for HS clock<br>transmission                                                                     | TCLK-PREPARE                | 38      | -   | 95  | ns    |

| Minimum lead HS-0 drive period before starting<br>clock                                                                         | TCLK-PREPARE<br>+ TCLK-ZERO | 300     | -   | -   | ns    |

| Time to enable Clock Lane receiver line<br>termination measured from when Dn cross<br>VIL.MAX                                   | THS-TERM-EN                 | -       | -   | 38  | ns    |

| Minimum time that the HS clock must be prior to<br>any associated data lane beginning the<br>transmission from LP to HS mode    | TCLK-PRE                    | 8       | -   | -   | UI    |

| Time to drive HS differential state after last<br>payload clock bit of a HS transmission burst                                  | TCLK-TRAIL                  | 60      | -   | -   | ns    |

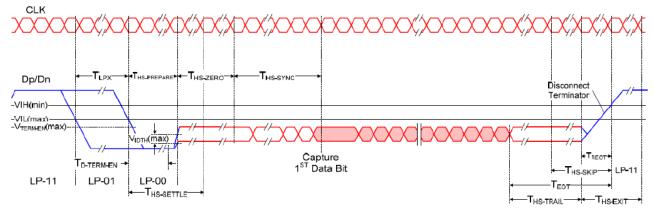

#### 5. High Speed Data Transmission in Bursts

Page 11 of 29

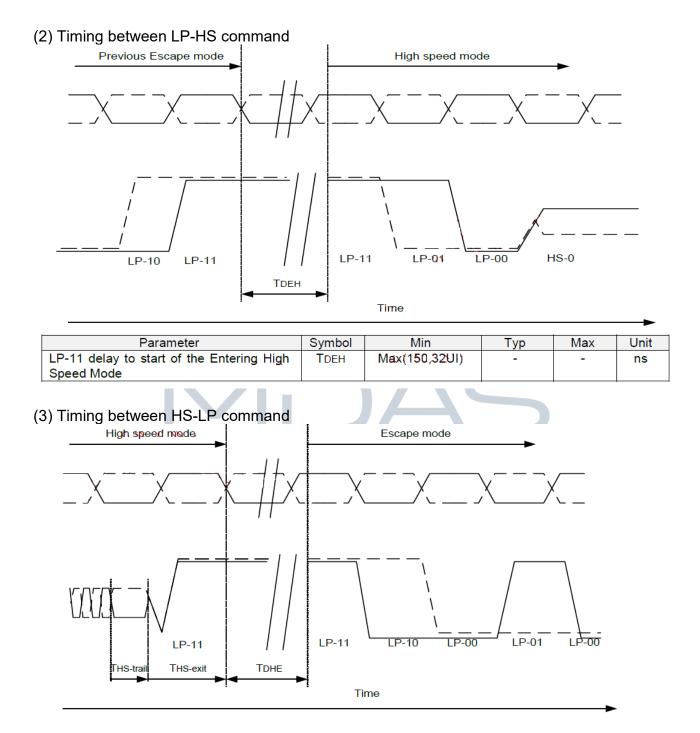

#### 6.LP11 timing request between data transformation

When Clock lane of DSI TX chip always keeps High speed mode, then Clock lane never go back to Low power mode. If Date lane of TX chip needs to transmit the next new data transmission or sequence, after the end of Low power mode or High speed mode or BTA. Then TX chip needs to keep LP-11 stop state before the next new data transmission, no matter in Low power mode or High speed mode or BTA. The LP-11 minimum timing is required for RX chip in the following 9 conditions, include of LP—LP, LP—HS, HS— LP, HS— HS, BTA— BTA, LP— BTA, BTA— LP, HS— BTA, and BTA— HS.This rule is suitable for short or long packet between TX and RX data transmission.

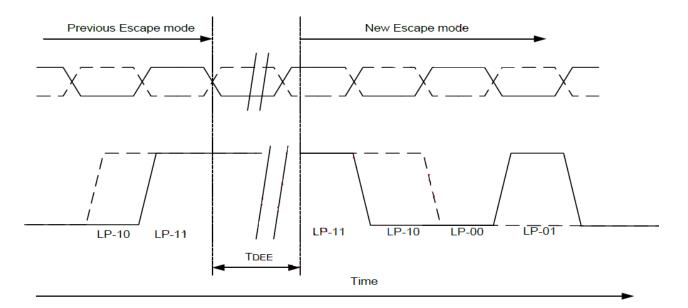

(1) Timing between LP-LP command

| Parameter                                         | Symbol | Min | Тур | Max | Unit |

|---------------------------------------------------|--------|-----|-----|-----|------|

| LP-11 delay to start of the new Escape Mode Entry | TDEE   | 150 | -   | -   | ns   |

| Parameter                               | Symbol | Min           | Тур | Max | Unit |

|-----------------------------------------|--------|---------------|-----|-----|------|

| LP-11 delay to start of the Escape Mode | TDHE   | Max(150,32UI) | -   | -   | ns   |

| Entry                                   |        |               |     |     |      |

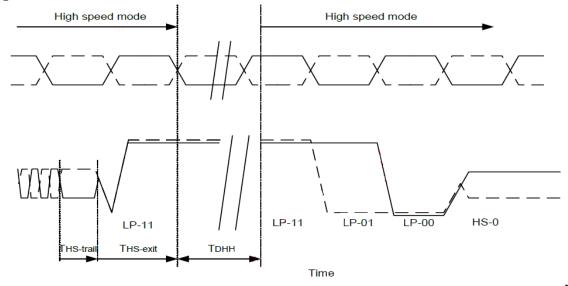

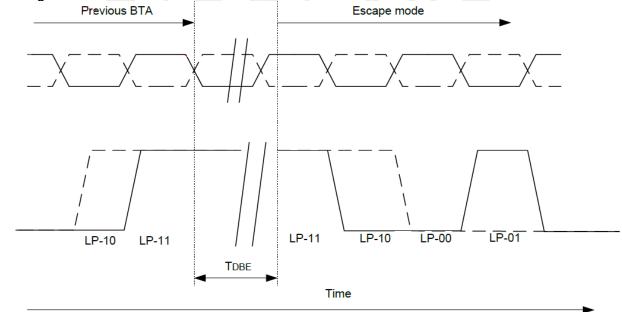

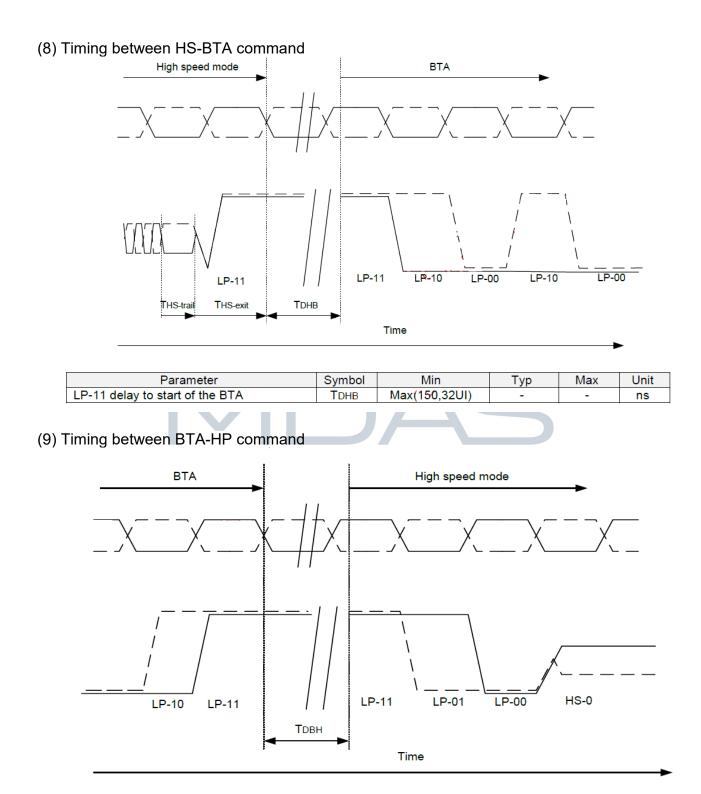

## (4) Timing between HS-HS command

| Parameter                                            | Symbol | Min           | Тур | Max | Unit |

|------------------------------------------------------|--------|---------------|-----|-----|------|

| LP-11 delay to start of the Entering High Speed Mode | TDHH   | Max(150,32UI) | -   | -   | ns   |

|                                                      |        |               |     |     |      |

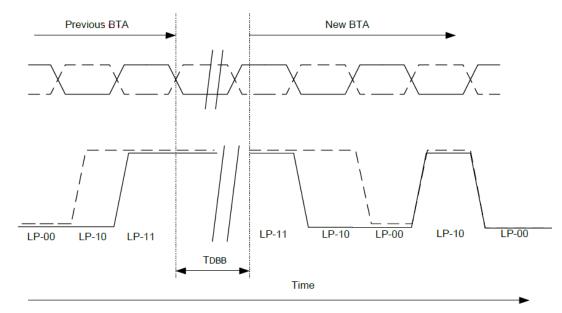

(5) Timing between BTA-BTA command

| Parameter                           | Symbol | Min | Тур | Max | Unit |

|-------------------------------------|--------|-----|-----|-----|------|

| LP-11 delay to start of the new BTA | TDBB   | 150 | -   | -   | ns   |

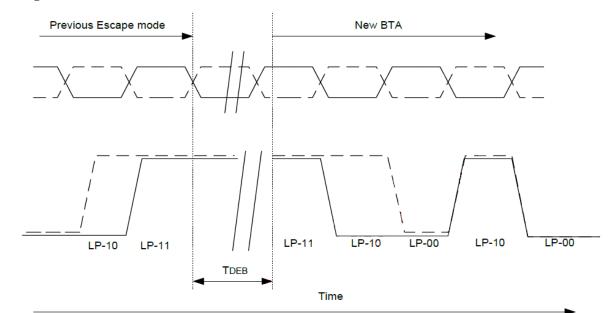

## (6) Timing between LP-BTA command

| Parameter                           | Symbol | Min | Тур | Max | Unit |

|-------------------------------------|--------|-----|-----|-----|------|

| LP-11 delay to start of the new BTA | TDEB   | 150 | -   | -   | ns   |

|                                     |        |     |     |     |      |

## (7) Timing between BTA-LP command

| Parameter                                     | Symbol | Min | Тур | Max | Unit |

|-----------------------------------------------|--------|-----|-----|-----|------|

| LP-11 delay to start of the Escape Mode Entry | TDBE   | 150 | -   | -   | ns   |

| Parameter                                 | Symbol | Min           | Тур | Max | Unit |

|-------------------------------------------|--------|---------------|-----|-----|------|

| LP-11 delay to start of the Entering High | TDBH   | Max(150,32UI) | -   | -   | ns   |

| Speed Mode                                |        |               |     |     |      |

# **Function Description**

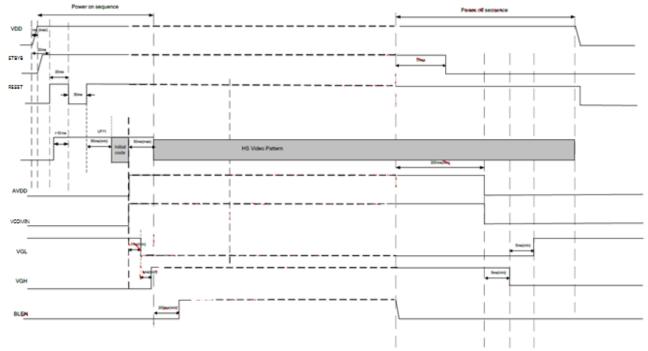

### 1. Power On/Off Sequence

In order to prevent IC from power on reset fail, the rising time (TPOR) of the digital power supply VDD should be maintained within the given specifications. Refer to "AC Characteristics" for more detail on timing.

#### **Power On/Off Sequence**

Note: CLK and Data Lanes should keep in LP11(stop state) before RESET.

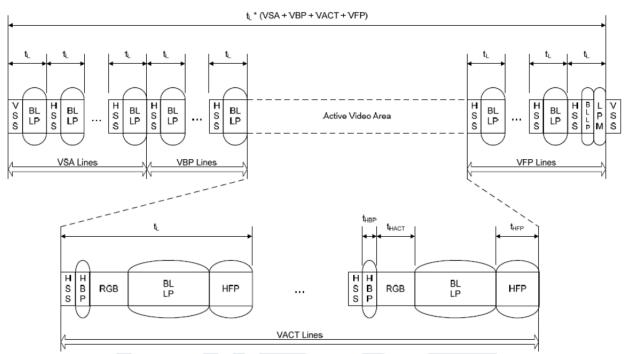

# 2. Vertical input timing

Vertical input timing

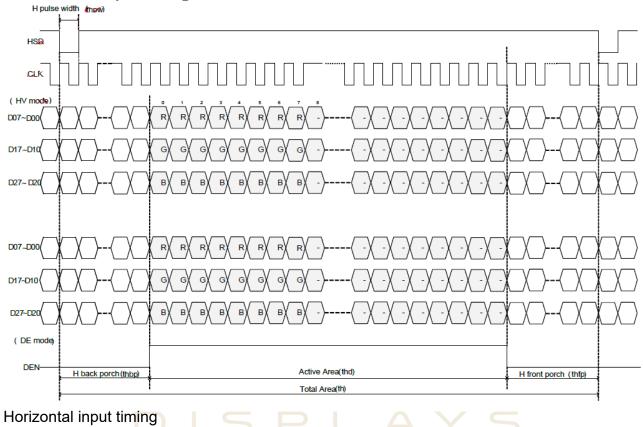

#### 3. Horizontal input timing

#### 4. Input Timing Table (2Lane) For 1024RGB x 600 panel DE mode

Value Parameter Symbol Unit Min. Тур. Max. DCLK frequency @Frame rate=60hz 40.8 51.2 fclk Mhz Horizontal display area thd 1024 DCLK HSYNC period time th 1114 1344 DCLK thb+thfp 90 320 DCLK HSYNC blanking Vertical display area Tvd 600 н VSYNC period time Τv 610 Н 635 VSYNC blanking Tvb+Tvfp 10 35 Н

#### HV mode Horizontal input timing

| Parameter                       |            | Symbol | Value |      |      | Unit |

|---------------------------------|------------|--------|-------|------|------|------|

| Horizontal display a            | rea        | thd    | 1024  |      |      | DCLK |

| DCLK frequency@ Frame rate=60hz |            | fclk   | Min.  | Тур. | Max. |      |

|                                 | Tale-00112 | ICIN   | 44.9  | 51   | .2   | Mhz  |

| 1 Horizontal Line               | e th       |        | 1200  | 1344 |      |      |

|                                 | Min.       |        | 1     |      |      |      |

| HSYNC pulse width               | Тур.       | thpw   |       | 70   |      | DCLK |

|                                 | Max.       |        |       | 140  |      |      |

| HSYNC blanking                  |            | thb    | 160   | 16   | 60   |      |

| HSYNC front porch               |            | thfp   | 16    | 16   | 60   |      |

#### HV mode

Vertical input timing

| Parameter             | Symbol |      | Unit |      |      |  |

|-----------------------|--------|------|------|------|------|--|

| Falameter             | Symbol | Min. | Тур. | Max. | Onit |  |

| Vertical display area | tvd    |      | 600  |      | Н    |  |

| VSYNC period time     | tv     | 624  | 635  |      | Н    |  |

| VSYNC pulse width     | tvpw   | 1    | 20   |      | Н    |  |

| VSYNC back porch      | tvb    | 23   | 23   |      | Н    |  |

| VSYNC front porch     | tvfp   | 1    | 12   |      | Н    |  |

DESIGN • MANUFACTURE • SUPPLY

# **MIPI Interface**

#### 1. MIPI INTERFACE (MOBILE INDUSTRY PROCESSING INTERFACE)

The Display Serial Interface standard defines protocols between a host processor and peripheral devices that adhere to MIPI Alliance standards for mobile device interfaces. The DSI standard builds on existing standards by adopting pixel formats and command set defined in MIPI Alliance standards.

DSI-compliant peripherals support either of two basic modes of operation: Command Mode and Video Mode. Which mode is used depends on the architecture and capabilities of the peripheral. The mode definitions reflect the primary intended use of DSI for display interconnect, but are not intended to restrict DSI from operating in other applications. Command Mode refers to operation in which transactions primarily take the form of sending commands and data to a peripheral, such as a display module, that incorporates a display controller. The display controller may include local registers. Systems using Command Mode write to, and read from, the registers. The host processor indirectly controls activity at the peripheral by sending commands, parameters and data to the display controller. The host processor can also read display module status information. Command Mode operation requires a bidirectional interface.

Video Mode refers to operation in which transfers from the host processor to the peripheral take the form of a real-time pixel stream. In normal operation, the display module relies on the host processor to provide image data at sufficient bandwidth to avoid flicker or other visible artifacts in the displayed image. Video information should only be transmitted using High Speed Mode. To reduce complexity and cost, systems that only operate in Video Mode may use a unidirectional data path.

|            | MCU (Master) Display Module (Slave)                                         |  |  |  |

|------------|-----------------------------------------------------------------------------|--|--|--|

| Clock Lane | Unidirectional Lane                                                         |  |  |  |

|            | Clock Only                                                                  |  |  |  |

|            | Escape Mode(ULPS Only)                                                      |  |  |  |

| Data Lane0 | Bi-directional Lane                                                         |  |  |  |

|            | <ul> <li>Forward High-Speed</li> </ul>                                      |  |  |  |

|            | <ul> <li>Bi-directional Escape Mode</li> <li>Bi-directional LPDT</li> </ul> |  |  |  |

| Data Lane1 | Unidirectional                                                              |  |  |  |

|            | <ul> <li>Forward High speed</li> </ul>                                      |  |  |  |

MIPI Lane Configuration:

#### 2. Display Serial Interface (DSI)

#### Video Mode Communication

Video Mode peripherals require pixel data delivered in real time. This section specifies the format and timing of DSI traffic for this type of display module.

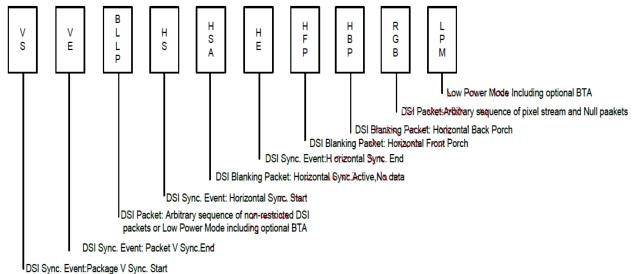

#### **Transmission Packet Sequences**

DSI supports several formats, or packet sequences, for Video Mode data transmission. The peripheral's timing requirements dictate which format is appropriate. These terms are used throughout the following sections:

□ Non-Burst Mode with Sync Pulses — enables the peripheral to accurately reconstruct original video timing, including sync pulse widths.

□ Non-Burst Mode with Sync Events — similar to above, but accurate reconstruction of sync pulse widths is not required, so a single Sync Event is substituted.

□ Burst mode — RGB pixel packets are time-compressed, leaving more time during a scan line for LP mode(saving power) or for multiplexing other transmissions onto the DSI link.

In the following figures the Blanking or Low-Power Interval (BLLP) is defined as a period during which video packets such as pixel-stream and sync event packets are not actively transmitted to the peripheral. To enable PHY synchronization the host processor should periodically end HS transmission and drive the Data Lanes to the LP state. This transition should take place at least once per frame; shown as LPM in the figures in this section. It is recommended to return to LP state once per scanline during the horizontal blanking time. Regardless of the frequency of BLLP periods, the host processor is responsible for meeting all documented peripheral timing requirements. Note, at lower frequencies BLLP periods will approach, or become, zero.

During the BLLP the DSI Link may do any of the following:

Remain in Idle Mode with the host processor in LP-11 state and the peripheral in LP-RX.

Transmit one or more non-video packets from the host processor to the peripheral using

Escape Mode.

Transmit one or more non-video packets from the host processor to the peripheral using HS Mode.

□ If the previous processor-to-peripheral transmission ended with BTA, transmit one or more packets from the peripheral to the host processor using Escape Mode.

□ Transmit one or more packets from the host processor to a different peripheral using a different Virtual Channel ID.

The sequence of packets within the BLLP or RGB portion of a HS transmission is arbitrary. The host processor may compose any sequence of packets, including iterations, within the limits of the packet format definitions. For all timing cases, the first line of a frame shall start with VS; all other lines shall start with HS. This is also true in the special case when VSA+VBP=0. Note that the position of synchronization packets, such as VS and HS, in time is

of utmost importance since this has a direct impact on the visual performance of the display panel.

Normally, RGB pixel data is sent with one full scan line of pixels in a single packet. Individual pixels shall not be split across packets.

Transmission packet components used in the figures in this section are defined in Figure below unless otherwise specified.

#### DSI Video Mode Interface Timing Legend

If a peripheral timing specification for HBP or HFP minimum period is zero, the corresponding Blanking Packet may be omitted. If the HBP or HFP maximum period is zero, the corresponding blanking packet shall be omitted.

#### **Clock Requirements**

A DSI host processor shall support continuous clock on the Clock Lane for display module that require it, so the host processor needs to keep the HS serial clock running.

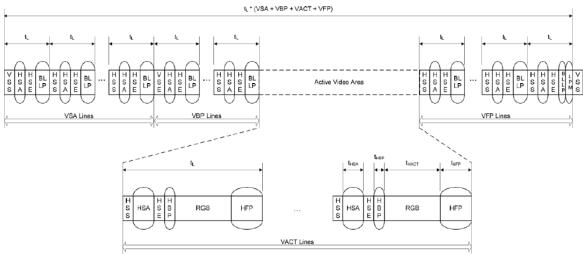

#### Non-Burst Mode with Sync Pulses

With this format, the goal is to accurately convey DPI-type timing over the DSI serial Link. This includes matching DPI pixel-transmission rates, and widths of timing events like sync pulses. Accordingly, synchronization periods are defined using packets transmitting both start and end of sync pulses. An example of this mode is shown in Figure below.

Normally, periods shown as I (Horizontal Sync Active), HBP (Horizontal Back Porch) and HFP (Horizontal Front Porch) are filled by Blanking Packets, with lengths (including packet overhead) calculated to match the period specified by the peripheral's data sheet. Alternatively, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power

#### □Non-Burst Mode with Sync Events

This mode is a simplification of the format described in section "Non-Burst Mode with Sync Pulse" .Only the start of each synchronization pulse is transmitted. The peripheral may regenerate sync pulses as needed from each Sync Event packet received. Pixels are transmitted at the same rate as they would in a corresponding parallel display interface such as DPI-2. An example of this mode is shown in Figure below.

As with the previous Non-Burst Mode, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

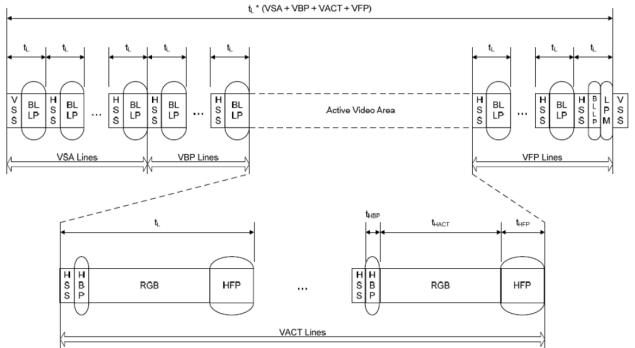

## Burst Mode IGN . MANUFACTURE . SUPPLY

In this mode, blocks of pixel data can be transferred in a shorter time using a timecompressed burst format. This is a good strategy to reduce overall DSI power consumption, as well as enabling larger blocks of time for other data transmissions over the Link in either direction. There may be a line buffer or similar memory on the peripheral to accommodate incoming data at high speed. Following HS pixel data transmission, the bus goes to Low Power Mode, during which it may remain idle, i.e. the host processor remains in LP-11 state, or LP transmission may take place in either direction. If the peripheral takes control of the bus for sending data to the host processor, its transmission time shall be limited to ensure data underflow does not occur from its internal buffer memory to the display device. An example of this mode is shown in Figure below

Similar to the Non-Burst Mode scenario, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

## DESIGN • MANUFACTURE • SUPPLY

# **Optical Characteristics**

| ltem          |        | Symbol | Condition.                    | Min   | Тур.  | Max.  | Unit              | Remark               |

|---------------|--------|--------|-------------------------------|-------|-------|-------|-------------------|----------------------|

| Response time |        | Tr     | θ=0°、Φ=0°                     | -     | 10    | 20    | .ms               | Note 3               |

| Response      | ume    | Tf     | υ-υ 、Ψ-υ                      | -     | 20    | 25    | .ms               | NOLE 3               |

| Contrast r    | atio   | CR     | At optimized<br>viewing angle | 600   | 800   | -     | -                 | Note 4               |

| Color         | White  | Wx     | θ=0°、Φ=0                      | 0.252 | 0.302 | 0.352 | -                 | Note<br>2,6,7        |

| Chromaticity  | vvnite | Wy     | θ-0、Φ-0                       | 0.274 | 0.324 | 0.374 |                   |                      |

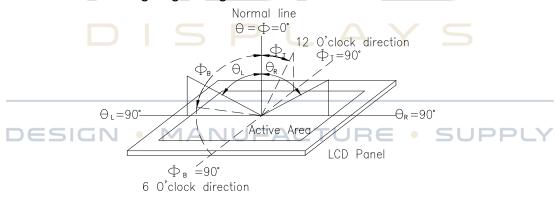

|               | Hor.   | ΘR     |                               | 80    | 85    | -     |                   | Note 1               |

| Viewing       |        | ΘL     |                               | 80    | 85    | -     | Dee               |                      |

| angle         | Ver    | ΦΤ     | CR≧10                         | 80    | 85    | -     | Deg.              |                      |

|               | Ver.   | ΦВ     |                               | 80    | 85    | -     |                   |                      |

| Brightne      | SS     | -      | -                             | 1000  | 1100  | -     | cd/m <sup>2</sup> | Center of<br>display |

| Uniform       | ity    | (U)    | -                             | 70    | - (   | -     | %                 | Note 5               |

Ta=25±2°C

Note 1: Definition of viewing angle range

Fig. 12.1. Definition of viewing angle

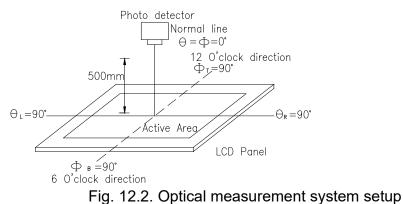

Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 10 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7 or BM-5 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

rig. 12.2. Optical measurement syste

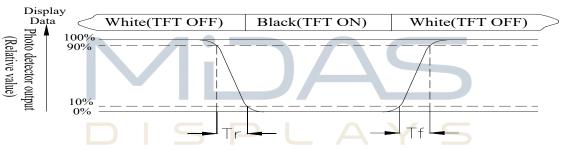

Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90% to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10% to 90%

Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

Contrast ratio (CR) = Luminance measured when LCD on the "White" state Luminance measured when LCD on the "Black" state

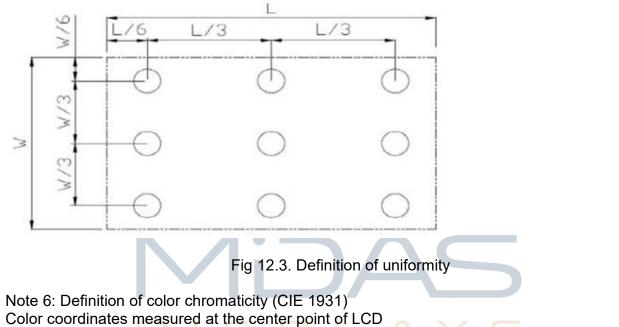

#### Note 5: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (reference the picture in below). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax x100%

L = Active area length

W = Active area width

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

## DESIGN • MANUFACTURE • SUPPLY

# Reliability

| Environmental Test                      |                                                                                                                        |                                                                                                                                                    |      |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Test Item                               | Content of Test                                                                                                        | Test Condition                                                                                                                                     | Note |

| High Temperature<br>storage             | Endurance test applying the high storage temperature for a long time.                                                  | 80°C<br>200hrs                                                                                                                                     | 2    |

| Low Temperature<br>storage              | Endurance test applying the low storage temperature for a long time.                                                   | -30°C<br>200hrs                                                                                                                                    | 1,2  |

| High Temperature<br>Operation           | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time. | 70°C<br>200hrs                                                                                                                                     |      |

| Low Temperature<br>Operation            | Endurance test applying the electric stress under low temperature for a long time.                                     | -20°C<br>200hrs                                                                                                                                    | 1    |

| High Temperature/<br>Humidity Operation | The module should be allowed to stand at 60°C,90%RH max                                                                | 60°C,90%RH<br>96hrs                                                                                                                                | 1,2  |

| Thermal shock<br>resistance             | The sample should be allowed stand the following 10 cycles of operation -20°C 25°C 70°C 30min 5min 30min 1 cycle       | -20°C/70°C<br>10 cycles                                                                                                                            |      |

| Vibration test                          | Endurance test applying the vibration during transportation and using.                                                 | Total fixed<br>amplitude : 1.5mm<br>Vibration Frequency :<br>10~55Hz<br>One cycle 60<br>seconds to 3<br>directions of X,Y,Z for<br>Each 15 minutes |      |

| Static electricity test                 | Endurance test applying the electric stress to the terminal.                                                           | VS=±600V(contact)<br>,±800v(air),<br>RS=330Ω<br>CS=150pF<br>10 times                                                                               | Y    |

Content of Reliability Test (Wide temperature, -20°C~70°C)

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

# **Initial Code For Reference**

command:

regw(0xB2,0x10); //Panel Control Register NW/2 Lanes

// 0x30=4LANE

- // 0x20=3LANE

- // 0x10=2LANE

regw(0x80,0x5B); //Gamma Control Register G2R/G1R regw(0x81,0x47); //Gamma Control Register G4R/G3R regw(0x82,0x84); //Gamma Control Register G6R/G5R regw(0x83,0x88); //Gamma Control Register G8R/G7R regw(0x84,0x88); //Gamma Control Register G10R/G9R regw(0x85,0x23); //Gamma Control Register G12R/G11R regw(0x86,0xB6); //Gamma Control Register G14R/G13R

\* Use MIPI Short Packet (0x15) To Write Command and Parameter DESIGN • MANUFACTURE • SUPPLY