# Intel<sup>®</sup> Cyclone<sup>®</sup> 10 LP FPGA Evaluation Kit User Guide

ID: 683580 Version: 2019.12.19

UG-20082

# intel

# Contents

| 1. Overview                                                                               | 4  |

|-------------------------------------------------------------------------------------------|----|

| 1.1. Evaluation Kit Description                                                           | 4  |

| 1.1.1. Evaluation Board Description                                                       |    |

| 1.1.2. Evaluation Kit Collateral                                                          |    |

| 1.1.3. Power Supply Description                                                           |    |

| 1.2. Recommended Operating Conditions                                                     |    |

| 1.3. Handling the Board<br>1.4. Evaluation Board Revisions                                |    |

|                                                                                           |    |

| 2. Getting Started                                                                        |    |

| 2.1. Installing Quartus Prime Software                                                    |    |

| 2.2. Installing the Evaluation Kit Collateral                                             |    |

| 2.3. Installing Intel FPGA Download Cable Driver                                          |    |

| 3. Evaluation Board Setup                                                                 |    |

| 3.1. Powering Up the Evaluation Board                                                     |    |

| 3.2. Default Switch Settings                                                              |    |

| 3.3. Recovering Factory Default Settings                                                  |    |

| 4. Evaluation Board Components                                                            | 14 |

| 4.1. Board Overview                                                                       | 14 |

| 4.2. Intel Cyclone 10 LP FPGA Overview                                                    |    |

| 4.3. MAX 10 System Controller Overview                                                    |    |

| 4.4. FPGA Configuration.                                                                  |    |

| 4.4.1. Using the Quartus Prime Programmer                                                 |    |

| 4.4.2. Program On-Board EPCQ or EPCQ-A Flash Memory<br>4.4.3. Active Serial Configuration |    |

| 4.4.5. Active Serial Configuration                                                        |    |

| 4.5. Setup Elements                                                                       |    |

| 4.7. General User Input/Output                                                            |    |

| 4.8. Clocks                                                                               |    |

| 4.9. Connectors and Interfaces                                                            | 23 |

| 4.9.1. Gigabit Ethernet PHY                                                               |    |

| 4.9.2. 2x20 GPIO Expansion Header                                                         |    |

| 4.9.3. Arduino Connectors                                                                 |    |

| 4.9.4. Pmod Connectors                                                                    |    |

| 4.10. Memory                                                                              |    |

| 4.10.1. HyperRAM<br>4.10.2. EPCQ or EPCQ-A Flash Memory                                   |    |

| 4.10.2. LFCQ of LFCQ-A Flash Memory.                                                      |    |

| 4.11.1. Power Supply Options                                                              |    |

| 4.11.2. Power Tree                                                                        |    |

| 4.11.3. Current Measurement                                                               |    |

| 5. Simple Socket Server                                                                   | 20 |

| 5.1. Connecting to the Simple Socket Server                                               |    |

|                                                                                           |    |

| 6. Board Test System                                                                      |    |

| 6.1. The Configure Menu                                                                   | 42 |

# intel

|      | 6.2. The System Info Tab                      | 42                    |

|------|-----------------------------------------------|-----------------------|

|      | 6.2. The System Info Tab<br>6.3. The GPIO Tab | 43                    |

|      | 6.4. The Flash Tab                            | 44                    |

|      | 6.5. The HyperRAM Tab                         | 45                    |

|      | 6.6. The Power Monitor                        |                       |

|      | 6.7. The Clock Control                        | 48                    |

| A. S | Safety and Regulatory Information             | 50                    |

|      | A.1. Safety Warnings                          | 51                    |

|      |                                               |                       |

|      | A.2. Safety Cautions                          |                       |

| в. А |                                               | 52                    |

| В. А | A.2. Safety Cautions                          | 52<br><b>55</b>       |

| B. A | A.2. Safety Cautions                          | 52<br><b>55</b><br>55 |

# **1. Overview**

The Intel<sup>®</sup> Cyclone<sup>®</sup> 10 LP Evaluation Kit provides an easy-to-use platform for evaluating the performance and features of the Intel Cyclone 10 LP FPGA device.

# **1.1. Evaluation Kit Description**

The Intel Cyclone 10 LP FPGA Evaluation Kit includes the following components:

- The Intel Cyclone 10 LP FPGA evaluation board

- USB Y-cable (USB Type-A to mini Type-B) for both on-board Intel FPGA Download Cable II and 5 V power supply from USB port

- Intel Cyclone 10 LP FPGA Evaluation Kit collateral, available from the Intel Cyclone 10 LP FPGA page

The design tools for the Intel Cyclone 10 LP FPGA Evaluation Kit are contained in the Intel Quartus<sup>®</sup> Prime Standard Edition software. Intel Quartus Prime software can be downloaded from the Intel FPGA Download Center.

#### **Related Information**

- Intel Cyclone 10 LP FPGA page

- Intel FPGA Download Center

# **1.1.1. Evaluation Board Description**

The evaluation kit includes a RoHS and CE compliant Intel Cyclone 10 LP FPGA Evaluation Board with the following components.

#### **Featured Devices**

- Intel Cyclone 10 LP FPGA (10CL025, U256 package)

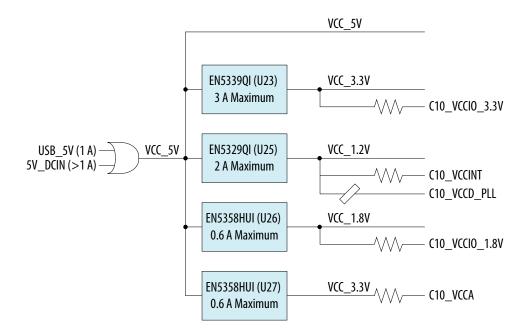

- Intel Enpirion<sup>®</sup> EN5329QI/EN5339QI 2A/3A PowerSoC Low Profile Synchronous Buck DC-DC Converter with Integrated Inductor

- Intel Enpirion EP5358xUI 600 mA PowerSoC DC-DC Step-Down Converters with Integrated Inductor

- Intel XWAY PHY11G Gigabit Ethernet PHY PEF7071

- Intel MAX<sup>®</sup> 10 FPGA 10M08SAU169C8G (Embedded Intel FPGA Download Cable II and System Management)

#### **Programming and Configuration**

- Embedded Intel FPGA Download Cable II (JTAG)

- Optional JTAG direct through 10-pin header

- Active Serial x1 configuration from EPCQ or EPCQ-A flash

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

#### **Memory Devices**

- 128 megabit (Mb) 8-bit HyperRAM with HBMC (Hyperbus Memory Controller) IP provided by Synaptic Labs

- Flash memory:

- Rev A1 board: 64 Mb EPCQ

- Rev A2 board: 128 Mb EPCQ-A

#### **Communication Ports**

- One Gigabit Ethernet (GbE) RJ-45 port

- One 2x20 GPIO Expansion Header

- One Arduino UNO R3 type connectors

- One 12-pin Digilent Pmod compatible connector

#### **Clock Circuits**

- Silicon Labs Si510 50 MHz crystal oscillator

- Silicon Labs Si5351 clock generator with programmable frequency GUI

#### **Power Supply**

- USB Y-cable (USB Type-A to mini Type-B) for both on-board Intel FPGA Download Cable II and 5 V power supply from USB port

- Supplemental 5 V DC power adapter option (5 V power adapter and cord are not included in the kit)

#### **Related Information**

EPCQ or EPCQ-A Flash Memory on page 34

## 1.1.2. Evaluation Kit Collateral

The Intel Cyclone 10 LP FPGA evaluation kit collateral includes example designs, board design files, documentation, and the Board Test System software.

#### **Related Information**

Installing the Evaluation Kit Collateral on page 8

#### **1.1.3. Power Supply Description**

There are two power supply options provided for the Intel Cyclone 10 LP FPGA Evaluation Board. The first is USB powered and the second is external AC/DC adapter powered. These two options can be used for different applications. There is an ORING circuit on-board to select suitable power source from USB power or DC jack.

#### **USB-Power**

A standard A to Mini-B USB Y-Cable is shipped with the evaluation board.

#### **AC/DC Adapter Power**

*Caution:* Use 5 V adapter for DC Jack J12 only. Components on the board can get damaged by power supplies with greater voltage.

# **1.2. Recommended Operating Conditions**

- Recommended ambient operating temperature range: 0C to 45C

- Maximum VCCINT current: 0.6 A

- Maximum board power consumption: 3 A @ 5 V when powered by AC/DC adapter

# **1.3. Handling the Board**

When handling the board, it is important to observe static discharge precautions.

- **Caution:** Without proper anti-static handling, the board could be damaged. Use anti-static handling precautions when touching the board.

- *Caution:* This evaluation board should not be operated in a vibration environment.

# **1.4. Evaluation Board Revisions**

Depending on its revision, your board has one of two flash memory devices: EPCQ64 or EPCQ128A. To determine which device you have, examine the part number label on the back side of the board, as shown in the following figure.

# Figure 1. Intel Cyclone 10 LP Evaluation Board Part Number Label

The following table shows the board revision and flash memory type corresponding to the part number.

### Table 1. Intel Cyclone 10 LP Evaluation Board Revision and Flash Type

| Part Number              | Board Revision | Flash Memory Type |

|--------------------------|----------------|-------------------|

| 6XX-44504R-0C or earlier | A1             | EPCQ64            |

| 6XX-44504R-0D or later   | A2             | EPCQ128A          |

intel

# 2. Getting Started

# 2.1. Installing Quartus Prime Software

To download the Intel Quartus Prime Standard Edition software, go to the **Quartus Prime Standard Edition** page in the Intel Download Center.

#### **About Intel Quartus Prime Software**

The Intel Quartus Prime design software is a multiplatform design environment that easily adapts to your specific needs in all phases of FPGA, CPLD, and SoC designs. The Intel Quartus Prime software delivers the highest performance and productivity for Intel FPGAs, CPLDs, and SoCs.

The Intel Quartus Prime Design Suite design software includes everything needed to design for Intel FPGAs, SoCs and CPLDs from design entry and synthesis to optimization, verification and simulation.

Intel Quartus Prime Standard Edition includes the most extensive support for Intel's latest device families and requires paid license.

Included in the Intel Quartus Prime Standard Edition are the Intel Quartus Prime software, Nios $^{\rm @}$  II EDS and the MegaCore IP Library.

#### **Related Information**

Intel FPGA Download Center

# 2.2. Installing the Evaluation Kit Collateral

To download the Intel Cyclone 10 LP FPGA Evaluation Kit collateral, perform the following steps:

- 1. Download the evaluation kit collateral from the Intel Cyclone 10 LP FPGA page.

- 2. Unzip the Intel Cyclone 10 LP FPGA Evaluation Kit collateral contents to your machine's local hard drive.

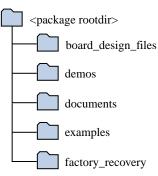

- 3. The collateral creates the directory structure shown in the figure below.

#### Figure 2. Evaluation Kit Directory Structure

#### The table below lists the file directory names and a description of their contents

#### Table 2.Directory Structure

| File Directory Name | Description of Directory Contents                                                                                                                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| board_design_files  | Contains schematics, layout, assembly and bill of material board design files. Use these files as a starting point for a new prototype board design |

| demos               | Contains demonstration applications when available                                                                                                  |

| documents           | Contains the evaluation kit documentation                                                                                                           |

| examples            | Contains the sample design files for the evaluation kit                                                                                             |

| factory_recovery    | Contains the original data programmed onto the board before shipment. Use this data to restore the board with its original factory contents.        |

#### **Related Information**

Intel Cyclone 10 LP FPGA page

# 2.3. Installing Intel FPGA Download Cable Driver

The Intel Cyclone 10 LP FPGA Evaluation Board includes embedded Intel FPGA Download Cable circuits for FPGA programming. However, for the host computer and board to communicate, you must install the Intel FPGA Download Cable driver on the host computer.

Installation instructions for the Intel FPGA Download Cable driver for your operating system are available on the Intel website.

On the Intel website, navigate to the Cable and Adapter Drivers Information link to locate the table entry for your configuration and click the link to access the instructions.

# **3. Evaluation Board Setup**

The instructions in this chapter explain how to set up the Intel Cyclone 10 LP FPGA Evaluation Board.

# **3.1. Powering Up the Evaluation Board**

There are two power supply options provided for the Intel Cyclone 10 LP FPGA Evaluation Board. The first is USB powered and the second is external AC/DC adapter powered. These two options can be used for different applications.

For most applications without Arduino, 2x20 GPIO, Pmod daughter cards, using an USB Cable offers sufficient current.

For some applications, daughter cards may draw high power consumption that USB port cannot offer sufficient current. A common 5 V AC/DC adapter can be plugged into the DC Jack J12 to offer higher current.

**Caution:** Use 5 V adapter for DC Jack J12 only. Components on the board can get damaged by power supplies with greater voltage.

To prepare and apply power to the board, perform the following steps:

- 1. The Intel Cyclone 10 LP evaluation board ships with its board switches preconfigured to support the design examples in the evaluation kit collateral. If you suspect your board might not be correctly configured with the default settings, follow the instructions in Default Switch Settings on page 10 to return the board to its factory settings before proceeding.

- 2. Connect either USB cable to J17 or 5 V DC adapter to J12 to power up the board.

- 3. After the board is powered up correctly, status LED illuminates. If you are using factory image stored in flash, the Blue LED will be ON to indicate power is good. Yellow LED D5 will be ON to indicate the FPGA is configured successfully. User LEDs D6, D7, D8, D9 will be blinking which is set in factory image.

# **3.2. Default Switch Settings**

This section shows the factory DIP switch settings for the Intel Cyclone 10 LP FPGA evaluation board.

| Switch | Board Label | Default Position | Function                |

|--------|-------------|------------------|-------------------------|

| SW1.4  | BYPASS      | OPEN/OFF/1       | Virtual JTAG TAP Enable |

| SW1.3  | DIPO        | OPEN/OFF/1       | Switch 0                |

| SW1.2  | DIP1        | OPEN/OFF/1       | Switch 1                |

| SW1.1  | DIP2        | OPEN/OFF/1       | Switch 2                |

#### Table 3. DIP Switch Settings

# **3.3. Recovering Factory Default Settings**

To restore the evaluation board to factory default settings, perform the following steps.

- 1. Make sure you have the latest Intel software tools, including the Intel Quartus Prime Standard Edition software, Nios II processor, and IP cores. If necessary, download the Intel Quartus Prime Standard Edition software from the Intel FPGA Download Center.

- 2. Launch the Board Test System (BTS) GUI application by one of the following methods:

- Nios II command shell:

- a. Launch the Nios II command shell.

- c. Type ./BoardTestSystem.exe to launch the BTS GUI.

- File manager:

- a. In a file manager GUI (such as File Explorer), change directory to cpackage dir>\examples\board\_test\_system\.

- b. Double-click BoardTestSystem.exe to launch the BTS GUI.

- 3. On the Restore menu, click Factory Restore.

# intel

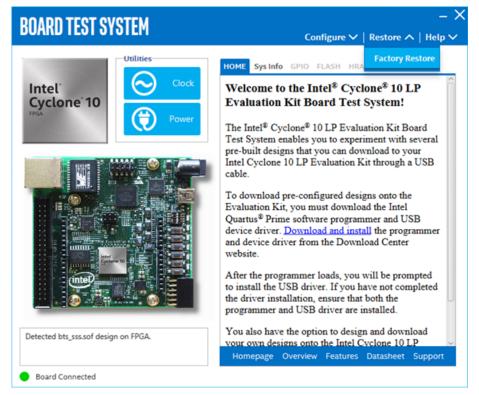

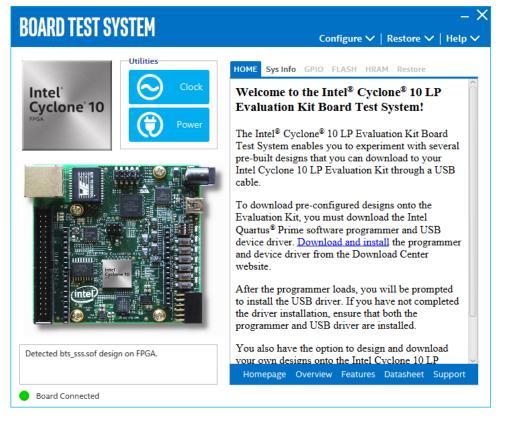

#### Figure 3. Board Test System GUI with Restore Menu

4. Fill in the text boxes with your board details, as shown in the example below, and click **Restore**.

The restore process takes several minutes.

# Figure 4. Restoring Factory Defaults on the Intel Cyclone 10 LP LP FPGA Evaluation Board

| BOARD TEST SYSTEM                       | - Ⅹ<br>Configure ✔   Restore ✔   Help ✔      |

|-----------------------------------------|----------------------------------------------|

| Utilities                               | HOME Sys Info GPIO FLASH HRAM Restore        |

| Intel' Clock                            | System Information                           |

| Cyclone 10                              | Board Name: Cyclone10 LP FPGA Evaluation Kit |

| Power                                   | Cyclone10 LP FPGA Evaluation Kit             |

|                                         | Board P/N: 6XX-44504R-0C                     |

|                                         | 6XX-44504R-XX                                |

|                                         | Serial Number: 10CLP025EK00064               |

|                                         | 10CLP025EK00004                              |

|                                         | Board Revision: Rev A.1                      |

|                                         | Rev A2                                       |

|                                         | Ethernet MAC: 00:07:ed:31:00:40              |

|                                         | Read Write Restore                           |

| Detected bts_config.sof design on FPGA. |                                              |

| Board Connected                         |                                              |

# **Related Information**

Intel FPGA Download Center

# **4. Evaluation Board Components**

This chapter introduces all important components on the evaluation board.

# 4.1. Board Overview

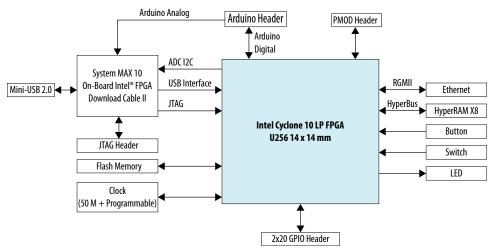

This topic provides a high-level list of major components on the Intel Cyclone 10 LP FPGA evaluation board.

#### Figure 5. Intel Cyclone 10 LP FPGA Evaluation Board Block Diagram

#### Table 4.Board Components

| Board Reference | Туре             | Description                                                                                                          |

|-----------------|------------------|----------------------------------------------------------------------------------------------------------------------|

|                 | Featured Devices |                                                                                                                      |

| U1              | FPGA             | Intel Cyclone 10 LP FPGA<br>10CL025YU256I7G, 25k LEs, U256<br>package                                                |

| U3              | FPGA             | Intel MAX 10 10M08SAU169C8G for<br>On-board Intel FPGA Download Cable<br>II and System Management                    |

| U25             | Power Regulator  | Intel Enpirion EN5329QI - 2A<br>PowerSoC Low Profile Synchronous<br>Buck DC-DC Converter with Integrated<br>Inductor |

| U23             | Power Regulator  | Intel Enpirion EN5339QI - 3A<br>PowerSoC Low Profile Synchronous<br>Buck DC-DC Converter with Integrated<br>Inductor |

|                 |                  | continued                                                                                                            |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

| Board Reference | Туре                                     | Description                                                                                                         |  |

|-----------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| U26, U27        | Power Regulator                          | Intel Enpirion EP5358HUI, 600 mA<br>PowerSoC DC-DC step-down<br>converters with integrated inductor.                |  |

| U14             | Gigabit Ethernet PHY                     | Intel XWAY PHY11G Single Port Gigabit<br>Ethernet PHY (10/100/1000 Mbps)<br>PEF7071                                 |  |

|                 | Configuration and Setup Elements         |                                                                                                                     |  |

| J17             | Embedded Intel FPGA Download Cable<br>II | Type-B Mini USB Connector for<br>programming and debugging the FPGA                                                 |  |

| 32              | 10-pin header                            | Optional JTAG direct through 10-pin header for external download cables                                             |  |

| SW1.4           | Virtual JTAG TAP Bypass Switch           | ON/Closed/0: Bypass Virtual JTAG TAP<br>OFF/Open/1: Enable Virtual JTAG TAP                                         |  |

| S1              | FPGA nCONFIG push button                 | Press this button to trigger reconfiguration                                                                        |  |

| S2              | FPGA reset push button                   | Press this button to reset all registers in the FPGA                                                                |  |

|                 | Status Elements                          |                                                                                                                     |  |

| D4              | Power LED (Blue)                         | Power Good LED (Detects VCC_3.3V<br>and VCC_1.2V)<br>ON: Detected Power is Good<br>OFF: Detected Power is Bad       |  |

| D5              | Configuration LED (Yellow)               | Config done status Indicator<br>ON: FPGA configured successfully<br>OFF: FPGA not configured                        |  |

| D10             | Ethernet LED0 (Green)                    | Ethernet link status indicator<br>ON: Link-up<br>OFF: Link-down<br>Blink: Link-up with traffic                      |  |

| D11             | Ethernet LED1 (Green)                    | Ethernet link speed indicator<br>ON: 100 Mbps<br>OFF: 10/1000 Mbps or Link-down                                     |  |

| D12             | Ethernet LED2 (Green)                    | Ethernet link speed indicator<br>ON: 1000 Mbps<br>OFF: 10/1000 Mbps or Link-down                                    |  |

|                 | Clock Circuits                           |                                                                                                                     |  |

| U20             | 50 MHz Oscillator                        | 50 MHz crystal oscillator for general<br>purpose logic of Intel Cyclone 10 LP<br>FPGA and Intel MAX 10 FPGA devices |  |

| U31             | Programmable clock generator             | Three channel Programmable clock<br>generator. Default frequencies are 125<br>MHz, 100 MHz and 50 MHz               |  |

|                 | General User Input/Output                |                                                                                                                     |  |

| S3, S4, S5, S6  | General user push buttons                | Four user push buttons. Driven low when pressed.                                                                    |  |

| D6, D7, D8, D9  | User LEDs                                | Four user LEDs. Illuminates when driven low.                                                                        |  |

#### 4. Evaluation Board Components 683580 | 2019.12.19

| Board Reference     | Туре                          | Description                                                                                                                                                                       |  |

|---------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SW1.1 - SW1.3       | User DIP Switches             | 3-bit user DIP switches                                                                                                                                                           |  |

|                     | Memory Devices                | ·                                                                                                                                                                                 |  |

| U13                 | HyperRAM Memory               | 128 Mb x8 HyperRAM with 1.8 V I/O                                                                                                                                                 |  |

| U2                  | Flash                         | <ul> <li>Board Rev A1: 64 Mb EPCQ</li> <li>Board Rev A2: 128 Mb EPCQ-A<sup>(1)</sup></li> </ul>                                                                                   |  |

|                     | I/O and Expansion Ports       | ·                                                                                                                                                                                 |  |

| J8                  | One Digilent Pmod Connector   | 12-pin interface with 8 I/O signal pins<br>used to connect low frequency, low I/O<br>peripheral modules                                                                           |  |

| J4, J5, J6, J7, J18 | Arduino UNO R3 type connector | Arduino UNO R3 type connectors with 3.3 V digital I/O and six analog input channels                                                                                               |  |

| J10                 | 2x20 GPIO Expansion Header    | 2x20 GPIO Expansion Header with 36 I/O                                                                                                                                            |  |

| J16                 | One Gigabit Ethernet Port     | RJ-45 connector provides a<br>10/100/1000 Ethernet connection<br>through a Intel PEF7071 PHY and the<br>FPGA-based Intel Triple Speed Ethernet<br>MegaCore function in RGMII mode |  |

|                     | Power Supply                  |                                                                                                                                                                                   |  |

| J12                 | DC input jack                 | Supplemental 5 V DC power adapter connector                                                                                                                                       |  |

| J17                 | USB Mini-B Connector          | For 5 V power from USB port also user<br>as Intel FPGA Download Cable<br>communication port                                                                                       |  |

### **Related Information**

EPCQ or EPCQ-A Flash Memory on page 34

# 4.2. Intel Cyclone 10 LP FPGA Overview

The Intel Cyclone 10 LP FPGA Evaluation Board features the Intel Cyclone 10 LP 10CL025YU256I7G FPGA device in a 256 pin Ultra FineLine BGA package.

The Intel Cyclone 10 LP FPGAs are optimized for low cost and low static power, making them ideal for high-volume and cost-sensitive applications.

#### Table 5. Intel Cyclone 10 LP FPGA

| Equivalent LEs | M9K Memory<br>Blocks | M9K Memory<br>Size (Kb) | 18-bit x 18-bit<br>multipliers | PLLs | Transceivers | Package Type                                        |

|----------------|----------------------|-------------------------|--------------------------------|------|--------------|-----------------------------------------------------|

| 25К            | 66                   | 594                     | 66                             | 4    |              | 256-pin UBGA<br>(14 mm x 14<br>mm, 0.8 mm<br>pitch) |

<sup>&</sup>lt;sup>(1)</sup> To identify your board revision, see "EPCQ or EPCQ-A Flash Memory".

#### Intel Cyclone 10 LP FPGA Feature Summary

Intel Cyclone 10 LP FPGA devices provide a high-density sea of programmable gates, on-board resources, and general purpose I/Os. These resources satisfy the requirements of I/O expansion and chip-to-chip interfacing. The Intel Cyclone 10 LP FPGA architecture suits smart and connected end applications across many market segments:

- Industrial and automotive

- Broadcast, wireline, and wireless

- Compute and storage

- Government, military, and aerospace

- Medical, consumer, and smart energy

#### Table 6. Summary of Features for Intel Cyclone 10 LP FPGA Devices

| Feature                         | Description                                                                                                                                                                                                                                                                                          |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Technology                      | <ul> <li>Low-cost, low-power FPGA fabric</li> <li>1.0 V and 1.2 V core voltage options</li> <li>Available in commercial, industrial, and automotive temperature grades</li> </ul>                                                                                                                    |  |

| Packaging                       | <ul> <li>Several package types and footprints:</li> <li>FineLine BGA (FBGA)</li> <li>Enhanced Thin Quad Flat Pack (EQFP)</li> <li>Ultra FineLine BGA (UBGA)</li> <li>Micro FineLine BGA (MBGA)</li> <li>Multiple device densities with pin migration capability</li> <li>RoHS6 compliance</li> </ul> |  |

| Core architecture               | <ul> <li>Logic elements (LEs)—four-input look-up table (LUT) and register</li> <li>Abundant routing/metal interconnect between all LEs</li> </ul>                                                                                                                                                    |  |

| Internal memory<br>blocks       | <ul> <li>M9K—9-kilobits (Kb) of embedded SRAM memory blocks, cascadable</li> <li>Configurable as RAM (single-port, simple dual port, or true dual port), FIFO buffers, or ROM</li> </ul>                                                                                                             |  |

| Embedded multiplier<br>blocks   | <ul> <li>One 18 × 18 or two 9 × 9 multiplier modes, cascadable</li> <li>Complete suite of DSP IPs for algorithmic acceleration</li> </ul>                                                                                                                                                            |  |

| Clock networks                  | <ul><li>Global clocks that drive throughout entire device, feeding all device quadrants</li><li>Up to 15 dedicated clock pins that can drive up to 20 global clocks</li></ul>                                                                                                                        |  |

| Phase-locked loops<br>(PLLs)    | <ul><li>Up to four general purpose PLLs</li><li>Provides robust clock management and synthesis</li></ul>                                                                                                                                                                                             |  |

| General-purpose I/Os<br>(GPIOs) | <ul> <li>Multiple I/O standards support</li> <li>Programmable I/O features</li> <li>True LVDS and emulated LVDS transmitters and receivers</li> <li>On-chip termination (OCT)</li> </ul>                                                                                                             |  |

| SEU mitigation                  | SEU detection during configuration and operation                                                                                                                                                                                                                                                     |  |

| Configuration                   | <ul> <li>Active serial (AS), passive serial (PS), fast passive parallel (FPP)</li> <li>JTAG configuration scheme</li> <li>Configuration data decompression</li> <li>Remote system upgrade</li> </ul>                                                                                                 |  |

#### **Related Information**

Intel Cyclone 10 LP FPGA Device Overview

# intel.

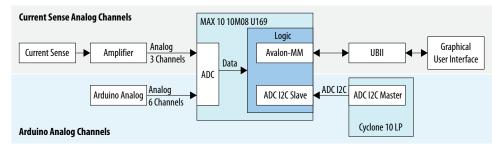

# 4.3. MAX 10 System Controller Overview

The highlights of the Intel MAX 10 devices include:

- Internally stored dual configuration flash

- User flash memory

- Instant on support

- Integrated analog-to-digital converter (ADC)

- Single-chip Nios II soft core processor support

Intel MAX 10 devices are the ideal solution for system management, I/O expansion, communication control planes, industrial, automotive, and consumer applications.

#### Table 7. Summary of Features for Intel MAX 10 Devices

| Feature                    | Description                                                                                                                                                                                                                                                                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                 | 55 nm TSMC Embedded Flash (Flash + SRAM) process technology                                                                                                                                                                                                                    |

| Packaging                  | <ul> <li>Low cost, small form factor packages—support multiple packaging technologies and pin pitches</li> <li>Multiple device densities with compatible package footprints for seamless migration between different device densities</li> <li>RoHS6-compliant</li> </ul>      |

| Core architecture          | <ul> <li>4-input look-up table (LUT) and single register logic element (LE)</li> <li>LEs arranged in logic array block (LAB)</li> <li>Embedded RAM and user flash memory</li> <li>Clocks and PLLs</li> <li>Embedded multiplier blocks</li> <li>General purpose I/Os</li> </ul> |

| Internal memory blocks     | <ul> <li>M9K—9 kilobits (Kb) memory blocks</li> <li>Cascadable blocks to create RAM, dual port, and FIFO functions</li> </ul>                                                                                                                                                  |

| User flash memory (UFM)    | <ul> <li>User accessible non-volatile storage</li> <li>High speed operating frequency</li> <li>Large memory size</li> <li>High data retention</li> <li>Multiple interface option</li> </ul>                                                                                    |

| Embedded multiplier blocks | <ul> <li>One 18 × 18 or two 9 × 9 multiplier modes</li> <li>Cascadable blocks enabling creation of filters, arithmetic functions, and image processing pipelines</li> </ul>                                                                                                    |

| ADC                        | <ul> <li>12-bit successive approximation register (SAR) type</li> <li>Up to 16 analog inputs</li> <li>Cumulative speed up to 1 million samples per second (MSPS)</li> <li>Integrated temperature sensing capability</li> </ul>                                                 |

| Clock networks             | <ul><li>Global clocks support</li><li>High speed frequency in clock network</li></ul>                                                                                                                                                                                          |

| Internal oscillator        | Built-in internal ring oscillator                                                                                                                                                                                                                                              |

| PLLs                       | <ul> <li>Analog-based</li> <li>Low jitter</li> <li>High precision clock synthesis</li> </ul>                                                                                                                                                                                   |

|                            | continued                                                                                                                                                                                                                                                                      |

| Feature                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                  | <ul> <li>Clock delay compensation</li> <li>Zero delay buffering</li> <li>Multiple output taps</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |  |  |

| General-purpose I/Os (GPIOs)     | <ul> <li>Multiple I/O standards support</li> <li>On-chip termination (OCT)</li> <li>Up to 830 megabits per second (Mbps) LVDS receiver, 800 Mbps LVDS transmitter</li> </ul>                                                                                                                                                                                                                                                                                     |  |  |

| External memory interface (EMIF) | <ul> <li>Supports up to 600 Mbps external memory interfaces:</li> <li>DDR3, DDR3L, DDR2, LPDDR2</li> <li>SRAM (Hardware support only)</li> <li>Note: For 600 Mbps performance, -6 device speed grade is required.<br/>Performance varies according to device grade (commercial, industrial, or automotive) and device speed grade (-6 or -7). Refer to the MAX 10<br/>Device Data Sheet or External Memory Interface Spec Estimator for more details.</li> </ul> |  |  |

| Configuration                    | <ul> <li>Internal configuration</li> <li>JTAG</li> <li>Advanced Encryption Standard (AES) 128-bit encryption and compression options</li> <li>Flash memory data retention of 20 years at 85 °C</li> </ul>                                                                                                                                                                                                                                                        |  |  |

| Flexible power supply schemes    | <ul> <li>Single- and dual-supply device options</li> <li>Dynamically controlled input buffer power down</li> <li>Sleep mode for dynamic power reduction</li> </ul>                                                                                                                                                                                                                                                                                               |  |  |

#### **Related Information**

MAX 10 FPGA Device Overview

# 4.4. FPGA Configuration

The Intel Cyclone 10 LP FPGA Evaluation Board supports two configuration methods:

- Configuration by downloading a .sof file to the FPGA. Any power cycling of the FPGA or reconfiguration will power up the FPGA to a blank state.

- Programming of the board EPCQ or EPCQ-A flash with a .jic file. Any power cycling of the FPGA or reconfiguration will lead to reconfigure from flash with AS mode.

You can use two different Intel FPGA Download Cable hardware components to program the .sof or .jic files:

- Embedded Intel FPGA Download Cable II type-B mini-USB connector (J17)

- JTAG header (J2). Use an external Intel FPGA Download Cable, Intel FPGA Download Cable II or Ethernet Blaster download cable. The external download cable connects to the board through the JTAG header (J2).

## 4.4.1. Using the Quartus Prime Programmer

You can use the Intel Quartus Prime Programmer to configure the FPGA with a .sof.

#### **Before configuring the FPGA**

- Ensure that the Intel Quartus Prime Programmer and the Intel FPGA Download Cable driver are installed on the host computer.

- The USB cable is connected to the board.

- Power to the board is on, and no other applications that use the JTAG chain are running.

#### To configure the Intel Cyclone 10 LP FPGA

- 1. Start the Intel Quartus Prime Programmer.

- 2. Click Add File and select the path to the desired .sof.

- 3. Turn on the Program/Configure option for the added file.

- 4. Click Start to download the selected file to the FPGA. Configuration is complete when the progress bar reaches 100%.

#### 4.4.2. Program On-Board EPCQ or EPCQ-A Flash Memory

The FPGA is set to Active Serial configuration mode by default. You can use the Intel Quartus Prime Programmer to program a .jic file to EPCQ or EPCQ-A flash.

#### **Program the EPCQ or EPCQ-A Flash**

- 1. Ensure the DIP switch SW1.4 is ON to bypass virtual JTAG TAP and then power on the board.

- 2. Open Intel Quartus Prime Programmer and ensure that JTAG is detected under Hardware Setup.

- 3. Select **Auto Detect** and choose the correct FPGA device.

- 4. Right-click on the FPGA device and select **Edit ➤ Attach Flash Device**.

- Select ASC Devices ➤ EPCQ64 (or EPCQ128A) in the pop-up window and then click OK.

- Right-click on the EPCQ64 (or EPCQ128A) device and select Edit ➤ Change File. Next, choose the generated .jic file you want to program.

- 7. Select the **Program/Configure** checkboxes for FPGA and EPCQ or EPCQ-A devices. Click **Start** to begin programming the FPGA.

- 8. Flash is programmed successfully when the progress bar reaches 100% and displays **Successful**.

- Attention: Please set SW1.4 to OFF if your following operations need to enable virtual JTAG TAP.

- *Note:* Either EPCQ64 or EPCQA128 may be used on boards of different board revisions. Refer to "EPCQ or EPCQ-A Flash Memory" for details.

#### **Related Information**

EPCQ or EPCQ-A Flash Memory on page 34

# 4.4.3. Active Serial Configuration

- 1. After all steps in the previous section are completed, press push button S1 C10\_NCONFIG or power cycle the board.

- 2. Yellow LED D5 will turn ON. This indicates that the FPGA is configured with the image in flash under Active Serial Mode.

# **4.5. Status Elements**

#### Table 8. LEDs

| Board Reference | Schematic Signal Name | Color  | Description                                                                                                   |

|-----------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------|

| D4              | PWR_GD_LED            | Blue   | Power Good LED (Detects<br>VCC_3.3V and VCC_1.2V)<br>ON: Detected Power is good<br>OFF: Detected Power is bad |

| D5              | SYS_CONF_DONE         | Yellow | Configuration Done Status<br>Indicator<br>ON: FPGA configured<br>successfully<br>OFF: FPGA not configured     |

| D10             | ENET_LED0             | Green  | Ethernet link status indicator<br>ON: Link-up<br>OFF: Link-down<br>Blink: Link-up with traffic                |

| D11             | ENET_LED1             | Green  | Ethernet link speed indicator<br>ON: 100 Mbps<br>OFF: 10/1000 Mbps or Link-<br>down                           |

| D12             | ENET_LED2             | Green  | Ethernet link speed indicator<br>ON: 1000 Mbps<br>OFF: 10/100 Mbps or Link-<br>down                           |

# **4.6. Setup Elements**

#### Table 9. DIP Switches

| [ | Board Reference | Schematic Signal Name | Description                                          |

|---|-----------------|-----------------------|------------------------------------------------------|

|   | SW1.4           | VTAP_BYPASSn          | Pull low to disable Virtual JTAG TAP in device chain |

#### Table 10. Push Buttons

| Board Reference | Schematic Signal Name | Description                                                                    |

|-----------------|-----------------------|--------------------------------------------------------------------------------|

| S1              | C10_nCONFIG           | Press this push button to reconfigure<br>Intel Cyclone 10 LP FPGA device       |

| S2              | C10_RESETN            | Press to do device-wide reset, connect<br>to Intel Cyclone 10 LP FPGA DEV_CLRn |

# intel.

# 4.7. General User Input/Output

## Table 11. DIP Switches

| Board Reference | Schematic Signal<br>Name | FPGA Signal Name | Description          |

|-----------------|--------------------------|------------------|----------------------|

| SW1.3           | USER_DIP0                | U1.M16           | User-defined Switch0 |

| SW1.2           | USER_DIP1                | U1.A8            | User-defined Switch1 |

| SW1.1           | USER_DIP2                | U1.A9            | User-defined Switch2 |

## Table 12. Push Buttons

| Board Reference | Schematic Signal<br>Name | FPGA Signal Name | Description      |

|-----------------|--------------------------|------------------|------------------|

| S3              | USER_PB0                 | U1.E15           | User-defined PB0 |

| S4              | USER_PB1                 | U1.F14           | User-defined PB1 |

| S5              | USER_PB2                 | U1.C11           | User-defined PB2 |

| S6              | USER_PB3                 | U1.D9            | User-defined PB3 |

## Table 13. LEDs

| Board Reference | Schematic Signal<br>Name | FPGA Signal Name | Color | Description                   |

|-----------------|--------------------------|------------------|-------|-------------------------------|

| D6              | USER_LED0                | U1.L14           | Green | User-defined LED0, active low |

| D7              | USER_LED1                | U1.K15           | Green | User-defined LED1, active low |

| D8              | USER_LED2                | U1.J14           | Green | User-defined LED2, active low |

| D9              | USER_LED3                | U1.J13           | Green | User-defined LED3, active low |

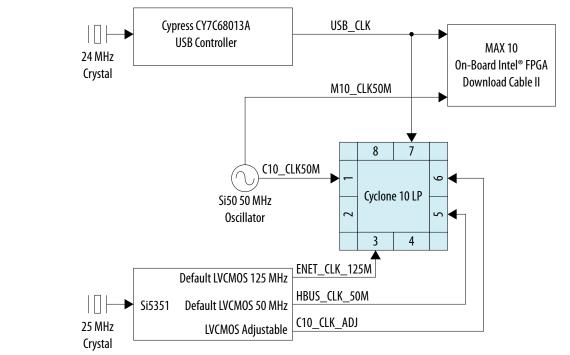

# 4.8. Clocks

Si5351 is a programmable clock generator that users can use Intel Clock GUI to program output frequency. It is controlled from Intel MAX 10 with  $I^2C$  bus.

The clock tree is shown in the figure below.

#### Figure 6. Intel Cyclone 10 LP FPGA Clock Tree

## 4.9. Connectors and Interfaces

This section describes the evaluation board's communication ports, and interface cards related to the Intel Cyclone 10 LP FPGA Evaluation Kit.

#### 4.9.1. Gigabit Ethernet PHY

The evaluation board supports single port Ethernet through Intel XWAY PHY11G PEF7071 Ethernet PHY chips. This physical layer device has general applications using RJ-45 connector.

#### Figure 7. MAC-to-PHY connection by PEF7071 device

Specific to the Intel Cyclone 10 LP FPGA evaluation board, the MAC-to-PHY interface is configured to a RGMII interface connection with MDIO interface as management.

| Schematic Signal<br>Name | Schematic<br>Shared Bus<br>Signal Name | FPGA Pin Number | I/O Standard | Direction @ FPGA | Description     |

|--------------------------|----------------------------------------|-----------------|--------------|------------------|-----------------|

| ENET_RG_TXCLK            | C10_RG_TXCLK                           | D3              | 3.3 V        | Out              | RGMII TX clock  |

| ENET_RG_TXD0             | C10_RG_TXD0                            | E6              | 3.3 V        | Out              | RGMII TX data 0 |

| ENET_RG_TXD1             | C10_RG_TXD1                            | A3              | 3.3 V        | Out              | RGMII TX data 1 |

| ENET_RG_TXD2             | C10_RG_TXD2                            | B3              | 3.3 V        | Out              | RGMII TX data 2 |

| continued                |                                        |                 |              |                  |                 |

#### Table 14.Ethernet PHY Table

| Schematic Signal<br>Name | Schematic<br>Shared Bus<br>Signal Name | FPGA Pin Number | I/O Standard | Direction @ FPGA | Description                 |

|--------------------------|----------------------------------------|-----------------|--------------|------------------|-----------------------------|

| ENET_RG_TXD3             | C10_RG_TXD3                            | A2              | 3.3 V        | Out              | RGMII TX data 3             |

| ENET_RG_TXCTL            | C10_RG_TXCTL                           | D6              | 3.3 V        | Out              | RGMII TX control            |

| ENET_RG_RXCLK            | RG_RXCLK                               | B8              | 3.3 V        | In               | RGMII RX Clock              |

| ENET_RG_RXD0             | RG_RXD0                                | A7              | 3.3 V        | In               | RGMII RX data 0             |

| ENET_RG_RXD1             | RG_RXD1                                | B7              | 3.3 V        | In               | RGMII RX data 1             |

| ENET_RG_RXD2             | RG_RXD2                                | A6              | 3.3 V        | In               | RGMII RX data 2             |

| ENET_EG_RXD3             | RG_RXD3                                | B6              | 3.3 V        | In               | RGMII RX data 3             |

| ENET_RG_RXCTL            | RG_RXCTL                               | A5              | 3.3 V        | In               | RGMII RX Control            |

| ENET_INT                 |                                        | B5              | 3.3 V        | In               | Management<br>Interrupt     |

| ENET_MDC                 |                                        | B4              | 3.3 V        | Out              | MDIO clock                  |

| ENET_MDIO                |                                        | A4              | 3.3 V        | I/O              | MDIO data                   |

| ENET_RSTn                |                                        | C6              | 3.3 V        | Out              | Device Reset                |

| ENET_XTAL1               |                                        |                 |              |                  |                             |

| ENET_XTAL2               |                                        |                 |              |                  |                             |

| ENET_LED0                |                                        |                 | 3.3 V        | Out              | Status LED0,<br>Green       |

| ENET_LED1                |                                        |                 | 3.3 V        | Out              | Status LED1,<br>Green       |

| ENET_LED2                |                                        |                 | 3.3 V        | Out              | Status LED2,<br>Green       |

| TPIAP                    |                                        |                 |              |                  | Twisted-Pair A, positive    |

| TPIAN                    |                                        |                 |              |                  | Twisted-Pair A, negative    |

| TPIBP                    |                                        |                 |              |                  | Twisted-Pair B, positive    |

| TPIBN                    |                                        |                 |              |                  | Twisted-Pair B,<br>negative |

| TPICP                    |                                        |                 |              |                  | Twisted-Pair C, positive    |

| TPICN                    |                                        |                 |              |                  | Twisted-Pair C,<br>negative |

| TPIDP                    |                                        |                 |              |                  | Twisted-Pair D, positive    |

| TPIDN                    |                                        |                 |              |                  | Twisted-Pair D,<br>negative |

*Note:* 10/100/1000 Ethernet is supported beginning with the Intel Quartus Prime v17.1 software release.

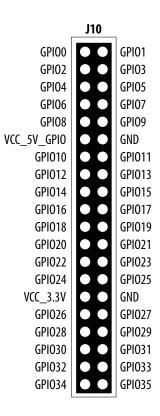

# 4.9.2. 2x20 GPIO Expansion Header

The Intel Cyclone 10 LP FPGA evaluation board provides one 40-pin expansion GPIO header with up to 36 GPIO signals. This 2x20 GPIO Header is compatible with some Terasic 2x20 GPIO cards.

There are also  $+5 \text{ V} (\text{VCC}_5\text{V}_G\text{PIO})$  and  $+3.3 \text{ V} (\text{VCC}_3.3\text{V})$  and two GND pins on 2x20 GPIO expansion header. All GPIO signals GPIO[0:35] are 3.3 V single-ended LVCMOS/LVTTL signals who are connected to Intel Cyclone 10 LP FPGA directly.

| Board Reference | Schematic Signal<br>Name | FPGA Pin Number | I/O Standard | Direction @ FPGA | Description     |

|-----------------|--------------------------|-----------------|--------------|------------------|-----------------|

| J10.1           | GPIO0                    | L13             | 3.3 V        | IO               | GPIO Signal 0   |

| J10.2           | GPI01                    | L16             | 3.3 V        | IO               | GPIO Signal 1   |

| J10.3           | GPIO2                    | L15             | 3.3 V        | IO               | GPIO Signal 2   |

| J10.4           | GPIO3                    | К16             | 3.3 V        | IO               | GPIO Signal 3   |

| J10.5           | GPIO4                    | P16             | 3.3 V        | IO               | GPIO Signal 4   |

| J10.6           | GPIO5                    | R16             | 3.3 V        | IO               | GPIO Signal 5   |

| J10.7           | GPI06                    | N16             | 3.3 V        | IO               | GPIO Signal 6   |

| J10.8           | GPIO7                    | N15             | 3.3 V        | IO               | GPIO Signal 7   |

| J10.9           | GPIO8                    | N14             | 3.3 V        | IO               | GPIO Signal 8   |

| J10.10          | GPIO9                    | P15             | 3.3 V        | IO               | GPIO Signal 9   |

| J10.11          | VCC_5V_GPIO              |                 |              |                  | Short to VCC_5V |

| J10.12          | GND                      |                 |              |                  | Ground          |

| J10.13          | GPIO10                   | N8              | 3.3 V        | IO               | GPIO Signal 10  |

| J10.14          | GPI011                   | P8              | 3.3 V        | IO               | GPIO Signal 11  |

| J10.15          | GPIO12                   | M8              | 3.3 V        | IO               | GPIO Signal 12  |

| J10.16          | GPIO13                   | L8              | 3.3 V        | IO               | GPIO Signal 13  |

| J10.17          | GPIO14                   | R7              | 3.3 V        | IO               | GPIO Signal 14  |

| J10.18          | GPIO15                   | Т7              | 3.3 V        | IO               | GPIO Signal 15  |

| J10.19          | GPIO16                   | L7              | 3.3 V        | IO               | GPIO Signal 16  |

| J10.20          | GPIO17                   | M7              | 3.3 V        | IO               | GPIO Signal 17  |

| J10.21          | GPIO18                   | R6              | 3.3 V        | Ю                | GPIO Signal 18  |

| J10.22          | GPIO19                   | Т6              | 3.3 V        | Ю                | GPIO Signal 19  |

| J10.23          | GPIO20                   | Т2              | 3.3 V        | Ю                | GPIO Signal 20  |

| J10.24          | GPIO21                   | M6              | 3.3 V        | Ю                | GPIO Signal 21  |

| J10.25          | GPIO22                   | R5              | 3.3 V        | Ю                | GPIO Signal 22  |

| J10.26          | GPIO23                   | Т5              | 3.3 V        | Ю                | GPIO Signal 23  |

|                 |                          |                 |              | ,                | continued       |

Table 15.

2X20 GPIO Header Signals

# intel.

| Board Reference | Schematic Signal<br>Name | FPGA Pin Number | I/O Standard | Direction @ FPGA | Description    |

|-----------------|--------------------------|-----------------|--------------|------------------|----------------|

| J10.27          | GPIO24                   | N5              | 3.3 V        | Ю                | GPIO Signal 24 |

| J10.28          | GPIO25                   | N6              | 3.3 V        | Ю                | GPIO Signal 25 |

| J10.29          | VCC_3.3V                 |                 |              |                  | VCC_3.3V       |

| J10.30          | GND                      |                 |              |                  | Ground         |

| J10.31          | GPIO26                   | R4              | 3.3 V        | Ю                | GPIO Signal 26 |

| J10.32          | GPIO27                   | T4              | 3.3 V        | IO               | GPIO Signal 27 |

| J10.33          | GPIO28                   | N3              | 3.3 V        | Ю                | GPIO Signal 28 |

| J10.34          | GPIO29                   | Р3              | 3.3 V        | IO               | GPIO Signal 29 |

| J10.35          | GPIO30                   | R3              | 3.3 V        | Ю                | GPIO Signal 30 |

| J10.36          | GPIO31                   | Т3              | 3.3 V        | IO               | GPIO Signal 31 |

| J10.37          | GPIO32                   | Р6              | 3.3 V        | ю                | GPIO Signal 32 |

| J10.38          | GPIO33                   | P2              | 3.3 V        | IO               | GPIO Signal 33 |

| J10.39          | GPIO34                   | P1              | 3.3 V        | Ю                | GPIO Signal 34 |

| J10.40          | GPIO35                   | R1              | 3.3 V        | IO               | GPIO Signal 35 |

Figure 8. GPIO

The maximum power output capability is shown in the table below. When using 2x20 GPIO Header, USB may not provide sufficient power. Hence, use an external adapter connector (J12) to power up the board.

#### Table 16. 2X20 GPIO Header Power Output Capability

| PowerRail   | Output Pin Location | Max Current | Note                                                                       |

|-------------|---------------------|-------------|----------------------------------------------------------------------------|

| VCC_5V_GPIO | J10.11              | 0.5 A       | VCC_5V output capability to card (depends on the power adapter capability) |

| VCC_3.3V    | J10.29              | 0.5 A       | VCC_3.3V output capability to daughter card                                |

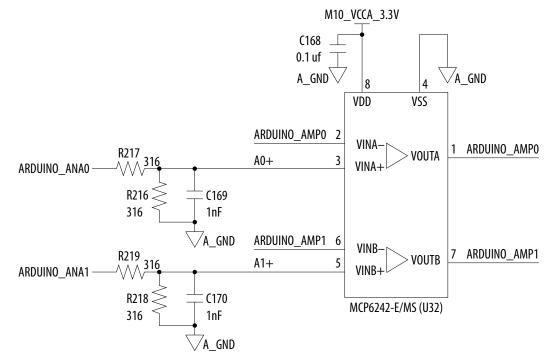

## **4.9.3. Arduino Connectors**

The Intel Cyclone 10 LP FPGA Evaluation Board features an Arduino UNO R3 type interface which is comprised of headers J4, J5, J6, J7, J18.

The header's location is compatible with Arduino UNO R3. This interface contains 17 digital IOs (include one Reset) and six Analog inputs.

The header's location and definition are shown in the figure below.

#### Figure 9. Arduino Connector

Intel<sup>®</sup> Cyclone<sup>®</sup> 10 LP FPGA Evaluation Kit User Guide

# intel.

## Table 17.Arduino Connector

| Header 1 (PWR)<br>J4.1NCJ4.2IOREFJ4.3ARDUINO_J4.4VCC_3.3VJ4.4VCC_5V_AJ4.5VCC_5V_AJ4.6GNDJ4.7GNDJ4.8NCJ6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GNDJ5.8ANA VREF                                                                                                                                                                                                                                                       |          |            | 1  |                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|----|----------------------------------------------------------|

| J4.3ARDUINO_J4.4VCC_3.3VJ4.5VCC_5V_AJ4.5GNDJ4.7GNDJ4.8NCJ4.8ARDUINO_J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                    |          |            |    |                                                          |

| J4.4VCC_3.3VJ4.5VCC_5V_AJ4.6GNDJ4.7GNDJ4.8NCHeader 2 (Analog)<br>J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J6.6ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                           |          |            |    | Connected to<br>VCC_3.3V                                 |

| J4.5VCC_5V_AJ4.6GNDJ4.7GNDJ4.8NCHeader 2 (Analog)<br>J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J6.6ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                       | _RSTn L3 | 3.3 V      | In | Arduino Reset<br>Input                                   |

| J4.6GNDJ4.7GNDJ4.7GNDJ4.8NCHeader 2 (Analog)<br>J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J6.6ARDUINO_J6.6ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                | 7        |            |    | 3.3 V Power for Arduino shield                           |

| J4.7         GND           J4.8         NC           Header 2 (Analog)         ARDUINO_           J6.1         ARDUINO_           J6.2         ARDUINO_           J6.3         ARDUINO_           J6.4         ARDUINO_           J6.5         ARDUINO_           J6.6         ARDUINO_           J6.6         ARDUINO_           J5.1         ARDUINO_           J5.2         ARDUINO_           J5.3         ARDUINO_           J5.4         ARDUINO_           J5.6         ARDUINO_           J5.7         GND | \R1      |            |    | 5 V Power for<br>Arduino shield<br>shared with<br>VCC_5V |

| J4.8 NC<br>Header 2 (Analog) ARDUINO_<br>J6.1 ARDUINO_<br>J6.2 ARDUINO_<br>J6.3 ARDUINO_<br>J6.4 ARDUINO_<br>J6.5 ARDUINO_<br>J6.6 ARDUINO_<br>J6.6 ARDUINO_<br>J5.1 ARDUINO_<br>J5.1 ARDUINO_<br>J5.3 ARDUINO_<br>J5.4 ARDUINO_<br>J5.5 ARDUINO_<br>J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                     |          |            |    |                                                          |

| Header 2 (Analog)<br>J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J6.6ARDUINO_J6.6ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                                                       |          |            |    |                                                          |

| J6.1ARDUINO_J6.2ARDUINO_J6.3ARDUINO_J6.4ARDUINO_J6.5ARDUINO_J6.6ARDUINO_J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                                                                            |          |            |    | Reserve option to<br>5 V                                 |

| J6.3 ARDUINO_<br>J6.4 ARDUINO_<br>J6.5 ARDUINO_<br>J6.6 ARDUINO_<br>J6.6 ARDUINO_<br>J5.1 ARDUINO_<br>J5.2 ARDUINO_<br>J5.3 ARDUINO_<br>J5.4 ARDUINO_<br>J5.5 ARDUINO_<br>J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                                                                                                | _ANA0    | <br>Analog | In | Arduino Analog<br>Channel 0                              |

| J6.4 ARDUINO_<br>J6.5 ARDUINO_<br>J6.6 ARDUINO_<br>Header 3 (Digital) ARDUINO_<br>J5.1 ARDUINO_<br>J5.2 ARDUINO_<br>J5.3 ARDUINO_<br>J5.4 ARDUINO_<br>J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                                                                                                                    | _ANA1    | Analog     | In | Arduino Analog<br>Channel 1                              |

| J6.5 ARDUINO_<br>J6.6 ARDUINO_<br>J6.6 ARDUINO_<br>J5.1 ARDUINO_<br>J5.2 ARDUINO_<br>J5.3 ARDUINO_<br>J5.4 ARDUINO_<br>J5.5 ARDUINO_<br>J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                                                                                                                                  | _ANA2    | Analog     | In | Arduino Analog<br>Channel 2                              |

| J6.6 ARDUINO_<br>Header 3 (Digital) ARDUINO_<br>J5.1 ARDUINO_<br>J5.2 ARDUINO_<br>J5.3 ARDUINO_<br>J5.4 ARDUINO_<br>J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                                                                                                                                                      | _ANA3    | Analog     | In | Arduino Analog<br>Channel 3                              |

| Header 3 (Digital)<br>J5.1ARDUINO_J5.2ARDUINO_J5.3ARDUINO_J5.4ARDUINO_J5.5ARDUINO_J5.6ARDUINO_J5.7GND                                                                                                                                                                                                                                                                                                                                                                                                              | _ANA4    | Analog     | In | Arduino Analog<br>Channel 4                              |

| J5.1     ARDUINO_       J5.2     ARDUINO_       J5.3     ARDUINO_       J5.4     ARDUINO_       J5.5     ARDUINO_       J5.6     ARDUINO_       J5.7     GND                                                                                                                                                                                                                                                                                                                                                       | _ANA5    | Analog     | In | Arduino Analog<br>Channel 5                              |

| J5.3     ARDUINO_       J5.4     ARDUINO_       J5.5     ARDUINO_       J5.6     ARDUINO_       J5.7     GND                                                                                                                                                                                                                                                                                                                                                                                                       | _IO8 K2  | 3.3 V      | IO | Arduino Digital Bi<br>8                                  |

| J5.4     ARDUINO_       J5.5     ARDUINO_       J5.6     ARDUINO_       J5.7     GND                                                                                                                                                                                                                                                                                                                                                                                                                               | _IO9 K5  | 3.3 V      | IO | Arduino Digital Bi<br>9                                  |

| J5.5         ARDUINO_           J5.6         ARDUINO_           J5.7         GND                                                                                                                                                                                                                                                                                                                                                                                                                                   | _IO10 L4 | 3.3 V      | IO | Arduino Digital Bi<br>10                                 |

| J5.6 ARDUINO_<br>J5.7 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _I011 K1 | <br>3.3 V  | IO | Arduino Digital 1                                        |

| J5.7 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _I012 L2 | 3.3 V      | IO | Arduino Digital 12                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _IO13 L1 | <br>3.3 V  | IO | Arduino Digital 1                                        |