## **MX93AUD-HAT Board User Manual**

Rev. 1 — 14 April 2023

**User manual**

#### **Document Information**

| Information | Content                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | MX93AUD-HAT-UM, i.MX 93                                                                                                                                                                                                         |

| Abstract    | The MX93AUD-HAT is an entry level audio evaluation platform that is fully compatible with the MCIMX93-EVK. It includes a multi-channel codec, S/PDIF, and microphone interfaces. This document supports Board Revision A and B. |

### 1 MX93AUD-HAT Overview

The MX93AUD-HAT is an entry level audio evaluation platform that is fully compatible with the MCIMX93-EVK. It includes a multi-channel codec, S/PDIF, and microphone interfaces.

For further information about MX93AUD-HAT, see http://www.nxp.com/.

### 1.1 Acronyms and abbreviations

The following table lists the acronyms and abbreviations used in this document.

Table 1. Acronyms and abbreviations

| Term             | Description                      |

|------------------|----------------------------------|

| ADC              | Analog-to-digital converter      |

| DAC              | Digital-to-analog converter      |

| I <sup>2</sup> S | Inter-IC sound                   |

| PDM              | Pulse density modulation         |

| S/PDIF           | Sony / Philips Digital InterFace |

| I <sup>2</sup> C | Inter-integrated circuit         |

| LDO              | Low dropout regulator            |

| LED              | Light-emitting diode             |

#### 1.2 Related documentation

The table below lists and explains the additional documents and resources that you can refer to for more information on the MX93AUD-HAT board. Some of the documents listed below may be available only under a non-disclosure agreement (NDA). To request access to these documents, contact your local field applications engineer (FAE) or sales representative.

Table 2. Related documentation

| Document                                                | Description                                                                                                                                                                                                                                                     | Link / how to access |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| i.MX 93 Applications Processor<br>Reference Manual      | Intended for system software and hardware developers and application programmers who want to develop products with i.MX 93 MPU                                                                                                                                  | IMX93RM              |

| i.MX 93 Industrial Application<br>Processors Data Sheet | Provides information about electrical characteristics, hardware design considerations, and ordering information                                                                                                                                                 | IMX93IEC             |

| i.MX93 Hardware Developer's<br>Guide                    | This document aims to help hardware engineers design and to test their i.MX 93 processor-based designs. It provides information about board layout recommendations and design checklists to ensure first-pass success and avoidance of board bring-up problems. | IMX93HDG             |

#### 1.3 Board kit contents

The table below lists the items included in the MX93AUD-HAT hardware kit.

MX93AUD-HAT-UM

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved.

Table 3. Board kit contents

| Item                       | Quantity |

|----------------------------|----------|

| MX93AUD-HAT                | 1        |

| Jumper sockets (installed) | 5        |

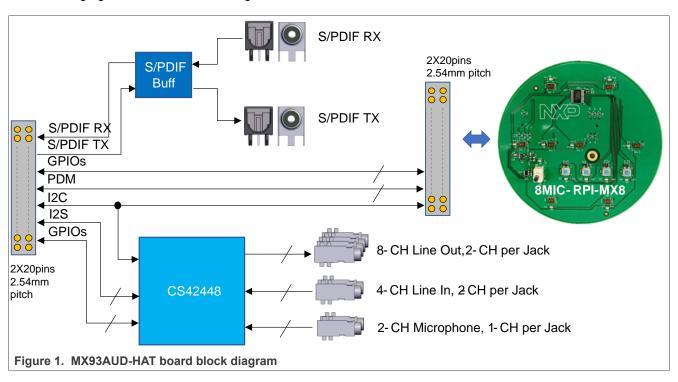

### 1.4 Block diagram

The following figure shows the block diagram of the MX93AUD-HAT board.

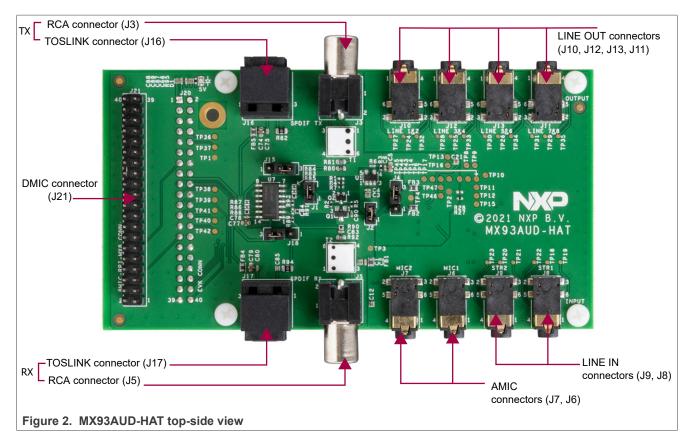

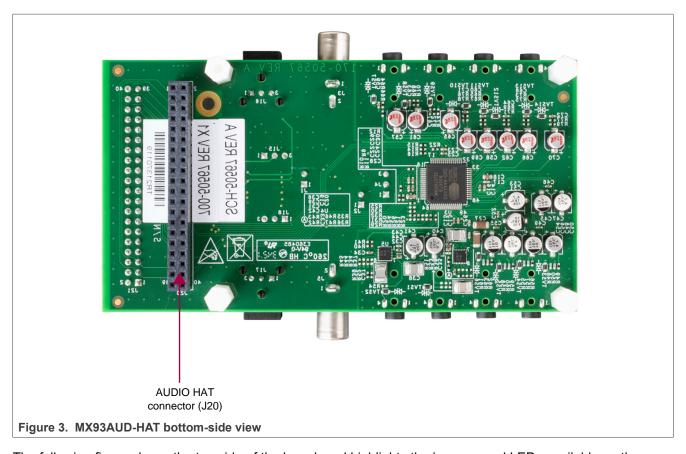

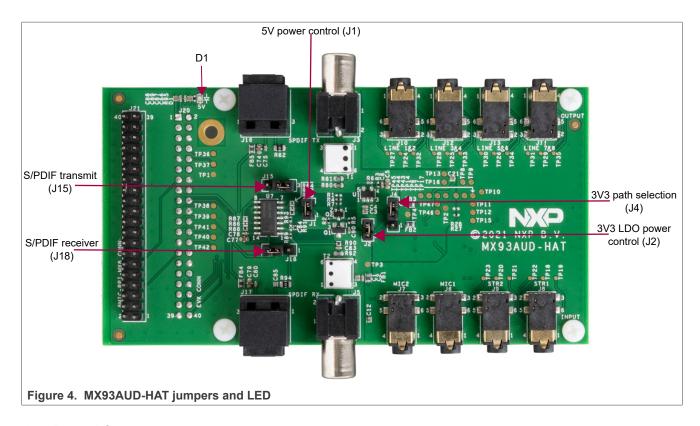

#### 1.5 Board pictures

The following figures show the top and bottom side of the MX93AUD-HAT board, and also highlight the connectors, jumpers, and LED available on the board.

The outline size of the board is 119 x 63 x 1.6 mm.

The following figure shows the top side of the board, and highlights the connectors available on the board (see Section 1.7 for detail).

The following figure shows the bottom side of the board, and highlights the connector available on bottom side of the board.

The following figure shows the top side of the board, and highlights the jumpers and LEDs available on the board (see<u>Section 1.8</u> and <u>Section 1.9</u> for detail).

#### 1.6 Board features

The table below lists the features of MX93AUD-HAT board.

Table 4. Board main features

| Board feature               | Processor feature used | Description                                                                                                                                    |

|-----------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Interfacing with Main board |                        | 40-pin connector used for MX93AUD-HAT board connection with the motherboard such as MCIMX93-EVK.                                               |

| Power                       | 3.3 V                  | MX93AUD-HAT board can be powered either by onboard 3.3 V or 3.3 V from motherboard.                                                            |

| 12C                         | I2C                    | MX93AUD-HAT is configured through the I2C interface at address 1001 000x.                                                                      |

| Audio                       | 12S                    | Supports one onboard codec CS42448 that provides six multi-bit analog-to-digital and eight multi-bit digital-to-analog delta-sigma converters. |

|                             | PDM                    | MX93AUD-HAT board supports one PDM interface (J21) to connect to the digital microphone board.                                                 |

|                             | S/PDIF                 | MX93AUD-HAT board provides two TOSLINK+RCA ports for S/PDIF receive and transmit.                                                              |

#### 1.7 Connectors

The following table describes the connectors available on the MX93AUD-HAT board.

**Table 5. Connectors**

| Part identifier | Connector type             | Description                                                                                                                                                                   |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J20             | 2x20-pin connector         | Audio Hat connector. It is 2.54 mm pitch, female connector, responsible for communication with motherboard, such as MCIMX93-EVK and so on. See Section 1.7.1 for more detail. |

| J21             | 2x20-pin connector         | It is used to provide PDM interface and is used for connection with digital microphone board 8MIC-RPI-MX8.                                                                    |

| J3              | RCA connector              | Coaxial cable connector for digital audio signals transmission                                                                                                                |

| J16             | TOSLINK connector          | Optical fiber connector for digital audio signals transmission                                                                                                                |

| J5              | RCA connector              | Coaxial cable receiver connector for digital audio signals                                                                                                                    |

| J17             | TOSLINK connector          | Optical fiber receiver connector for digital audio signals                                                                                                                    |

| J6              | PJ31360, 3.5 mm audio jack | Single-ended analog input connector for CS42448 audio                                                                                                                         |

| J7              |                            | codec (AIN5B/AIN5A/AIN6B/AIN6A pins)                                                                                                                                          |

| J8              |                            | Differential analog input connector for CS42448 audio                                                                                                                         |

| J9              |                            | codec (AIN1+/-, AIN2+/-, AIN3+/-, AIN4+/- pins)                                                                                                                               |

| J10             | PJ31360, 3.5 mm audio jack | CS42448 audio codec Line 1 and Line 2 analog output connector                                                                                                                 |

| J12             |                            | CS42448 audio codec Line 3 and Line 4 analog output connector                                                                                                                 |

| J13             |                            | CS42448 audio codec Line 5 and Line 6 analog output connector                                                                                                                 |

| J11             |                            | CS42448 audio codec Line 7 and Line 8 analog output connector                                                                                                                 |

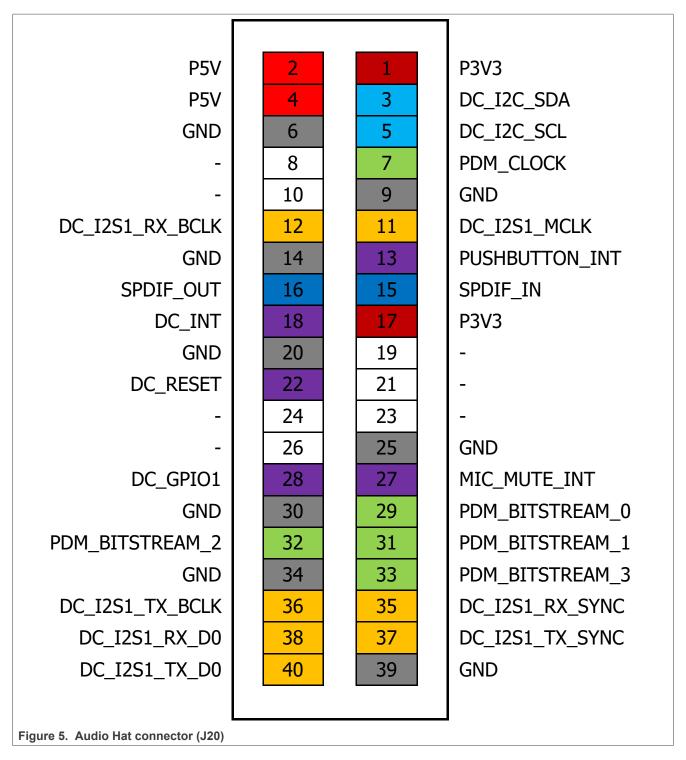

#### 1.7.1 Audio Hat connector

<u>Figure 5</u> shows the description of each pin of the 2x20-pin connector. This connector supports I2S, 4-lane PDM, S/PDIF I/O, I<sup>2</sup>C and some control pins, all signals are 3.3 V logic level.

<u>Table 6</u> describes the pin description of the J20 connector. All signals are grouped by functions and their directions are mentioned with respect to MX93AUD-HAT board.

Table 6. Audio Hat connector pin description with GPIO mapping

| Pin<br>Number           | Pin Name        | <b>GPIO Mapping</b> | I/O | Voltage<br>(V) | Description                                     |  |

|-------------------------|-----------------|---------------------|-----|----------------|-------------------------------------------------|--|

| 3                       | DC_I2C_SDA      | GPIO2_I2C4.SDA      | I/O | 3.3            | I <sup>2</sup> C bus                            |  |

| 5                       | DC_I2C_SCL      | GPIO3_I2C4.SCL      | I   | 3.3            |                                                 |  |

| 7                       | PDM_CLOCK       | GPIO4               | I   | 3.3            | PDM interface for 8MIC-RPI-MX8                  |  |

| 29                      | PDM_BITSTREAM_0 | GPIO5               | 0   | 3.3            | board                                           |  |

| 31                      | PDM_BITSTREAM_1 | GPIO6               | 0   | 3.3            |                                                 |  |

| 32                      | PDM_BITSTREAM_2 | GPIO12              | 0   | 3.3            |                                                 |  |

| 33                      | PDM_BITSTREAM_3 | GPIO13              | 0   | 3.3            |                                                 |  |

| 11                      | DC_I2S1_MCLK    | GPIO17              | I   | 3.3            | I2S interface, include 1-lane RX                |  |

| 12                      | DC_I2S1_RX_BCLK | GIO18               | I   | 3.3            | and 1-lane TX.  MX93AUD-HAT board (CS42448)     |  |

| 35                      | DC_I2S1_RX_SYNC | GPIO19              | I   | 3.3            | as slave device by default                      |  |

| 38                      | DC_I2S1_RX_D0   | GPIO20              | 0   | 3.3            |                                                 |  |

| 36                      | DC_I2S1_TX_BCLK | GPIO16              | I   | 3.3            |                                                 |  |

| 37                      | DC_I2S1_TX_SYNC | GPIO26              | I   | 3.3            |                                                 |  |

| 40                      | DC_I2S1_TX_D0   | GPIO21              | I   | 3.3            |                                                 |  |

| 15                      | SPDIF_IN        | GPIO22              | 0   | 3.3            | S/PDIF I/O                                      |  |

| 16                      | SPDIF_OUT       | GPIO23              | I   | 3.3            |                                                 |  |

| 13                      | PUSHBUTTON_INT  | GPIO27              | 0   | 3.3            | Button interrupt signal from 8MIC-RPI-MX8 board |  |

| 27                      | MIC_MUTE_INT    | GPIO0               | I   | 3.3            | Mute signal to 8MIC-RPI-MX8 board               |  |

| 18                      | DC_INT          | GPIO24              | 0   | 3.3            | CS42448 interrupt signal                        |  |

| 22                      | DC_RESET        | GPIO25              | I   | 3.3            | Reset CS42448, active low                       |  |

| 28                      | DC_GPIO1        | GPIO1               | I   | 3.3            | Power control signal, active high               |  |

| 1, 17                   | P3V3            | -                   | Pi  | 3.3            | 3.3 V power supply                              |  |

| 2,4                     | P5V             | -                   | Pi  | 5.0            | 5.0 V power supply                              |  |

| 9, 14, 20,<br>25,30, 39 | GND             | -                   | Р   | 0              | Ground                                          |  |

## 1.8 Jumpers

To facilitate the development and debugging and for the diversity of functions, some jumpers have been added to the MX93AUD-HAT board. The following table describes the jumpers available on the board.

Table 7. Jumper Description

| Part identifier | Jumper type | Name/Function     | Settings                                                                              |  |

|-----------------|-------------|-------------------|---------------------------------------------------------------------------------------|--|

| J1              | 1x2 header  | 5 V power control | Open: Disconnect 5 V power supply from<br>the motherboard to the MX93AUD-HAT<br>board |  |

Table 7. Jumper Description...continued

| Part identifier | Jumper type | Name/Function         | Settings                                                                                                                                  |

|-----------------|-------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                 |             |                       | Shorted: Connect 5 V power supply from<br>the motherboard to the MX93AUD-HAT<br>board [Default setting]                                   |

| J2              | 1x2 header  | 3V3 LDO power control | <ul> <li>Open: Disconnect 3.3 V LDO U1 input path</li> <li>Shorted: Connect 3.3 V LDO U1 input path<br/>[Default setting]</li> </ul>      |

| J4              | 1x3 header  | 3.3 V path selection  | <ul> <li>1-2 shorted: 3.3 V source from motherboard</li> <li>2-3 shorted: 3.3 V source from on board<br/>LDO (default setting)</li> </ul> |

| J15             | 1x3 header  | S/PDIF transmit       | 1-2 shorted: TOSLINK port is used for S/PDIF transmit     2-3 shorted: RCA port is used for S/PDIF transmit (default setting)             |

| J18             | 1x3 header  | S/PDIF receiver       | 1-2 shorted: TOSLINK port is used as S/PDIF receiver     2-3: RCA port is used as S/PDIF receiver (default setting)                       |

#### 1.9 **LED**

The MX93AUD-HAT board has one LED with detail as below:

- LED color Red

- Part Identifier D1

- LED name 5 V

- Description LED for 5 V power supply. When On, indicates that 5 V power supply is available on board.

## 2 Function Description

This chapter describes the features and different interfaces of MX93AUD-HAT board.

#### 2.1 Power

Two types of power supply paths are available on the MX93AUD-HAT board.

- For the first power supply path, source is motherboard that provides 5 V power to the board. The DC\_GPIO1 signal controls the 5 V supply to either ON or OFF. Setting DC\_GPIO1 as high, enables the 5 V supply on the board. The onboard LDO (U1) converts the 5 V power supply to 3.3 V power supply.

- For the second power supply path, motherboard supplies 3.3 V power direct to the board. The power supply path does not pass through onboard LDO (U1).

For both supply paths, it is ensured that the ripple is small enough and the PSRR is large enough, which is beneficial to the audio signal.

#### 2.2 Reset

The MX93AUD-HAT board is reset through DC\_RESET [GPIO25] input signal coming from motherboard through J20 connector.

Hold DC\_RESET signal low until the power supply and clocks are stable or a reset occurs after power up. If the analog or digital supplies drop below the recommended operating condition, it is recommended to activate the reset signal to prevent power-glitch-related issues. A time delay of approximately 400 ms is required after applying power to the device or after exiting a reset state.

#### 2.3 I2C

The MX93AUD-HAT board is configured through the I2C interface at address 1001 000x. The default address can be changed using pins AD0/CS and AD1/CDIN of the CS42448 codec (U3). For more detail, refer to the MX93AUD-HAT board schematics.

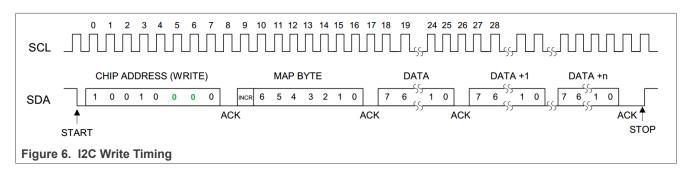

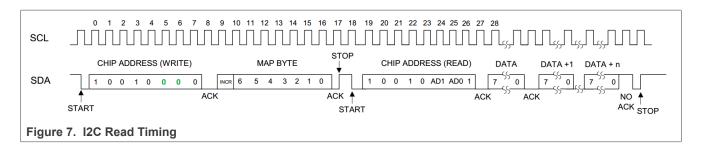

I<sup>2</sup>C bus on this board supports standard speed mode 100 kHz. The signal timings for a read and write cycle are shown in <u>Figure 6</u> and <u>Figure 7</u>. A Start condition is defined as a falling transition of SDA while the clock is high. A Stop condition is a rising transition while the clock is high. All other transitions of SDA occur while the clock is low.

MX93AUD-HAT-UM

#### 2.4 I2S

I<sup>2</sup>S (Inter-IC Sound) provides audio processing feature. It is an electrical serial bus interface standard used for connecting digital audio devices together. The ADC and DAC serial ports of the audio codec CS42448 available on this board support the I<sup>2</sup>S, Left-Justified, Right-Justified, One-Line Mode (OLM), and TDM digital interface formats with varying bit depths from 16 to 32. The I2S interface of ADC consists of SCLK, LRCK, and one-lane SDOUT and the I2S interface of DAC consists of SCLK, LRCK, and one-lane SDIN. The below table describes the audio feature summary.

Table 8. Audio feature summary

| Digital input/output | Interface format         | Analog output/input channel allocation form/to digital I/O   |

|----------------------|--------------------------|--------------------------------------------------------------|

| ADC_SDOUT1           | I <sup>2</sup> S, LJ, RJ | AIN 1, 2                                                     |

|                      | OLM                      | AIN 1, 2, 3, 4, 5, 6                                         |

|                      | TDM                      | AIN 1, 2, 3, 4, 5, 6 (two additional channels from AUX_SDIN) |

| DAC_SDIN1            | I <sup>2</sup> S, LJ, RJ | AOUT 1, 2                                                    |

|                      | OLM                      | AOUT 1, 2, 3, 4, 5, 6                                        |

|                      | TDM                      | AOUT 1, 2, 3, 4, 5, 6, 7, 8                                  |

#### **2.5 S/PDIF**

S/PDIF (Sony/Phillips Digital Interface) is a consumer audio connection standard for transmitting high-quality digital audio. It can carry two channels of uncompressed PCM audio or compressed 5.1/7.1 surround sound such as Dolby Digital or DTS audio. The S/PDIF interface and the associated connectors can be implemented in two different ways "optical and coaxial". On MX93AUD-HAT board, it supports two pairs of RCA and TOSLINK connectors (see Section 1.7). The NRZ signal transmission speed of TOSLINK connectors can support 25 Mbit/s. Different communication media can be switched with J15 and J18. For detail, see Section 1.8.

#### 2.6 PDM

PDM (Pulse density modulation) is a form of modulation used to represent an analog signal in the digital domain. It is a high frequency stream of 1-bit digital samples. In a PDM signal, the relative density of the pulses corresponds to the analog signal's amplitude.

The PDM interface is available on the MX93AUD-HAT board at J21 connector, it supports 4-lane data with one clock. The digital microphone board 8MIC-RPI-MX8 can be connected to this connector.

MX93AUD-HAT-UM

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved

MX93AUD-HAT Board User Manual

## 3 Board Errata

None

## 4 Revision history

The following table summarizes revisions to this document.

Table 9. Revision history

| Revision | Date          | Topic cross-reference | Description            |

|----------|---------------|-----------------------|------------------------|

| 1        | 14 April 2023 | -                     | Initial public release |

## 5 Legal information

#### 5.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** - NXP B.V. is not an operating company and it does not distribute or sell products.

#### 5.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

MX93AUD-HAT-UM

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved.

#### **MX93AUD-HAT Board User Manual**

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINK-pro, µVision, Versatile — are trademarks and/or registered trademarks of Arm Limited (or its subsidiaries or affiliates) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

i.MX — is a trademark of NXP B.V.

### **MX93AUD-HAT Board User Manual**

## **Contents**

| 1     | MX93AUD-HAT Overview       | 2  |

|-------|----------------------------|----|

| 1.1   | Acronyms and abbreviations | 2  |

| 1.2   | Related documentation      |    |

| 1.3   | Board kit contents         | 2  |

| 1.4   | Block diagram              | 3  |

| 1.5   | Board pictures             | 3  |

| 1.6   | Board features             | 6  |

| 1.7   | Connectors                 | 6  |

| 1.7.1 | Audio Hat connector        | 7  |

| 1.8   | Jumpers                    | 9  |

| 1.9   | LED                        | 10 |

| 2     | Function Description       | 11 |

| 2.1   | Power                      | 11 |

| 2.2   | Reset                      | 11 |

| 2.3   | I2C                        | 11 |

| 2.4   | I2S                        | 12 |

| 2.5   | S/PDIF                     | 12 |

| 2.6   | PDM                        | 12 |

| 3     | Board Errata               | 13 |

| 4     | Revision history           | 14 |

| 5     | Legal information          | 15 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.