# Embedded Package on Package ePOP

$e^{\bullet}MMC^{TM}5.1 HS400 + LPDDR3$

08EP08-N3GTC32-GA67

Datasheet v1.1

Kingston Digital Inc.

# **Contents**

Section 1 <u>Product Overview & Packaging</u>

Section 2 <u>Embedded Multi-Media Card</u>

Section 3 Low Power Double Data Rate DRAM (LPDDR3)

Section 4 <u>Revision History</u>

# **Section 1**

Product Overview & Packaging

#### **Product Features**

- Embedded Multi-Media storage and LPDDR3 DRAM combined into a single Multi-Chip package

- Package: JEDEC 136 ball FBGA Type –10.0 mm x 10.0 mm x (Max 0.85mm)

- Operating temperature range: -25°C to +85°C

## Introduction

The ePOP device is a Multi-Chip Package Memory device which combines JEDEC, JESD84-B51, embedded MultiMediaCard (e•MMC<sup>TM</sup>) and Low Power DDR3 Synchronous Dynamic RAM (JESD209-3B). The e•MMC<sup>TM</sup> part is an embedded flash memory storage solution with an e•MMC<sup>TM</sup> interface. The e•MMC<sup>TM</sup> controller directly manages NAND flash, including error control, wear-leveling, IOPS optimization and read sensing.

The device is suitable for use in data memory of mobile communication systems to reduce not only PCB size but also power consumption. This device is available in 136-ball FBGA Type.

| Product<br>Part number | NAND<br>Density | DRAM<br>Density | CH & CS<br>DRAM | Package | Nominal Operating voltage                                      |

|------------------------|-----------------|-----------------|-----------------|---------|----------------------------------------------------------------|

| 08EP08-N3GTC32-GA67    | 08GB            | 08Gb            | 1CH,2CS         | FBGA136 | VCC=3.3V, VCCQ=1.8V/3.3V,<br>VDD1 = 1.8V,<br>VDD2, VDDQ = 1.2V |

**Table 1-1 Device Summary**

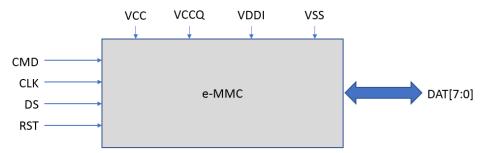

## **Device Block Diagram**

Figure 1-1 Device Block Diagram

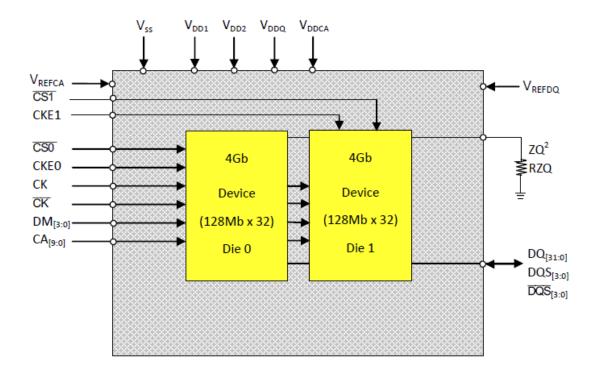

Figure 1-2 LPDDR3 Block Diagram

# $Operating\ Temperature\ Range$

**Table 1-2 Device Operating Temperature**

| Parameter             | Rating                  | Unit | Note |

|-----------------------|-------------------------|------|------|

| Operating temperature | <b>-25</b> ∼ <b>+85</b> | °C   |      |

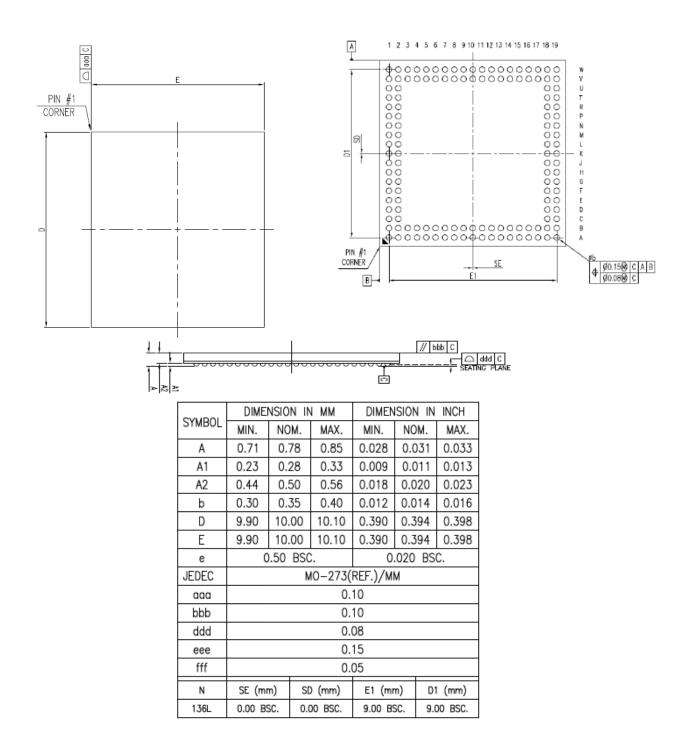

## Package Mechanical

$10.0 \times 10.0 \times (Max \ 0.85mm)$

**Table 1-3 Device Package Dimensions**

# Ball Assignment (136 ball)

|   | 1     | 2        | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10     | 11   | 12   | 13   | 14   | 15   | 16   | 17   | 18       | 19     |

|---|-------|----------|------|------|------|------|------|------|------|--------|------|------|------|------|------|------|------|----------|--------|

| Α | DNU   | VSSm     | DS   | CLK  | DAT7 | VCCQ | DAT4 | DAT3 | vccq | DAT0   | VSS  | VDDQ | DQ29 | DQ28 | VSS  | DQ26 | DQ24 | VSS      | DNU    |

| В | VSS   | VCC      | VDDI | VSSm | DAT6 | DAT5 | VSSm | VCC  | DAT2 | DAT1   | VSSm | DQ31 | DQ30 | VDDQ | DQ27 | DQ25 | VDDQ | VDD1     | VSS    |

| С | ZQ    | CMD      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQS3_t   | DQS3_c |

| D | CA9   | RST_n    |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDD2     | DM3    |

| E | CA8   | VDDCA    |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQ15     | VSS    |

| F | VSS   | CA7      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDDQ     | DQ14   |

| G | CA6   | VDD2     |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQ12     | DQ13   |

| Н | CA5   | VDD1     |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQ11     | VSS    |

| J | VSS   | Vref(CA) |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDDQ     | DQ10   |

| К | CK_t  | CK_c     |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQ9      | DQ8    |

| L | VSS   | VDD2     |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDDQ     | VSS    |

| М | CKE1  | VSS      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQS1_t   | DQS1_c |

| N | CKE0  | CS1_n    |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VSS      | DM1    |

| Р | CA4   | CSO_n    |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDD1     | VDD2   |

| R | VDDCA | CA3      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | Vref(DQ) | VSS    |

| Т | CA2   | VSS      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | VDDQ     | DM0    |

| U | CA1   | CA0      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      | DQS0_t   | DQS0_c |

| ٧ | VSS   | VDD1     | VDD2 | DQ17 | DQ18 | VSS  | DQ21 | DQ22 | VSS  | DQS2_t | VDDQ | DQ0  | VDDQ | DQ3  | DQ4  | VSS  | DQ7  | VDDQ     | VSS    |

| w | DNU   | VSS      | VSS  | DQ16 | VDDQ | DQ19 | DQ20 | VDDQ | DQ23 | DQS2_c | DM2  | VSS  | DQ1  | DQ2  | VDD2 | DQ6  | DQ5  | VSS      | DNU    |

|   |       |          |      |      |      |      |      |      |      |        |      |      |      |      |      |      |      |          |        |

ASSIGNMENT (TOP VIEW)

# **Device Marking**

# Kingston

240xxxx-xxx.xxxxx YYWW

XXXXXXX-XXXX

**XXXXXX**

TAIWAN

Kingston logo

240xxxx-xxx.xxxxxx : Internal control number

YYWW: Date code (YY-Last 2 digital of year, WW-Work week)

PPPPPPPP: Internal control number

xxxxxxx-xxxx Sales P/N

xxxxxxx : Internal control number

Country: TAIWAN

# **Section 2**

Embedded Multi-Media Card (e•MMC 5.1)

#### **Product Features**

- Packaged managed NAND flash memory with *e*•MMC<sup>™</sup> 5.1 interface

- Backward compatible with all prior e•MMC<sup>TM</sup> specification revisions

- Operating voltage range:

- $\circ$  VCCQ = 3.3V / 1.8 V

- $\circ$  VCC = 3.3 V

- Operating Temperature (T<sub>case</sub>) 25C to +85C

- Storage Temperature -40C to +85C

- Compliant with e•MMC™ 5.1 JEDEC Standard Number JESD84-B51

#### e•MMC<sup>TM</sup> Specific Feature Support

- High-speed *e*•MMC<sup>™</sup> protocol

- Variable clock frequencies of 0-200MHz

- Ten-wire bus interface (clock, 1 bit command, 8 bit data bus) with an optional hardware reset

- Supports three different data bus widths: 1 bit(default), 4 bits, 8 bits

- Bus Modes:

- o Single data transfer rate: up to 52MB/s (using 8 parallel data lines at 52MHz)

- O Dual data rate mode (DDR-104): up to 104MB/s @ 52MHz

- o High speed, single data rate mode (HS-200): up to 200MB/s @ 200MHz

- o High speed, dual data rate mode (HS-400): up to 400MB/s @ 200MHz

- Supports alternate boot operation mode to provide a simple boot sequence method

- Supports SLEEP/AWAKE (CMD5)

- Host initiated explicit sleep mode for power saving

- Enhanced write protection with permanent and partial write protection options

- Multiple user data partition with enhanced attribute for increased reliability

- Error free memory access

- o Cyclic Redundancy Code (CRC) for reliable command and data communication

- o Internal error correction code (ECC) for improved data storage integrity

- o Internal enhanced data management algorithm

- Data protection for sudden power failure during program operations

- Security

- Secure block erase commands

- Enhanced write protection with permanent and partial protection options

- Power off notification

- Field firmware update (FFU)

- Production state awareness

- Device health report

- Command queuing

- Enhanced strobe

- Cache flushing report

- Cache barrier

- Background operation control & High Priority Interrupt (HPI)

- RPMB throughput improvement

- Secure write protection

- Pre EOL information

- Optimal size

## **Product Description**

Kingston's e•MMC<sup>TM</sup> products conform to the JEDEC e•MMC<sup>TM</sup> 5.1 standard. These devices are an ideal universal storage solution for many commercial and industrial applications. In a single integrated packaged device, e•MMC<sup>TM</sup> combines triple-level cell (TLC) NAND flash memory with an onboard e•MMC<sup>TM</sup> controller, providing an industry standard interface to the host system. The integrated e•MMC<sup>TM</sup> controller directly manages NAND flash media which relieves the host processor of these tasks, including flash media error control, wear-leveling, NAND flash management and performance optimization. Future revision to the JEDEC e•MMC<sup>TM</sup> standard will always maintain backward compatibility. The industry standard interface to the host processor ensures compatibility across future NAND flash generations as well, easing product sustainment throughout the product life cycle.

#### **Device Performance**

Table 2-1 below provides sequential read and write speeds for all capacities. Performance numbers can vary under different operating conditions. Values are given at HS400 bus mode.

| Duo duo4            | Typical value          |                         |  |  |  |  |  |

|---------------------|------------------------|-------------------------|--|--|--|--|--|

| Product             | Read Sequential (MB/s) | Write Sequential (MB/s) |  |  |  |  |  |

| 08EP08-N3GTC32-GA67 | 280                    | 110                     |  |  |  |  |  |

- Note 1: Values given for an 8-bit bus width, running HS400 mode from KSI proprietary tool,  $V_{CC}=3.3V$ ,  $V_{CCQ}=1.8V$ .

- Note 2: For performance numbers under other test conditions, please contact KSI representatives.

- Note 3: Performance numbers might be subject to changes without notice.

| Duoduot             | Dynamic booster value  |                         |  |  |  |  |  |

|---------------------|------------------------|-------------------------|--|--|--|--|--|

| Product             | Read Sequential (MB/s) | Write Sequential (MB/s) |  |  |  |  |  |

| 08EP08-N3GTC32-GA67 | 280                    | 115                     |  |  |  |  |  |

Note 1: KSI adopt force-PSA for one-third user capacity in eMMC first write-cycle ,Values is measured by KSI proprietary tool with 8-bits bus width and DDR 200 MHz , without file system over head.

Note 2: PSA refer to JESD84-B51 6.6.17

Table 2-1 - Sequential Read / Write Performance

## **Power Consumption**

Device current consumption for various device configurations is defined in the power class fields of the EXT\_CSD register. Power consumption values are summarized in Table 2-2 below.

| Product             | Read       | (mA)      | Write      | e(mA)     | Standby(mA) |           |  |

|---------------------|------------|-----------|------------|-----------|-------------|-----------|--|

| Troduct             | VCCQ(1.8V) | VCC(3.3V) | VCCQ(1.8V) | VCC(3.3V) | VCCQ(1.8V)  | VCC(3.3V) |  |

| 08EP08-N3GTC32-GA67 | 99.44      | 88.37     | 34.44      | 48.32     | 0.050       | 0.035     |  |

Note 1: Values given for an 8-bit bus width, a clock frequency of 200MHz DDR mode, V<sub>CC</sub>=3.3V±5%, V<sub>CCO</sub>=1.8V±5%

Note 2: Standby current is measured at Vcc=3.3V±5%, 8-bit bus width without clock frequency.

Note 3: Current numbers might be subject to changes without notice.

**Table 2-2 - Device Power Consumption**

## **Device and Partition Capacity**

The device NAND flash capacity is divided across two boot partitions (4096 KB each), a Replay Protected Memory Block (RPMB) partition (4096 KB), and the main user storage area. Four additional general purpose storage partitions can be created from the user partition. These partitions can be factory preconfigured or configured in-field by following the procedure outlined in section 6.2 of the JEDEC e•MMC<sup>TM</sup> specification JESD84-B51. A small portion of the NAND storage capacity is used for the storage of the onboard controller firmware and mapping tables. Additionally, several NAND blocks are held in reserve to boost performance and extend the life of the e•MMC<sup>TM</sup> device. Table 2-3dentifies the specific capacity of each partition. This information is reported in the device EXT\_CSD register. The contents of this register are also listed in the Appendix.

| Product | User density                | Boot partition 1 | Boot partition 2 | RPMB    |

|---------|-----------------------------|------------------|------------------|---------|

| 8GB     | <b>8GB</b> 7851737088 Bytes |                  | 4096 KB          | 4096 KB |

**Table 2-3 - Partition Capacity**

Table 2-4 - e•MMC<sup>TM</sup> Operating Voltage

| Parameter                                | Symbol                                                                                                | Min | Nom | Max  | Unit |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|

| Supply voltage (NAND)                    | $V_{CC}$                                                                                              | 2.7 | 3.3 | 3.6  | V    |  |  |  |

| Supply volto as (I/O)                    | V <sub>CCQ</sub> (1)                                                                                  | 2.7 | 3.3 | 3.6  | V    |  |  |  |

| Supply voltage(I/O)                      | V CCQ \                                                                                               | 1.7 | 1.8 | 1.95 | V    |  |  |  |

| Supply power-up for 3.3 V                | $t_{ m PRUH}$                                                                                         |     |     | 35   | ms   |  |  |  |

| Supply power-up for 1.8V                 | $t_{PRUL}$                                                                                            |     |     | 25   | ms   |  |  |  |

| Note 1: $V_{CCO}(I/O)$ 3.3 volt range is | Note 1: V <sub>CCO</sub> (I/O) 3.3 volt range is not supported while operating in HS200 & HS400 modes |     |     |      |      |  |  |  |

## e•MMC<sup>TM</sup> Bus Modes

Kingston e•MMC<sup>TM</sup> devices support all bus modes defined in the JEDEC e•MMC<sup>TM</sup> 5.1 specification. These modes are summarized in Table 2-5 below.

Table 2-5 - e•MMC<sup>TM</sup> Bus Modes

| Mode           | Data Rate | IO Voltage  | Bus Width | CLK Frequency        | Maximum Data<br>Bus Throughput |

|----------------|-----------|-------------|-----------|----------------------|--------------------------------|

| Legacy MMC     | Single    | 3.3V / 1.8V | 1, 4, 8   | $0-26~\mathrm{MHz}$  | 26 MB/s                        |

| High Speed SDR | Single    | 3.3V / 1.8V | 4, 8      | 0 – 52 MHz           | 52 MB/s                        |

| High Speed DDR | Dual      | 3.3V / 1.8V | 4, 8      | 0 – 52 MHz           | 104 MB/s                       |

| HS200          | Single    | 1.8V        | 4, 8      | $0-200~\mathrm{MHz}$ | 200 MB/s                       |

| HS400          | Dual      | 1.8V        | 8         | 0 – 200 MHz          | 400 MB/s                       |

# **Signal Description**

Table 2-6a - e•MMC<sup>TM</sup> Signals

| Name     | Type   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK      | I      | Clock: Each cycle of this signal directs a one bit transfer on the command and either a one bit $(1x)$ or a two bits transfer $(2x)$ on all the data lines. The frequency may vary between zero and the maximum clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DAT[7:0] | I/O/PP | Data: These are bidirectional data channels. The DAT signals operate in push-pull mode. These bidirectional signals are driven by either the e•MMC <sup>TM</sup> device or the host controller. By default, after power up or reset, only DAT0 is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0-DAT7, by the e•MMC <sup>TM</sup> host controller. The e•MMC <sup>TM</sup> device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the device disconnects the internal pull-ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode, the device disconnects the internal pull-ups of lines DAT1-DAT7. |

Table 2-6b - e•MMC<sup>TM</sup> Signals (continued)

| Name  | Type      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD   | I/O/PP/OD | Command: This signal is a bidirectional command channel used for device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the e•MMC <sup>TM</sup> host controller to the e•MMC <sup>TM</sup> device and responses are sent from the device to the host.                                                                                                              |

| DS    | 0         | This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data - one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status and CMD Response are latched on the positive edge only, and don't care on the negative edge. |

| RST_n | I         | Hardware Reset: By default, hardware reset is disabled and must be enabled in the EXT_CSD register if used. Otherwise, it can be left un-connected.                                                                                                                                                                                                                                                                                                                                                     |

| RFU   | -         | Reserved for future use: These pins are not internally connected. Leave floating                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NC    | -         | Not Connected: These pins are not internally connected. Signals can be routed through these balls to ease printed circuit board design. See Kingston's Design Guidelines for further details.                                                                                                                                                                                                                                                                                                           |

| VSF   | -         | Vendor Specific Function: These pins are not internally connected                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vddi  | -         | Internal Voltage Node: Note that this is not a power supply input. This pin provides access to the output of an internal voltage regulator to allow for the connection of an external Creg capacitor. See Kingston's Design Guidelines for further details.                                                                                                                                                                                                                                             |

| Vcc   | S         | Supply voltage for core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Vccq  | S         | Supply voltage for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vss   | S         | Supply ground for core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vssq  | S         | Supply ground for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **Design Guidelines**

Design guidelines are outlined in a separate document. Contact your KSI Representative for more information.

## **Card Identification Register (CID)**

The Card Identification (CID) register is a 128-bit register that contains device identification information used during the  $e^{\bullet}MMC^{TM}$  protocol device identification phase. Refer to JEDEC Standard Specification No.JESD84-B51 for details.

| Field    | Byte      | Value                  |

|----------|-----------|------------------------|

| MID      | [127:120] | 0x70                   |

| reserved | [119:114] | 0x00                   |

| CBX      | [113:112] | 0x01                   |

| OID      | [111:104] | 0x00                   |

| PNM      | [103:56]  | JU8MP8                 |

| PRV      | [ 55:48 ] | 0x67                   |

| PSN      | [ 47:16 ] | Random                 |

| MDT      | [ 15:8 ]  | month, year            |

| CRC      | [ 7:1 ]   | Follows JEDEC Standard |

| reserved | [ 0:0 ]   | 0x01                   |

# **Card Specific Data Register [CSD]**

The Card-Specific Data (CSD) register provides information on how to access the contents stored in  $e^{\bullet}MMC^{TM}$ . The CSD registers are used to define the error correction type, maximum data access time, data transfer speed, data format...etc. For details, refer to section 7.3 of the JEDEC Standard Specification No.JESD84-B51.

| Field              | Byte      | Value            |

|--------------------|-----------|------------------|

| CSD_Structure      | [127:126] | 0x03 (V2.0)      |

| SPEC_VER           | [125:122] | 0x04 (V4.0~4.2)  |

| reserved           | [121:120] | 0x00             |

| TAAC               | [119:112] | 0x4F (40ms)      |

| NSAC               | [111:104] | 0x01             |

| TRAN_SPEED         | [103:96]  | 0x32 (26Mbit/s)  |

| CCC                | [ 95:84 ] | 0x8F5            |

| READ_BL_LEN        | [ 83:80 ] | 0x09 (512 Bytes) |

| READ_BL_PARTIAL    | [ 79:79 ] | 0x00             |

| WRITE_BLK_MISALIGN | [ 78:78 ] | 0x00             |

| READ_BLK_MISALIGN  | [ 77:77 ] | 0x00             |

| DSR_IMP            | [ 76:76 ] | 0x00             |

| reserved           | [ 75:74 ] | 0x00             |

| C_SIZE             | [ 73:62 ] | 0xFFF            |

| VDD_R_CURR_MIN     | [ 61:59 ] | 0x07 (100mA)     |

| VDD_R_CURR_MAX     | [ 58:56 ] | 0x07 (200mA)     |

| VDD_W_CURR_MIN     | [ 55:53 ] | 0x07 (100mA)     |

| VDD_W_CURR_MAX     | [ 52:50 ] | 0x07 (200mA)     |

| C_SIZE_MULT        | [ 49:47 ] | 0x07 (512 Bytes) |

| ERASE_GRP_SIZE     | [ 46:42 ] | 0x1F             |

| ERASE_GRP_MULT     | [ 41:37 ] | 0x1F             |

| WP_GRP_SIZE        | [ 36:32 ] | 0x0F             |

| WP_GRP_ENABLE      | [31:31]   | 0x01             |

| DEFAULT_ECC        | [ 30:29 ] | 0x00             |

| R2W_FACTOR         | [ 28:26 ] | 0x02             |

| WRITE_BL_LEN       | [ 25:22 ] | 0x09 (512 Bytes) |

| WRITE_BL_PARTIAL   | [21:21]   | 0x00             |

| reserved           | [ 20:17 ] | 0x00             |

| CONTENT_PROT_APP   | [ 16:16 ] | 0x00             |

| FILE_FORMAT_GRP    | [ 15:15 ] | 0x00             |

| СОРҮ               | [ 14:14 ] | 0x00             |

| PERM_WRITE_PROTECT | [ 13:13 ] | 0x00             |

| TMP_WRITE_PROTECT  | [ 12:12 ] | 0x00             |

| FILE_FORMAT        | [11:10]   | 0x00             |

| Field    | Byte    | Value                 |

|----------|---------|-----------------------|

| ECC      | [ 9:8 ] | 0x00                  |

| CRC      | [ 7:1 ] | Follow JEDEC Standard |

| reserved | [ 0:0 ] | 0x01                  |

# **Extended Card Specific Data Register [EXT\_CSD]**

The Extended CSD register defines the Device properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host by means of the SWITCH command. For details, refer to section 7.4 of the JEDEC Standard Specification No.JESD84-B51.

| Name    | Width (Bytes) | Description                                                                                                                       | Implementation |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| CID     | 16            | Device Identification number, an individual number for identification.                                                            | Mandatory      |

| RCA     | 2             | Relative Device Address is the Device system address, dynamically assigned by the host during initialization.                     | Mandatory      |

| DSR     | 2             | Driver Stage Register, to configure the Device's output drivers.                                                                  | Optional       |

| CSD     | 16            | Device Specific Data, information about the Device operation conditions.                                                          | Mandatory      |

| OCR     | 4             | Operation Conditions Register. Used by a special broadcast command to identify the voltage type of the Device.                    | Mandatory      |

| EXT_CSD | 512           | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in standard v4.0 | Mandatory      |

**Table 2-6 eMMC Registers**

| Field                                     | Byte      | Value |

|-------------------------------------------|-----------|-------|

| Reserved                                  | [511:506] | 0     |

| EXT_SECURITY_ERR                          | [505:505] | 0x00  |

| S_CMD_SET                                 | [504:504] | 0x01  |

| HPI_FEATURES                              | [503:503] | 0x01  |

| BKOPS_SUPPORT                             | [502:502] | 0x01  |

| MAX_PACKED_READS                          | [501:501] | 0x3F  |

| MAX_PACKED_WRITES                         | [500:500] | 0x20  |

| DATA_TAG_SUPPORT                          | [499:499] | 0x01  |

| TAG_UNIT_SIZE                             | [498:498] | 0x03  |

| TAG_RES_SIZE                              | [497:497] | 0x00  |

| CONTEXT_CAPABILITIES                      | [496:496] | 0x05  |

| LARGE_UNIT_SIZE_M1                        | [495:495] | 0x23  |

| EXT_SUPPORT                               | [494:494] | 0x03  |

| SUPPORTED_MODES                           | [493:493] | 0x01  |

| FFU_FEATURES                              | [492:492] | 0x00  |

| OPERATION_CODE_TIMEOUT                    | [491:491] | 0x00  |

| FFU_ARG                                   | [490:487] | 65535 |

| BARRIER_SUPPORT                           | [486:486] | 0x01  |

| Reserved                                  | [485:309] | 0     |

| CMDQ_SUPPORT                              | [308:308] | 0x01  |

| CMDQ_DEPTH                                | [307:307] | 0x1F  |

| Reserved                                  | [306:306] | 0x00  |

| NUMBER_OF_FW_SECTORS_CORRECTLY_PROGRAMMED | [305:302] | 0     |

| VENDOR_PROPRIETARY_HEALTH_REPORT          | [301:270] | 0     |

| DEVICE_LIFE_TIME_EST_TYP_B                | [269:269] | 0x01  |

| DEVICE_LIFE_TIME_EST_TYP_A                | [268:268] | 0x01  |

| PRE_EOL_INFO                              | [267:267] | 0x01  |

| OPTIMAL_READ_SIZE                         | [266:266] | 0x01  |

| OPTIMAL_WRITE_SIZE                        | [265:265] | 0x08  |

| OPTIMAL_TRIM_UNIT_SIZE                    | [264:264] | 0x01  |

| DEVICE_VERSION                            | [263:262] | 0     |

| FIRMWARE_VERSION                          | [261:254] | 0x67  |

| PWR_CL_DDR_200_360                        | [253:253] | 0x00  |

| CACHE_SIZE                                | [252:249] | 512   |

| GENERIC_CMD6_TIME                         | [248:248] | 0x32  |

| POWER_OFF_LONG_TIME                       | [247:247] | 0xFF  |

| BKOPS_STATUS                              | [246:246] | 0x00  |

| CORRECTLY_PRG_SECTORS_NUM                 | [245:242] | 0     |

| INI_TIMEOUT_AP                            | [241:241] | 0x64  |

| CACHE_FLUSH_POLICY                        | [240:240] | 0x01  |

| Field                              | Byte      | Value    |

|------------------------------------|-----------|----------|

| PWR_CL_DDR_52_360                  | [239:239] | 0x00     |

| PWR_CL_DDR_52_195                  | [238:238] | 0x00     |

| PWR_CL_200_195                     | [237:237] | 0x00     |

| PWR_CL_200_130                     | [236:236] | 0x00     |

| MIN_PERF_DDR_W_8_52                | [235:235] | 0x00     |

| MIN_PERF_DDR_R_8_52                | [234:234] | 0x00     |

| Reserved                           | [233:233] | 0x00     |

| TRIM_MULT                          | [232:232] | 0x05     |

| SEC_FEATURE_SUPPORT                | [231:231] | 0x55     |

| SEC_ERASE_MULT                     | [230:230] | 0xF7     |

| SEC_TRIM_MULT                      | [229:229] | 0xF7     |

| BOOT INFO                          | [228:228] | 0x07     |

| Reserved                           | [227:227] | 0x00     |

| BOOT SIZE MULT                     | [226:226] | 0x20     |

| ACC_SIZE                           | [225:225] | 0x07     |

| HC_ERASE_GRP_SIZE                  | [224:224] | 0x01     |

| ERASE TIMEOUT MULT                 | [223:223] | 0x05     |

| REL WR SEC C                       | [222:222] | 0x01     |

| HC WP GRP SIZE                     | [221:221] | 0x10     |

| S_C_VCC                            | [220:220] | 0x08     |

| S_C_VCCQ                           | [219:219] | 0x08     |

| PRODUCTION_STATE_AWARENESS_TIMEOUT | [218:218] | 0x14     |

| S_A_TIMEOUT                        | [217:217] | 0x15     |

| SLEEP_NOTIFICATION_TIME            | [216:216] | 0x0F     |

| SEC_COUNT                          | [215:212] | 15335424 |

| SECURE_WP_INFO                     | [211:211] | 0x01     |

| MIN_PERF_W_8_52                    | [210:210] | 0x08     |

| MIN_PERF_R 8_52                    | [209:209] | 0x08     |

| MIN_PERF_W_8_26_4_52               | [208:208] | 0x08     |

| MIN_PERF_R_8_26_4_52               | [207:207] | 0x08     |

| MIN_PERF_W_4_26                    | [206:206] | 0x08     |

| MIN_PERF_R_4_26                    | [205:205] | 0x08     |

| Reserved                           | [204:204] | 0x00     |

| PWR_CL_26_360                      | [203:203] | 0x00     |

| PWR_CL_52_360                      | [202:202] | 0x00     |

| PWR_CL_26_195                      | [201:201] | 0x00     |

| PWR_CL_52_195                      | [200:200] | 0x00     |

| PARTITION_SWITCH_TIME              | [199:199] | 0x03     |

| OUT_OF_INTERRUPT_TIME              | [198:198] | 0xFF     |

| DRIVER_STRENGTH                    | [197:197] | 0x1F     |

| DEVICE_TYPE                        | [196:196] | 0x57     |

| Field                       | Byte      | Value |

|-----------------------------|-----------|-------|

| Reserved                    | [195:195] | 0x00  |

| CSD_STRUCTURE               | [194:194] | 0x02  |

| Reserved                    | [193:193] | 0x00  |

| EXT_CSD_REV                 | [192:192] | 0x08  |

| CMD_SET                     | [191:191] | 0x00  |

| Reserved                    | [190:190] | 0x00  |

| CMD_SET_REV                 | [189:189] | 0x00  |

| Reserved                    | [188:188] | 0x00  |

| POWER_CLASS                 | [187:187] | 0x00  |

| Reserved                    | [186:186] | 0x00  |

| HS_TIMING                   | [185:185] | 0x01  |

| STROBE_SUPPORT              | [184:184] | 0x01  |

| BUS_WIDTH                   | [183:183] | 0x02  |

| Reserved                    | [182:182] | 0x00  |

| ERASED_MEM_CONT             | [181:181] | 0x00  |

| Reserved                    | [180:180] | 0x00  |

| PARTITION_CONFIG            | [179:179] | 0x00  |

| BOOT CONFIG PROT            | [178:178] | 0x00  |

| BOOT_BUS_CONDITIONS         | [177:177] | 0x00  |

| Reserved                    | [176:176] | 0x00  |

| ERASE_GROUP_DEF             | [175:175] | 0x00  |

| BOOT_WP_STATUS              | [174:174] | 0x00  |

| BOOT_WP                     | [173:173] | 0x00  |

| Reserved                    | [172:172] | 0x00  |

| USER_WP                     | [171:171] | 0x00  |

| Reserved                    | [170:170] | 0x00  |

| FW_CONFIG                   | [169:169] | 0x00  |

| RPMB_SIZE_MULT              | [168:168] | 0x20  |

| WR_REL_SET                  | [167:167] | 0x00  |

| WR_REL_PARAM                | [166:166] | 0x15  |

| SANITIZE_START              | [165:165] | 0x00  |

| BKOPS_START                 | [164:164] | 0x00  |

| BKOPS_EN                    | [163:163] | 0x00  |

| RST_n_FUNCTION              | [162:162] | 0x00  |

| HPI_MGMT                    | [161:161] | 0x00  |

| PARTITIONING_SUPPORT        | [160:160] | 0x07  |

| MAX_ENH_SIZE_MULT           | [159:157] | 936   |

| PARTITIONS_ATTRIBUTE        | [156:156] | 0x01  |

| PARTITION_SETTING_COMPLETED | [155:155] | 0x01  |

| GP_SIZE_MULT_4              | [154:152] | 0     |

| Field                              | Byte      | Value   |

|------------------------------------|-----------|---------|

| GP_SIZE_MULT_3                     | [151:149] | 0       |

| GP_SIZE_MULT_2                     | [148:146] | 0       |

| GP_SIZE_MULT_1                     | [145:143] | 0       |

| ENH_SIZE_MULT                      | [142:140] | 936     |

| ENH_START_ADDR                     | [139:136] | 0       |

| Reserved                           | [135:135] | 0x00    |

| SEC_BAD_BLK_MGMNT                  | [134:134] | 0x00    |

| PRODUCTION_STATE_AWARENESS         | [133:133] | 0x00    |

| TCASE_SUPPORT                      | [132:132] | 0x00    |

| PERIODIC_WAKEUP                    | [131:131] | 0x00    |

| PROGRAM_CID_CSD_DDR_SUPPORT        | [130:130] | 0x01    |

| Reserved                           | [129:128] | 0       |

| VENDOR_SPECIFIC_FIELD              | [127:63]  | N/A     |

| USE_NATIVE_SECTOR                  | [ 62:62 ] | 0x00    |

| DATA_SECTOR_SIZE                   | [ 61:61 ] | 0x00    |

| INI_TIMEOUT_EMU                    | [ 60:60 ] | 0x00    |

| CLASS_6_CTRL                       | [ 59:59 ] | 0x00    |

| DYNCAP_NEEDED                      | [ 58:58 ] | 0x00    |

| EXCEPTION_EVENTS_CTRL              | [ 57:56 ] | 0       |

| EXCEPTION_EVENTS_STATUS            | [ 55:54 ] | 0       |

| EXT_PARTITIONS_ATTRIBUTE           | [ 53:52 ] | 0       |

| CONTEXT_CONF                       | [ 51:37 ] | 0       |

| PACKED_COMMAND_STATUS              | [ 36:36 ] | 0x00    |

| PACKED_FAILURE_INDEX               | [ 35:35 ] | 0x00    |

| POWER_OFF_NOTIFICATION             | [ 34:34 ] | 0x00    |

| CACHE_CTRL                         | [ 33:33 ] | 0x00    |

| FLUSH_CACHE                        | [ 32:32 ] | 0x00    |

| BARRIER_CTRL                       | [ 31:31 ] | 0x00    |

| MODE_CONFIG                        | [ 30:30 ] | 0x00    |

| MODE_OPERATION_CODES               | [ 29:29 ] | 0x00    |

| Reserved                           | [ 28:27 ] | 0       |

| FFU_STATUS                         | [ 26:26 ] | 0x00    |

| PRE_LOADING_DATA_SIZE              | [ 25:22 ] | 0       |

| MAX_PRE_LOADING_DATA_SIZE          | [21:18]   | 4866048 |

| PRODUCT_STATE_AWARENESS_ENABLEMENT | [ 17:17 ] | 0x01    |

| SECURE_REMOVAL_TYPE                | [ 16:16 ] | 0x39    |

| CMDQ_MODE_EN                       | [ 15:15 ] | 0x00    |

| Reserved                           | [ 14:0 ]  | 0       |

# **Section 3**

Low Power Double Data Rate 3 (LPDDR3 SDRAM)

# 8Gb(4Gbx2) DDP LPDDR3 SDRAM

# Product Features LPDDR3

- •Ultra-low voltage core and I/O power supplies

- VDD1 = 1.70-1.95V; 1.8V nominal

- -VDD2 = 1.14-1.30V; 1.2V nominal

- VDDQ = 1.14-1.30V; 1.2V nominal

- Organization

- 16M words × 32 bits × 8 banks

- JEDEC LPDDR3-compliant

- •4KB page size (×32 bits)

- Row address: R0 to R13 (×32 bits)

- Column address: C0 to C9

- Frequency range

- 1600Mbps Max

- 8n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL =8)

- Directed per-bank refresh for concurrent bank operation and ease for command scheduling

- On-chip temperature sensor to control self refresh rate

- Partial-array self refresh (PASR)

- Selectable output drive strength (DS)

- Clock-stop capability

- Operating temperature range

- -TC = -25°C to +85°C

# **Product Description**

The LPDDR3 portion of the device is fully compatible with the JEDEC Standard Specification No.JESD209-3B. This datasheet describes the key and specific features of the LPDDR3. Any additional information required to interface the device to a host system and all the practical methods for device detection and access can be found in the proper sections of the JEDEC Standard Specification.

# **LPDDR3** Interface

# **Pin Function and Descriptions**

Table 3-1 - Pin Function and Descriptions

| Name                                                                            | Tymo   | Pagarintian                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                            | Type   | Description Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CK_t, CK_c                                                                      | Input  | <b>Clock:</b> CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK_t. Single Data Rate (SDR) inputs, CS_n and CKE, are sampled at the positive Clock edge.  Clock is defined as the differential pair, CK_t and CK_c. The positive Clock edge is defined by the crosspoint of a rising CK_t and a falling CK_c. The negative Clock edge is defined by the crosspoint of a falling CK_t and a |

| СКЕ                                                                             | Input  | rising CK_c.  Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and therefore device input buffers and output drivers. Power savings modes are entered and exited through CKE transitions. CKE is considered part of the command code. See Command Truth Table for command code descriptions. CKE is sampled at the positive Clock edge.                                                                                                         |

| CS_n                                                                            | Input  | <b>Chip Select:</b> CS_n is considered part of the command code. See Command Truth Table for command code descriptions. CS_n is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                                            |

| CA0 – CA9                                                                       | Input  | <b>DDR Command/Address Inputs:</b> Uni-directional command/address bus inputs. CA is considered part of the command code. See Command Truth Table for command code descriptions.                                                                                                                                                                                                                                                                                               |

| DQ0 - DQ15 (x16)<br>DQ0 - DQ31(x32)                                             | I/O    | Data Inputs/Output: Bi-directional data bus                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DQS0_t,DQS0_c,<br>DQS1_t,DQS1_c(x16)<br>DQS0_t- DQS3_t,<br>DQS0_c -DQS3_c (x32) | I/O    | <b>Data Strobe (Bi-directional, Differential):</b> The data strobe is bi-directional (used for read and write data) and differential (DQS_t and DQS_c). It is output with read data and input with write data. DQS_t is edgealigned to read data and centered with write data.                                                                                                                                                                                                 |

| DQ35_C (x32)                                                                    |        | For x16, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7; DQS1_t and DQS1_c to the data on DQ8 - DQ15.                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                 |        | For x32 DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7, DQS1_t and DQS1_c to the data on DQ8 - DQ15, DQS2_t and DQS2_c to the data on DQ16 - DQ23, DQS3_t and DQS3_c to the data on DQ24 - DQ31.                                                                                                                                                                                                                                                                        |

| DM0-DM1 (x16)<br>DM0 - DM3 (x32)                                                | Input  | <b>Input Data Mask:</b> DM is the input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS_t. Although DM is for input only, the DM loading shall match the DQ and DQS_t (or DQS_c).                                                                                                                                                                           |

|                                                                                 |        | For x16 and x32 devices, DM0 is the input data mask signal for the data on DQ0-7. DM1 is the input data mask signal for the data on DQ8-15.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                 |        | For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is the input data mask signal for the data on DQ24-31.                                                                                                                                                                                                                                                                                                                                      |

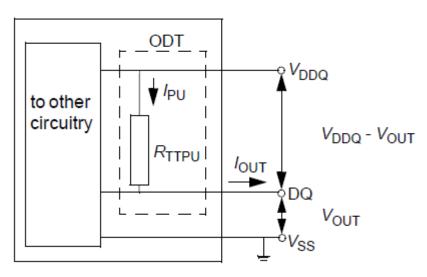

| ODT                                                                             | Input  | <b>On-Die Termination</b> : This signal enables and disables termination on the DRAM DQ bus according to the specified mode register settings.                                                                                                                                                                                                                                                                                                                                 |

| VDD1                                                                            | Supply | Core Power Supply 1                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD2                                                                            | Supply | Core Power Supply 2                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDCA                                                                           | Supply | Input Receiver Power Supply: Power supply for CAO-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDQ                                                                            | Supply | I/O Power Supply: Power supply for Data input/output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VREF(CA)                                                                        | Supply | <b>Reference Voltage for CA Command and Control Input Receiver:</b> Reference voltage for all CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                  |

| VREF(DQ)                                                                        | Supply | Reference Voltage for DQ Input Receiver: Reference voltage for all Data input buffers.                                                                                                                                                                                                                                                                                                                                                                                         |

| VSS                                                                             | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ZQ                                                                              | I/0    | Reference Pin for Output Drive Strength Calibration                                                                                                                                                                                                                                                                                                                                                                                                                            |

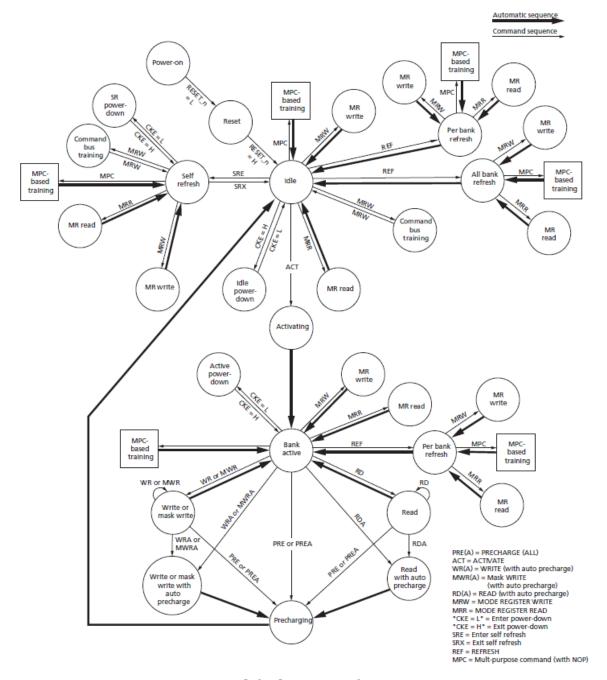

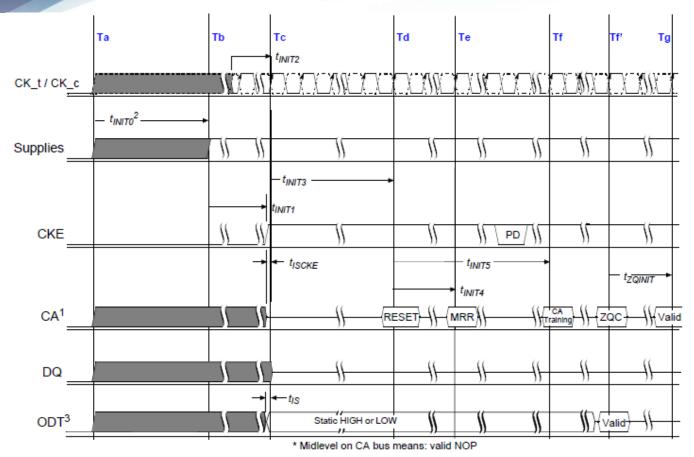

# **Simplified State Diagram**

Figure 3-1 — Simplified Bus Interface State Diagram

Notes:

- 1. From the self-refresh state, the device can enter power-down, MRR, MRW, or any of the training modes initiated with the MPC command. See the Self Refresh section.

- 2. All banks are pre-charged in the idle state.

- 3. In the case of using an MRW command to enter a training mode, the state machine will not automatically return to the idle state at the conclusion of training.

- 4. In the case of an MPC command to enter a training mode, the state machine may not automatically return to the idle state at the conclusion of training. See the applicable training section for more information.

- 5. This diagram is intended to provide an overview of the possible state transitions and commands to control

them; however, it does not contain the details necessary to operate the device. In particular, situations involving more than one bank are not captured in complete detail.

- 6. States that have an "automatic return" and can be accessed from more than one prior state (that is, MRW from either idle or active states) will return to the state where they were initiated (that is, MRW from idle will return to idle).

- 7. The RESET pin can be asserted from any state and will cause the device to enter the reset state. The diagram shows RESET applied from the power-on and idle states as an example, but this should not be construed as a restriction on RESET.

- 8. MRW commands from the active state cannot change operating parameters of the device that affect timing. Mode register fields which may be changed via MRW from the active state include: MR1-OP[3:0], MR1-OP[7], MR3-OP[7:6], MR10-OP[7:0], MR11-OP[7:0], MR13-OP[5], MR15-OP[7:0], MR16-OP[7:0], MR17-OP[7:0], MR20-OP[7:0], and MR22-OP[4:0].

## **Electrical Conditions**

All voltages are referenced to VSS (GND)

- Execute power-up and Initialization sequence before proper device operation is achieved.

- Operation or timing that is not specified is illegal, and after such an event, in order to guarantee proper operation, the DDR2 Mobile RAM Device must be powered down and then restarted through the specialized initialization sequence before normal operation can continue.

### **Absolute Maximum Ratings**

**Table 3-2 Absolute Maximum Ratings**

| Parameter                              | Symbol    | min. | max. | Unit | Note |

|----------------------------------------|-----------|------|------|------|------|

| VDD1 supply voltage relative to VSS    | VDD1      | -0.4 | 2.3  | V    | 2    |

| VDD2 supply voltage relative to VSS    | VDD2      | -0.4 | 1.6  | V    | 2    |

| VDDCA supply voltage relative to VSSCA | VDDCA     | -0.4 | 1.6  | V    | 2, 3 |

| VDDQ supply voltage relative to VSSQ   | VDDQ      | -0.4 | 1.6  | V    | 2, 4 |

| Voltage on any ball relative to VSS    | VIN, VOUT | -0.4 | 1.6  | V    |      |

| Storage Temperature                    | TSTG      | -55  | 125  | °C   | 5    |

#### Notes:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Refer "Power-up, initialization and Power-Off "for relationship between power supplies

- 3.  $VREFCA \le 0.6 \times VDDCA$ ; however, VREFCA may be  $\ge VDDCA$  provided that  $VREFCA \le 300$  mV.

- 4.  $VREFDQ \le 0.7 \times VDDQ$ ; however, VREFDQ may  $be \ge VDDQ$  provided that  $VREFDQ \le 300$  mV.

- 5. Storage Temperature is the case surface temperature on the center/top side of the DDR3 Mobile RAM Device.

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### **Recommended DC Operating Conditions**

Table 3-3 Recommended DC Operating Conditions (TC = -25°C to +85°C)

| Table 5 Recommended 2 coperating conditions (1c 25 cto 105 c) |        |      |      |      |      |      |

|---------------------------------------------------------------|--------|------|------|------|------|------|

| Parameter                                                     | Symbol | min. | Тур. | max. | Unit | Note |

| Core Power1                                                   | VDD1   | 1.7  | 1.8  | 1.95 | V    | 1    |

| Core Power2,                                                  | VDD2   | 1.14 | 1.2  | 1.3  | V    | 1,2  |

| Input Buffer Power                                            | VDDCA  | 1.14 | 1.2  | 1.3  | V    | 1,2  |

| I/O Buffer Power                                              | VDDQ   | 1.14 | 1.2  | 1.3  | V    | 2    |

Notes: 1. VDD1 uses significantly less power than VDD2.

## AC and DC Input Levels for Single-Ended CA/CS Signals

Table 3-4 Single-Ended AC and DC Input Levels for CA/CS Inputs

| Parameter                          | Symbol     | Speed       | min.         | max.         | Unit | Note |

|------------------------------------|------------|-------------|--------------|--------------|------|------|

| AC inputlogic high                 | VIHCA(AC)  | 1333 / 1600 | VREF + 0.150 | Note 2       | V    | 1, 2 |

| AC inputlogic low                  | VILCA(AC)  | 1333 / 1600 | Note 2       | VREF - 0.150 | V    | 1, 2 |

| DC input logic high                | VIHCA(DC)  | 1333 / 1600 | VREF + 0.100 | VDDCA        | V    | 1    |

| DC inputlogic low                  | VILCA(DC)  | 1333 / 1600 | VSS          | VREF - 0.100 | V    | 1    |

| Reference Voltage for CA/CS inputs | VREFCA(DC) | 1333 / 1600 | 0.49 ×VDDCA  | 0.51 ×VDDCA  | V    | 3,4  |

Notes: 1. For CA/CS input only pins. VREF = VREFCA(DC). 2. Refer "Overshoot and Undershoot Specifications".

- 3. The ac peak noise on VREFCA may not allow VREFCA to deviate from VREFCA(DC) by more than ± 1% VDDCA (for reference: 43dditio. ± 12 mV).

- 4. For reference: 43dditio. VDDCA/2 ± 12 mV.

## **AC and DC Input Levels for CKE**

Table 3-5 Single-Ended AC and DC Innut Levels for CKE

| Table 3-3 Single-Ended Ac and DC input Levels for CKE |        |              |                     |      |      |  |  |

|-------------------------------------------------------|--------|--------------|---------------------|------|------|--|--|

| Parameter                                             | Symbol | min.         | max.                | Unit | Note |  |  |

| CKE Input High Level                                  | VIHCKE | 0.65 × VDDCA | Note 1              | V    | 1    |  |  |

| CKE Input Low Level                                   | VILCKE | Note 1       | $0.35 \times VDDCA$ | V    | 1    |  |  |

Notes: 1. Refer "Overshoot and Undershoot Specifications".

<sup>2.</sup> The voltage range is for DC voltage only. DC voltage is the voltage supplied at the DRAM and is inclusive of all noise up to 1 MHz at the DRAM package ball.

## AC and DC Input Levels for Single-Ended Data Signals

Table 3-6 Single-Ended AC and DC Input Levels for DQ and DM

| 102100 0011                         | <u> </u>                       |           |                          |                          |      |         |

|-------------------------------------|--------------------------------|-----------|--------------------------|--------------------------|------|---------|

| Parameter                           | arameter Symbol                |           | Speed min.               |                          | Unit | Note    |

| AC input logic high                 | VIHDQ(AC)                      | 1333/1600 | VREF + 0.150             | Note 2                   | V    | 1, 2 ,5 |

| AC input logic low                  | VILDQ(AC)                      | 1333/1600 | Note 2                   | VREF - 0.150             | V    | 1, 2, 5 |

| DC input logic high                 | VIHDQ(DC)                      | 1333/1600 | VREF + 0.100             | VDDQ                     | V    | 1       |

| DC input logic low                  | VILDQ(DC)                      | 1333/1600 | VSSQ                     | VREF - 0.100             | V    | 1       |

| Reference Voltage for DQ, DM inputs | VREFDQ(DC)<br>(DQ ODT disable) | 1333/1600 | 0.49 × VDDQ              | 0.51 × VDDQ              | V    | 3, 4    |

| Reference Voltage for DQ, DM inputs | VREFDQ(DC)<br>(DQ ODT enable)  | 1333/1600 | VODTR/2 –<br>0.01 * VDDQ | VODTR/2 +<br>0.01 * VDDQ | V    | 3,5,6   |

- 1. For DQ input only pins. VREF = VREFDQ(DC).

- 2. Refer "Overshoot and Undershoot Specifications".

- 3. The ac peak noise on VREFDQ may not allow VREFDQ to deviate from VREFDQ(DC) by more than  $\pm$  1% VDDQ (for reference: dditio.  $\pm$  12 mV).

- 4. For reference: 7alibra. VDDQ/2+/-12 mV.

- 5. For reference: 7alibra. VODTR/2+/-12 mV.

- 6. The nominal mode register programmed value for RODT and the nominal controller output impedance RON are used for the calculation of VODTR. For testing purposes a controller RON value of  $50 \Omega$  is used.

$$Vodtr = \frac{2Ron + Rtt}{Ron + Rtt} \times Vddq$$

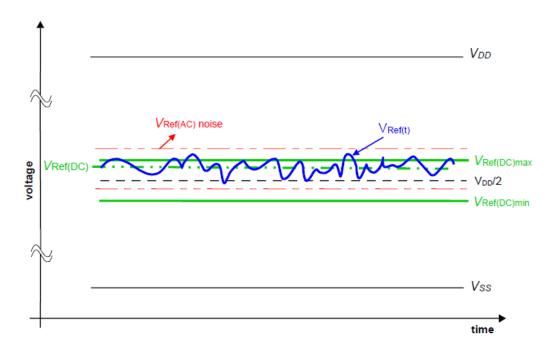

#### **VREF Tolerances**

The dc-tolerance limits and ac-noise limits for the reference voltages VREFCA and VREFDQ are illustrated in Figure 3-2. It shows a valid reference voltage VREF(t) as a function of time. (VREF stands for VREFCA and VREFDQ likewise).

VDD stands for VDD2 for VREFCA and VDDQ for VREFDQ. VREF(DC) is the linear average of VREF(t) over a very long period of time (e.g. 1 sec) and is specified as a fraction of the linear average of VDDQ or VDD2 also over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirements in Table 3-5. Furthermore VREF(t) may temporarily deviate from VREF(DC) by no more than  $\pm$  1% VDD. VREF(t) cannot track noise on VDDQ or VDD2 if this would send VREF outside these specification.

Figure 3-2 — Illustration of VREF(DC) Tolerance and VREF AC-noise Limits

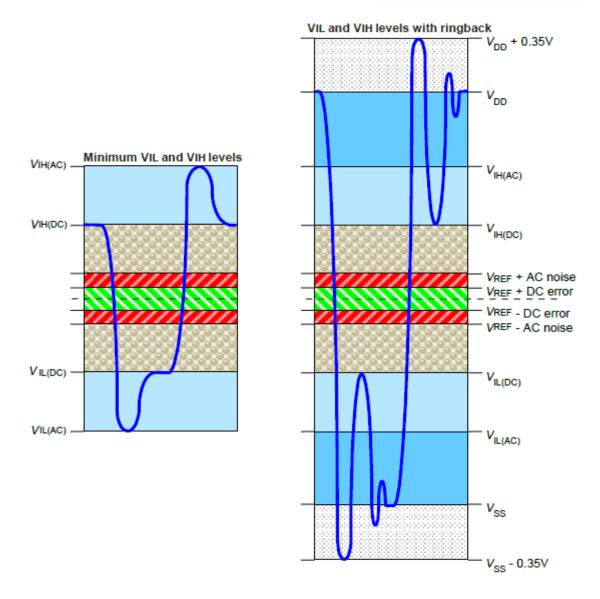

The voltage levels for setup and hold time measurements VIH(AC), VIH(DC), VIL(AC) and VIL(DC) are dependent on VREF. "VREF" shall be understood as VREF(DC), as defined in Figure 3-2.

This clarifies that dc-variations of VREF affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to which setup and hold is measured. Devices will function correctly with appropriate timing deratings with VREF outside these specified levels so long as VREF is maintained between  $0.44 \times VDDQ$  (or VDD2) and  $0.56 \times VDDQ$  (or VDD2) and so long as the controller achieves the required single-ended AC and DC input levels from instantaneous VREF . Therefore, system timing and voltage budgets need to account for VREF deviations outside of this range.

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with VREF AC-noise. Timing and voltage effects due to AC-noise on VREF up to the specified limit ( $\pm$  1% of VDD) are included in DRAM timings and their associated deratings.

## **Input Signal**

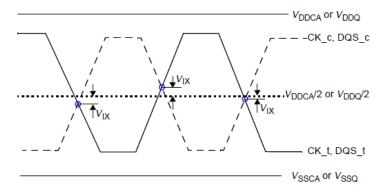

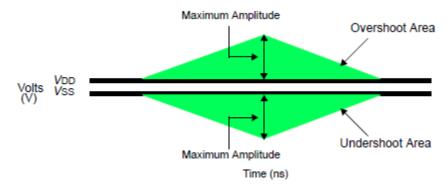

Figure 3-3 — LPDDR3 Input Signal

Notes: 1. Numbers reflect nominal values.

- 2. For CAO-9, CK\_t, CK\_c, and CS\_n, VDD stands for VDDCA. For DQ, DM, DQS\_t, DQS\_c and ODT, VDD stands for VDDQ.

- 3. For CAO-9, CK\_t, CK\_c, and CS\_n, VSS stands for VSSCA. For DQ, DM, DQS\_t, DQS\_c and ODT VSS stands for VSS.

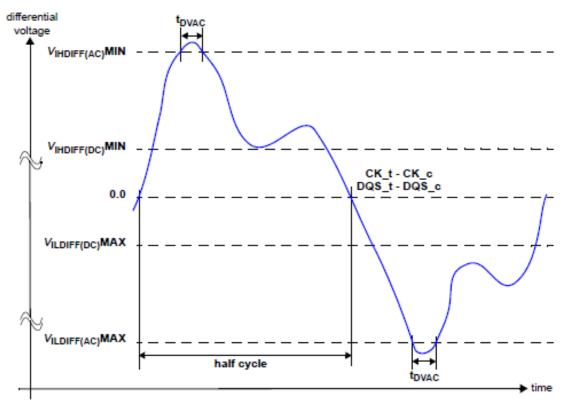

## AC and DC Logic Input Levels for Differential Signals

### **Differential Signal Definition**

Figure 3-4 Definition of Differential AC-swing and "Time above AC-level" tDVAC

## $Differential \ Swing \ Requirements \ for \ Clock \ (CK_t-CK_c) \ and \ Strobe \ (DQS_t-DQS_c)$

Table 3-7 Differential AC and DC Input Levels

| Parameter                  | Symbol      | min.                        | max.                        | Unit | Note |

|----------------------------|-------------|-----------------------------|-----------------------------|------|------|

| Differential input high    | VIHdiff(DC) | $2 \times (VIH(DC) - VREF)$ | Note 3                      | V    | 1    |

| Differential input low     | VILdiff(DC) | Note 3                      | $2 \times (VIL(DC) - VREF)$ | V    | 1    |

| Differential input high AC | VIHdiff(AC) | $2 \times (VIH(AC) - VREF)$ | Note 3                      | V    | 2    |

| Differential input low AC  | VILdiff(AC) | Note 3                      | $2 \times (VIL(AC) - VREF)$ | V    | 2    |

#### Notes:

- Used to define a differential signal slew-rate. For CK\_t CK\_c use VIH/VIL(dc) of CA and VREFCA; for DQS\_t DQS\_c, use VIH/VIL(dc) of DQs and VREFDQ; if a reduced dc-high or dc-low level is used for a signal group, then the reduced level applies also here.

- 2. For CK\_t CK\_c use VIH/VIL(ac) of CA and VREFCA; for DQS\_t DQS\_c, use VIH/VIL(ac) of DQs and VREFDQ; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here.

- 3. These values are not defined, however the single-ended signals CK\_t, CK\_c, DQS\_t, and DQS\_c need to be within the respective limits (VIH(dc) max, VIL(dc)min) for single-ended signals as well as the limitations for overshoot and undershoot

For CK\_t and CK\_c, Vref = VrefCA(DC). For DQS\_t and DQS\_c, Vref = VrefDQ(DC)

Table 3-8 Allowed Time Before Ringback (tDVAC) for CK\_t - CK\_c and DQS\_t - DQS\_c

| Slew Rate [V/ns] | tDVAC [ps] @<br> VIH/Ldiff(ac)  = 300mV<br>1333Mbps | tDVAC [ps] @<br> VIH/Ldiff(ac)  = 300mV<br>1600Mbp |  |  |

|------------------|-----------------------------------------------------|----------------------------------------------------|--|--|

|                  | min.                                                | min.                                               |  |  |

| > 4.0            | 58                                                  | 48                                                 |  |  |

| 8.0              | 58                                                  | 48                                                 |  |  |

| 7.0              | 56                                                  | 46                                                 |  |  |

| 6.0              | 53                                                  | 43                                                 |  |  |

| 5.0              | 50                                                  | 40                                                 |  |  |

| 4.0              | 45                                                  | 35                                                 |  |  |

| 3.0              | 37                                                  | 27                                                 |  |  |

| < 3.0            | 37                                                  | 27                                                 |  |  |

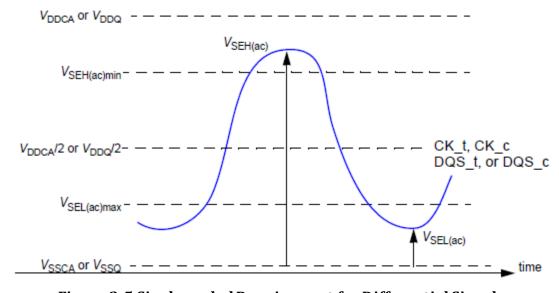

#### Single-ended Requirements for Differential Signals

Each individual component of a differential signal (CK\_t, DQS\_t, CK\_c, or DQS\_c) has also to comply with certain requirements for single-ended signals.

CK\_t and CK\_c shall meet VSEH(ac)min / VSEL(ac)max in every half-cycle.

DQS\_t, DQS\_c shall meet VSEH(ac)min / VSEL(ac)max in every half-cycle preceeding and following a valid transition. Note that the applicable ac-levels for CA and DQ's are different per speed-bin.

Figure 3-5 Single-ended Requirement for Differential Signals.

Note that while CA and DQ signal requirements are with respect to VREF, the single-ended components of differential signals have a requirement with respect to VDDQ/2 for DQS\_t, DQS\_c and VDDCA/2 for CK\_t, CK\_c; this is nominally the same. The transition of single-ended signals through the AC-levels is used to measure setup time. For single-ended components of differential signals the requirement to reach VSEL(AC)max, VSEH(AC)min has no bearing on timing, but adds a restriction on the common mode characteristics of these signals.

Table 3-9 Single-ended Levels for CK\_t, DQS\_t, CK\_c, DQS\_c

| Parameter                              | Symbol        | min.            | max.                | Unit | Note |

|----------------------------------------|---------------|-----------------|---------------------|------|------|

| Single-ended high-level for strobes    | VSEH(AC150)   | (VDDQ/2)+0.150  | Note 3              | V    | 1, 2 |

| Single-ended high-level for CK_t, CK_c | VSEII(ACISO)  | (VDDCA/2)+0.150 | Note 3              | V    | 1, 2 |

| Single-ended low-level for strobes     | VSEL(AC150)   | Note 3          | (VDDQ / 2) - 0.150  | V    | 1, 2 |

| Single-ended low-level for CK_t, CK_c  | ,             | Note 3          | (VDDCA / 2) – 0.150 | V    | 1, 2 |

| Single-ended high-level for<br>strobes | VSEH(AC135)   | (VDDQ/2)+0.135  | Note 3              | V    | 1, 2 |

| Single-ended high-level for CK_t, CK_c | V3EII(AC133)  | (VDDCA/2)+0.135 | Note 3              | V    | 1, 2 |

| Single-ended low-level for strobes     | VSEL(AC135)   | Note 3          | (VDDQ / 2) - 0.135  | V    | 1, 2 |

| Single-ended low-level for CK_t, CK_c  | V SEE (AC133) | Note 3          | (VDDCA/2) - 0.135   | V    | 1, 2 |

Notes: 1. For CK\_t, CK\_c use VSEH/VSEL(AC) of CA; for strobes (DQS0\_t, DQS0\_c, DQS1\_t, DQS1\_c, DQS2\_t, DQS2\_t, DQS3\_t, DQS3\_c) use VIH/VIL(AC) of DQs.

- 2. VIH(AC)/VIL(AC) for DQs is based on VREFDQ; VSEH(AC)/VSEL(AC) for CA is based on VREFCA; if a reduced Achigh or AC-low level is used for a signal group, then the reduced level applies also here

- 3. These values are not defined, however the single-ended signals CK\_t, CK\_c, DQS0\_t, DQS0\_c, DQS1\_t, DQS1\_c, DQS2\_t, DQS2\_c, DQS3\_t, DQS3\_c need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot Specifications".

#### **Differential Input Cross Point Voltage**

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input signals (CK\_t, CK\_c and DQS\_t, DQS\_c) must meet the requirements in Table 3-10. The differential input cross point voltage VIX is measured from the actual cross point of true and complement signals to the midlevel between of VDD and VSS.

Figure 3-6 VIX Definition

Table 3-10 Cross Point Voltage for Differential Input Signals (CK, DQS)

| Parameter                                                                  | Symbol | min. | max. | Unit | Note |

|----------------------------------------------------------------------------|--------|------|------|------|------|

| Differential Input Cross Point Voltage relative to VDDCA/2 for CK_t, CK_c  | VIXCA  | -120 | 120  | mV   | 1, 2 |

| Differential Input Cross Point Voltage relative to VDDQ/2 for DQS_t, DQS_c | VIXDQ  | -120 | 120  | mV   | 1, 2 |

#### Notes:

- 1. The typical value of VIX(AC) is expected to be about  $0.5 \times \text{VDD}$  of the transmitting device, and VIX(AC) is expected to track variations in VDD.VIX(AC) indicates the voltage at which differential input signals must cross.

- 2. For CK\_t and CK\_c, VREF = VREFCA(DC). For DQS\_t and DQS\_c, VREF = VREFDQ(DC).

#### Slew Rate Definitions for Single-Ended Input Signals

See "CA and CS\_c Setup, Hold and Derating" for single-ended slew rate definitions for address and command signals.

See "Data Setup, Hold and Slew Rate Derating" for single-ended slew rate definitions for data signals.

## Slew Rate Definitions for Differential Input Signals

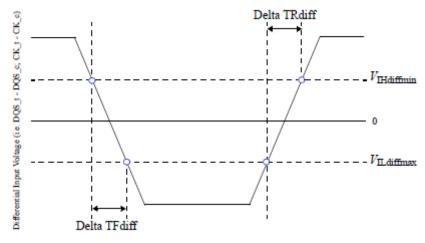

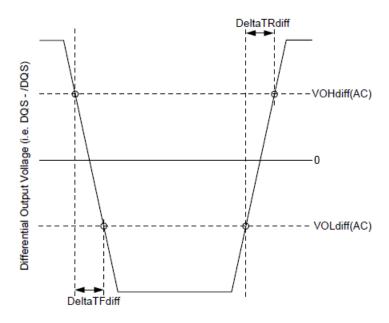

Input slew rate for differential signals (CK\_t, CK\_c and DQS\_t, DQS\_c) are defined and measured as shown in Table 3-11 and Figure 3-7.

Table 3-11 Differential Input Slew Rate Definition

| Docarintion                                                                    | Measured   |            | Defined by                              |  |  |

|--------------------------------------------------------------------------------|------------|------------|-----------------------------------------|--|--|

| Description                                                                    | from       | to         | Defined by                              |  |  |

| Differential input slew rate for rising edge (CK_t - CK_c and DQS_t - DQS_c).  | VILdiffmax | VIHdiffmin | [VIHdiffmin – VILdiffmax] / DeltaTRdiff |  |  |

| Differential input slew rate for falling edge (CK_t - CK_c and DQS_t - DQS_c). | VIHdiffmin | VILdiffmax | [VIHdiffmin – VILdiffmax] / DeltaTFdiff |  |  |

Note: 1. The differential signal (i.e.  $CK_t - CK_c$  and  $DQS_t - DQS_c$ ) must be linear between these thresholds.

Figure 3-7 — Differential Input Slew Rate Definition for DQS\_t, DQS\_c and CK\_t, CK\_c

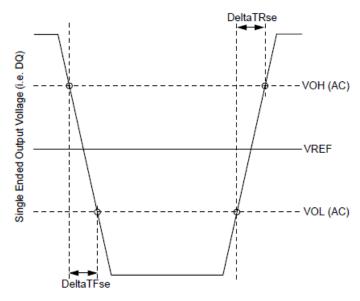

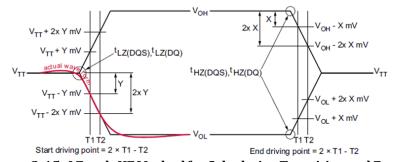

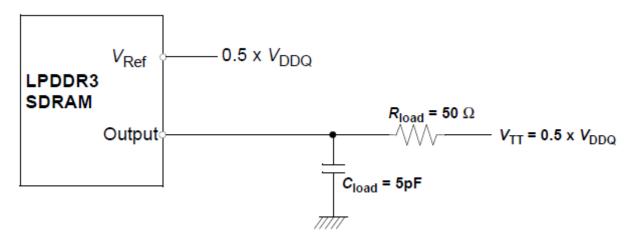

## Single Ended AC and DC Output Levels

Table 3-12 shows the output levels used for measurements of single ended signals.

Table 3-12 Single-ended AC and DC Output Levels