Sample &

Buv

#### LP8755

SNVSA20A - NOVEMBER 2013 - REVISED FEBRUARY 2015

# LP8755 Multi-Phase Six-Core Step-Down Converter

Technical

Documents

Check for Samples: LP8755

# 1 Features

- Six High-Efficiency Step-Down DC-DC Converter Cores:

- Max Output Current 15 A

- Cores Bundled to a 6-Phase Converter

- Load Current Reporting

- Programmable Overcurrent Protection (OCP)

- Auto PWM/PFM and Forced-PWM Operations and Automatic Low Power-Mode Setting

- Automatic Phase Adding/Shedding

- Remote Differential Feedback Voltage Sensing

- Output Voltage Ramp Control

- V<sub>OUT</sub> Range = 0.6 V to 1.67 V

- I<sup>2</sup>C-Compatible Interface which Supports Standard (100 kHz), Fast (400 kHz), and High-Speed (3.4 MHz) Modes

- Four Selectable I<sup>2</sup>C Addresses

- Interrupt Function with Programmable Masking

- Output Short-Circuit and Input Overvoltage Protection (OVP)

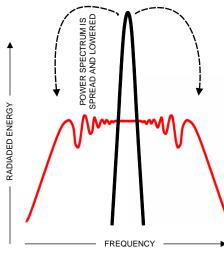

- Spread Spectrum and Phase Control for EMI Reduction

- Overtemperature Protection (OTP)

- Undervoltage Lockout (UVLO)

# 2 Applications

- Smart Phones, eBooks and Tablets

- GSM, GPRS, EDGE, LTE, CDMA and WCDMA Handsets

- Gaming Devices

# 3 Description

Tools &

Software

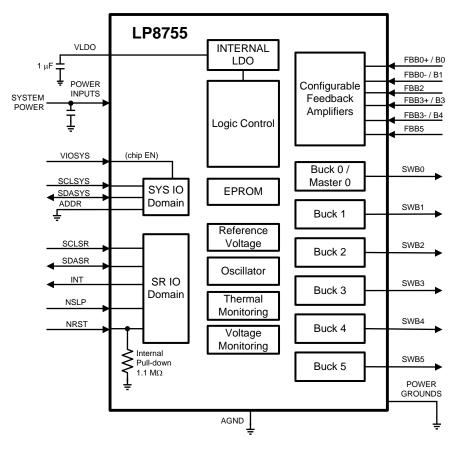

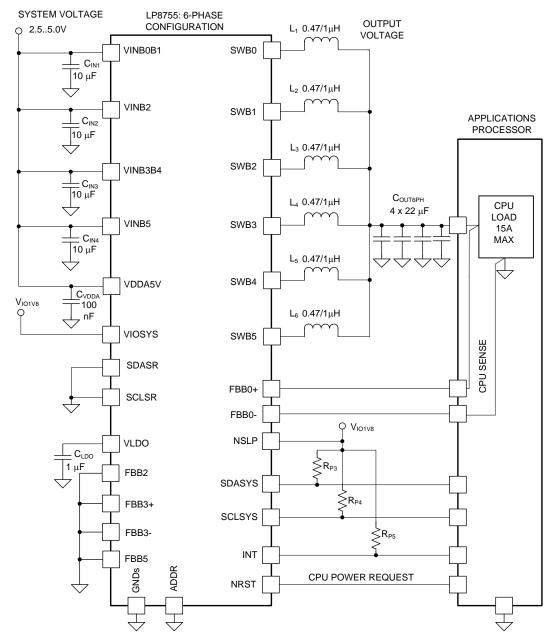

The LP8755 is designed to meet the power management requirements of the latest applications processors in mobile phones and similar portable applications. The device contains six step-down DC-DC converter cores, which are bundled together in a 6-phase buck converter. The device is fully controlled by a SmartReflex<sup>™</sup>-compatible (DVS) interface or an I<sup>2</sup>C-compatible serial interface.

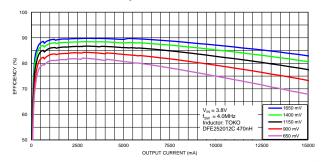

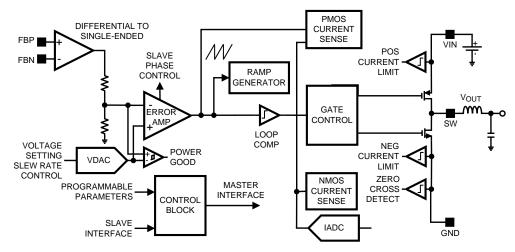

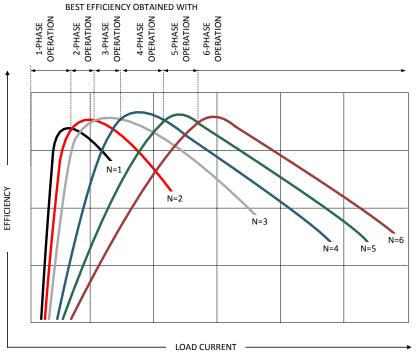

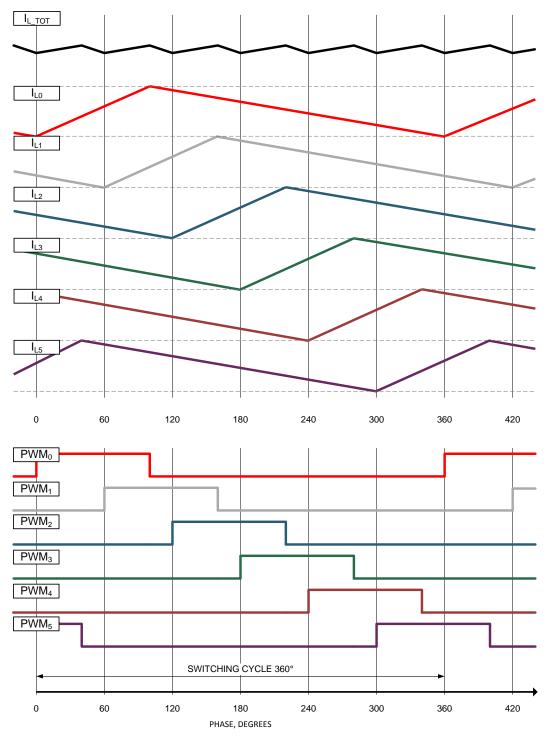

The automatic PWM/PFM operation together with the automatic phase adding/shedding maximizes efficiency over a wide output current range. The LP8755 supports remote differential voltage sensing to compensate IR drop between the regulator output and the point-of-load thus improving the accuracy of the output voltage.

The protection features include short-circuit protection, current limits, input OVP, UVLO, temperature warning, and shutdown functions. Several error flags are provided for status information of the IC. In addition, I<sup>2</sup>C read-back includes total load current and load current for each buck core: The LP8755 has the ability to sense current being delivered to the load without the addition of current sense resistors. During start-up, the device controls the output voltage slew rate to minimize overshoot and the inrush current.

#### Device Information<sup>(1)</sup>

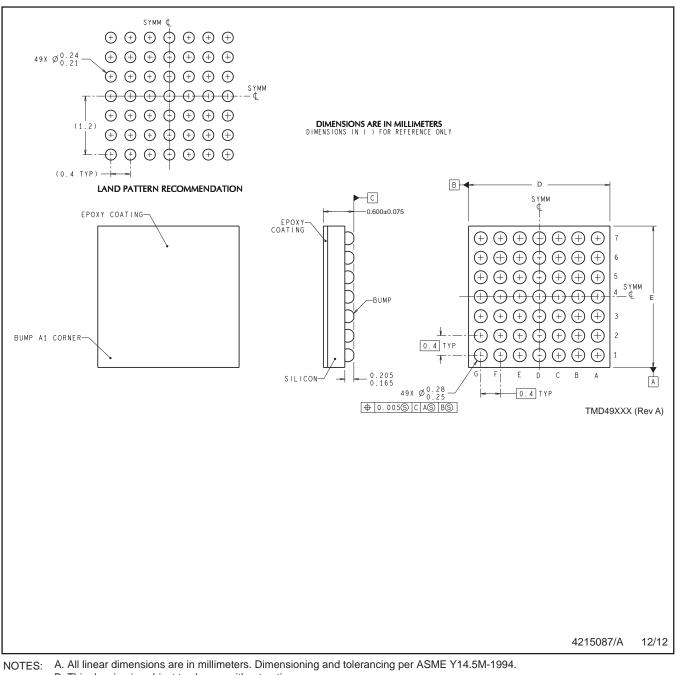

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)     |

|-------------|------------|---------------------|

| LP8755      | DSBGA (49) | 3.022 mm x 2.882 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### Efficiency vs. Load Current

# **Table of Contents**

7.5

8

9

12

| геа  |                                                  |

|------|--------------------------------------------------|

| Арр  | lications 1                                      |

| Des  | cription1                                        |

|      | ision History2                                   |

|      | Configuration and Functions                      |

|      | cifications5                                     |

| 6.1  | Absolute Maximum Ratings5                        |

| 6.2  | ESD Ratings5                                     |

| 6.3  | Recommended Operating Conditions5                |

| 6.4  | Thermal Information 6                            |

| 6.5  | General Electrical Characteristics               |

| 6.6  | 6-Phase Buck Electrical Characteristics          |

| 6.7  | 6-Phase Buck System Characteristics9             |

| 6.8  | Protection Features Characteristics 11           |

| 6.9  | I <sup>2</sup> C Serial Bus Timing Parameters 12 |

| 6.10 | Typical Characteristics 14                       |

| Deta | ailed Description 15                             |

| 7.1  | Overview 15                                      |

| 7.2  | Functional Block Diagram 16                      |

|      |                                                  |

| 4 Revision Histor |

|-------------------|

|-------------------|

Easturas

1

2

3

4

5

6

7

Changes from Original (November 2013) to Revision A

- Changed formatting to match new TI datasheet guidelines; added Device Information and ESD Ratings tables, Power Supply Recommendations, Layout, and Device and Documentation Support sections; moved some curves to Application Curves section, reformatted Detailed Description and Application and Implementation sections, adding additional content. ......1

- Features Descriptions ...... 16 7.3 7.4 Register Maps ..... 29 7.6 8.1 8.2 Typical Application ...... 38 Power Supply Recommendations ...... 47 10.1 Layout Guidelines ..... 47 10.2 Layout Example ..... 48 11 Device and Documentation Support ...... 49 Device Support...... 49 11.1 Documentation Support ...... 49 11.2 11.3 Trademarks ..... 49 11.4 Electrostatic Discharge Caution ...... 49 11.5 Glossary ...... 49 Mechanical, Packaging, and Orderable Information ...... 49

Page

STRUMENTS

EXAS

2

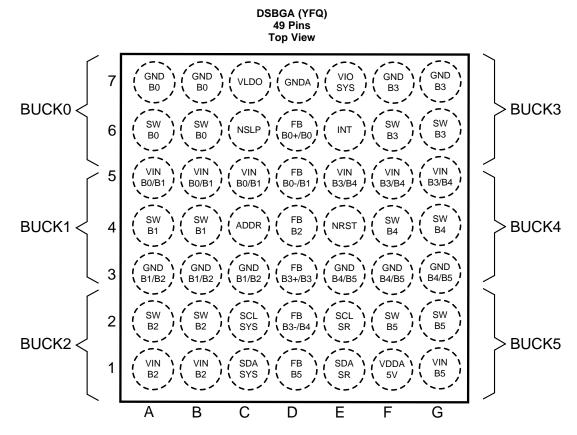

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN        |          | TVDE  | DESCRIPTION                                                                                                                                                                                            |  |  |

|------------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER     | NAME     | TYPE  | DESCRIPTION                                                                                                                                                                                            |  |  |

| A1, B1     | VINB2    | Р     | Input for Buck 2. The separate power pins VINBXX are not connected together internally - VINBXX pins must be connected together in the application and be locally bypassed.                            |  |  |

| A2, B2     | SWB2     | А     | Buck 2 switch node                                                                                                                                                                                     |  |  |

| A3, B3, C3 | GNDB1/B2 | G     | Power Ground for Buck 1 and Buck 2                                                                                                                                                                     |  |  |

| A4, B4     | SWB1     | А     | Buck 1 switch node                                                                                                                                                                                     |  |  |

| A5, B5, C5 | VINB0/B1 | Р     | Input for Buck 0 and Buck 1. The separate power pins VINBXX are not connected together internally - VINBXX pins must be connected together in the application and be locally bypassed.                 |  |  |

| A6, B6     | SWB0     | А     | Buck 0 switch node                                                                                                                                                                                     |  |  |

| A7, B7     | GNDB0    | G     | Power Ground for Buck 0                                                                                                                                                                                |  |  |

| C1         | SDASYS   | D/I/O | Serial interface data input and output for system access. Connect a pullup resistor.                                                                                                                   |  |  |

| C2         | SCLSYS   | D/I   | Serial interface clock input for system access. Connect a pullup resistor.                                                                                                                             |  |  |

| C4         | ADDR     | D/I   | Serial bus address selection. Connect to GND (addr = 60h), VIOSYS (addr = 61h), SDASYS (addr = 62h) or SCLSYS (addr = 63h).                                                                            |  |  |

| C6         | NSLP     | D/I   | Full Power to Low Power state transition control signal (By default active LOW for Low-Power PFM mode)                                                                                                 |  |  |

| C7         | VLDO     | А     | Internal supply voltage capacitor pin. A ceramic low ESR 1-µF capacitor should be connected from this pin to GNDA. The LDO voltage is generated internally, do NOT supply or load this pin externally. |  |  |

| D1         | FBB5     | А     | Not used for six-phase converter. Connect to GND.                                                                                                                                                      |  |  |

| D2         | FBB3-/B4 | А     | Not used for six-phase converter. Connect to GND.                                                                                                                                                      |  |  |

| D3         | FBB3+/B3 | А     | Not used for six-phase converter. Connect to GND.                                                                                                                                                      |  |  |

| D4         | FBB2     | А     | Not used for six-phase converter. Connect to GND.                                                                                                                                                      |  |  |

Copyright © 2013–2015, Texas Instruments Incorporated

LP8755 SNVSA20A – NOVEMBER 2013 – REVISED FEBRUARY 2015

www.ti.com

Texas Instruments

# Pin Functions (continued)

| PIN           |                   | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER        | NAME              | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| D5            | FBB0-/B1          | А           | Remote sensing (negative). Connect to the respective sense pin of the processor or to the negative power supply trace of the processor as close as possible to the processor.                                                                                                                                                                                                                                    |  |  |

| D6            | FBB0+/B0          | А           | Remote sensing (positive). Connect to the respective sense pin of the processor or to the positive power supply trace of the processor as close as possible to the processor.                                                                                                                                                                                                                                    |  |  |

| D7            | GNDA              | G           | Ground                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| E1            | SDASR             | D/I/O       | Serial Interface data input and output for Dynamic Voltage Scaling (DVS). Connect a pullup resistor / connect to GND if not used.                                                                                                                                                                                                                                                                                |  |  |

| E2            | SCLSR             | D/I         | Serial Interface clock input for DVS. Connect a pullup resistor / connect to GND if not used.                                                                                                                                                                                                                                                                                                                    |  |  |

| E3, F3, G3    | GNDB4/B5          | G           | Power Ground for Buck 4 and Buck 5                                                                                                                                                                                                                                                                                                                                                                               |  |  |

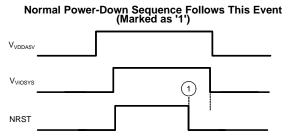

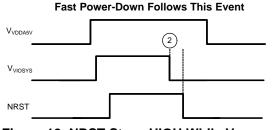

| E4            | NRST              | А           | Voltage reference input for DVS interface. Setting NRST input HIGH triggers start-up sequence                                                                                                                                                                                                                                                                                                                    |  |  |

| E5, F5, G5    | VINB3/B4          | Ρ           | Input for Buck 3 and Buck 4. The separate power pins VINBXX are not connected together internally - VINBXX pins must be connected together in the application and be locally bypassed.                                                                                                                                                                                                                           |  |  |

| E6            | INT               | D/O         | Open-drain interrupt output. Active LOW. Connect a pullup resistor to I/O supply.                                                                                                                                                                                                                                                                                                                                |  |  |

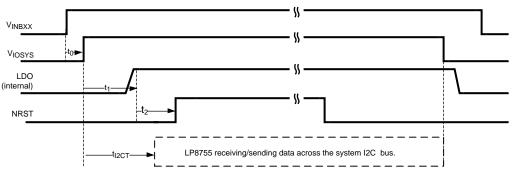

| E7            | VIOSYS            | A           | This pin shall be tied to the system I/O-voltage. Bias supply voltage for the device. Enables the I/O interface: All registers are accessible via serial bus interface when this pin is pulled high. An internal power-on reset (POR) occurs when VIOSYS is toggled low/high. The I <sup>2</sup> C host should allow at least 500 µs before sending data to the LP8755 after the rising edge of the VIOSYS line. |  |  |

| F1            | VDDA5V            | Р           | Input for Analog blocks                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| F2, G2        | SWB5              | А           | Buck 5 switch node                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| F4, G4        | SWB4              | А           | Buck 4 switch node                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| F6, G6        | SWB3              | А           | Buck 3 switch node                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| F7, G7        | GNDB3             | G           | Power Ground for Buck 3                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| G1            | VINB5             | Ρ           | Input for Buck 5. The separate power pins VINBXX are not connected together internally - VINBXX pins must be connected together in the application and be locally bypassed.                                                                                                                                                                                                                                      |  |  |

| A: Analog Pin | , D: Digital Pin, | G: Ground F | Pin, P: Power Pin, I: Input Pin, O: Output Pin                                                                                                                                                                                                                                                                                                                                                                   |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                                                                    | MIN  | MAX                                        | UNIT |

|----------------------------------------------------------------------------------------------------|------|--------------------------------------------|------|

| INPUT VOLTAGE                                                                                      |      |                                            |      |

| Voltage on power connections (VIOSYS, VDDA5V, VINBXX)                                              | -0.3 | 6                                          |      |

| Voltage on logic pins (input or output pins) (SCLSYS, SDASYS, NRST, NSLP, ADDR, INT, SCLSR, SDASR) | -0.3 | 6                                          | V    |

| Buck switch nodes (SWBXX)                                                                          | -0.3 | (V <sub>VINBXX</sub> + 0.2 V) with 6 V max | V    |

| VLDO, FBB0+/B0, FBB0-/B1, FBB2, FBB3+/B3, FBB3-/B4, FBB5                                           | -0.3 | 2                                          | V    |

| All other analog pins                                                                              | -0.3 | 6                                          | V    |

| TEMPERATURE                                                                                        |      |                                            |      |

| Junction temperature (T <sub>J-MAX</sub> )                                                         |      | 150                                        |      |

| Maximum lead temperature (soldering, 10 s) <sup>(3)</sup>                                          |      | 260                                        | °C   |

| Storage temperature, T <sub>stg</sub>                                                              | -65  | 150                                        |      |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (2) All voltage values are with respect to network ground pin.

- (3) For detailed soldering specifications and information, please refer to Texas Instruments AN-1112: DSBGA Wafer-Level Chip-Scale Package (SNVA009).

### 6.2 ESD Ratings

|        |               |                                                                                | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------|-------|------|

| V      | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V(ESD) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                      | MIN | MAX                              | UNIT |

|------------------------------------------------------|-----|----------------------------------|------|

| INPUT VOLTAGE                                        |     |                                  |      |

| Voltage on power connections (VDDA5V, VINBXX)        | 2.5 | 5                                | V    |

| Voltage on VIOSYS                                    | 1.8 | smaller of 3.3 V or $V_{VINBXX}$ | V    |

| SCLSYS, SDASYS, ADDR                                 | 0   | V <sub>VIOSYS</sub>              | V    |

| SCLSR, SDASR, NSLP, INT                              | 0   | V <sub>NRST</sub>                | V    |

| NRST                                                 | 0   | 1.8                              | V    |

| TEMPERATURE                                          |     |                                  |      |

| Junction temperature (T <sub>J</sub> )               | -40 | 125                              | *    |

| Ambient temperature (T <sub>A</sub> ) <sup>(3)</sup> | -40 | 85                               | °C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(2) All voltage values are with respect to network ground pin.

(3) Junction-to-ambient thermal resistance value given is valid for High-K PCB, and is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

### 6.4 Thermal Information

|                     |                                                             | LP8755  |      |

|---------------------|-------------------------------------------------------------|---------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                               | YFQ     | UNIT |

|                     |                                                             | 49 PINS |      |

| R <sub>θJA</sub>    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 49.2    |      |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 0.2     |      |

| $R_{\theta JB}$     | Junction-to-board thermal resistance <sup>(4)</sup>         | 6.6     | °C/W |

| Ψ <sub>JT</sub>     | Junction-to-top characterization parameter <sup>(5)</sup>   | 2.9     | C/VV |

| Ψ <sub>JB</sub>     | Junction-to-board characterization parameter <sup>(6)</sup> | 6.5     |      |

| R <sub>0JCbot</sub> | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | n/a     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953. (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard (3) test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

The junction-to-top characterization parameter,  $\psi JT$ , estimates the junction temperature of a device in a real system and is extracted (5) from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi JB$ , estimates the junction temperature of a device in a real system and is extracted

(6) from the simulation data for obtaining R<sub>0.JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific (7) JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## 6.5 General Electrical Characteristics

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) values at  $T_A = 25^{\circ}C$  (unless otherwise noted).  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).<sup>(1)(2)</sup>

|                      | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                                                                                                                              | MIN                       | TYP  | MAX                   | UNIT |

|----------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-----------------------|------|

| CURREN               | ITS                                                                                          |                                                                                                                                                                                                                              | 1                         |      |                       |      |

| I <sub>SHDN</sub>    | Shutdown supply current.<br>Total current into power<br>connections VDDA5V and<br>VINBXX     | V <sub>VIOSYS</sub> = 0 V, V <sub>NRST</sub> = 0 V                                                                                                                                                                           |                           | 0.1  | 2                     |      |

| I <sub>STBY</sub>    | Standby mode supply current.<br>Total current into power<br>connections VDDA5V and<br>VINBXX | V <sub>VIOSYS</sub> = 1.8 V, V <sub>NRST</sub> = 0 V                                                                                                                                                                         |                           | 80   |                       | μA   |

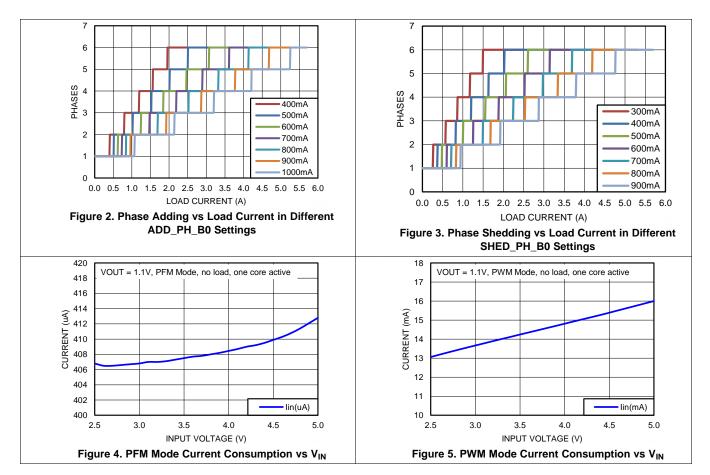

| I <sub>Active</sub>  | Active mode current<br>consumption. Total current<br>into power connections                  | PFM Mode, no load, one core active<br>Forced PWM Mode, no load, one core<br>active                                                                                                                                           |                           | 0.4  |                       | mA   |

|                      | VDDA5V and VINBXX                                                                            |                                                                                                                                                                                                                              |                           |      |                       |      |

|                      |                                                                                              |                                                                                                                                                                                                                              |                           |      | 0.3 x                 |      |

| V <sub>IL</sub>      | Input low level                                                                              | $V_{VIOSYS}$ = 1.8 V to 3.3 V                                                                                                                                                                                                |                           |      | V <sub>VIOSYS</sub>   |      |

| V <sub>IH</sub>      | Input high level                                                                             | V <sub>VIOSYS</sub> = 1.8 V to 3.3 V                                                                                                                                                                                         | 0.7 x V <sub>VIOSYS</sub> |      |                       | V    |

| V <sub>hys</sub>     | Hysteresis of Schmitt trigger inputs (SCLSYS, SDASYS)                                        |                                                                                                                                                                                                                              | 0.1 x V <sub>VIOSYS</sub> |      |                       |      |

| Ci                   | Capacitance of pins                                                                          | See <sup>(3)</sup>                                                                                                                                                                                                           |                           |      | 4                     | pF   |

| LOGIC A              | ND CONTROL INPUTS SCLSR,                                                                     | SDASR, NSLP, NRST                                                                                                                                                                                                            |                           |      |                       |      |

| V <sub>IL</sub>      | Input low level                                                                              | V <sub>NRST</sub> = 1.8 V                                                                                                                                                                                                    |                           | 0.   | 3 x V <sub>NRST</sub> |      |

| V <sub>IH</sub>      | Input high level                                                                             | V <sub>NRST</sub> = 1.8 V                                                                                                                                                                                                    | 0.7 x V <sub>NRST</sub>   |      |                       | V    |

| V <sub>hys</sub>     | Hysteresis of Schmitt trigger inputs (SCLSR, SDASR)                                          |                                                                                                                                                                                                                              | 0.1 x V <sub>NRST</sub>   |      |                       | ·    |

| Ci                   | Capacitance of SCLSR and<br>SDASR pins                                                       |                                                                                                                                                                                                                              |                           |      | 4                     | pF   |

| R <sub>IN</sub>      | Input resistance                                                                             | NRST pulldown resistor to GND                                                                                                                                                                                                |                           | 1200 |                       | kΩ   |

| V <sub>IL_NRST</sub> | Input low level NRST                                                                         |                                                                                                                                                                                                                              |                           |      | 0.54                  | V    |

| V <sub>IH_NRST</sub> | Input high level NRST                                                                        |                                                                                                                                                                                                                              | 1.3                       |      |                       | V    |

| LOGIC A              | ND CONTROL OUTPUTS                                                                           |                                                                                                                                                                                                                              |                           |      |                       |      |

|                      |                                                                                              | Voltage on INT pin, I <sub>SINK</sub> = 3 mA,<br>V <sub>NRST</sub> = V <sub>VIOSYS</sub> = 1.8 V                                                                                                                             |                           |      | 0.4                   |      |

| V <sub>OL</sub>      | Output low level                                                                             | Voltage on SDASYS, SDASR, $I_{SINK} = 3$ mA,<br>V <sub>NRST</sub> = V <sub>VIOSYS</sub> = 1.8 V                                                                                                                              |                           |      | 0.36                  | V    |

| R <sub>P</sub>       | External pullup resistor for INT                                                             | To I/O Supply                                                                                                                                                                                                                |                           | 10   |                       | kΩ   |

| ALL LOO              | GIC AND CONTROL INPUTS                                                                       |                                                                                                                                                                                                                              |                           |      | 1                     |      |

| I <sub>LEAK</sub>    | Input current                                                                                | All logic inputs over pin voltage range.<br>Note that NRST pin does have an 1.2-M $\Omega$ internal pulldown resistor and current through this resistor is not included into I <sub>LEAK</sub> rating. T <sub>A</sub> = 25°C | -1                        |      | 1                     | μΑ   |

(1) All voltage values are with respect to network ground pin.

(2) Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis. Typical (Typ.) numbers are not ensured, but do represent the most likely norm.

(3) Maximum capacitance of SCLSYS or SDASYS line is 8 pF, if ADDR pin is connected to line for serial bus address selection.

# 6.6 6-Phase Buck Electrical Characteristics

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) values at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7$  V,  $V_{VIOSYS} = V_{NRST} = 1.8$  V,  $V_{OUT} = 1.1$  V (unless otherwise noted).

|                     | PARAMETER                                             | TEST CONDITIONS                                                                                                                   | MIN                            | TYP                 | MAX                            | UNIT |

|---------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------|--------------------------------|------|

|                     |                                                       | PWM Mode, V <sub>OUTSET</sub> = 0.6 V to 1.67 V, $I_{OUT} \le 15 A^{(5)}$                                                         | 0.975 x<br>V <sub>OUTSET</sub> | V <sub>OUTSET</sub> | 1.025 x<br>V <sub>OUTSET</sub> | V    |

| V <sub>FB</sub>     | Differential feedback voltage <sup>(3)(4)</sup>       | PFM Mode, $V_{OUTSET} = 0.6 V$ to 1.67 V,<br>$I_{OUT} \le 375 \text{ mA}$                                                         | 0.975 x<br>V <sub>OUTSET</sub> | V <sub>OUTSET</sub> | 1.025 x<br>V <sub>OUTSET</sub> |      |

|                     | V <sub>FB0+/B0</sub> - V <sub>FB0-/B1</sub>           | Low-Power PFM Mode, $V_{OUTSET} = 0.6 V$ to 1.67 V,<br>I <sub>OUT</sub> ≤ 30 mA                                                   | 0.97 x<br>V <sub>OUTSET</sub>  | V <sub>OUTSET</sub> | 1.03 x<br>V <sub>OUTSET</sub>  |      |

| I <sub>LIMITP</sub> | High side switch current limit                        | 3-A register setting <sup>(4)</sup>                                                                                               | 2700                           | 3200                | 3700                           |      |

| I <sub>LIMITN</sub> | Low side switch current limit                         | Reverse current <sup>(4)</sup>                                                                                                    | 650                            | 850                 | 1050                           | mA   |

| M                   | Output upltana                                        | Range, programmable by register setting                                                                                           | 0.6                            |                     | 1.67                           | V    |

| V <sub>OUT</sub>    | Output voltage                                        | Step                                                                                                                              |                                | 10                  |                                | mV   |

| 4                   | Switching frequency                                   | 2.5 V $\leq$ V_{VINBXX} $\leq$ 5 V, 0.6 V $\leq$ V_{OUTSET} $<$ 0.8 V $^{(4)}$                                                    | 2.7                            | 3                   | 3.4                            | MHz  |

| f <sub>SW</sub>     |                                                       | $2.5 \text{ V} \le \text{V}_{\text{VINBXX}} \le 5 \text{ V}, 0.8 \text{ V} \le \text{V}_{\text{OUTSET}} \le 1.67 \text{ V}^{(4)}$ | 3.6                            | 4                   | 4.5                            |      |

| D                   |                                                       | Test current = 200 mA; Split FET                                                                                                  |                                | 120                 |                                |      |

| R <sub>DSON_P</sub> | Pin-pin resistance for PFET                           | Test current = 200 mA; Full FET                                                                                                   |                                | 60                  |                                | mΩ   |

| R <sub>DSON_N</sub> | Pin-pin resistance for NFET                           | I <sub>OUT</sub> = -200 mA                                                                                                        |                                | 50                  |                                |      |

| I <sub>LK_HS</sub>  | High-side leakage current                             | V <sub>SW</sub> = 0 V, Per Buck Core                                                                                              |                                |                     | 2                              |      |

| I <sub>LK_LS</sub>  | Low-side leakage current                              | $V_{SW} = 3.7 V = V_{VINBXX}$ , per buck core                                                                                     |                                |                     | 2                              | μA   |

| R <sub>PD</sub>     | Pull-down resistor                                    | Enabled via control register, Active only when converter disabled, Per Buck Core                                                  |                                | 250                 |                                | Ω    |

| R <sub>IN_FB</sub>  | Differential feedback Input resistance <sup>(6)</sup> | T <sub>A</sub> = 25°C                                                                                                             | 200                            | 300                 | 400                            | kΩ   |

(1) Junction-to-ambient thermal resistance value given is valid for High-K PCB, and is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(2) Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics. The performance of the LP8755 device depends greatly on the care taken in designing the Printed Wiring Board (PWB). The use of low inductance and low serial resistance ceramic capacitors is strongly recommended, while proper grounding is crucial. Attention should be given to decoupling the power supplies. Decoupling capacitors must be connected close to the IC and between the power and ground pins to support high peak currents being drawn from System Power Rail during turn-on of the switching MOSFETs. Keep input and output traces as short as possible, because trace inductance, resistance and capacitance can easily become the performance limiting items.

(3) Due to the nature of the converter operating in PFM Mode/Low-Power Mode, the feedback voltage accuracy specification is for the lower point of the ripple. Thus the converter will position the average output voltage typically slightly above the nominal PWM-Mode output voltage.

(4) Datasheet min/max specification limits are specified by design, test, or statistical analysis.

(5) The power switches in the LP8755 are designed to operate continuously with currents up to the switch current limit thresholds. However, when continuously operating at high current levels there will be significant heat generated within the IC and thus sustained total DC current which the device can support is typically limited by thermal constraints. Thermal issues will become extremely important when designing PCB and the thermal environment of the LP8755. PCB with high thermal efficiency is required to ensure the junction temperature is kept below 125°C. Completing thermal analyses in early stages of the product design process is highly recommended to predict thermal performance at board level. Under high current load conditions the serial bus master device must monitor the temperature of the converter using the Thermal warning feature, see *Protection Features Characteristics*. If the 2nd thermal warning is triggered at 120°C, the application must quickly decrease the load current to keep the converter within its recommended operating temperature.

(6) Datasheet min/max specification limits are specified by design.

# 6.7 6-Phase Buck System Characteristics

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) values at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).

|                      | PARAMETER                                | TEST CONDITIONS                                                                                       | MIN TYP | MAX | UNIT  |

|----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|-----|-------|

|                      |                                          | Programmable via control register <sup>(3)</sup>                                                      |         |     |       |

|                      |                                          | RAMP_B0[2:0] = 000                                                                                    | 30      |     |       |

|                      |                                          | RAMP_B0[2:0] = 001                                                                                    | 15      |     | 1     |

|                      |                                          | RAMP_B0[2:0] = 010                                                                                    | 7.5     |     |       |

| K <sub>RAMP</sub>    | Ramp timer                               | RAMP_B0[2:0] = 011                                                                                    | 3.8     |     | mV/µs |

|                      |                                          | RAMP_B0[2:0] = 100                                                                                    | 1.9     |     |       |

|                      |                                          | RAMP_B0[2:0] = 101                                                                                    | 0.94    |     |       |

|                      |                                          | RAMP_B0[2:0] = 110                                                                                    | 0.47    |     |       |

|                      |                                          | RAMP_B0[2:0] = 111                                                                                    | 0.23    |     |       |

| T <sub>START</sub>   | Start-up time                            | Time from NRST-HIGH to start of switching                                                             | 25      |     | μs    |

| T <sub>RAMP</sub>    | V <sub>OUT</sub> rise time               | Time to ramp from 5% to 95% of V <sub>OUT</sub>                                                       | 20      |     | μs    |

|                      |                                          | Average output current, programmable via control register, $V_{OUT} = 1.1 \text{ V}$ . <sup>(4)</sup> |         |     | -     |

|                      |                                          | PFM_EXIT_B0[2:0] = 000                                                                                | 100     |     |       |

|                      |                                          | PFM_EXIT_B0[2:0] = 001                                                                                | 125     |     |       |

| I <sub>PFM-PWM</sub> | PFM-to-PWM switch–over current threshold | PFM_EXIT_B0[2:0] = 010                                                                                | 150     |     | mA    |

|                      |                                          | PFM_EXIT_B0[2:0] = 011                                                                                | 175     |     |       |

|                      |                                          | PFM_EXIT_B0[2:0] = 100                                                                                | 225     |     |       |

|                      |                                          | PFM_EXIT_B0[2:0] = 101                                                                                | 275     |     |       |

|                      |                                          | PFM_EXIT_B0[2:0] = 110                                                                                | 325     |     |       |

|                      |                                          | PFM_EXIT_B0[2:0] = 111                                                                                | 375     |     |       |

|                      |                                          | Average output current, programmable via control register, $V_{OUT}$ = 1.1 V. <sup>(4)</sup>          |         |     |       |

|                      |                                          | PFM_ENTRY_B0[2:0] = 000                                                                               | 50      |     |       |

|                      |                                          | PFM_ENTRY_B0[2:0] = 001                                                                               | 75      |     |       |

|                      | PWM-to-PFM switchover current            | PFM_ENTRY_B0[2:0] = 010                                                                               | 100     |     |       |

| I <sub>PWM-PFM</sub> | threshold                                | PFM_ENTRY_B0[2:0] = 011                                                                               | 125     |     | mA    |

|                      |                                          | PFM_ENTRY_B0[2:0] = 100                                                                               | 175     |     |       |

|                      |                                          | PFM_ENTRY_B0[2:0] = 101                                                                               | 225     |     |       |

|                      |                                          | PFM_ENTRY_B0[2:0] = 110                                                                               | 275     |     |       |

|                      |                                          | PFM_ENTRY_B0[2:0] = 111                                                                               | 325     |     |       |

|                      |                                          | ADD_PH_B0[2:0] = 001                                                                                  | 400     |     |       |

|                      |                                          | ADD_PH_B0[2:0] = 010                                                                                  | 500     |     |       |

|                      |                                          | ADD_PH_B0[2:0] = 011                                                                                  | 600     |     | I     |

| I <sub>ADD</sub>     | Phase adding level                       | ADD_PH_B0[2:0] = 100                                                                                  | 700     |     |       |

|                      |                                          | ADD_PH_B0[2:0] = 101                                                                                  | 800     |     | mA    |

|                      |                                          | ADD_PH_B0[2:0] = 110                                                                                  | 900     |     |       |

|                      |                                          | ADD_PH_B0[2:0] = 111                                                                                  | 1000    |     | T     |

(1) Junction-to-ambient thermal resistance value given is valid for High-K PCB, and is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(2) Specifications listed in this table are for 6-phase configuration only. Besides the default 6-phase, single-output voltage rail configuration, the 6 switcher cores can be bundled to a variety of different grouping configurations. For applications requiring other DC-DC converter configuration(s), please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) In the real application, achievable output voltage ramp profiles are influenced by a number of factors, including the amount of output capacitance, the load current level, the load characteristic (either resistive or constant-current), and the voltage ramp amplitude. Typical values are measured with typical conditions. The falling edge ramp rate can be limited by the negative current limit I<sub>LIMITN</sub>.

The final PFM-to-PWM and PWM-to-PFM switchover current varies slightly and is dependent on the output voltage, input voltage, and the inductor current level. Typical values are measured with typical conditions.

Copyright © 2013–2015, Texas Instruments Incorporated

(4)

# 6-Phase Buck System Characteristics (continued)

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) values at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).

|                            | PARAMETER                                                       | TEST CONDITIONS                                                                                                | MIN TYP |       | MAX   | UNIT             |

|----------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|-------|-------|------------------|

|                            |                                                                 | SHED_PH_B0[2:0] = 000                                                                                          |         | 300   |       |                  |

|                            |                                                                 | SHED_PH_B0[2:0] = 001                                                                                          |         | 400   |       |                  |

|                            |                                                                 | SHED_PH_B0[2:0] = 010                                                                                          |         | 500   |       |                  |

| SHED                       | Phase shedding level                                            | SHED_PH_B0[2:0] = 011                                                                                          |         | 600   |       |                  |

|                            |                                                                 | SHED_PH_B0[2:0] = 100                                                                                          |         | 700   |       |                  |

|                            |                                                                 | SHED_PH_B0[2:0] = 101                                                                                          |         | 800   |       |                  |

|                            |                                                                 | SHED_PH_B0[2:0] = 110                                                                                          |         |       |       |                  |

|                            | Line regulation                                                 | $2.5 \text{ V} \le \text{V}_{\text{VINBXX}} \le 5 \text{ V}$<br>I <sub>LOAD</sub> = 1 Å, forced PWM            |         | 0.05  |       | %/V              |

|                            | Load regulation in PWM mode of operation                        | 100 mA $\leq$ I <sub>LOAD</sub> $\leq$ 10 A, Differential sensing enabled                                      |         | 0.2   |       | %/A              |

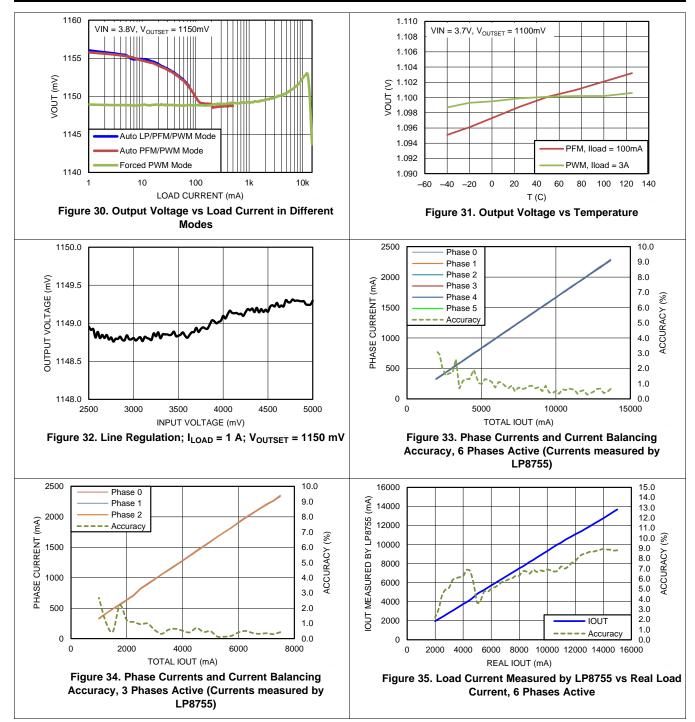

|                            |                                                                 | AUTO (no Low-Power PFM) mode, $\rm I_{OUT}$ 0.5 mA $\rightarrow$ 500 mA $\rightarrow$ 0.5 mA, 100 ns load step |         | ±30   |       | mV               |

| ΔV <sub>OUT</sub>          | Transient load step response                                    | PWM mode, $I_{OUT}$ 0.6 A $\rightarrow$ 2 A $\rightarrow$ 0.6 A, 400-ns load step                              |         | ±20   |       | mV               |

|                            |                                                                 | PWM mode, $I_{OUT} 1 A \rightarrow 8 A \rightarrow 1 A$ , 400-ns load step                                     |         | ±60   |       | mV               |

|                            | Transient line response                                         | $V_{VINBXX}$ stepping 3.3 V <> 3.8 V, $t_r$ = $t_f$ = 10 $\mu s,$ $l_{OUT}$ = 2000 mA DC                       |         | ±15   |       | mV               |

| 1                          | Output oursent                                                  | DC load each phase                                                                                             |         |       | 2500  |                  |

| I <sub>OUT</sub>           | Output current                                                  | Six phases combined <sup>(5)</sup>                                                                             |         |       | 15000 | mA               |

| C <sub>OUT</sub>           | Output capacitance <sup>(6)</sup>                               | Effective capacitance during operation, $V_{OUT} = 0.6 V$ to 1.67 V, Min value over $T_A -40^{\circ}C$ to 85°C | 30      | 50    |       | μF               |

| C <sub>IN</sub>            | Input capacitance on each input voltage rail <sup>(6)(7)</sup>  | Effective capacitance during operation, 2.5 V $\leq$ V <sub>VINBXX</sub> $\leq$ 5 V                            | 2.5     | 10    |       | μF               |

| L                          | Output inductance                                               | Effective inductance during operation                                                                          | 0.25    | 0.47  | 1     | μH               |

| <b>I<sub>BALANCE</sub></b> | Current balancing accuracy                                      | I <sub>OUT</sub> ≥ 1000 mA                                                                                     |         | < 10% |       |                  |

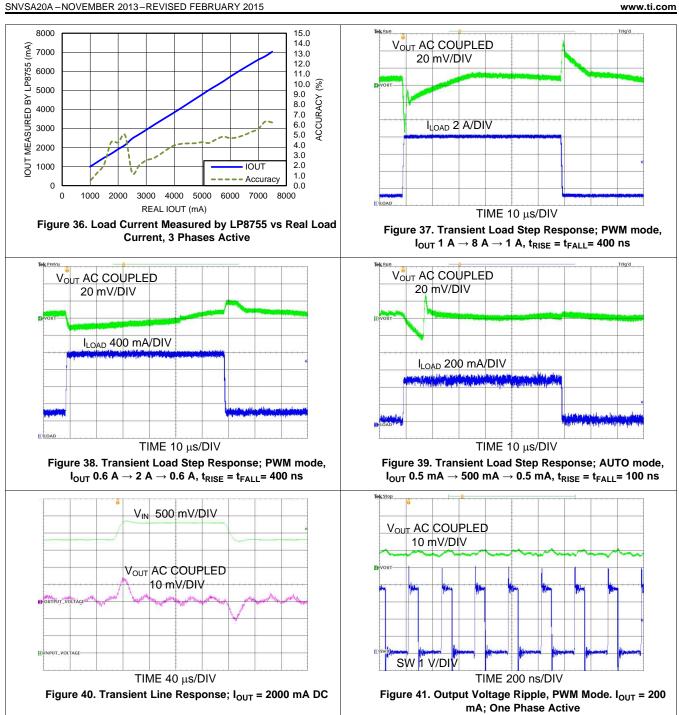

| V <sub>RIPPLE_PWM</sub>    | Output voltage ripple PWM mode, One phase active <sup>(8)</sup> | $C_{OUT}$ ESR = 10 m $\Omega$<br>PWM mode, I <sub>OUT</sub> = 200 mA<br>Switching frequency = 4 MHz            |         | 7     |       | mV <sub>PP</sub> |

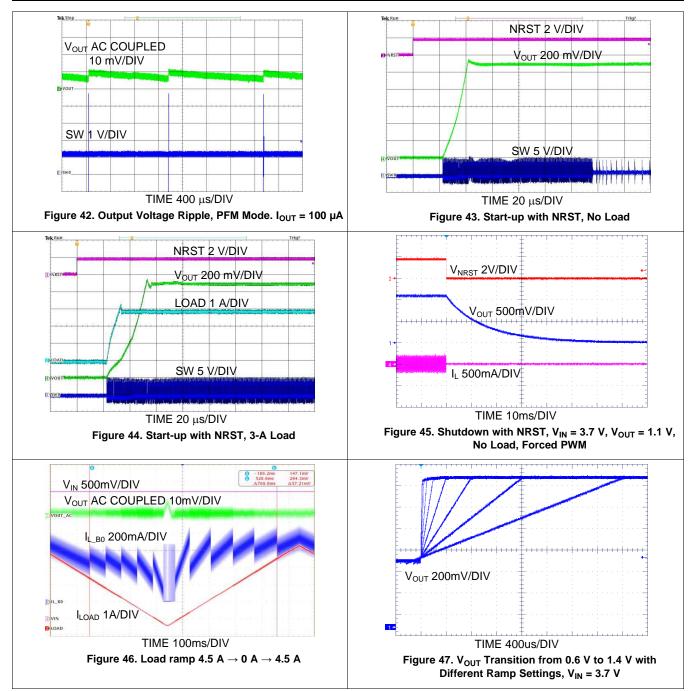

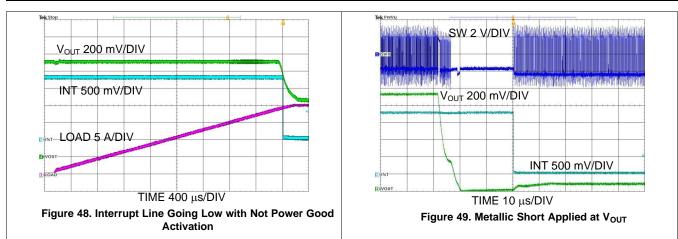

| V <sub>RIPPLE_PFM</sub>    | Output voltage ripple PFM mode <sup>(8)</sup>                   | $\begin{array}{l} C_{OUT} \mbox{ ESR = 10 m} \Omega \\ \mbox{ PFM mode} \\ I_{OUT} = 100 \ \mu A \end{array}$  |         | 8     |       | mV <sub>PP</sub> |

(5) The power switches in the LP8755 are designed to operate continuously with currents up to the switch current limit thresholds. However, when continuously operating at high current levels there will be significant heat generated within the IC and thus sustained total DC current which the device can support is typically limited by thermal constraints. Thermal issues will become extremely important when designing PCB and the thermal environment of the LP8755. PCB with high thermal efficiency is required to ensure the junction temperature is kept below 125°C. Completing thermal analyses in early stages of the product design process is highly recommended to predict thermal performance at board level. Under high current load conditions the serial bus master device must monitor the temperature of the converter using the Thermal warning feature, see *Protection Features Characteristics*. If the 2nd thermal warning is triggered at 120°C, the application must quickly decrease the load current to keep the converter within its recommended operating temperature.

- (6) Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics. The performance of the LP8755 device depends greatly on the care taken in designing the Printed Circuit Board (PCB). The use of low inductance and low serial resistance ceramic capacitors is strongly recommended, while proper grounding is crucial. Attention should be given to decoupling the power supplies. Decoupling capacitors must be connected close to the IC and between the power and ground pins to support high peak currents being drawn from System Power Rail during turn-on of the switching MOSFETs. Keep input and output traces as short as possible, because trace inductance, resistance and capacitance can easily become the performance limiting items.

- (7) In addition to these capacitors, at least one higher value capacitor (for example, 22 μF) should be placed close to the power pins. Note that cores B0-B1 and B3-B4 do have combined power input pins.

- (8) Ripple voltage should be measured at C<sub>OUT</sub> electrode on a well-designed PCB, using suggested inductors and capacitors and with a high-quality scope probe.

### 6-Phase Buck System Characteristics (continued)

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) values at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                | MIN | TYP | MAX | UNIT             |

|------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------------------|

| V <sub>RIPPLE_LP</sub> | Output Voltage Ripple Low-<br>Power PFM mode <sup>(8)</sup> | $C_{OUT}$ ESR = 10 m $\Omega$<br>Low-power PFM mode<br>$I_{OUT}$ = 100 $\mu$ A |     | 8   |     | mV <sub>PP</sub> |

### 6.8 Protection Features Characteristics

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).

| PARAMETER            |                                                                    | TEST CONDITIONS                                                                     | MIN     | TYP      | MAX  | UNIT |

|----------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------|----------|------|------|

| VOLTAGE              | MONITORING                                                         |                                                                                     | · · · · |          |      |      |

| V <sub>PG</sub>      | Power good threshold voltage                                       | Power good threshold for voltage decreasing, % of setting, V <sub>OUT</sub> = 1.1 V |         | 90%      |      |      |

| V <sub>OVP</sub>     | Input overvoltage protection trigger point <sup>(3)(4)</sup>       | V <sub>IN</sub> rising. Voltage monitored on VDDA5V pin                             | 5.15    | 5.3 5.45 |      | V    |

| V <sub>UVLO</sub>    | Input undervoltage lockout (UVLO) turn-on threshold <sup>(3)</sup> | V <sub>IN</sub> falling. Voltage monitored on VDDA5V pin                            | 2.15    | 2.25     | 2.35 | V    |

| V <sub>SCP</sub>     | Output short-circuit fault threshold                               | Detected by sensing the voltage on converter output with respect to GND.            |         | 400      |      | mV   |

| t <sub>MASKSCP</sub> | SCP masking time                                                   | Triggered by converter start-up, specified by design                                |         | 400      |      | μs   |

|                      |                                                                    | Triggered by converter start-up, specified by design                                |         | 400      |      | μs   |

|                      |                                                                    | Triggered by VSET transition, specified by design<br>Slew Rate setting mV/µs        |         |          |      |      |

|                      |                                                                    | 30                                                                                  |         | 50       |      |      |

| +                    | Power Good masking time                                            | 15                                                                                  |         | 100      |      |      |

| t <sub>MASKPG</sub>  | Fower Good masking time                                            | 7.5                                                                                 |         | 200      |      |      |

|                      |                                                                    | 3.8                                                                                 |         | 400      |      |      |

|                      |                                                                    | 1.9                                                                                 | 800     |          |      | μs   |

|                      |                                                                    | 0.94                                                                                | 1600    |          |      |      |

|                      |                                                                    | 0.47                                                                                | 3200    |          |      |      |

|                      |                                                                    | 0.23                                                                                |         | 6400     |      |      |

(1) Junction-to-ambient thermal resistance value given is valid for High-K PCB, and is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(2) Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics. The performance of the LP8755 device depends greatly on the care taken in designing the Printed Circuit Board (PCB). The use of low inductance and low serial resistance ceramic capacitors is strongly recommended, while proper grounding is crucial. Attention should be given to decoupling the power supplies. Decoupling capacitors must be connected close to the IC and between the power and ground pins to support high peak currents being drawn from System Power Rail during turn-on of the switching MOSFETs. Keep input and output traces as short as possible, because trace inductance, resistance and capacitance can easily become the performance limiting items.

(3) Undervoltage lockout (UVLO) and overvoltage protection (OVP) circuits shut down the LP8755 when the system input voltage is outside the desired operating range.

(4) Limits for OVP trigger points apply when  $V_{VIOSYS}$  is high. False OVP alarm may occur, if the input voltage rises close to 5 V while  $V_{VIOSYS}$  is low.

# **Protection Features Characteristics (continued)**

Minimum (MIN) and maximum (MAX) limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; typical (TYP) at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted).

|                                 | PARAMETER                    | TEST CONDITIONS                                                     | MIN | TYP | MAX | UNIT |  |  |

|---------------------------------|------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|--|--|

| THERMAL SHUTDOWN AND MONITORING |                              |                                                                     |     |     |     |      |  |  |

| T <sub>SHUT</sub>               | Thermal shutdown (TSD)       | Threshold, Temperature rising                                       |     | 150 |     |      |  |  |

|                                 |                              | Hysteresis                                                          | 25  |     |     |      |  |  |

|                                 | Thermal warning              | Temperature rising, 1 <sup>st</sup> warning, Interrupt only         |     | 85  |     | °C   |  |  |

| -                               |                              | Hysteresis                                                          | 10  |     |     |      |  |  |

| I <sub>WARN</sub>               | Thermal warning prior to TSD | Temperature rising, 2 <sup>nd</sup> warning, Interrupt and flag set | 120 |     |     |      |  |  |

|                                 |                              | Hysteresis                                                          |     | 10  |     |      |  |  |

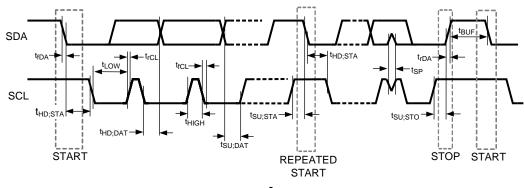

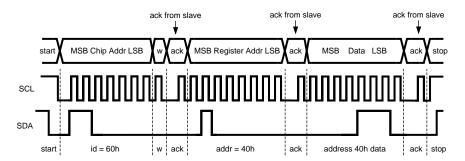

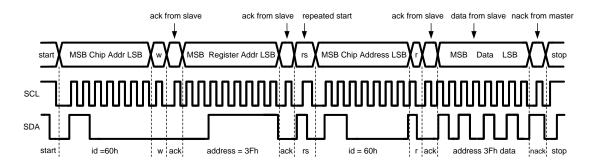

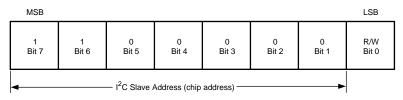

### 6.9 I<sup>2</sup>C Serial Bus Timing Parameters

Serial bus address is selected by the ADDR pin. Connect the pin to GND (addr = 60h), VIOSYS (addr = 61h), SDASYS (addr = 62h), or SCLSYS (addr = 63h). Both of the serial buses share the same address; that is, if addr = 60h is selected for the System bus, the Dynamic Voltage Scaling bus will respond to the same address. Start conditions are used to secure the  $I^2C$  slave address. During the  $I^2C$  bus start condition, it is detected whether the ADDR is connected to SDASYS, SCLSYS, GND, or VIOSYS. The  $I^2C$  host should allow at least 500 µs before sending data to the LP8755 after the rising edge of the VIOSYS line.

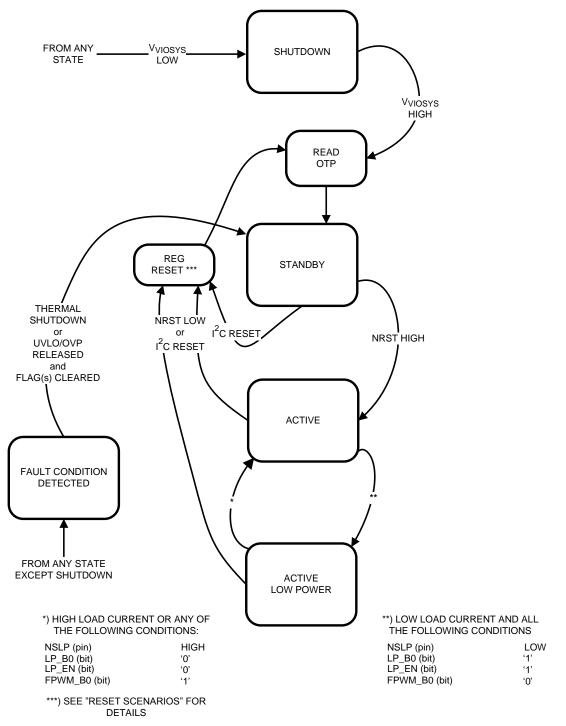

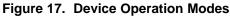

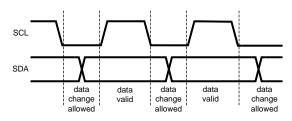

These specifications are ensured by design. Limits apply over the full ambient temperature range  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ,  $V_{VDDA5V} = V_{VINBXX} = 3.7 \text{ V}$ ,  $V_{VIOSYS} = V_{NRST} = 1.8 \text{ V}$ ,  $V_{OUT} = 1.1 \text{ V}$  (unless otherwise noted) (See Figure 1).

|                     |                           |                                                            | MIN | NOM   | MAX  | UNIT |

|---------------------|---------------------------|------------------------------------------------------------|-----|-------|------|------|

| DIGITAL 1           | TIMING SPECIFICATIONS (SC | CL, SDA) <sup>(1)(2)(3)</sup>                              |     |       |      |      |

|                     |                           | Standard mode                                              |     |       | 100  | kHz  |

| 4                   | Carial alask fraguenau    | Fast mode                                                  |     |       | 400  | kHz  |

| f <sub>CLK</sub>    | Serial clock frequency    | High-speed mode, $C_b = 100 \text{ pF} \text{ (max)}$      |     |       | 3.4  | MHz  |

|                     |                           | High-speed mode, $C_b = 400 \text{ pF} (\text{max})^{(4)}$ |     |       | 1.7  | MHz  |

|                     |                           | Standard mode                                              | 4.7 |       |      |      |

| +                   | SCL low time              | Fast mode                                                  | 1.3 |       |      | μs   |

| t <sub>LOW</sub>    | SCL IOW UITIE             | High-speed mode, $C_b = 100 \text{ pF} \text{ (max)}$      | 160 |       |      | ~~   |

|                     |                           | High-speed mode, $C_b = 400 \text{ pF} (\text{max})^{(4)}$ | 320 |       |      | ns   |

|                     |                           | Standard mode                                              | 4   |       |      |      |

| +                   | SCL high time             | Fast mode                                                  | 0.6 |       |      | μs   |

| t <sub>HIGH</sub>   | SCL nigh unie             | High-speed mode, $C_b = 100 \text{ pF} \text{ (max)}$      | 60  |       |      | 20   |

|                     |                           | High-speed mode, $C_b = 400 \text{ pF} (\text{max})^{(4)}$ | 120 |       |      | ns   |

|                     |                           | Standard mode                                              | 250 |       |      |      |

| t <sub>SU;DAT</sub> | Data setup time           | Fast mode                                                  | 100 |       |      | ns   |

|                     |                           | High-speed mode                                            | 10  |       |      |      |

|                     |                           | Standard mode                                              | 0   |       | 3.45 | μs   |

|                     | Data hold time            | Fast mode                                                  | 0   | 0 0.9 |      |      |

| t <sub>HD;DAT</sub> |                           | High-speed mode, $C_b = 100 \text{ pF} \text{ (max)}$      | 0   | 0 70  |      |      |

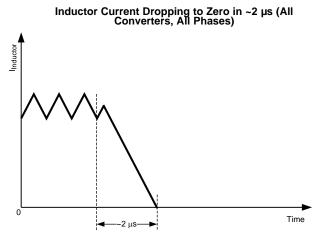

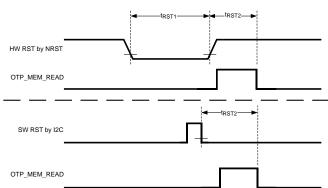

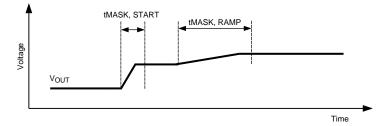

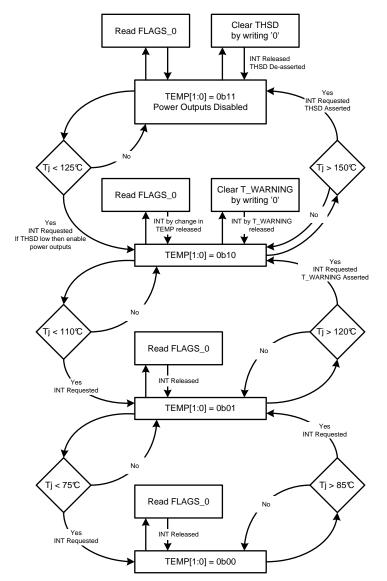

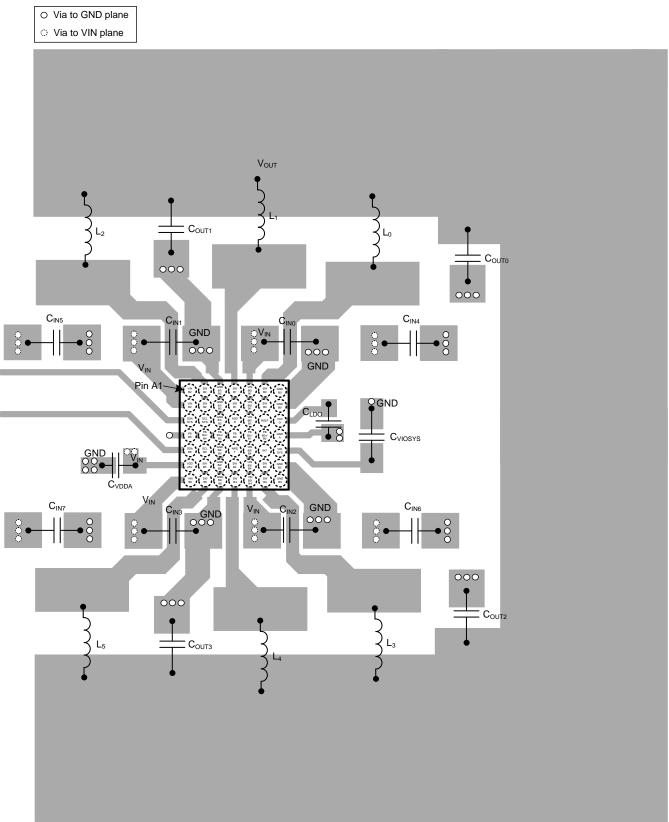

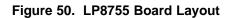

|                     |                           | High-speed mode, $C_b = 400 \text{ pF} (\text{max})^{(4)}$ | 0   |       | 150  | ns   |