# PST-360: Instructions for use

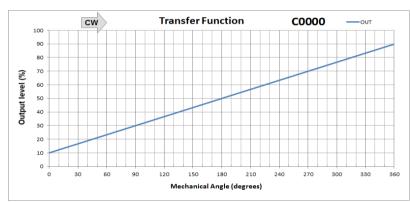

HOW TO ORDER: PST360G2-1S-C0000-ERA360-05K OUTPUT TYPE: Simple - SPI Protocol SIGNAL OUTPUT 10% to 90% SPI Protocol (360° ERA)

ROTOR: 14mm OUTPUT FUNCTION: Curve 0000 SUPPLY VOLTAGE: 5V ± 10% TEMPERATURE: -40 °C to +125 °C

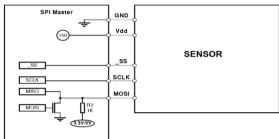

## Connections scheme:

| Wire color                                                                                                                | Connection                    | Recommended connections |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|--|--|--|--|--|--|--|

| Brown                                                                                                                     | Power supply<br>Vdd: 5V ± 10% | SPI Master CND          |  |  |  |  |  |  |  |

| Blue                                                                                                                      | Ground                        |                         |  |  |  |  |  |  |  |

| Black                                                                                                                     | MOSI                          |                         |  |  |  |  |  |  |  |

| White                                                                                                                     | /SS                           |                         |  |  |  |  |  |  |  |

| Grey                                                                                                                      | SCLK                          |                         |  |  |  |  |  |  |  |

| A WARNING<br>-In order to minimize the possibility of short circuits, we recommend to connect the power supply at the end |                               |                         |  |  |  |  |  |  |  |

## Signal output:

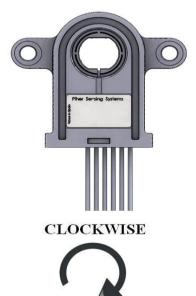

### Reference position:

Rotor is shown at zero position

To get more information about our full Legal Disclaimer and Limitation of Liability please visit www.piher.net/disclaimer\_hollow\_shaft.pdf. Users acknowledge that they have read this legal disclaimer and agree to abide by its terms. Piher Sensors & Controls SA \*\*\* confidential \*\*\*

Polígono Industrial Municipal, Vial T2, No 22, 31500 Tudela, Navarra, Spain

Piher is an Amphenol<sup>™</sup> company. RM Navarra Tomo 551, Folio 7, Hoja 5.580 CIF/VAT ESA31169907

Tel: +34 948 820 450 Fax: +34 948 824 050 www.piher.net

## SPI Protocol information

The PST-360 features a digital Serial protocol mode. The PST-360 is considered as a Slave node. The serial protocol of the PST-360 is a three wires protocol (/SS, SCLK, MOSI-MISO):

- /SS pin is a 5V tolerant digital input.

- SCLK pin is a 5V tolerant digital input.

- MOSI-MISO pin is a 5V tolerant open drain digital input/output.

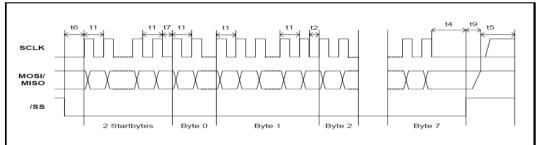

### 1. Timing

To synchronize communication, the master deactives /SS high for at least t5 (1.5 ms). In this case, the Slave will be ready to receive a new frame. The master can re-synchronize at any time, even in the middle of a byte transfer.

| Timings              | Min <sup>(1)</sup> | Max     | Remarks                                                                                         |  |  |  |  |  |  |  |  |

|----------------------|--------------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| t1                   | t1 6.9 μs          |         | No capacitive load on MISO.<br>t1 is the minimum clock period for any bits within a byte.       |  |  |  |  |  |  |  |  |

| t2                   | 37.5 µs            | -       | t2 the minimum time between any other byte.                                                     |  |  |  |  |  |  |  |  |

| t4                   | 6.9 µs             | -       | Time between last clock and /SS=high=chip de selection.                                         |  |  |  |  |  |  |  |  |

| t5                   | 1500 µs            | -       | Minimum /SS=Hi time where it's guaranteed that a frame re-synchronizations will be<br>started.  |  |  |  |  |  |  |  |  |

| t5                   | 0 µs               | -       | Maximum /SS=Hi time where it's guaranteed that NO frame re-synchronizations will be<br>started. |  |  |  |  |  |  |  |  |

| t6                   | 6.9 µs             | -       | The time t6 defines the minimum time between /SS=Lo and the first clock edge.                   |  |  |  |  |  |  |  |  |

| t7                   | 45 µs              | -       | t7 is the minimum time between the StartByte and the Byte0.                                     |  |  |  |  |  |  |  |  |

| t9                   | -                  | < 1 µs  | Maximum time between /SS=Hi and MISO Bus High-Impedance.                                        |  |  |  |  |  |  |  |  |

| T <sub>StartUp</sub> | -                  | < 16 µs | Minimum time between reset-inactive and any master signal change.                               |  |  |  |  |  |  |  |  |

<sup>(1)</sup> Timings shown for oscillator base frequency of 7MHz (Slow mode)

## 2. Slave Reset

On internal soft failures the Slave resets after 1 second or after an (error) frame is sent. On internal hard failures the Slave resets itself. In that case, the Serial protocol will not come up. The serial protocol link is enabled only after the completion of the first synchronization (the Master deactivates /SS for at least 15).

## 3. Slave Start-Up

The Slave start-up (after power-up or an internal failure) takes 16 ms. Within this time /SS and SCLK is ignored by the Slave. The first frame can therefore be sent after 16 ms. MISO is Hi-Z (i.e. Hi-Impedance) until the Slave is selected by its /SS input. MTS-360 will cope with any signal from the Master while starting up.

To get more information about our full Legal Disclaimer and Limitation of Liability please visit www.piher.net/disclaimer\_hollow\_shaft.pdf. Users acknowledge that they have read this legal disclaimer and agree to abide by its terms. Piher Sensors & Controls SA \*\*\*\* confidential \*\*\* Polígono Industrial Municipal, Vial T2, No 22, 31500 Tudela, Navarra, Spain Tel: +34 948 820 450 Fax: +34 948 824 050 www.piher.net Piher is an Amphenol<sup>™</sup> company

RM Navarra Tomo 551, Folio 7, Hoja 5.580 CIF/VAT ESA31169907

## SPI Protocol information

## 4. Frame Layer

#### 4.1. Command Device Mechanism

Before each transmission of a data frame, the Master should send a byte AAh to enable a frame transfer. The latch point for the angle measurement is at the last clock before the first data frame byte.

#### 4.2. Data Frame Structure

A data frame consists of 10 bytes:

2 start bytes (AAh followed by FFh)

- 2 data bytes (DATA16 most significant byte first)

- · 2 inverted data bytes (/DATA16 most significant byte first)

- 4 all-Hi bytes

The Master should send AAh (55h in case of inverting transistor) followed by 9 bytes FFh. The Slave will answer with two bytes FFh followed by 4 data bytes and 4 bytes FFh.

#### 4.3. Timing

There are no timing limits for frames: a frame transmission could be initiated at any time. There is no inter-frame time defined.

#### 4.4. Data structure

The DATA16 could be a valid angle, or an error condition. The two meanings are distinguished by the LSB.

| DATA16: Angle A[13:0] with (Angle Span)/2 <sup>14</sup> |       |                     |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|---------------------------------------------------------|-------|---------------------|---------|--------|------|-----------------------------------------------------------------------------------------|--------|--------|-------|-------|----------------------|---------|----|----|-----|--|

|                                                         |       | Most                | Signifi | cant B | vte  | le l                                                                                    |        |        |       |       | ess Significant Byte |         |    |    |     |  |

|                                                         | ISB   |                     | l       |        | ,    |                                                                                         | LSB    | MSB    |       |       | Cigini               | locarre | J  |    | LSB |  |

|                                                         | A13 A | 12 A11              | A10     | A9     | A8   | A7                                                                                      | A6     | A5     | A4    | A3    | A2                   | A1      | A0 | 0  | 1   |  |

|                                                         |       |                     |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

| DATA16: Error                                           |       |                     |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

| Most Significant By                                     |       |                     |         |        |      | te Less Significant Byte                                                                |        |        |       |       |                      |         |    |    |     |  |

| MSB                                                     |       |                     |         |        | 1    |                                                                                         | LSB    | MSB    |       |       |                      |         |    |    | LSB |  |

| 1                                                       | E15 E | 14 E13              | E12     | E11    | E10  | E9                                                                                      | E8     | E7     | E6    | E5    | E4                   | E3      | E2 | E1 | E0  |  |

|                                                         |       |                     |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | BIT   | NAME                |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | _E0   | 0                   |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E1    | 1                   |         |        |      |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E2    | F_ADCN              |         |        |      | ADC Failure                                                                             |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E3    | F_ADCSATURA         |         |        |      | ADC Saturation (Electrical failure or field too strong)                                 |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E4    | F_RGTC              | DOLOV   | V      |      | Analog Gain Below Trimmed Threshold                                                     |        |        |       |       |                      |         |    |    |     |  |

|                                                         |       |                     |         |        |      | (Likely reason : field too weak)                                                        |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E5    | F_MAG               |         |        |      | Magnetic Field Too Weak                                                                 |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E6    | F_MAG               |         |        |      | Magnetic Field Too Strong                                                               |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E7    | F_RGTC              | OHIG    | н      |      | Analog Gain Above Trimmed Threshold                                                     |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E8    | F FGC               |         |        |      | (Likely reason : field too strong)                                                      |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E9    |                     |         |        |      | Never occurring in serial protocol<br>Analog Chain Rough Offset Compensation : Clipping |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E10   | F_ROCLAMP<br>F MT7V |         |        |      | Device Supply VDD Greater than 7V                                                       |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E11   | -                   | /       |        | De   | vice c                                                                                  | supply | VUU GI | eater | ulali | / V                  |         |    |    |     |  |

|                                                         | E12   |                     |         |        | -    |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E13   | -                   |         |        | -    |                                                                                         |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E14   | F DACM              |         | OR     | Ne   | Never occurring in serial protocol                                                      |        |        |       |       |                      |         |    |    |     |  |

|                                                         | E15   | -                   |         |        | 1.10 |                                                                                         |        |        |       |       | -                    |         |    |    |     |  |

#### 4.5. Angle Calculation

All communication timing is independent (asynchronous) of the angle data processing. The angle is calculated continuously by the Slave:

#### • Slow mode: every 1.5 ms at most.

The last angle calculated is hold to be read by the Master at any time. Only valid angles are transferred by the Slave, because any internal failure of the Slave will lead to a soft reset.

#### 4.6. Error handling

CIF/VAT ESA31169907

In case of any errors listed in the previous table, the Serial protocol will be initialized and the error condition can be read by the master. The Slave will perform a soft reset once the error frame is sent.

In case of any other errors (ROM CRC error, EEPROM CRC error, RAM check error, intelligent watchdog error ...) the Slave's serial protocol is not initialized. The MOSI/MISO pin will stay Hi-impedant (no error frames are sent).

Information contained in and/or attached to this document may be subject to export control regulations of the European Community, USA, or other countries. Each recipient of this document is responsible to ensure that usage and/or transfer of any information, contained in this document complies with all relevant export control regulations. If you are in any doubt about the export control restrictions that apply to this information, please contact the sender immediately. For any Piher Sensors & Controls SA Exports, Note: All products / technologies are EAR99 Classified commodities. Exports from the United States are in accordance with the Export Administration Regulations. Diversion contrary to US law is prohibited. To get more information about our full Legal Disclaimer and agree to abide by its terms.

Piher Sensors & Controls SA \*\*\* confidential \*\*\* Tel: +34 948 820 450 Fax: +34 948 820 450 Fax: +34 948 824 050 www.piher.net/