# DATA SHEET (DOC No. HM0360-MWA-00FP963-DS)

# <sup>>></sup>HM0360-MWA-00FP963

Compact Camera Module Preliminary version 01 July, 2021

Himax Imaging, Ltd.

**Compact Camera Module**

### **Revision History**

| Version | Date       | Description of changes |

|---------|------------|------------------------|

| 01      | 2021/07/30 | New setup.             |

#### **List of Contents**

| 1.      | Senso  | r Specification                                                                                                                                                     | 7                |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ••      |        | -eatures                                                                                                                                                            |                  |

|         |        | Application                                                                                                                                                         |                  |

|         |        | Key parameters                                                                                                                                                      |                  |

|         |        | /GA window readout                                                                                                                                                  |                  |

|         |        | Electrical specification                                                                                                                                            |                  |

|         |        | I.5.1. Operating voltages                                                                                                                                           |                  |

|         |        | I.5.2. DC characteristics                                                                                                                                           |                  |

|         |        | I.5.3. Master Clock (MCLK) input                                                                                                                                    |                  |

|         | 16     | Power up sequence                                                                                                                                                   | 12               |

| 2       | Camor  | ra Modulo Specification                                                                                                                                             | IS               |

| ۷.      | 21     | ra Module Specification<br>Pin map and description of camera module                                                                                                 | 1 <u>-</u>       |

|         | 2.1.   | Mechanical drawing of camera module                                                                                                                                 | 15<br>1 <i>6</i> |

|         | 2.2. 1 | Application schomatic of camera module                                                                                                                              | I C              |

|         | 2.3. 7 | Application schematic of camera module                                                                                                                              | IC               |

|         | 2      | 2.2. Leveut consideration                                                                                                                                           | ١٠               |

| 2       | Ontion | V.S.Z. Layout consideration                                                                                                                                         | IC               |

| Э.      | 2 1 N  | Mochanical drawing of entical lane                                                                                                                                  | 17<br>17         |

|         | 22 0   | Specification of optical lane                                                                                                                                       | 17<br>17         |

| 4       | J.Z.   | Quality Specification                                                                                                                                               | 1 <i>1</i>       |

| 4.<br>5 | Polish | ility Tost Conditions                                                                                                                                               | IC               |

| ٥.<br>د | Inches | Al Lens Specification  Mechanical drawing of optical lens  Specification of optical lens  Quality Specification  Illity Test Conditions  Constitution Specification | เจ               |

| 0.      | 61 C   | Sampling plan /isual inspection method nspection item Remark                                                                                                        | <b>.∠</b> (      |

|         | 62 \   | /isual inspection method                                                                                                                                            | 20               |

|         | 6.2. V | nspection item                                                                                                                                                      | 20               |

|         | 6.0. 1 | Pemark 701 A 701 A                                                                                                                                                  | 20               |

|         | 6.5 A  | Appearance / Dimension check                                                                                                                                        | ∠\               |

|         | 0.5. F | Appearance / Dimension check                                                                                                                                        | ∠                |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        | 4 00 60                                                                                                                                                             |                  |

|         |        | ∠L                                                                                                                                                                  |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

|         |        |                                                                                                                                                                     |                  |

## **Compact Camera Module**

## List of Figures

| Figure 1.1: VGA resolution pixel readout             | 10 |

|------------------------------------------------------|----|

| Figure 1.2: Power up sequence                        |    |

| Figure 2.1: Mechanical drawing of camera module      |    |

| Figure 2.2: Reference circuit of camera module (CSP) |    |

| Figure 3.1: Mechanical drawing of optical lens       |    |

#### List of Tables

| Table 1.1: Operating voltages                       | 11 |

|-----------------------------------------------------|----|

| Table 1.2: DC characteristics                       |    |

| Table 1.3: Master Clock (MCLK) timing               |    |

| Table 1.4: Power up sequence timing                 |    |

| Table 2.1: Pin map and description of camera module |    |

| Table 3.1: Specification of optical lens            |    |

| Table 4.1: Image quality specification              |    |

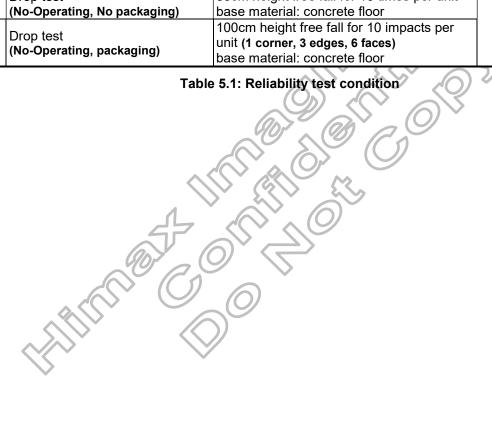

| Table 5.1: Reliability test condition               |    |

# >> HM0360-MWA-00FP963

Compact Camera Module

### Important Notice

July, 2021

#### **Disclaimer**

Himax Imaging reserves the right to modify this documentation without prior notice. The information appearing in this publication is believed to be accurate and reliable. However, Himax Imaging makes no warranty for any errors which may appear in this document. Contact Himax Imaging to obtain the latest version of product specifications before placing your order. No responsibility is assumed by Himax Imaging, Ltd. for any infringement of patent or other rights of third parties which may result from its use. Products described herein are intended for use in normal commercial applications. Please note that application circuits illustrated in this document are for reference purposes only.

## **All Rights Reserved**

The following are trademarks of Himax Imaging Ltd.: Himax Imaging, BrightSense, ClearSense, the Himax Imaging logo symbol. The use of any trademark, trade name, or service mark found in this document without the owner's express written consent is strictly prohibited.

Himax Imaging strives to produce quality documentation and welcomes your feedback. Please send comments or suggestions to hi marketing@himaximaging.com.

Compact Camera Module

### **Preliminary Version 01**

July, 2021

## 1. Sensor Specification

The HM0360 is an ultra-low power, Back Side Illuminated (BSI) CMOS image sensor designed for energy efficient smart vision applications, such as object-specific classification, tracking and identification. The advanced 3.6µ low noise, deep diode pixel achieves superior image quality performance to enable monitoring, detection and video capture in low light environments while minimizing the use of external, power consuming, LED illuminators.

The HM0360 Always On Sensor architecture delivers a target current consumption of 256µA in AoS monitor mode and 8.6mA in VGA 60 frames per second read out mode. In order to reduce host processor loading, camera latency and system power consumption, the HM0360 features on-chip oscillator with automatic external reference clock detection, automatic frame mode switch, fast sensor initialization, <2ms frame trigger time, context switching and instant frame update. The sensor offers several monitoring options with programmable interrupt thereby allowing the host processor to be placed in low power standby until notified by the sensor.

The HM0360 is available in a compact Chip Scale Package (CSP) compatible with standard SMT reflow process. The sensor supports multiple power supply configurations and uses few passive components to enable a highly compact camera module design for next generation energy efficient, smart camera devices.

## HM0360-MWA-00FP963

**Compact Camera Module**

DATASHEET Preliminary V01

#### 1.1. Features

- Ultra Low Power, high sensitivity, low noise VGA sensor

- Operates 8.6mA VGA 60 FPS down to 256µA in monitor mode

- Automatic wake and sleep operation with programmable event interrupt to wake host processor

- On chip high precision oscillator, auto exposure / gain, ambient light sensor and zone detection

- Metered exposure provides well exposed first frame and after extended sleep (blanking) period

- External frame synch and stereo camera support

- Flexible binning, subsampling and region of interest

- Embedded line provides metadata frame, AE statistics, zone trigger and other interrupt event information

- On-chip high precision oscillator and LDO

- 1-lane MIPI CSI2 and 8-bit parallel/serial data format that supports 1-bit, 4-bit and 8-bit protocol

- I2C 2-wrie serial interface supporting burst operation for fast register access

- < 13 mm2 CSP sensor package option</li>

- High CRA for low profile module design

#### 1.2. Application

- Cellular and mobile phones

- · Digital video camcorders

- PC multimedia

- Tablets

# >> HM0360-MWA-00FP963

DATASHEET Preliminary V01

#### 1.3. Key parameters

| Parameters                       |            | Value                                  |  |  |

|----------------------------------|------------|----------------------------------------|--|--|

| Image sensor part number         |            | HM0360-MWA                             |  |  |

| Pixel array (Active / Effective) |            | 656 x 496 / 640 x 480                  |  |  |

| Pixel size                       |            | 3.6µm x 3.6µm / BSI                    |  |  |

| Image diagonal                   |            | 2.88mm (1/6")                          |  |  |

| Color filter array               |            | Bayer, Monochrome                      |  |  |

| Shutter type                     |            | Electronic Rolling Shutter             |  |  |

| Frame rate @24MHz                |            | QQVGA 1 FPS to VGA 60 FPS              |  |  |

| S/N ratio (Max.)                 |            | 45.5 dB                                |  |  |

| Dynamic range (1x)               |            | 60 dB                                  |  |  |

| Concitivity                      |            | 5.5V / Lux-sec @530nm                  |  |  |

| Sensitivity                      |            | 15V / (µW-cm <sup>-2</sup> sec) @850nm |  |  |

| Pixel CRA (Max.)                 |            | 35.74°                                 |  |  |

|                                  | AVDD       | 2.8V                                   |  |  |

| Supply voltage                   | DVDD       | 1.2V (Internal LDO)                    |  |  |

|                                  | IOVDD      | 1.8V / 2.8V                            |  |  |

| Input reference clock            |            | 6 – 24MHz                              |  |  |

| Internal oscillator              |            | 48MHz                                  |  |  |

| Serial interface                 |            | I2C (1MHz max., single / burst)        |  |  |

| MIPI data format                 |            | 8-bit                                  |  |  |

| Parallel / Serial data format    |            | 8-bit, 4-bit+4-bit / 4-bit / 1-bit     |  |  |

| Current Consumption              |            | QVGA( <b>S2</b> ), 2FPS: 179 μA        |  |  |

| (8-bit parallel interface, Typ.) |            | QVGA, 60FPS: 5.25 mA                   |  |  |

| (8-bit paraller interface, Typ.) | GOF        | VGA, 60FPS: 8.6 mA                     |  |  |

| Temperature                      |            | Operating -40 °C to 85 °C              |  |  |

| Temperature                      |            | Stable Image 0 °C to 60 °C             |  |  |

| Construction                     |            | 4P >>                                  |  |  |

| EFL                              | /// [[/    | 1.27 mm                                |  |  |

| BFL                              |            | 0.97 mm                                |  |  |

| Image circle                     | 7 (( ) <   | ψ3.3 mm                                |  |  |

| F/No                             |            | 2.4 ± 5%                               |  |  |

| TV distortion                    |            | < 40%                                  |  |  |

|                                  | Horizontal | 98.1°                                  |  |  |

| Field of view Vertical           |            | 73.2°                                  |  |  |

|                                  | Diagonal   | 129.4°                                 |  |  |

| Relative illumination            |            | >65.4% at y=1.0 field                  |  |  |

| Chief ray angle                  |            | < 33.1°                                |  |  |

| Barrel size                      | •          | M5.5 x P0.3                            |  |  |

| Holder size                      |            | 6.5mm x 6.5mm                          |  |  |

| Total track (Barrel to image)    |            | Y=4.36mm                               |  |  |

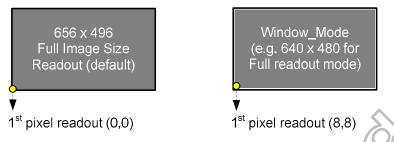

#### 1.4. VGA window readout

The HM0360 full active pixel array of  $656 \times 496$  can be windowed to  $640 \times 480$  by register **0x3030[0]**.

Figure 1.1: VGA resolution pixel readout

#### 1.5. Electrical specification

#### 1.5.1. Operating voltages

| Parameter              | Symbol                |      | Unit      |      |       |  |

|------------------------|-----------------------|------|-----------|------|-------|--|

| Parameter              | Symbol                | Min. | Тур.      | Max. | Ullit |  |

| Analog supply voltage  | $V_{DD-A}$            | 2.6  | 2.8       | 3.0  | V     |  |

| Digital supply voltage | $V_{DD	ext{-}D}$      | 1.08 | 1.2       | 1.32 | V     |  |

| IO supply voltage      | $V_{DD	ext{-}IO}$     | 1.7  | 1.8 / 2.8 | 3.0  | V     |  |

| LDO supply voltage     | V <sub>DD-LDOIN</sub> | 1.7  | 1.8 / 2.8 | 3.0  | V     |  |

**Table 1.1: Operating voltages**

#### 1.5.2. DC characteristics

The power consumptions are measured in color bar ( $C_L = 5pF$ ).

|                                              |                                                       | Condition                                                                     |                     | Spec. |      | 11   |

|----------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|-------|------|------|

| Parameter                                    | Symbol                                                | Condition                                                                     | Min.                | Тур.  | Max. | Unit |

| Average Current Consun                       | nption – Par                                          | allel 8b, External LDO mode                                                   |                     |       |      |      |

|                                              | I <sub>DD-AVDD1</sub>                                 | Video,<br>VGA @ 60 FPS,                                                       | )) <del>-</del> (0) | 1940  | -    | μA   |

| Continuous video output                      | I <sub>DD-DVDD1</sub>                                 | PCLKO free running,                                                           | 9,00                | 4860  | -    | μA   |

|                                              | I <sub>DD-IOVDD1</sub>                                | $V_{DD-A} = 2.8V, V_{DD-D} = 1.2V,$<br>$V_{DD-IO} = 1.8V$                     | \$\frac{1}{2} \     | 1790  | -    | μA   |

|                                              | I <sub>DD-AVDD1</sub>                                 | Auto wake up sleep,<br>QQVGA@ 2 FPS,                                          |                     | 36.6  | -    | μA   |

| S1 (Gate single frame with software standby) | I <sub>DD-DVDD1</sub>                                 | PCLKO gated,<br>V <sub>DD-A</sub> = 2.8V, V <sub>DD-D</sub> = 1.2V,           |                     | 215.6 | -    | μA   |

|                                              | IDD-IOVDD1                                            | V <sub>DD-IO</sub> = 1.8V,<br>XSLEEP high                                     | <u>-</u>            | 4     | -    | μA   |

|                                              | I <sub>DD-AVDD1</sub>                                 | Auto wake up sleep,<br>QQVGA@ 2 FPS,                                          | ı                   | 22.6  | -    | μA   |

| S2 (Gate single frame with hardware standby) | IDD-DVDD1                                             | PCLKO gated,<br>$V_{DD-A} = 2.8V, V_{DD-D} = 1.2V,$                           | ı                   | 70.1  | -    | μΑ   |

|                                              | IDD-IOVDD1                                            | V <sub>DD-IO</sub> = 1.8V,<br>XSLEEP control by host                          | ı                   | 2.5   | -    | μΑ   |

| Software Standby current                     | IDD-SLEEP1                                            | $V_{DD-A}$ = 2.8V, $V_{DD-D}$ = 1.2V, $V_{DD-IO}$ = 1.8V XSLEEP inactive      | -                   | 176   | -    | μA   |

| Hardware Standby current                     | I <sub>DD-SLEEP2</sub>                                | $V_{DD-A} = 2.8V$ , $V_{DD-D} = 1.2V$ , $V_{DD-IO} = 1.8V$<br>XSLEEP active   | -                   | 16    | -    | μA   |

| Average Current Consun                       | Average Current Consumption – MIPI, External LDO mode |                                                                               |                     |       |      |      |

|                                              | I <sub>DD-AVDD1</sub>                                 | Video,<br>VGA @ 60 FPS,                                                       | -                   | 2120  | -    | μA   |

| Continuous video output                      | I <sub>DD-DVDD1</sub>                                 | gated by line, w/o LSLE                                                       | -                   | 8840  | -    | μA   |

|                                              | I <sub>DD-IOVDD1</sub>                                | $V_{DD-A} = 2.8V, V_{DD-D} = 1.2V,$<br>$V_{DD-IO} = 1.8V$                     | -                   | 1     | -    | μA   |

|                                              | IDD-AVDD1                                             | Auto wake up sleep,<br>QQVGA@ 2 FPS,                                          | -                   | 42.4  | -    | μA   |

| S1 (Gate single frame with software standby) | I <sub>DD-DVDD1</sub>                                 | gated by line, w/o LSLE<br>V <sub>DD-A</sub> = 2.8V,V <sub>DD-D</sub> = 1.2V, | -                   | 224.2 | -    | μA   |

|                                              | I <sub>DD-IOVDD1</sub>                                | V <sub>DD-IO</sub> = 1.8V,<br>XSLEEP high                                     | -                   | 4.5   | -    | μΑ   |

| Damamatan                                    | Oh. a.l                | O a malisti a m                                                                |                       | Spec.      |                          | I I m i 4 |

|----------------------------------------------|------------------------|--------------------------------------------------------------------------------|-----------------------|------------|--------------------------|-----------|

| Parameter                                    | Symbol Condition       |                                                                                | Min.                  | Тур.       | Max.                     | Unit      |

|                                              | I <sub>DD-AVDD1</sub>  | Auto wake up sleep,<br>QQVGA@ 2 FPS,                                           | -                     | 26.3       | -                        | μA        |

| S2 (Gate single frame with hardware standby) | I <sub>DD-DVDD1</sub>  | gated by line, w/o LSLE $V_{DD-A} = 2.8V, V_{DD-D} = 1.2V,$                    | -                     | 75.7       | -                        | μΑ        |

|                                              | IDD-IOVDD1             | V <sub>DD-IO</sub> = 1.8V,<br>XSLEEP control by host                           | ı                     | 2.5        | -                        | μΑ        |

| Software Standby current                     | IDD-SLEEP1             | $V_{DD-A}$ = 2.8V, $V_{DD-D}$ = 1.2V,<br>$V_{DD-IO}$ = 1.8V<br>XSLEEP inactive | 1                     | 179        | -                        | μΑ        |

| Hardware Standby current                     | I <sub>DD-SLEEP2</sub> | $V_{DD-A}$ = 2.8V, $V_{DD-D}$ = 1.2V, $V_{DD-IO}$ = 1.8V XSLEEP active         | ı                     | 17         | -                        | μΑ        |

| <b>Average Current Consun</b>                | nption – Har           | dware shutdown                                                                 |                       |            |                          |           |

| Hardware shutdown (Parallel/MIPI)            | $I_{DD}$               | MCLK off                                                                       | $\wedge$              | 1          | -                        | μA        |

| Digital Inputs (MCLK, TR                     | IGGER, SCL             | )                                                                              |                       |            |                          |           |

| Input voltage low                            | $V_{IL}$               | -                                                                              | GND –<br>0.3          | -          | 0.3V <sub>DD-IO</sub>    | V         |

| Input voltage high                           | V <sub>IH</sub>        | -                                                                              | 0.7V <sub>DD-IO</sub> | > -<       | V <sub>DD-IO</sub> + 0.3 | V         |

| Digital Output                               |                        |                                                                                |                       |            |                          |           |

| Output voltage low                           | $V_{OL}$               | \$ C/\-                                                                        | (A)                   | 0-7        | 0.2V <sub>DD-IO</sub>    | V         |

| Output voltage high                          | Vон                    |                                                                                | $0.8V_{DD-10}$        | <b>V</b> - | -                        | V         |

| Tri-state leakage current                    | loz                    |                                                                                |                       | <b>V</b> - | 10                       | μΑ        |

Table 1.2: DC characteristics

### 1.5.3. Master Clock (MCLK) input

| Parameter              | Symbol   | Condition |      | Spec. |      | Unit  |

|------------------------|----------|-----------|------|-------|------|-------|

| Parameter              | Symbol   | Condition | Min. | Тур.  | Max. | Ullit |

| Input frequency        | MCLK     |           | 6    | -     | 24   | MHz   |

| Input clock duty cycle | MCLKDUTY |           | 45   | -     | 55   | %     |

Table 1.3: Master Clock (MCLK) timing

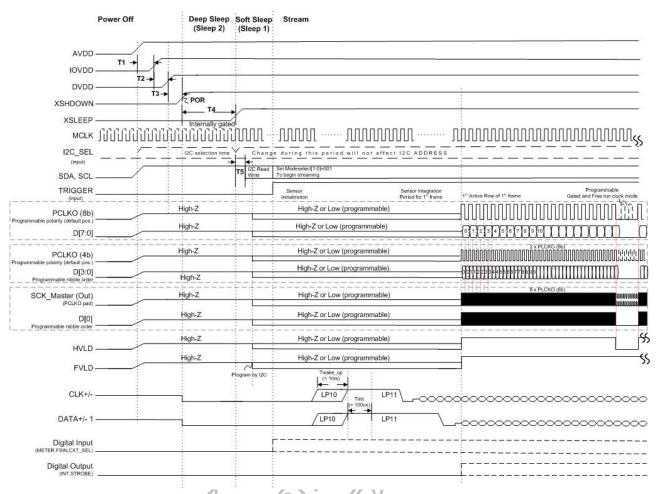

#### 1.6. Power up sequence

Figure 1.2: Power up sequence

| Parameter                       | Symbol |      | l lmi4 |      |      |

|---------------------------------|--------|------|--------|------|------|

| Faranietei                      | Symbol | Min. | Тур.   | Max. | Unit |

| AVDD to IOVDD                   | T1     | 0    | -      | 8    | S    |

| IOVDD to DVDD                   | T2     | 0    | -      | ∞    | S    |

| DVDD to XSHDOWN (External DVDD) | T3     | 0    | -      | ∞    | S    |

| XSHDOWN to XSLEEP               | T4     | 400  | -      | -    | μs   |

| XSLEEP to 1st I2C command       | T5     | 38.6 | -      | -    | μs   |

Note: (1) The minimum timing of T4 is 50µs when using external LDO mode.

Table 1.4: Power up sequence timing

<sup>(2)</sup> The maximum timing for power on reset time (POR) is 50µs.

# 2. Camera Module Specification

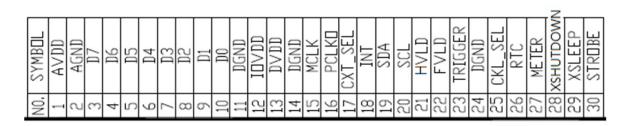

#### 2.1. Pin map and description of camera module

| 1 AVDD Power Analog power. (2.8V) 2 AGND Ground Analog ground. 3 D7 Out Data 7 output. 4 D6 Out Data 6 output. 5 D5 Out Data 5 output. 6 D4 Out Data 3 output. 7 D3 Out Data 3 output. 8 D2 Out Data 2 output. 9 D1 Out Data 1 output. 10 D0 Out Data 0 output. 11 DGND Ground Digital ground. 12 IOVDD Power IO power. (1.8V) 13 DVDD Power Core digital power. (1.2V) 14 DGND Ground Digital ground. 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 20 SCL In I2C serial clock. 21 HVLD Out Frame valid output. 22 FVLD Out Frame valid output. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin no. | Pin name  | Type      | Description                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|-----------|------------------------------------------------------------------------------------------------------|

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1       | AVDD      | Power     | Analog power. (2.8V)                                                                                 |

| 4         D6         Out         Data 6 output.           5         D5         Out         Data 5 output.           6         D4         Out         Data 4 output.           7         D3         Out         Data 3 output.           8         D2         Out         Data 2 output.           9         D1         Out         Data 1 output.           10         D0         Out         Data 0 output.           11         DGND         Ground         Digital ground.           12         IOVDD         Power         IO power. (1.8V)           13         DVDD         Power         Core digital power. (1.2V)           14         DGND         Ground         Digital ground.           15         MCLK         In         Master clock input.           16         PCLKO         Out         Pixel clock           17         CXT SEL         In         Context switching selection. (Internal pull low)           18         INT         Out         Interrupt output. (Active high)           19         SDA         In/Out         Serial Data I/O. (Open drain)           20         SCL         In         I2C serial clock.           21 <td>2</td> <td>AGND</td> <td>Ground</td> <td>Analog ground.</td> | 2       | AGND      | Ground    | Analog ground.                                                                                       |

| 5 D5 Out Data 5 output. 6 D4 Out Data 4 output. 7 D3 Out Data 3 output. 8 D2 Out Data 2 output. 9 D1 Out Data 1 output. 10 D0 Out Data 0 output. 11 DGND Ground Digital ground. 12 IOVDD Power IO power. (1.8V) 13 DVDD Power Core digital power. (1.2V) 14 DGND Ground Digital ground. 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock. 21 HVLD Out Frame valid output. 22 FVLD Out Frame valid output. 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3       | D7        | Out       | Data 7 output.                                                                                       |

| 6 D4 Out Data 4 output. 7 D3 Out Data 3 output. 8 D2 Out Data 2 output. 9 D1 Out Data 1 output. 10 D0 Out Data 0 output. 11 DGND Ground Digital ground. 12 IOVDD Power IO power. (1.8V) 13 DVDD Power Core digital power. (1.2V) 14 DGND Ground Digital ground. 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock. 21 HVLD Out Frame valid output. 22 FVLD Out Frame valid output. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | D6        | Out       | Data 6 output.                                                                                       |

| 7 D3 Out Data 3 output.  8 D2 Out Data 2 output.  9 D1 Out Data 1 output.  10 D0 Out Data 0 output.  11 DGND Ground Digital ground.  12 IOVDD Power IO power. (1.8V)  13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  Clock getters coloct. (Internal pull low / Active high)  Clock getters coloct. (Internal pull low / Active high)  Clock getters coloct. (Internal pull low / Active high)  Clock getters coloct. (Internal pull low / Active high)                                                                                                                                                                                                                                                                                                                                                       | 5       | D5        | Out       | Data 5 output.                                                                                       |

| 8 D2 Out Data 2 output.  9 D1 Out Data 1 output.  10 D0 Out Data 0 output.  11 DGND Ground Digital ground.  12 IOVDD Power IO power. (1.8V)  13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT_SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  Clock course coloct. (Internal pull low / Active high)  Clock course coloct. (Internal pull low / Active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | D4        | Out       | Data 4 output.                                                                                       |

| 9 D1 Out Data 1 output.  10 D0 Out Data 0 output.  11 DGND Ground Digital ground.  12 IOVDD Power IO power. (1.8V)  13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  Clock course select (Internal pull low / Active high)  Clock course select (Internal pull low / Active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7       | D3        | Out       | Data 3 output.                                                                                       |

| 10 D0 Out Data 0 output.  11 DGND Ground Digital ground.  12 IOVDD Power IO power. (1.8V)  13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT_SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O: (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -       |           | Out       | Data 2 output.                                                                                       |

| 11 DGND Ground Digital ground.  12 IOVDD Power IO power. (1.8V)  13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9       | D1        | Out       | Data 1 output.                                                                                       |

| 12 IOVDD Power IO power. (1.8V) 13 DVDD Power Core digital power. (1.2V) 14 DGND Ground Digital ground. 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT_SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock 21 HVLD Out Line valid output. 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10      | D0        | Out       | Data 0 output.                                                                                       |

| 13 DVDD Power Core digital power. (1.2V)  14 DGND Ground Digital ground.  15 MCLK In Master clock input.  16 PCLKO Out Pixel clock  17 CXT_SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11      | DGND      | Ground    | Digital ground.                                                                                      |

| 14 DGND Ground Digital ground. 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT_SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock. 21 HVLD Out Line valid output. 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12      | IOVDD     | Power     | IO power. (1.8V)                                                                                     |

| 15 MCLK In Master clock input. 16 PCLKO Out Pixel clock 17 CXT_SEL In Context switching selection. (Internal pull low) 18 INT Out Interrupt output. (Active high) 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock. 21 HVLD Out Line valid output. 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13      | DVDD      | Power     | Core digital power. (1.2V)                                                                           |

| 16 PCLKO Out Pixel clock  17 CXT_SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14      | DGND      | Ground    |                                                                                                      |

| 17 CXT_SEL In Context switching selection. (Internal pull low)  18 INT Out Interrupt output. (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15      | MCLK      | In        | Master clock input.                                                                                  |

| 18 INT Out Interrupt output, (Active high)  19 SDA In/Out Serial Data I/O. (Open drain)  20 SCL In I2C serial clock.  21 HVLD Out Line valid output.  22 FVLD Out Frame valid output.  23 TRIGGER In Frame trigger input. (Internal pull low / Active high)  24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16      | PCLKO     | Out       | Pixel clock                                                                                          |

| 19 SDA In/Out Serial Data I/O. (Open drain) 20 SCL In I2C serial clock. 21 HVLD Out Line valid output. 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17      | CXT_SEL   |           | Context switching selection. (Internal pull low)                                                     |

| 20 SCL In I2C serial clock. 21 HVLD Out Line valid output. 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18      | INT       | Out       | Interrupt output. (Active high)                                                                      |

| 21 HVLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19      | SDA       | In/Out    | Serial Data I/O. (Open drain)                                                                        |

| 22 FVLD Out Frame valid output. 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20      | SCL       | In        | I2C serial clock.                                                                                    |

| 23 TRIGGER In Frame trigger input. (Internal pull low / Active high) 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |           | Out       |                                                                                                      |

| 24 DGND Ground Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22      | FVLD      | Out       | Frame valid output.                                                                                  |

| Clock cottroe select Untermal will law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | TRIGGER   | In        | Frame trigger input. (Internal pull low / Active high)                                               |

| Clock source select (Internal pull low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24      | DGND      | Ground    | Digital ground.                                                                                      |

| L: Oscillator, H: MCLK, connect to ground for oscillator mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25      | CLK_SEL   | ln        |                                                                                                      |

| 26 RTC In Real time clock source input. (Must not be left floating, conn to DGND without RTC clock input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26      | RTC       | <u>In</u> | Real time clock source input. (Must not be left floating, connected to DGND without RTC clock input) |

| 27 METER In Exposure meter enable pin. (Internal pull low / Active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27      | METER     | In In     | Exposure meter enable pin. (Internal pull low / Active high)                                         |

| 28 XSHUTDOWN In Reset and power down control pin. (Active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28      | XSHUTDOWN | 10/ In    | Reset and power down control pin. (Active low)                                                       |

| 29 XSLEEP In Low power sleep mode. (Active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29      | XSLEEP    | ln ,      | Low power sleep mode. (Active low)                                                                   |

| 30 STROBE Out Strobe output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30      | STROBE    | Out       |                                                                                                      |

Note: (1) HM0360 sensor default slave address: 0x24.

Table 2.1: Pin map and description of camera module

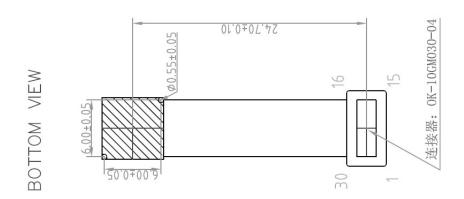

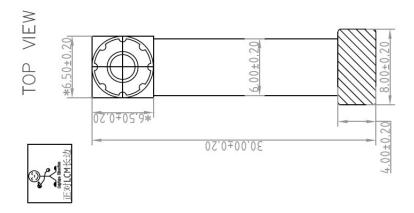

#### 2.2. Mechanical drawing of camera module

Figure 2.1: Mechanical drawing of camera module

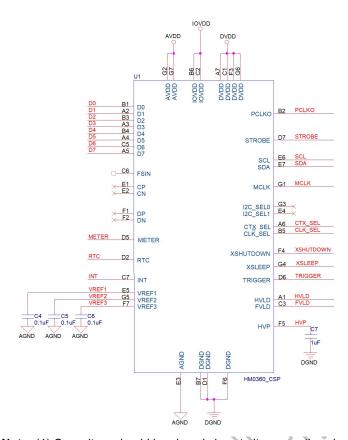

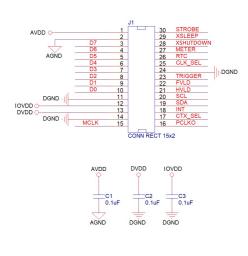

#### 2.3. Application schematic of camera module

#### 2.3.1. Reference circuit

Note: (1) Capacitors should be placed close to its respective pin. All power supplies must be adequately decoupled.

(2) CCI pull-up resistors should have a value based on the CCI specification (typically 4k7 ohm).

(3) RTC pin must not be left floating, connected to DGND without RTC clock input.

(4) MCLK connect to DGND when using internal oscillator.

Figure 2.2: Reference circuit of camera module (CSP)

#### 2.3.2. Layout consideration

- A. In order to reduce power noise to the camera module, it is suggested that a 0.1μF capacitor and a high value decoupling capacitor (10μF or above) be placed across every power line (AVDD & DVDD & IOVDD) and corresponding ground pin. Try to place these capacitors close to the module connector. The power noise will contribute to image noise and it is necessary to reduce them as much as possible.

- B. In order to reduce interference and noise caused by the high frequency clocks. It is suggested that the master and pixel clocks be surrounded with ground shielding pins.

- C. In order to avoid the ground loop, it is recommended that the sensor analog ground be connected to sensor digital ground through a point or 0ohm resistor. Then the sensor digital ground should be connected to system ground through a point or a 0 ohm resistor.

- D. In order to reduce EM radiation, it is recommended that ground pins be assigned to the edge of the module connector.

# 3. Optical Lens Specification

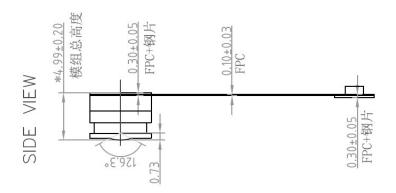

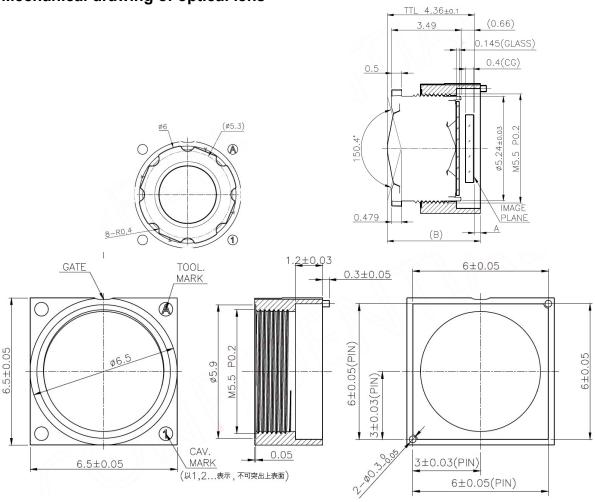

#### 3.1. Mechanical drawing of optical lens

Figure 3.1: Mechanical drawing of optical lens

### 3.2. Specification of optical lens

| Parameter                     | ·          | Spec.                 |

|-------------------------------|------------|-----------------------|

| Construction                  |            | 4P                    |

| EFL                           |            | 1.27 mm               |

| BFL                           |            | 0.97 mm               |

| Image circle                  |            | ψ3.3 mm               |

| F/No                          |            | 2.4 ± 5%              |

| TV distortion                 |            | < 40%                 |

|                               | Horizontal | 98.1°                 |

| Field of view                 | Vertical   | 73.2°                 |

| Diagonal                      |            | 129.4°                |

| Relative illumination         |            | >65.4% at y=1.0 field |

| Chief ray angle               |            | < 33.1°               |

| Barrel size                   |            | M5.5 x P0.3           |

| Holder size                   | ·          | 6.5mm x 6.5mm         |

| Total track (Barrel to image) | ·          | Y=4.36mm              |

Table 3.1: Specification of optical lens

# 4. Image Quality Specification

| No. | Test item       | Diagram                                                  | Test condition                                                                                         | Standard                                                                                                                                                                                    |

|-----|-----------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MTF             |                                                          | Test chart: 1/8 N<br>Pattern chart<br>Distance: 35cm<br>Full image size                                | Center (0% field): >=0.8<br>Corner (65% field): >=0.6                                                                                                                                       |

| 2   | Shading         | AOI: 32x32 pixel Shading ratio= Ycorner (Min.) / Ycenter | Without ISP (raw image) Distance: 1cm Light condition: 1500 ± 300 lux, 5100 ± 300K                     | >=30%                                                                                                                                                                                       |

| 3   | Blemish         | A: 324 pixel B: 324 pixel Block size: 9x9 pixel          | Without ISP (raw image) Distance: 1cm Light condition: 1500 ± 300 lux, 5100 ± 300K                     | The luminance difference between each block and the adjacent block should be less than 3%                                                                                                   |

|     | Defect<br>pixel | Dark pixel defect                                        | The sensor is illuminated to midlevel: ~ 400 LSBs to 700 LSBs.                                         | Within a color plane, each pixel is compared to the mean of the neighboring 40 x 40 pixels.  If the pixel value is 40 percent or more below the mean, it is considered a dark pixel defect. |

| 4   |                 | Bright pixel defect                                      | The sensor is illuminated to midlevel: ~ 400 LSBs to 700 LSBs. (Analog gain = 1; exposure time = 10ms) | Within a color plane, each pixel is compared to the mean of the neighboring 40 x 40 pixels.  If the pixel value is 40 percent or more above the mean, it is considered a dark pixel defect. |

|     |                 | Bright cluster<br>Defect no.: 10                         | By "Bright Pixel Defect"<br>Result                                                                     | The defects within each color plane are examined. If any two adjacent pixels that are considered bright pixel defects are detected, they are then defined as a bright cluster.              |