www.ti.com

# Digital Input Class-D Speaker Amplifier with Embedded miniDSP and mono headphone amplifier

Check for Samples: TAS2521

#### 1 INTRODUCTION

#### 1.1 Features

- Digital Input Mono Speaker Amp

- Instruction-Programmable Embedded miniDSP

- Supports 8-kHz to 192-kHz Sample Rates

- Mono Class-D BTL Speaker Driver (2 W Into 4  $\Omega$  or 1.7 W Into 8  $\Omega$ )

- Mono Headphone Driver

- Two Single-Ended Inputs With Output Mixing and Level Control

- Embedded Power-on-Reset

- Integrated LDO

- Built-in Digital Audio Processing Blocks With User-Programmable Biquad Filters

- Integrated PLL Used for Programmable Digital Audio Processor

- I<sup>2</sup>S, Left-Justified, Right-Justified, DSP, and TDM Audio Interfaces

- I<sup>2</sup>C and SPI control with auto-increment

- Full Power-Down Control

- Power Supplies:

Analog: 1.5 V-1.95 V

Digital Core: 1.65 V-1.95 V

Digital I/O: 1.1 V-3.6 V

Class-D: 2.7 V-5.5 V (SPKVDD ≥ AVDD)

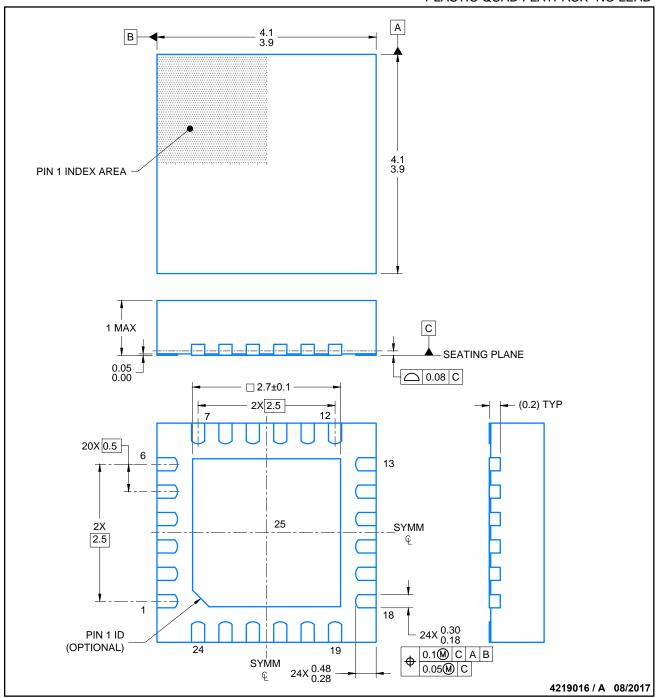

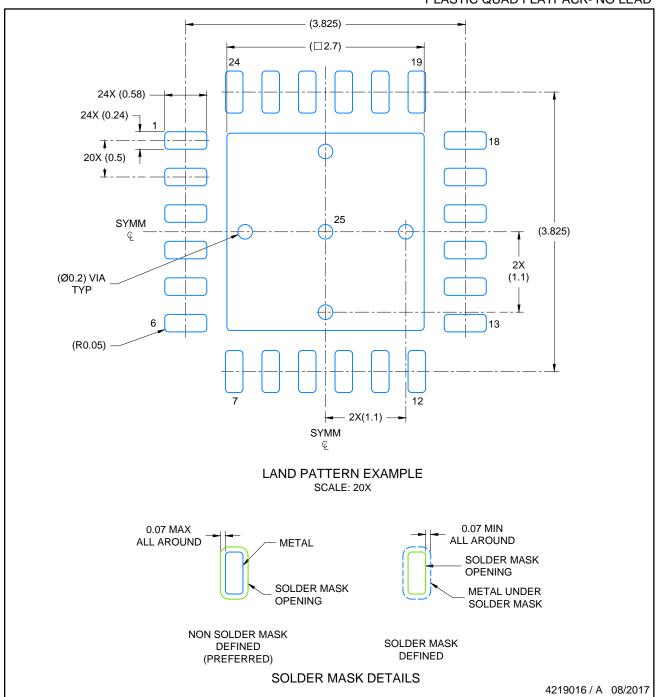

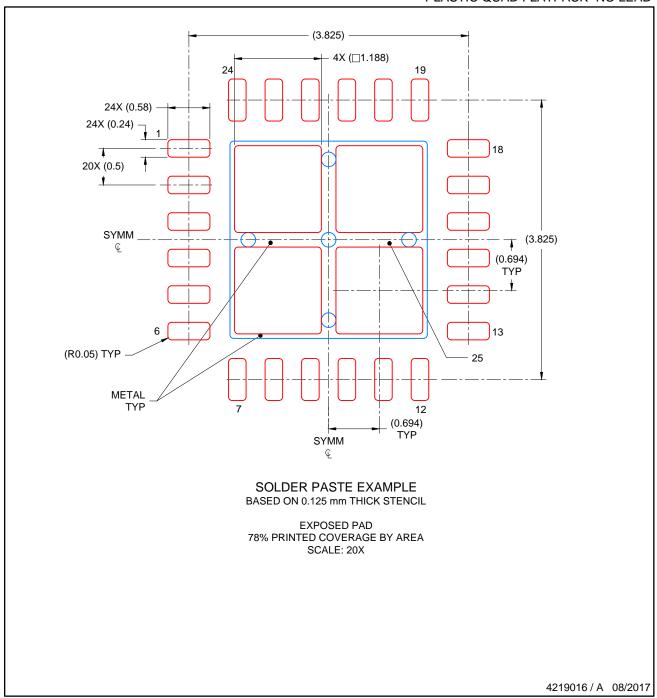

24-Pin QFN Package (4mm × 4mm)

# 1.2 Applications

- Portable Audio Devices

- White goods

- Portable Navigation Devices

#### 1.3 Description

The TAS2521 is a low power digital input speaker amp with support for 24-bit digital I2S data mono playback.

In addition to driving a speaker amp upto 4- $\Omega$ , the device also features a mono headphone driver and a fully programmable miniDSP for signal processing. The digital audio data format is programmable to work with popular audio standard protocols (12S, left/right-justified) in master, slave, DSP and TDM modes. The fully programmable miniDSP can support several functions such equalization for audio, multiband DRC, tone generation and several other user defined functions. An on-chip PLL provides the highspeed clock needed by the digital signal-processing block. The volume level can be controlled by register control. The audio functions are controlled using the I<sup>2</sup>C<sup>™</sup> serial bus or SPI bus. The device includes an on-board LDO that runs off the speaker power supply to handle all internal device analog and digital power needs. The included POR as power-on-resetcircuit reliably resets the device into its default state so no external reset is required at normal usage; however, the device does have a reset pin for more complex system initialization needs. The device also includes two analog inputs for mixing and muxing in both speaker and headphone analog paths.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

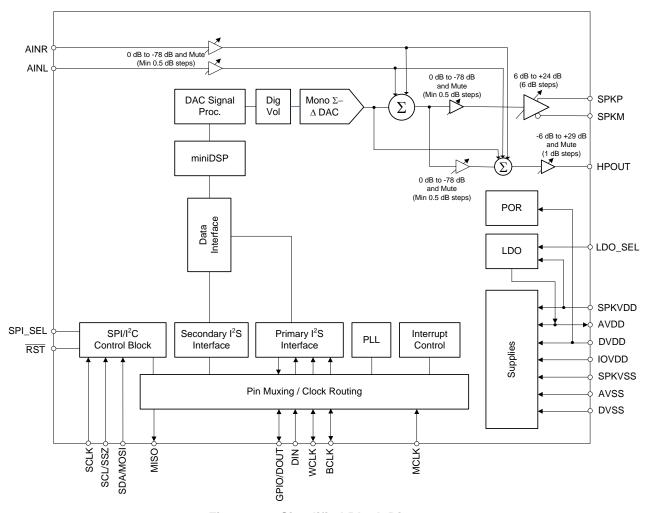

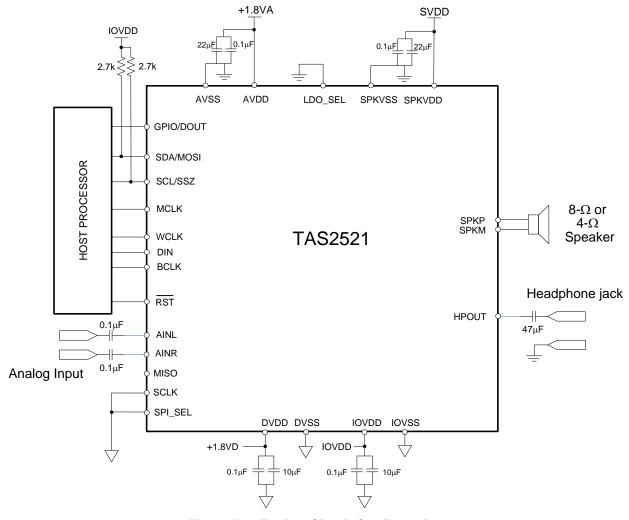

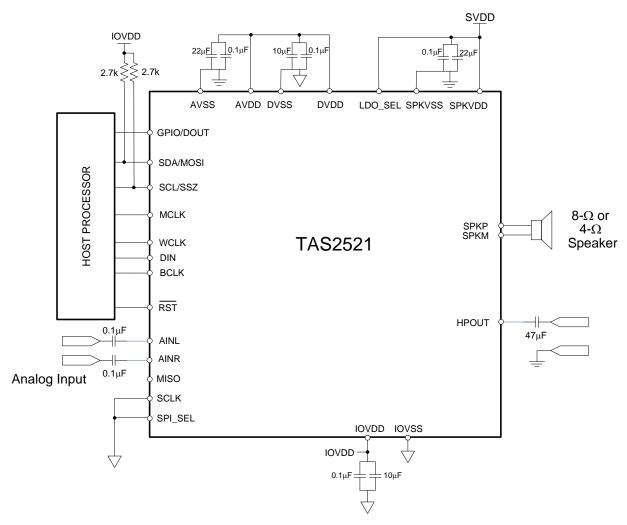

Figure 1-1. Simplified Block Diagram

#### **NOTE**

This data manual is designed using PDF document-viewing features that allow quick access to information. For example, performing a global search on "page 0 / register 27" produces all references to this page and register in a list. This makes is easy to traverse the list and find all information related to a page and register. Note that the search string must be of the indicated format. Also, this document includes document hyperlinks to allow the user to quickly find a document reference. To come back to the original page, click the green left arrow near the PDF page number at the bottom of the file. The hot-key for this function is alt-left arrow on the keyboard. Another way to find information quickly is to use the PDF bookmarks.

# 2 PACKAGE AND SIGNAL DESCRIPTIONS

# 2.1 Package/Ordering Information

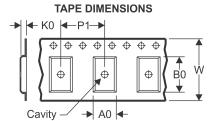

| PRODUCT | PACKAGE | PACKAGE<br>DESIGNATOR | OPERATING<br>TEMPERATURE<br>RANGE | ORDERING NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|---------|-----------------------|-----------------------------------|-----------------|------------------------------|

| TAS2521 | OEN 24  | DOE                   | 40°C to 05°C                      | TAS2521IRGET    | Tape and reel, 250           |

| 1A52521 | QFN-24  | RGE                   | –40°C to 85°C                     | TAS2521IRGER    | Tape and reel, 3000          |

#### 2.2 Device Information

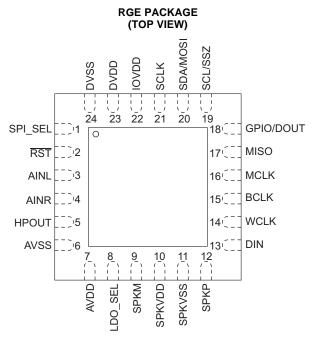

**Table 2-1. RGE PIN FUNCTIONS**

| PIN     |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                           |

|---------|-----|--------------------|---------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0(-/             | DESCRIPTION                                                                           |

| SPI_SEL | 1   | 1                  | Selects between SPI and I2C digital interface modes; (1 = SPI mode) (0 = I2C mode)    |

| RST     | 2   | 1                  | Reset for logic, state machines, and digital filters; asserted LOW.                   |

| AINL    | 3   | 1                  | Analog single-ended line left input                                                   |

| AINR    | 4   | 1                  | Analog single-ended line right input                                                  |

| HPOUT   | 5   | 0                  | Headphone and Lineout Driver Output                                                   |

| AVSS    | 6   | GND                | Analog Ground, 0V                                                                     |

| AVDD    | 7   | PWR                | Analog Core Supply Voltage, 1.5V - 1.95V, tied internally to the LDO output           |

| LDO_SEL | 8   | 1                  | Select Pin for LDO; ties to either SPKVDD or SPKVSS                                   |

| SPKM    | 9   | 0                  | Class-D speaker driver inverting output                                               |

| SPKVDD  | 10  | PWR                | Class-D speaker driver power supply                                                   |

| SPKVSS  | 11  | PWR                | Class-D speaker driver power supply ground supply                                     |

| SPKP    | 12  | 0                  | Class-D speaker driver non-inverting output                                           |

| DIN     | 13  | 1                  | Audio Serial Data Bus Input Data                                                      |

| WCLK    | 14  | I/O                | Audio Serial Data Bus Word Clock                                                      |

| BCLK    | 15  | I/O                | Audio Serial Data Bus Bit Clock                                                       |

| MCLK    | 16  | I                  | Master CLK Input / Reference CLK for CLK Multiplier - PLL (On startup PLLCLK = CLKIN) |

(1) I = Input, O = Output, GND = Ground, PWR = Power, Z = High Impedance

#### Table 2-1. RGE PIN FUNCTIONS (continued)

| PIN       |     | VO <sup>(1)</sup> | DECCRIPTION                                                                        |  |  |  |

|-----------|-----|-------------------|------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO. | 1/0               | DESCRIPTION                                                                        |  |  |  |

| MISO      | 17  | 0                 | SPI Serial Data Output                                                             |  |  |  |

| GPIO/DOUT | 18  | I/O/Z             | GPIO / Audio Serial Bus Output                                                     |  |  |  |

| SCL/SSZ   | 19  | ı                 | Either I2C Input Serial Clock or SPI Chip Select Signal depending on SPI_SEL state |  |  |  |

| SDA/MOSI  | 20  | ı                 | Either I2C Serial Data Input or SPI Serial Data Input depending on SPI_SEL state.  |  |  |  |

| SCLK      | 21  | ı                 | Serial clock for SPI interface                                                     |  |  |  |

| IOVDD     | 22  | PWR               | I/O Power Supply, 1.1V - 3.6V                                                      |  |  |  |

| DVDD      | 23  | PWR               | Digital Power Supply, 1.65V - 1.95V                                                |  |  |  |

| DVSS      | 24  | GND               | Digital Ground, 0V                                                                 |  |  |  |

#### 3 ELECTRICAL SPECIFICATIONS

# 3.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                        |                                                       |             | VALUE                           | UNIT |

|----------------------------------------|-------------------------------------------------------|-------------|---------------------------------|------|

|                                        |                                                       | MIN         | UNIT                            |      |

| AVDD to AVSS                           |                                                       | -0.3        | 2.2                             | V    |

| DVDD to DVSS                           |                                                       | -0.3        | 2.2                             | V    |

| SPKVDD to SPKVSS                       |                                                       | -0.3        | 6                               | V    |

| IOVDD to IOVSS                         |                                                       | -0.3        | 3.9                             | V    |

| Digital input voltage                  |                                                       | IOVSS - 0.3 | IOVDD + 0.3                     | V    |

| Analog input voltage                   |                                                       | AVSS - 0.3  | AVDD + 0.3                      | V    |

| Operating temperature ran              | ge                                                    | -40         | 85                              | °C   |

| Storage temperature range              |                                                       | -55         | 150                             | °C   |

| Junction temperature (T <sub>J</sub> N | Лах)                                                  |             | 105                             | °C   |

| QFN                                    | Power dissipation(with thermal pad soldered to board) |             | $(T_J Max - T_A) / \theta_{JA}$ | W    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 3.2 THERMAL INFORMATION

|                  | THERMAL METRIC <sup>(1)</sup>                | TAS2521       | LIMITO |

|------------------|----------------------------------------------|---------------|--------|

|                  | THERMAL METRIC                               | RGE (24 PINS) | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 32.2          |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 30.0          |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 9.2           | 0C/\/  |

| ΨЈΤ              | Junction-to-top characterization parameter   | 0.3           | °C/W   |

| ΨЈВ              | Junction-to-board characterization parameter | 9.2           |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.2           |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953

#### 3.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                                         |                                               | MIN  | NOM | MAX  | UNIT      |

|-----------------------|---------------------------------------------------------|-----------------------------------------------|------|-----|------|-----------|

| AVDD <sup>(1)</sup>   | Dower cumply valtage range                              | Referenced to AVSS <sup>(2)</sup>             | 1.5  | 1.8 | 1.95 |           |

| DVDD                  | Power-supply voltage range                              | Referenced to DVSS(2)                         | 1.65 | 1.8 | 1.95 | V         |

| SPKVDD <sup>(1)</sup> |                                                         | Referenced to SPKVSS <sup>(2)</sup>           | 2.7  |     | 5.5  | V         |

| IOVDD                 |                                                         | Referenced to IOVSS <sup>(2)</sup>            | 1.1  | 1.8 | 3.6  |           |

|                       | Speaker impedance                                       | Load applied across class-D output pins (BTL) | 4    |     |      | Ω         |

|                       | Headphone impedance                                     | AC-coupled to R <sub>L</sub>                  | 16   |     |      | Ω         |

| VI                    | Analog audio full-scale input voltage                   | AVDD = 1.8 V, single-ended                    |      | 0.5 |      | $V_{RMS}$ |

|                       | Line output load impedance (in half drive ability mode) | AC-coupled to R <sub>L</sub>                  |      | 10  |      | kΩ        |

| MCLK <sup>(3)</sup>   | Master clock frequency                                  | IOVDD = DVDD = 1.8V                           |      |     | 50   | MHz       |

| SCL                   | SCL clock frequency                                     |                                               |      |     | 400  | kHz       |

| T <sub>A</sub>        | Operating free-air temperature                          |                                               | -40  |     | 85   | °C        |

<sup>(1)</sup> To minimize battery-current leakage, the SPKVDD voltage level should not be below the AVDD voltage level.

#### 3.4 Electrical Characteristics

At 25°C, AVDD = 1.8 V, IOVDD = 1.8 V, SPKVDD = 3.6 V, DVDD = 1.8 V,  $f_S$  (audio) = 48 kHz, CODEC\_CLKIN = 256  $\times$   $f_S$ , PLL = Off

|         | PARAMETER                         | TEST CONDITIONS                                                                                                                                                                       | MIN TYP | MAX | UNIT |

|---------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| INTERNA | AL OSCILLATOR—RC_CLK              |                                                                                                                                                                                       |         |     |      |

|         | Oscillator frequency              |                                                                                                                                                                                       | 8.48    |     | MHz  |

| Audio D | AC – Stereo Single-Ended Headph   | one Output                                                                                                                                                                            |         | •   |      |

|         | Device Setup                      | Load = 16Ω (single-ended), Input & Output CM = 0.9V, DOSR = 128, Device Setup MCLK = 256* fs, Channel Gain = 0dB word length = 16 bits; Processing Block = PRB_P1 Power Tune = PTM_P3 |         |     |      |

|         | Full-scale output voltage (0 dB)  |                                                                                                                                                                                       | 0.5     |     | Vrms |

| ICN     | Idle channel noise                | Measured as idle-channel noise, A-weighted (1) (2)                                                                                                                                    | 20.7    |     | μVms |

| THD+N   | Total harmonic distortion + noise | 0-dBFS input, 1-kHz input signal                                                                                                                                                      | -78.2   |     | dB   |

|         | Mute attenuation                  | Mute                                                                                                                                                                                  | 103.7   |     | dB   |

| PSRR    | Power-supply rejection ratio (3)  | Ripple on AVDD (1.8 V) = 200 mV <sub>PP</sub> at 1 kHz                                                                                                                                | 47.2    |     | dB   |

| DR      | Dynamic range, A-weighted (1) (2) | -60dB 1kHz input full-scale signal                                                                                                                                                    | 88.1    |     |      |

|         | Gain error                        | 0dB, 1kHz input full scale signal                                                                                                                                                     | ±0.3    |     | dB   |

| 1       | Manifestore automate annual       | $R_L = 32 \Omega$ , THD+N $\leq -40 \text{ dB}$                                                                                                                                       | 11      |     | \^/  |

| Po      | Maximum output power              | R <sub>L</sub> = 16 Ω, THD+N ≤ −40 dB                                                                                                                                                 | 18      |     | mW   |

<sup>(1)</sup> Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the inputs short-circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

<sup>(2)</sup> All grounds on board are tied together, so they should not differ in voltage by more than 0.2 V maximum for any combination of ground signals. By use of a wide trace or ground plane, ensure a low-impedance connection between AVSS and DVSS.

<sup>(3)</sup> The maximum input frequency should be 50 MHz for any digital pin used as a general-purpose clock.

<sup>(2)</sup> All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may result in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

<sup>(3)</sup> DAC to headphone-out PSRR measurement is calculated as PSRR = 20 X  $\log(\Delta V_{HP} / \Delta V_{AVDD})$ .

#### **Electrical Characteristics (continued)**

At 25°C, AVDD = 1.8V, IOVDD = 1.8 V, SPKVDD = 3.6 V, DVDD = 1.8 V,  $f_S$  (audio) = 48 kHz, CODEC\_CLKIN = 256  $\times$   $f_S$ , PLL = Off

|                | PARAMETER                               | TEST CONDITIONS                                                                                                                                                                        | MIN TYP | MAX | UNIT |

|----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| Audio DA       | AC – Stereo Single-Ended Headph         | one Output                                                                                                                                                                             |         |     |      |

|                | Device Setup                            | Load = 16Ω (single-ended), Input & Output CM = 0.75V, DOSR = 128, Device Setup MCLK = 256* fs, Channel Gain = 0dB word length = 16 bits; Processing Block = PRB_P1 Power Tune = PTM_P3 |         |     |      |

|                | Full-scale output voltage (0 dB)        |                                                                                                                                                                                        | 0.375   |     | Vrms |

| ICN            | Idle channel noise                      | Measured as idle-channel noise, A-weighted (1) (2)                                                                                                                                     | 18.1    |     | μVms |

| THD+N          | Total harmonic distortion + noise       | 0-dBFS input, 1-kHz input signal                                                                                                                                                       | -78.2   |     | dB   |

|                | Mute attenuation                        | Mute                                                                                                                                                                                   | 105.5   |     | dB   |

| PSRR           | Power-supply rejection ratio (3)        | Ripple on AVDD (1.8 V) = 200 mV <sub>PP</sub> at 1 kHz                                                                                                                                 | 48.4    |     | dB   |

| DR             | Dynamic range, A-weighted (1) (2)       | -60dB 1kHz input full-scale signal                                                                                                                                                     | 86.8    |     |      |

|                | Gain error                              | 0dB, 1kHz input full scale signal                                                                                                                                                      | ±0.3    |     | dB   |

| _              | Nanciana autoritaria                    | $R_L = 32 \Omega$ , THD+N $\leq -40 \text{ dB}$                                                                                                                                        | 8       |     | \^/  |

| P <sub>O</sub> | Maximum output power                    | R <sub>L</sub> = 16 Ω, THD+N ≤ -40 dB                                                                                                                                                  | 16      |     | mW   |

| DAC DIG        | ITAL INTERPOLATION FILTER CH            | IARACTERISTICS                                                                                                                                                                         |         |     |      |

| See for D      | AC interpolation filter characteristics |                                                                                                                                                                                        |         |     |      |

| DAC OU         | TPUT TO CLASS-D SPEAKER OUT             | TPUT; LOAD = 4 Ω (DIFFERENTIAL)                                                                                                                                                        |         |     |      |

| ICN            | Idle channel noise                      | BTL measurement, class-D gain = 6 dB, Measured as idle-channel noise, A-weighted <sup>(1)</sup> (2)                                                                                    | 37      |     | μVms |

|                | Output voltage                          | BTL measurement, class-D gain = 6 dB, -3dBFS input                                                                                                                                     | 1.4     |     | Vrms |

| THD+N          | Total harmonic distortion + noise       | BTL measurement, DAC input = -6 dBFS, class-D gain = 6 dB                                                                                                                              | -73.9   |     | dB   |

| PSRR           | Power-supply rejection ratio            | BTL measurement, ripple on SPKVDD = 200 mV <sub>PP</sub> at 1 kHz                                                                                                                      | 55      |     | dB   |

|                | Mute attenuation                        | Mute                                                                                                                                                                                   | 103     |     | dB   |

|                |                                         | SPKVDD = 3.6 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 10%                                                                                                            | 1.1     |     |      |

|                |                                         | SPKVDD = 4.2 V, BTL measurement, CM = 0.9 V, class-D gain = 18 dB, THD = 10%                                                                                                           | 1.4     |     |      |

| P <sub>O</sub> | Maximum output power                    | SPKVDD = 3.6 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 1%                                                                                                             | 0.8     |     | W    |

|                |                                         | SPKVDD = 4.2 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 1%                                                                                                             | 1.1     |     |      |

|                |                                         | SPKVDD = 5.5 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB                                                                                                                       |         | 2   |      |

<sup>(1)</sup> Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the inputs short-circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

(3) DAC to headphone-out PSRR measurement is calculated as PSRR = 20 X log(ΔV<sub>HP</sub> / ΔV<sub>AVDD</sub>).

<sup>(2)</sup> All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may result in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

#### **Electrical Characteristics (continued)**

At 25°C, AVDD = 1.8 V, IOVDD = 1.8 V, SPKVDD = 3.6 V, DVDD = 1.8 V,  $f_S$  (audio) = 48 kHz, CODEC\_CLKIN = 256  $\times$   $f_S$ , PLL = Off

|                | PARAMETER                         | TEST CONDITIONS                                                                                                                                 | MIN TYP | MAX | UNIT |

|----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| DAC OU         | TPUT TO CLASS-D SPEAKER OUT       | TPUT; LOAD = 8 Ω (DIFFERENTIAL)                                                                                                                 |         |     |      |

| ICN            | Idle channel noise                | BTL measurement, class-D gain = 6 dB, Measured as idle-channel noise, A-weighted <sup>(1)</sup> (2)                                             | 35.2    |     | μVms |

|                | Output voltage                    | BTL measurement, class-D gain = 6 dB, -3dBFS input                                                                                              | 1.4     |     | Vrms |

| THD+N          | Total harmonic distortion + noise | BTL measurement, DAC input = -6 dBFS, class-D gain = 6 dB                                                                                       | -73.6   |     | dB   |

|                |                                   | SPKVDD = 3.6 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 10%                                                                     | 0.7     |     |      |

|                |                                   | SPKVDD = 4.2 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 10%                                                                     | 1       |     |      |

| Б              | Maximum output power              | SPKVDD = 5.5 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 10%                                                                     | 1.7     |     | W    |

| P <sub>O</sub> |                                   | SPKVDD = 3.6 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 1%                                                                      | 0.5     |     | VV   |

|                |                                   | SPKVDD = 4.2 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 1%                                                                      | 0.8     |     |      |

|                |                                   | SPKVDD = 5.5 V, BTL measurement, CM = 0.9V, class-D gain = 18 dB, THD = 1%                                                                      | 1.3     |     |      |

| ANALOG         | BYPASS TO HEADPHONE AMPL          | IFIER                                                                                                                                           |         |     |      |

|                | Device Setup                      | AC-COUPLED LOAD = 16 $\Omega$ (SINGLE-ENDED),<br>DRIVER GAIN = 0 dB, Input and output common-<br>mode = 0.9 V, input signal frequency fi = 1kHz |         |     |      |

|                | Voltage Gain                      | Input common-mode = 0.9 V                                                                                                                       | 1       |     | V/V  |

|                | Gain Error                        | -1dBFS (446mVrms), 1-kHz input signal                                                                                                           | ±0.8    |     | dB   |

| ICN            | Idle channel noise                | Idle channel, IN1L and IN1R ac-shorted to ground, Measured as idle-channel noise, A-weighted (1) (2)                                            | 10.2    |     | μVms |

| THD+N          | Total harmonic distortion + noise | -1 dBFS (446mVrms), 1-kHz input signal                                                                                                          | -80.4   |     | dB   |

Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the inputs short-circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may

<sup>(2)</sup> All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may result in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

# **Electrical Characteristics (continued)**

At 25°C, AVDD = 1.8 V, IOVDD = 1.8 V, SPKVDD = 3.6 V, DVDD = 1.8 V,  $f_S$  (audio) = 48 kHz, CODEC\_CLKIN = 256  $\times$   $f_S$ , PLL = Off

|                 | PARAMETER                         | TEST CONDITIONS                                                                                                 | MIN -          | TYP N    | IAX         | UNIT |

|-----------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|----------|-------------|------|

| ANALOG          | BYPASS TO CLASS-D SPEAKER         | AMPLIFIER                                                                                                       | •              |          | 1           |      |

|                 | Device Setup                      | BTL measurement, DRIVER GAIN = 6 dB, LOAD = 4 $\Omega$ (DIFFERENTIAL), 50 pF, input signal frequency fi = 1 KHz |                |          |             |      |

|                 | Voltage Gain                      | Input common-mode = 0.9 V                                                                                       |                | 4        |             | V/V  |

|                 | Gain Error                        | -1dBFS (446mVrms), 1-kHz input signal                                                                           | =              | ±0.7     |             | dB   |

| ICN             | Idle channel noise                | Idle channel, IN1L and IN1R ac-shorted to ground, Measured as idle-channel noise, A-weighted (1) (2)            | ;              | 32.6     |             | μVms |

| THD+N           | Total harmonic distortion + noise | -1 dBFS (446mVrms), 1-kHz input signal                                                                          | -7             | 73.7     |             | dB   |

| LOW DR          | OPOUT REGULATOR (AVDD)            |                                                                                                                 |                |          |             |      |

|                 | AVDD Output Voltage 1.8V          | SPKVDD = 2.7V, Page 1, Reg 2, D5-D4 = 00, $I_0$ = 50mA                                                          |                | 1.79     |             | V    |

|                 |                                   | SPKVDD = 3.6V, Page 1, Reg 2, D5-D4 = 00, $I_0$ = 50mA                                                          |                | 1.79     |             | V    |

|                 |                                   | SPKVDD = 5.5V, Page 1, Reg 2, D5-D4 = 00, I <sub>O</sub> = 50mA                                                 |                | 1.79     |             | V    |

|                 | Output Voltage Accuracy           | SPVDD = 2.7V                                                                                                    |                | ±2       |             | %    |

|                 | Load Regulation                   | SPVDD = 2.7V, 0A to 50mA                                                                                        |                | 7        |             | mV   |

|                 | Line Regulation                   | Input Supply Range 2.7V to 5.5V                                                                                 |                | 0.6      |             | mV   |

|                 | Decoupling Capacitor              |                                                                                                                 | 1.0            |          |             | uF   |

|                 | Bias Current                      |                                                                                                                 |                | 55       |             | uA   |

|                 | Noise @0A Load                    | A-weighted, 20Hz to 20kHz bandwidth                                                                             |                | 166      |             | uV   |

|                 | Noise @50mA Load                  | A-weighted, 20Hz to 20kHz bandwidth                                                                             |                | 174      |             | uV   |

| SHUTDO          | WN POWER CONSUMPTION              |                                                                                                                 |                |          |             |      |

|                 | Device Setup                      | Power down POR, /RST held low, AVDD = 1.8V, IOVDD = 1.8 V, SPKVDD = 4.2 V, DVDD = 1.8 V                         |                |          |             |      |

|                 | I(AVDD)                           |                                                                                                                 |                | 1.32     |             | μA   |

|                 | I(DVDD)                           |                                                                                                                 | (              | 0.04     |             | μΑ   |

|                 | I(IOVDD)                          |                                                                                                                 |                | 0.68     |             | μΑ   |

|                 | I(SPKVDD)                         |                                                                                                                 |                | 2.24     |             | μΑ   |

| DIGITAL         | INPUT/OUTPUT                      |                                                                                                                 |                |          |             |      |

| Logic fan       | nily                              |                                                                                                                 | CN             | MOS      |             |      |

| V <sub>IH</sub> |                                   | I <sub>IH</sub> = 5 μA, IOVDD ≥ 1.6 V                                                                           | 0.7 ×<br>IOVDD |          |             | V    |

|                 |                                   | I <sub>IH</sub> = 5 μA, IOVDD < 1.6 V                                                                           | IOVDD          |          |             |      |

| V <sub>IL</sub> | Logic level                       | I <sub>IL</sub> = 5 μA, IOVDD ≥ 1.6 V                                                                           | -0.3           | 0<br>IOV | .3 ×<br>′DD | V    |

|                 |                                   | I <sub>IL</sub> = 5 μA, IOVDD < 1.6 V                                                                           |                |          | 0           |      |

| V <sub>OH</sub> |                                   | I <sub>OH</sub> = 2 TTL loads                                                                                   | 0.8 ×<br>IOVDD |          |             | V    |

| V <sub>OL</sub> |                                   | I <sub>OL</sub> = 2 TTL loads                                                                                   |                | (        | ).25        | V    |

|                 | Capacitive load                   |                                                                                                                 |                | 10       | Ī           | рF   |

<sup>(1)</sup> Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the inputs short-circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

<sup>(2)</sup> All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may result in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

# 3.5 Timing Characteristics

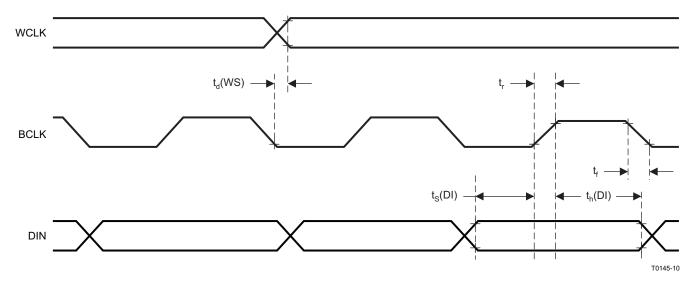

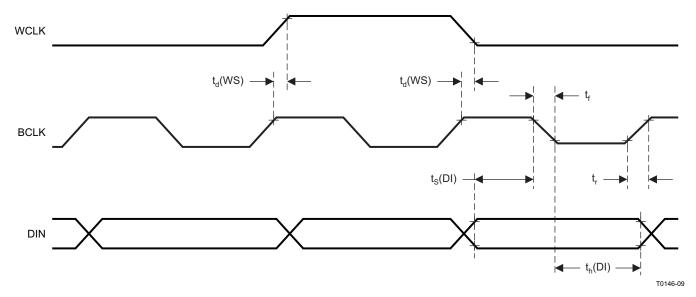

# 3.5.1 fS/LJF/RJF Timing in Master Mode

All specifications at 25°C, DVDD = 1.8 V

|                     | PARAMETER  | IOVDD = 1.8 V |     | IOVDD = 3.3 V |     | UNIT |

|---------------------|------------|---------------|-----|---------------|-----|------|

|                     |            | MIN           | MAX | MIN           | MAX |      |

| t <sub>d</sub> (WS) | WCLK delay |               | 45  |               | 45  | ns   |

| t <sub>s</sub> (DI) | DIN setup  | 8             |     | 6             |     | ns   |

| t <sub>h</sub> (DI) | DIN hold   | 8             |     | 6             |     | ns   |

| t <sub>r</sub>      | Rise time  |               | 25  |               | 10  | ns   |

| t <sub>f</sub>      | Fall time  |               | 25  |               | 10  | ns   |

Figure 3-1. I<sup>2</sup>S/LJF/RJF Timing in Master Mode

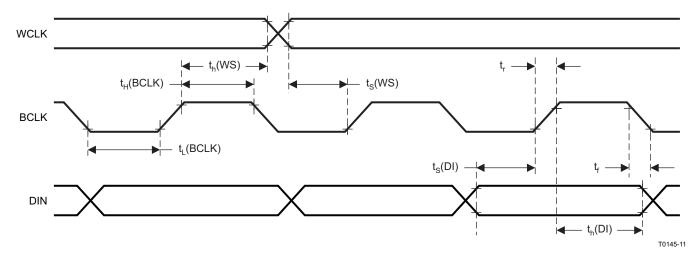

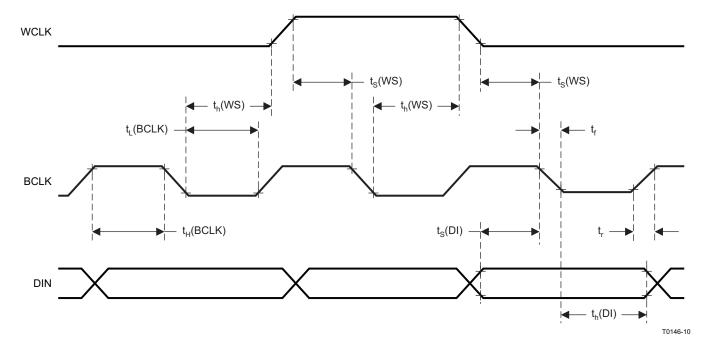

# 3.5.2 fS/LJF/RJF Timing in Slave Mode

All specifications at 25°C, DVDD = 1.8 V

| PARAMETER             |                  | IOVDD = 1.8 V |     | IOVDD = 3.3 V |     | LINUT |

|-----------------------|------------------|---------------|-----|---------------|-----|-------|

|                       |                  | MIN           | MAX | MIN           | MAX | UNIT  |

| t <sub>H</sub> (BCLK) | BCLK high period | 35            |     | 35            |     | ns    |

| t <sub>L</sub> (BCLK) | BCLK low period  | 35            |     | 35            |     | ns    |

| t <sub>s</sub> (WS)   | WCLK setup       | 8             |     | 6             |     | ns    |

| t <sub>h</sub> (WS)   | WCLK hold        | 8             |     | 6             |     | ns    |

| t <sub>s</sub> (DI)   | DIN setup        | 8             |     | 6             |     | ns    |

| t <sub>h</sub> (DI)   | DIN hold         | 8             |     | 6             |     | ns    |

| t <sub>r</sub>        | Rise time        |               | 4   |               | 4   | ns    |

| t <sub>f</sub>        | Fall time        |               | 4   |               | 4   | ns    |

Figure 3-2. I<sup>2</sup>S/LJF/RJF Timing in Slave Mode

# 3.5.3 DSP Timing in Master Mode

All specifications at 25°C, DVDD = 1.8 V

|                     | DADAMETED  | IOVE | IOVDD = 1.8 V IOVDD = 3.3 V |     |     |      |  |

|---------------------|------------|------|-----------------------------|-----|-----|------|--|

|                     | PARAMETER  | MIN  | MAX                         | MIN | MAX | UNIT |  |

| t <sub>d</sub> (WS) | WCLK delay |      | 45                          |     | 45  | ns   |  |

| $t_s(DI)$           | DIN setup  | 8    |                             | 6   |     | ns   |  |

| t <sub>h</sub> (DI) | DIN hold   | 8    |                             | 6   |     | ns   |  |

| t <sub>r</sub>      | Rise time  |      | 25                          |     | 10  | ns   |  |

| t <sub>f</sub>      | Fall time  |      | 25                          |     | 10  | ns   |  |

Figure 3-3. DSP Timing in Master Mode

# 3.5.4 DSP Timing in Slave Mode

All specifications at 25°C, DVDD = 1.8 V

|                       | DADAMETED        | IOVDD = 1.8 | 8V  | IOVDD = | LINUT |      |

|-----------------------|------------------|-------------|-----|---------|-------|------|

|                       | PARAMETER        | MIN N       | MAX | MIN     | MAX   | UNIT |

| t <sub>H</sub> (BCLK) | BCLK high period | 35          |     | 35      |       | ns   |

| t <sub>L</sub> (BCLK) | BCLK low period  | 35          |     | 35      |       | ns   |

| t <sub>s</sub> (WS)   | WCLK setup       | 8           |     | 8       |       | ns   |

| t <sub>h</sub> (WS)   | WCLK hold        | 8           |     | 8       |       | ns   |

| t <sub>s</sub> (DI)   | DIN setup        | 8           |     | 8       |       | ns   |

| t <sub>h</sub> (DI)   | DIN hold         | 8           |     | 8       |       | ns   |

| t <sub>r</sub>        | Rise time        | -           | 4   |         | 4     | ns   |

| t <sub>f</sub>        | Fall time        |             | 4   |         | 4     | ns   |

Figure 3-4. DSP Timing in Slave Mode

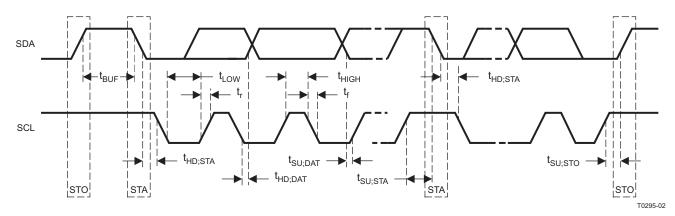

# 3.5.5 PC Interface Timing

All specifications at 25°C, DVDD = 1.8 V

|                     | PARAMETER                                                                                    | Stand | lard-Mode | )    | Fast                    | -Mode |     | UNITS |

|---------------------|----------------------------------------------------------------------------------------------|-------|-----------|------|-------------------------|-------|-----|-------|

|                     |                                                                                              | MIN   | TYP       | MAX  | MIN                     | TYP   | MAX |       |

| $f_{SCL}$           | SCL clock frequency                                                                          | 0     |           | 100  | 0                       |       | 400 | kHz   |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4     |           |      | 0.8                     |       |     | μs    |

| $t_{LOW}$           | LOW period of the SCL clock                                                                  | 4.7   |           |      | 1.3                     |       |     | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 4     |           |      | 0.6                     |       |     | μs    |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 4.7   |           |      | 0.8                     |       |     | μs    |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0     |           | 3.45 | 0                       |       | 0.9 | μs    |

| t <sub>SU;DAT</sub> | Data setup time                                                                              | 250   |           |      | 100                     |       |     | ns    |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |       |           | 1000 | 20 + 0.1 C <sub>b</sub> |       | 300 | ns    |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        |       |           | 300  | 20 + 0.1 C <sub>b</sub> |       | 300 | ns    |

| t <sub>SU:STO</sub> | Set-up time for STOP condition                                                               | 4     |           |      | 0.8                     |       |     | μs    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 4.7   |           |      | 1.3                     |       |     | μs    |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |       |           | 400  |                         |       | 400 | pF    |

Figure 3-5. I<sup>2</sup>C Interface Timing

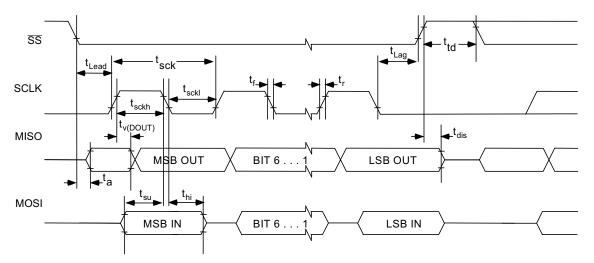

# 3.5.6 SPI Interface Timing

Figure 3-6. SPI Interface Timing Diagram

# **Timing Requirements**

At 25°C, DVDD = 1.8V

**Table 3-1. SPI Interface Timing**

|                   | PARAMETER                 | TEST CONDITION | IOVI | DD=1.8V | IOVDD=3.3V |       |     | UNITS |

|-------------------|---------------------------|----------------|------|---------|------------|-------|-----|-------|

|                   |                           |                | MIN  | TYP MAX | MIN        | TYP I | MAX |       |

| t <sub>sck</sub>  | SCLK Period (1)           |                | 100  |         | 50         |       |     | ns    |

| t <sub>sckh</sub> | SCLK Pulse width High     |                | 50   |         | 25         |       |     | ns    |

| t <sub>sckl</sub> | SCLK Pulse width Low      |                | 50   |         | 25         |       |     | ns    |

| t <sub>lead</sub> | Enable Lead Time          |                | 30   |         | 20         |       |     | ns    |

| t <sub>lag</sub>  | Enable Lag Time           |                | 30   |         | 20         |       |     | ns    |

| t <sub>d</sub>    | Sequential Transfer Delay |                | 40   |         | 20         |       |     | ns    |

| ta                | Slave DOUT access time    |                |      | 40      |            |       | 40  | ns    |

| t <sub>dis</sub>  | Slave DOUT disable time   |                |      | 40      |            |       | 40  | ns    |

| t <sub>su</sub>   | DIN data setup time       |                | 15   |         | 15         |       |     | ns    |

| t <sub>hi</sub>   | DIN data hold time        |                | 15   |         | 10         |       |     | ns    |

| $t_{v;DOUT}$      | DOUT data valid time      |                |      | 25      |            |       | 18  | ns    |

| t <sub>r</sub>    | SCLK Rise Time            |                |      | 4       |            |       | 4   | ns    |

| t <sub>f</sub>    | SCLK Fall Time            |                |      | 4       |            |       | 4   | ns    |

<sup>(1)</sup> These parameters are based on characterization and are not tested in production.

# 4 Typical Performance

#### 4.1 Class D Speaker Driver Performance

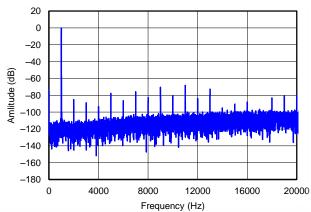

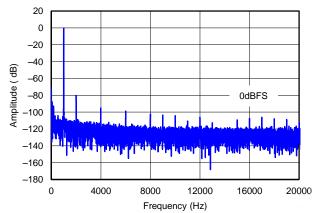

Figure 4-1. DAC To Speaker Amplitude at 0 dBFS vs Frequency (4  $\Omega$  Load)

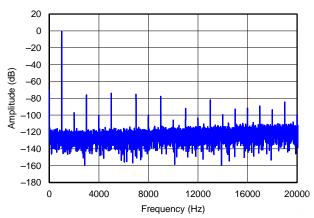

Figure 4-2. AINL To Speaker FFT Amplitude at 0 dBFS vs Frequency (4  $\Omega$  Load)

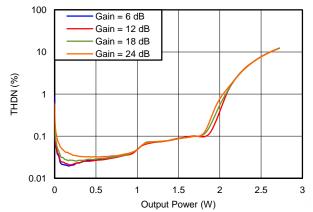

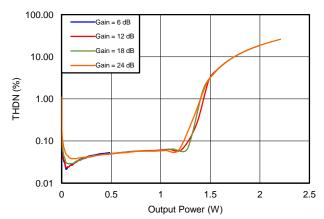

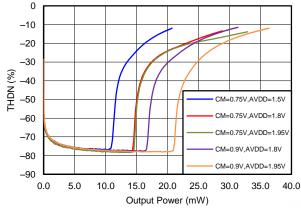

Figure 4-3. Total Harmonic Distortion + Noise vs 4  $\Omega$  Speaker Power (SPKVDD = 5.5 V)

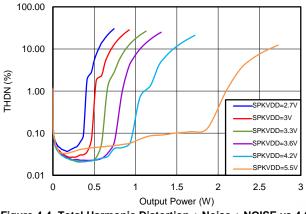

Figure 4-4. Total Harmonic Distortion + Noise + Noise vs 4  $\Omega$  Speaker Power (Gain = 18 dB)

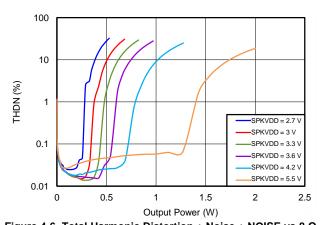

Figure 4-5. Total Harmonic Distortion + Noise + NOISE vs 8  $\Omega$  Speaker Power (SPKVDD = 5.5 V)

Figure 4-6. Total Harmonic Distortion + Noise + Noise vs 8  $\Omega$  Speaker Power (Gain = 18 dB)

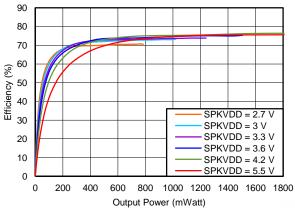

Figure 4-7. Total Power Consumption vs Output Power Consumption (Gain = 18 dB, Load =  $4 \Omega$ )

#### 4.2 HP Driver Performance

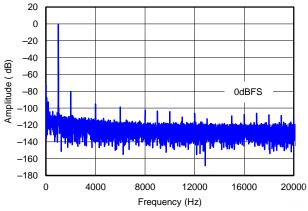

Figure 4-8. DAC TO HP FFT Amplitude at 0 dBFS vs Frequency (16  $\Omega$  Load)

Figure 4-9. AINL TO HP FFT Amplitude at 0 dBFS vs Frequency (16  $\Omega$  Load)

0

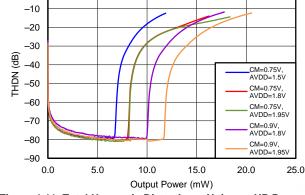

Figure 4-10. Total Harmonic Distortion + Noise vs HP Power (Gain = 9 dB)

Figure 4-11. Total Harmonic Distortion + Noise vs HP Power (Gain = 32 dB)

# 5 Application Overview

The TAS2521 offers a wide range of configuration options. Figure 1-1 shows the simplified functional blocks of the device.

# 5.1 Typical Circuit Configuration

Figure 5-1. Typical Circuit Configuration

# 5.2 Circuit Configuration with Internal LDO

Figure 5-2. Application Schematics for LDO

#### 5.3 Device Connections

#### 5.3.1 Digital Pins

Only a small number of digital pins are dedicated to a single function; whenever possible, the digital pins have a default function, and also can be reprogrammed to cover alternative functions for various applications.

The fixed-function pins are  $\overline{RST}$  LDO\_SEL and the SPI\_SEL pin, which are HW control pins. Depending on the state of SPI\_SEL, the two control-bus pins SCL/SSZ and SDA/MOSI are configured for either I<sup>2</sup>C or SPI protocol.

Other digital IO pins can be configured for various functions via register control. An overview of available functionality is given in Section 5.3.3.

# 5.3.2 Analog Pins

Analog functions can also be configured to a large degree. For minimum power consumption, analog blocks are powered down by default. The blocks can be powered up with fine granularity according to the application needs.

#### 5.3.3 Multifunction Pins

Table 5-1 shows the possible allocation of pins for specific functions. The PLL input, for example, can be programmed to be any of 4 pins (MCLK, BCLK, DIN, GPIO).

Table 5-1. Multifunction Pin Assignments

|   |                                       | 1                                  | 2                   | 3    | 4    | 5             | 6                | 7    |

|---|---------------------------------------|------------------------------------|---------------------|------|------|---------------|------------------|------|

|   | Pin Function                          | MCLK                               | BCLK                | WCLK | DIN  | GPIO<br>/DOUT | SCLK             | MISO |

| Α | PLL Input                             | S <sup>(1)</sup>                   | S <sup>(2)</sup>    |      | Е    |               | S <sup>(3)</sup> |      |

| В | Codec Clock Input                     | S <sup>(1)</sup> ,D <sup>(4)</sup> | S <sup>(2)</sup>    |      |      |               | S <sup>(3)</sup> |      |

| С | I <sup>2</sup> S BCLK input           |                                    | S <sup>(2)</sup> ,D |      |      |               |                  |      |

| D | I <sup>2</sup> S BCLK output          |                                    | E <sup>(5)</sup>    |      |      |               |                  |      |

| E | I <sup>2</sup> S WCLK input           |                                    |                     | E, D |      |               |                  |      |

| F | I <sup>2</sup> S WCLK output          |                                    |                     | Е    |      |               |                  |      |

| G | I <sup>2</sup> S DIN                  |                                    |                     |      | E, D |               |                  |      |

| Н | I <sup>2</sup> S DOUT                 |                                    |                     |      |      | Е             |                  |      |

| I | General Purpose Output I              |                                    |                     |      |      | Е             |                  |      |

| 1 | General Purpose Output II             |                                    |                     |      |      |               |                  | E    |

| J | General Purpose Input I               |                                    |                     |      | E    |               |                  |      |

| J | General Purpose Input II              |                                    |                     |      |      | Е             |                  |      |

| J | General Purpose Input III             |                                    |                     |      |      |               | Е                |      |

| K | INT1 output                           |                                    |                     |      |      | Е             |                  | E    |

| L | INT2 output                           |                                    |                     |      |      | Е             |                  | E    |

| M | Secondary I <sup>2</sup> S BCLK input |                                    |                     |      |      | Е             | Е                |      |

| N | Secondary I <sup>2</sup> S WCLK input |                                    |                     |      |      | Е             | Е                |      |

| 0 | Secondary I <sup>2</sup> S DIN        |                                    |                     |      |      | Е             | Е                |      |

| Р | Secondary I <sup>2</sup> S BCLK OUT   |                                    |                     |      |      | Е             |                  | E    |

| Q | Secondary I <sup>2</sup> S WCLK OUT   |                                    |                     |      |      | Е             |                  | E    |

| R | Secondary I <sup>2</sup> S DOUT       |                                    |                     |      |      |               |                  | E    |

| S | Aux Clock Output                      |                                    |                     |      |      | Е             |                  | E    |

<sup>(1)</sup> S(1): The MCLK pin can drive the PLL and Codec Clock inputs **simultaneously**.

# 5.4 Audio Analog I/O

The TAS2521 features a mono audio DAC. It supports a wide range of analog interfaces to support different headsets such as  $16-\Omega$  to  $200-\Omega$  impedance and analog line outputs. TheTAS2521 can drive a speaker upto  $4-\Omega$  impedance.

# 5.5 Analog Signals

The TAS2521 analog signals consist of:

- Analog inputs AINR and AINL, which can be used to pass-through or mix analog signals to output stages

- Analog outputs class-D speaker driver and headphone/lineout driver providing output capability for the DAC, AINR, AINL, or a mix of the three

<sup>(2)</sup> S<sup>(2)</sup>: The BCLK pin can drive the PLL and Codec Clock and audio interface bit clock inputs **simultaneously**.

<sup>(3)</sup> S<sup>(3)</sup>: The GPIO/DOUT pin can drive the PLL and Codec Clock inputs **simultaneously**.

<sup>(4)</sup> D: Default Function

<sup>(5)</sup> E: The pin is **exclusively** used for this function, no other function can be implemented with the same pin. (If GPIO/DOUT has been allocated for General Purpose Output, it cannot be used as the INT1 output at the same time.)

#### 5.5.1 Analog Inputs AINL and AINR

AINL (pin 3 or C2) and AINR (pin 4 or B2) are inputs to Mixer P and Mixer M along with the DAC output. Also AINL and AINR can be configured inputs to HP driver. Page1 / register 12 provides control signals for determining the signals routed through Mixer P, Mixer M and HP driver. Input of Mixer P can be attenuated by Page1 / register 24, input of Mixer M can be attenuated by Page1 / register 25 and input of HP driver can be attenuated by Page1 / register 22. Also AINL and AINR can be configured to a monaural differential input with use Mixer P and Mixer M by Page1 / register 12 setting.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6 Audio DAC and Audio Analog Outputs

The mono audio DAC consists of a digital audio processing block, a digital interpolation filter, a digital delta-sigma modulator, and an analog reconstruction filter. The high oversampling ratio (normally DOSR is between 32 and 128) exhibits good dynamic range by ensuring that the quantization noise generated within the delta-sigma modulator stays outside of the audio frequency band. Audio analog outputs include mono headphone and lineout and mono class-D speaker outputs. Because the TAS2521 contains a mono DAC, it inputs the mono data from the left channel, the right channel, or a mix of the left and right channels as  $[(L + R) \div 2]$ , selected by page 0, register 63, bits D5–D4.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.1 DAC

The TAS2521 mono audio DAC supports data rates from 8 kHz to 192 kHz. The audio channel of the mono DAC consists of a signal-processing engine with fixed processing blocks, a programmable miniDSP, a digital interpolation filter, multibit digital delta-sigma modulator, and an analog reconstruction filter. The DAC is designed to provide enhanced performance at low sampling rates through increased oversampling and image filtering, thereby keeping quantization noise generated within the delta-sigma modulator and observed in the signal images strongly suppressed within the audio band to beyond 20 kHz. To handle multiple input rates and optimize power dissipation and performance, the TAS2521 allows the system designer to program the oversampling rates over a wide range from 1 to 1024 by configuring page 0, register 13 and page 0 / register 14. The system designer can choose higher oversampling ratios for lower input data rates and lower oversampling ratios for higher input data rates.

The TAS2521 DAC channel includes a built-in digital interpolation filter to generate oversampled data for the delta-sigma modulator. The interpolation filter can be chosen from three different types, depending on required frequency response, group delay, and sampling rate.

The DAC path of the TAS2521 features many options for signal conditioning and signal routing:

- Digital volume control with a range of -63.5 to +24dB

- Mute function

In addition to the standard set of DAC features the TAS2521 also offers the following special features:

- Digital auto mute

- Adaptive filter mode

#### 5.6.1.1 DAC Processing Blocks — Overview

The TAS2521 implements signal-processing capabilities and interpolation filtering via processing blocks. These fixed processing blocks give users the choice of how much and what type of signal processing they may use and which interpolation filter is applied.

The choices among these processing blocks allows the system designer to balance power conservation and signal-processing flexibility. Table 5-2 gives an overview of all available processing blocks of the DAC channel and their properties. The resource-class column gives an approximate indication of power consumption for the digital (DVDD) supply; however, based on the out-of-band noise spectrum, the analog power consumption of the drivers (AVDD) may differ.

The signal-processing blocks available are:

- First-order IIR

- · Scalable number of biquad filters

The processing blocks are tuned for common cases and can achieve high image rejection or low group delay in combination with various signal-processing effects such as audio effects and frequency shaping. The available first-order IIR and biquad filters have fully user-programmable coefficients.

Table 5-2. Overview – DAC Predefined Processing Blocks

| Processing<br>Block No. | Interpolation Filter | Channel | First-Order<br>IIR Available | Number of Biquads | Resource<br>Class |

|-------------------------|----------------------|---------|------------------------------|-------------------|-------------------|

| PRB_P1                  | Α                    | Mono    | Yes                          | 6                 | 6                 |

| PRB_P2                  | Α                    | Mono    | No                           | 3                 | 4                 |

| PRB_P3                  | В                    | Mono    | Yes                          | 6                 | 4                 |

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.2 Digital Mixing and Routing

The TAS2521 has four digital mixing blocks. Each mixer can provide either mixing or multiplexing of the digital audio data. The first mixer/multiplexer can be used to select input data for the mono DAC from left channel, right channel, or (left channel + right channel) / 2 mixing. This digital routing can be configured by writing to page 0, register 63, bits D5–D4.

#### 5.6.3 Analog Audio Routing

The TAS2521 has the capability to route the DAC output to either the headphone or the speaker output. If desirable, both output drivers can be operated at the same time while playing at different volume levels. The TAS2521 provides various digital routing capabilities, allowing digital mixing or even channel swapping in the digital domain. All analog outputs other than the selected ones can be powered down for optimal power consumption.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.4 5V LDO

The TAS2521 has a built-in LDO which can generate the analog supply (AVDD) also the digital supply (DVDD) from input voltage range of 2.7 V to 5.5 V with high PSRR. If combined power supply current is 50 mA or less, then this LDO can deliver power to both analog and digital power supplies. If the only speaker power supply is present and LDO Select pin is enabled, the LDO can power up without requiring other supplies. This LDO requires a minimum dropout voltage of 300 mV and can support load currents up to 50 mA. For stability reasons the LDO requires a minimum decoupling capacitor of 1  $\mu$ F (±50%) on the analog supply (AVDD) pin and the digital supply (DVDD) pin. If use this LDO output voltage for the digital supply (DVDD) pin, the analog supply (AVDD) pin connected to the digital supply (DVDD) externally is required.

The LDO is by default powered down for low sleep mode currents and can be enabled driving the LDO\_SELECT pin to SPKVDD (Speaker power supply). When the LDO is disabled the AVDD pin is tristated and the device AVDD needs to be powered using external supply. In that case the DVDD pin is also tri-stated and the device DVDD needs to be powered using external supply. The output voltage of this LDO can be adjusted to a few different values as given in the Table 5-3.

#### Table 5-3. AVDD LDO Settings

| Page-1, Register 2, D(5:4) | LDO Output |

|----------------------------|------------|

| 00                         | 1.8 V      |

| 01                         | 1.6 V      |

| 10                         | 1.7 V      |

| 00                         | 1.5 V      |

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.5 POR

TAS2521 has a POR (Power On Reset) function. This function insures that all registers are automatically set to defaults when a proper power up sequence is executed.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.6 CLOCK Generation and PLL

The TAS2521 supports a wide range of options for generating clocks for the DAC sections as well as interface and other control blocks. The clocks for the DAC require a source reference clock. This clock can be provided on a variety of device pins, such as the MCLK, BCLK, or GPIO pins. The source reference clock for the codec can be chosen by programming the CODEC\_CLKIN value on page 0, register 4, bits D1–D0. The CODEC\_CLKIN can then be routed through highly-flexible clock dividers shown in to generate the various clocks required for the DAC and the miniDSP section. In the event that the desired audio clocks cannot be generated from the reference clocks on MCLK, BCLK, or GPIO, the TAS2521 also provides the option of using the on-chip PLL which supports a wide range of fractional multiplication values to generate the required clocks. Starting from CODEC\_CLKIN, the TAS2521 provides several programmable clock dividers to help achieve a variety of sampling rates for the DAC and clocks for the miniDSP sections.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.7 Digital Audio and Control Interface

#### 5.6.7.1 Digital Audio Interface

Audio data is transferred between the host processor and the TAS2521 via the digital audio data serial interface, or audio bus. The audio bus on this device is flexible, including left- or right-justified data options, support for I<sup>2</sup>S or PCM protocols, programmable data-length options, a TDM mode for multichannel operation, flexible master/slave configurability for each bus clock line, and the ability to communicate with multiple devices within a system directly.

The audio bus of the TAS2521 can be configured for left- or right-justified, I<sup>2</sup>S, DSP, or TDM modes of operation, where communication with standard telephony PCM interfaces is supported within the TDM mode. These modes are all MSB-first, with data width programmable as 16, 20, 24, or 32 bits by configuring page 0, register 27, bits D5–D4. In addition, the word clock and bit clock can be independently configured in either master or slave mode for flexible connectivity to a wide variety of processors. The word clock is used to define the beginning of a frame, and may be programmed as either a pulse or a square-wave signal. The frequency of this clock corresponds to the maximum of the selected DAC sampling frequencies.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.7.2 Control Interface

The TAS2521 control interface supports SPI or I2C communication protocols, with the protocol selectable using the SPI\_SEL pin. For SPI, SPI\_SEL should be tied high; for I2C, SPI\_SEL should be tied low. It is not recommended to change the state of SPI\_SEL during device operation.

#### 5.6.7.2.1 **PC** Control Mode

The TAS2521 supports the I<sup>2</sup>C control protocol, and will respond to the I<sup>2</sup>C address of 0011 000. I<sup>2</sup>C is a two-wire, open-drain interface supporting multiple devices and masters on a single bus. Devices on the I<sup>2</sup>C bus only drive the bus lines LOW by connecting them to ground; they never drive the bus lines HIGH. Instead, the bus wires are pulled HIGH by pullup resistors, so the bus wires are HIGH when no device is driving them LOW. This way, two devices cannot conflict; if two devices drive the bus simultaneously, there is no driver contention.

#### 5.6.7.2.2 SPI Digital Interface

In the SPI control mode,the TAS2521 uses the pins SCL/SSZ=SSZ, SCLK=SCLK, MISO=MISO, SDA/MOSI=MOSI as a standard SPI port with clock polarity setting of 0 (typical microprocessor SPI control bit CPOL = 0). The SPI port allows full-duplex, synchronous, serial communication between a host processor (the master) and peripheral devices (slaves). The SPI master (in this case, the host processor) generates the synchronizing clock (driven onto SCLK) and initiates transmissions. The SPI slave devices (such as the TAS2521) depend on a master to start and synchronize transmissions. A transmission begins when initiated by an SPI master. The byte from the SPI master begins shifting in on the slave MOSI pin under the control of the master serial clock(driven onto SCLK). As the byte shifts in on the MOSI pin, a byte shifts out on the MISO pin to the master shift tregister.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.7.3 Power Supply

The TAS2521 integrates a large amount of digital and analog functionality, and each of these blocks can be powered separately to enable the system to select appropriate power supplies for desired performance and power consumption. The device has separate power domains for digital IO, digital core, analog core, analog input, headphone driver, and speaker drivers. If desired, all of the supplies (except for the supplies for speaker drivers, which can directly connect to the battery) can be connected together and be supplied from one source in the range of 1.65 to 1.95V. Individually, the IOVDD voltage can be supplied in the range of 1.1V to 3.6V. For improved power efficiency, the digital core power supply can range from 1.26V to 1.95V. The analog core supply can either be derived from the internal LDO accepting an SPKVDD voltage in the range of 2.7V to 5.5V, or the AVDD pin can directly be driven with a voltage in the range of 1.5V to 1.95V. The speaker driver voltages (SPKVDD) can range from 2.7V to 5.5V.

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

#### 5.6.7.4 Device Special Functions

- Interrupt generation

- Flexible pin multiplexing

For more detailed information see the TAS2521 Application Reference Guide (SLAU456).

# 5.6.7.5 miniDSP

The TAS2521 features a miniDSP core which is tightly coupled to the DAC. The fully programmable algorithms for the miniDSP must be loaded into the device after power up. The miniDSP has direct access to the digital audio stream, offering the possibility for advanced, very low-group-delay DSP algorithms. The miniDSP has 512 programmable instructions, 896 data memory locations, and 512 programmable coefficients (in the adaptive mode, each bank has 256 programmable coefficients).

www.ti.com

#### 5.6.7.5.1 Software

Software development for the TAS2521 is supported through TI's comprehensive PurePath™ Studio software development environment, a powerful, easy-to-use tool designed specifically to simplify software development on Texas Instruments miniDSP audio platforms. The graphical development environment consists of a library of common audio functions that can be dragged and dropped into an audio signal flow and graphically connected together. The DSP code can then be assembled from the graphical signal flow with the click of a mouse. See the TAS2521 product folder on <a href="https://www.ti.com">www.ti.com</a> to learn more about PurePath Studio and the latest status on available, ready-to-use DSP algorithms.

# **Register Map**

#### **Register Map Summary** 6.1

Table 6-1. Summary of Register Map

| Dec      | imal     | Н        | ex          | DESCRIPTION                                                   |

|----------|----------|----------|-------------|---------------------------------------------------------------|

| PAGE NO. | REG. NO. | PAGE NO. | REG. NO.    |                                                               |

| 0        | 0        | 0x00     | 0x00        | Page Select Register                                          |

| 0        | 1        | 0x00     | 0x01        | Software Reset Register                                       |

| 0        | 2 - 3    | 0x00     | 0x02 - 0x03 | Reserved Registers                                            |

| 0        | 4        | 0x00     | 0x04        | Clock Setting Register 1, Multiplexers                        |

| 0        | 5        | 0x00     | 0x05        | Clock Setting Register 2, PLL P and R Values                  |

| 0        | 6        | 0x00     | 0x06        | Clock Setting Register 3, PLL J Values                        |

| 0        | 7        | 0x00     | 0x07        | Clock Setting Register 4, PLL D Values (MSB)                  |

| 0        | 8        | 0x00     | 0x08        | Clock Setting Register 5, PLL D Values (LSB)                  |

| 0        | 9 - 10   | 0x00     | 0x09 - 0x0A | Reserved Registers                                            |

| 0        | 11       | 0x00     | 0x0B        | Clock Setting Register 6, NDAC Values                         |

| 0        | 12       | 0x00     | 0x0C        | Clock Setting Register 7, MDAC Values                         |

| 0        | 13       | 0x00     | 0x0D        | DAC OSR Setting Register 1, MSB Value                         |

| 0        | 14       | 0x00     | 0x0E        | DAC OSR Setting Register 2, LSB Value                         |

| 0        | 15       | 0x00     | 0x0F        | miniDSP_D Instruction Control Register 1                      |

| 0        | 16       | 0x00     | 0x10        | miniDSP_D Instruction Control Register 2                      |

| 0        | 17       | 0x00     | 0x11        | miniDSP_D Interpolation Factor Setting Register               |

| 0        | 18 - 24  | 0x00     | 0x12 - 0x18 | Reserved Registers                                            |

| 0        | 25       | 0x00     | 0x19        | Clock Setting Register 10, Multiplexers                       |

| 0        | 26       | 0x00     | 0x1A        | Clock Setting Register 11, CLKOUT M divider value             |

| 0        | 27       | 0x00     | 0x1B        | Audio Interface Setting Register 1                            |

| 0        | 28       | 0x00     | 0x1C        | Audio Interface Setting Register 2, Data offset setting       |

| 0        | 29       | 0x00     | 0x1D        | Audio Interface Setting Register 3                            |

| 0        | 30       | 0x00     | 0x1E        | Clock Setting Register 12, BCLK N Divider                     |

| 0        | 31       | 0x00     | 0x1F        | Audio Interface Setting Register 4, Secondary Audio Interface |

| 0        | 32       | 0x00     | 0x20        | Audio Interface Setting Register 5                            |

| 0        | 33       | 0x00     | 0x21        | Audio Interface Setting Register 6                            |

| 0        | 34       | 0x00     | 0x22        | Reserved Register                                             |

| 0        | 35 - 36  | 0x00     | 0x23 - 0x24 | Reserved Registers                                            |

| 0        | 37       | 0x00     | 0x25        | DAC Flag Register 1                                           |

| 0        | 38       | 0x00     | 0x26        | DAC Flag Register 2                                           |

| 0        | 39-41    | 0x00     | 0x27-0x29   | Reserved Registers                                            |

| 0        | 42       | 0x00     | 0x2A        | Sticky Flag Register 1                                        |

| 0        | 43       | 0x00     | 0x2B        | Interrupt Flag Register 1                                     |

| 0        | 44       | 0x00     | 0x2C        | Sticky Flag Register 2                                        |

| 0        | 45       | 0x00     | 0x2D        | Reserved Register                                             |

| 0        | 46       | 0x00     | 0x2E        | Interrupt Flag Register 2                                     |