## **MP1720** 2.7W Mono Class D Low-EMI High-Efficiency Audio Amplifier

The Future of Analog IC Technology

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

## DESCRIPTION

The MP1720 is a high efficiency Class-D audio amplifier. It utilizes a full bridge output structure capable of delivering 2.7W into  $4\Omega$  speaker. This device exhibits the high fidelity of a class AB amplifier with an efficiency of 90% which dramatically reduces solution size by integrating the following:

- 250mΩ power MOSFETs (V<sub>IN</sub> =3.3V)

- Startup / Shutdown pop elimination

- Short circuit /Thermal overload Protection

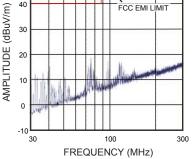

The MP1720 features a pin-selectable 1MHz or 1.3MHz frequency control or can be synchronized to an external clock source. The flexible switching frequency and internal EMI-reduction scheme eliminates the need for an output LC filter and passes emission standards without filter & with considerable cable.

The MP1720 has five fixed gain options. MP1720-3: 3dB; MP1720-6: 6dB; MP1720-9: 9dB; MP1720-12: 12dB; MP1720-216: 21.6dB.

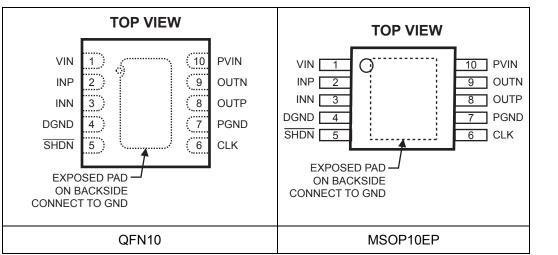

The MP1720 is available in 10-pin MSOP-EP and 10-pin QFN packages.

# FEATURES

- Passes FCC-Radiated Emissions Standards with 24inch of Cable without output filter

- 2.7W Into 4Ω with 5V VIN @ 10% THD+N

- Up to 90% Efficiency

- Flexible Switching Frequency setting

- Low Noise (53µV Typical) with 3.3V VIN

- 15ms Start-up time Eliminates pop

- Low Quiescent Current (4mA @3.3V)

- Low Shutdown Current (0.1µA)

- Full Bridge Output Drive

- Fully Differential Input

- Short circuit Protection

50

Thermal Shutdown

### APPLICATIONS

- Cellular Phones

- PDAs

- MP3 Players

- Portable Audio

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

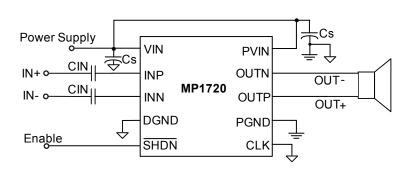

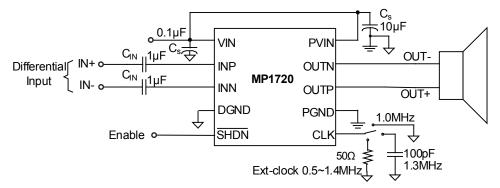

## TYPICAL APPLICATION

EMI Spectrum Diagram VIN=3.3V, R<sub>LOAD</sub>=8Ω, no output filter, CLK=GND, Near field, 6 inch unshielded twisted-pair-speaker cable

.02 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

**MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY**

### **ORDERING INFORMATION**

| Part Number* | Package           | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|-------------------|-------------|----------------------------------------|

| MP1720DQ-3   |                   | 6J          |                                        |

| MP1720DQ-6*  | QFN10 (3mm x 3mm) | 7J          |                                        |

| MP1720DQ-9*  |                   | 8J          |                                        |

| MP1720DQ-12* |                   | 9J          |                                        |

| MP1720DQ-216 |                   | 2К          | 1000 to 10500                          |

| MP1720DH-3*  |                   | 1720K       | -40°C to +85°C                         |

| MP1720DH-6*  | MSOP10EP          | 1720L       |                                        |

| MP1720DH-9*  |                   | 1720M       |                                        |

| MP1720DH-12* |                   | 1720N       |                                        |

| MP1720DH-216 |                   | 1720P       |                                        |

\* Contact factory for availability

### PACKAGE REFERENCE

### ABSOLUTE MAXIMUM RATINGS (1)

| VIN to DGND6.0V                                           |

|-----------------------------------------------------------|

| PVIN to PGND6.0V                                          |

| DGND to PGND0.3V to +0.3V                                 |

| PVIN to VIN0.3V to +0.3V                                  |

| All Other Pins to DGND0.3V to (VIN + 0.3V)                |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |

| QFN10                                                     |

| MSOP10-EP 1.2W                                            |

| Junction Temperature+140°C                                |

| Storage Temperature Range65°C to +150°C                   |

| Lead Temperature (soldering, 10s)+260°C                   |

| Recommended Operating Conditions <sup>(3)</sup>           |

| Supply Voltage VIN                                        |

Operating Junct. Temp. (T<sub>J</sub>).... -40°C to +125°C

### Thermal Resistance $^{(4)}$ $\theta_{JA}$

| 3x3 QFN10 | 50  | . 12 | .°C/W |

|-----------|-----|------|-------|

| MSOP10-EP | 105 | . 19 | .°C/W |

$\theta_{JC}$

Notes:

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operation conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

<sup>1)</sup> Exceeding these ratings may damage the device.

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION - INTERNAL USE ONLY

## **ELECTRICAL CHARACTERISTICS**

VIN = PVIN =  $\overline{SHDN}$  =3.3V, DGND = PGND = 0V, CLK = DGND (f<sub>CLK</sub>=1.0MHz), R<sub>Load</sub> =  $\infty$ , R<sub>Load</sub> connected between OUT+ and OUT-, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                        | Symbol                               | Conditio                                         |                             | Min  | Тур   | Max  | Unit  |

|--------------------------------------------------|--------------------------------------|--------------------------------------------------|-----------------------------|------|-------|------|-------|

| Output Offset Voltage                            | V <sub>os</sub>                      | Vs=0V, Av=4V/V,<br>V <sub>IN</sub> =2.5V to 5.5V |                             |      | ± 6   | ± 80 | mV    |

| Power Supply Rejection Ratio                     | PSRR                                 | V <sub>IN</sub> =2.5V to 5.5V                    |                             |      | -70   |      | dB    |

| Common Mode Rejection Ratio                      | CMRR                                 | $\Delta V_{IC}=0.6$                              |                             |      | -66   |      | dB    |

|                                                  |                                      | V <sub>IN</sub> =5.5V, no load,<br>switching     |                             |      | 7     |      |       |

| Quiescent Current                                | Ι <sub>Q</sub>                       | V <sub>IN</sub> =3.3V<br>switching               |                             |      | 4     | 8    | mA    |

|                                                  |                                      | V <sub>IN</sub> =2.5V<br>switching               |                             |      | 3.5   |      |       |

| Shut Down Current                                | l <sub>ds</sub>                      | SHDN =0<br>5.5V                                  | ), V <sub>IN</sub> =2.5V to |      | 0.1   | 4    | μA    |

| Turn-On Time                                     | t <sub>on</sub>                      |                                                  |                             |      | 15    |      | ms    |

| Input Equivalent Resistance                      | R <sub>INE</sub>                     |                                                  |                             | 12   | 21    |      | kΩ    |

|                                                  |                                      |                                                  | MP1720-3                    | 950  | 995   | 1035 | mV    |

|                                                  |                                      | <b>_</b>                                         | MP1720-6                    | 900  | 940   | 980  |       |

| Input Bias Voltage                               | V <sub>BIAS</sub>                    | Either<br>input                                  | MP1720-9                    | 820  | 860   | 900  |       |

|                                                  |                                      |                                                  | MP1720-12                   | 745  | 784   | 825  |       |

|                                                  |                                      |                                                  | MP1720-216                  | 410  | 465   | 530  |       |

|                                                  | Av                                   | MP1720-3                                         |                             | 1.3  | 1.4   | 1.5  | V/V   |

|                                                  |                                      | MP1720-6                                         |                             | 1.9  | 2.0   | 2.1  |       |

| Voltage Gain                                     |                                      | MP1720-9                                         |                             | 2.7  | 2.85  | 3.0  |       |

|                                                  |                                      | MP1720-12                                        |                             | 3.8  | 4.0   | 4.2  |       |

|                                                  |                                      | MP1720-216                                       |                             | 11.4 | 12.0  | 12.6 |       |

| Output Slew Rate                                 | SR                                   | V <sub>IN</sub> =3.3V                            |                             |      | 200   |      | V/µs  |

| Rise/Fall Time                                   | $t_{\text{RISE}}, t_{\text{FALL}}$   | 10% to 90%                                       |                             |      | 12    |      | ns    |

| Oscillator Frequency                             | f <sub>osc</sub>                     | CLK = GND                                        |                             |      | 1000  |      | kHz   |

| Oscillator Frequency                             |                                      | CLK = FLOAT                                      |                             |      | 1300  |      | KI IZ |

| CLK Frequency Lock Range                         | F <sub>CLK</sub>                     | V <sub>IN</sub> =2.5V to 5.5V                    |                             | 500  |       | 1400 | kHz   |

| UVLO                                             |                                      |                                                  |                             |      | 2.25  |      | V     |

| CLK Input Thresholds $V_{CLKH} = V_{CLKH}$       |                                      | V <sub>IN</sub> =2.5V                            | to 5.5V                     | 2.5  |       | 1    | V     |

| SHDN Input Thresholds                            | V <sub>SDH</sub><br>V <sub>SDL</sub> | V <sub>IN</sub> =2.5V to 5.5V                    |                             | 1.6  |       | 0.45 | V     |

| SHDN Input Leakage Current I <sub>Lkg_SHND</sub> |                                      | SHDN =6.3V                                       |                             |      | 0.1   | ±1   | μA    |

| CLK Input Current (5)                            | I <sub>Lkg CLK</sub>                 | Vclk = 0V                                        |                             |      | -1.25 | ±10  | μA    |

Notes:

5) CLK has an internal  $1M\Omega$  resistor to VREF.

### MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY OPERATION CHARACTERISTICS

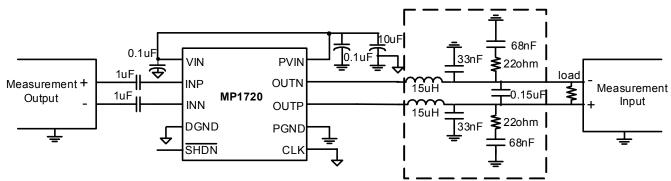

TEST SET-UP GRAPH, VIN = PVIN =  $\overline{SHDN}$  =3.3V, DGND = PGND = 0V, CLK = DGND (f<sub>CLK</sub>=1.0MHz), R<sub>Load</sub> = 4 $\Omega$ , Gain=12dB, T<sub>A</sub> = +25°C, unless otherwise noted <sup>(6)</sup>.

| Parameter                                       | Symbol         | Conditions                                                                              |                       | Min | Тур   | Мах | Unit                                    |

|-------------------------------------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------|-----|-------|-----|-----------------------------------------|

|                                                 |                |                                                                                         | V <sub>IN</sub> =5.0V |     | 2.14  |     | W                                       |

|                                                 |                | THD+N=1%,                                                                               | V <sub>IN</sub> =3.3V |     | 0.87  |     |                                         |

|                                                 |                | $R_{Load}$ =4 $\Omega$                                                                  | V <sub>IN</sub> =2.5V |     | 0.48  |     |                                         |

|                                                 |                |                                                                                         | V <sub>IN</sub> =5.0V |     | 2.78  |     |                                         |

|                                                 |                | THD+N=10%,<br>R <sub>Load</sub> =4Ω                                                     | V <sub>IN</sub> =3.3V |     | 1.18  |     |                                         |

| Output Bower                                    | р              | RLoad-412                                                                               | V <sub>IN</sub> =2.5V |     | 0.64  |     |                                         |

| Output Power                                    | Pout           |                                                                                         | V <sub>IN</sub> =5.0V |     | 1.19  |     |                                         |

|                                                 |                | THD+N=1%,<br>R <sub>Load</sub> =8Ω                                                      | V <sub>IN</sub> =3.3V |     | 0.55  |     |                                         |

|                                                 |                | RLoad-012                                                                               | V <sub>IN</sub> =2.5V |     | 0.31  |     | w                                       |

|                                                 |                | THD+N=10%,<br>$R_{Load}$ =8 $\Omega$                                                    | V <sub>IN</sub> =5.0V |     | 1.56  |     | - VV<br>-                               |

|                                                 |                |                                                                                         | V <sub>IN</sub> =3.3V |     | 0.71  |     |                                         |

|                                                 |                |                                                                                         | V <sub>IN</sub> =2.5V |     | 0.40  |     |                                         |

| Total Distortion Pulse                          | THD+N          | P <sub>OUT</sub> =2W,                                                                   | V <sub>IN</sub> =5.0V |     | 0.15% |     |                                         |

| Noise                                           |                | P <sub>OUT</sub> =0.8W                                                                  | V <sub>IN</sub> =3.3V |     | 0.13% |     |                                         |

| NOISE                                           |                | P <sub>OUT</sub> =0.4W                                                                  | V <sub>IN</sub> =2.5V |     | 0.13% |     |                                         |

| Supply Ripple<br>Rejection Ratio <sup>(7)</sup> | $K_{SVR}$      | f <sub>S</sub> =217Hz,<br>V <sub>Ripple</sub> =300mV <sub>PP</sub> ,<br>input AC-ground | V <sub>IN</sub> =3.3V |     | -60   |     | dB                                      |

| Signal to Noise Ratio                           | SNR            | V <sub>OUT</sub> =2 V <sub>RMS</sub><br>A-weighted                                      | V <sub>IN</sub> =3.3V |     | 91.3  |     | dB                                      |

| Output Noise                                    | V <sub>n</sub> | $V_{IN}$ =3.3V, $f_s$ =20Hz<br>to 20kHz, input AC-                                      | No weighting          |     | 72    |     | μV <sub>RMS</sub>                       |

|                                                 |                | grounded                                                                                | A weighting           |     | 53    |     | , , , , , , , , , , , , , , , , , , , , |

| Common Mode<br>Rejection Ratio <sup>(8)</sup>   | CMRR           | $Vic_{RIPPLE}$ =300mV <sub>PP</sub> ,<br>f <sub>s</sub> =1kHz                           | V <sub>IN</sub> =3.3V |     | -62   |     | dB                                      |

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION - INTERNAL USE ONLY

### **PIN FUNCTIONS**

| Pin # | Name        | Description                                                                                                                                                                                                        |  |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | VIN         | Analog Power Supply                                                                                                                                                                                                |  |

| 2     | INP         | Positive differential input                                                                                                                                                                                        |  |

| 3     | INN         | Negative differential input                                                                                                                                                                                        |  |

| 4     | DGND        | Analog Ground                                                                                                                                                                                                      |  |

| 5     | SHDN        | Shutdown input (drive high to enable the MP1720)                                                                                                                                                                   |  |

| 6     | CLK         | Frequency select and external clock input;<br>CLK=GND: Operate frequency $f_{CLK}$ =1.0MHz<br>CLK=FLOAT: Operate frequency $f_{CLK}$ =1.3MHz<br>CLK=Clocked: Operate frequency $f_{CLK}$ =external clock frequency |  |

| 7     | PGND        | Power Ground                                                                                                                                                                                                       |  |

| 8     | OUTP        | Positive BTL output                                                                                                                                                                                                |  |

| 9     | OUTN        | Negative BTL output                                                                                                                                                                                                |  |

| 10    | PVIN        | Power Supply                                                                                                                                                                                                       |  |

|       | Thermal Pad | Must be soldered to a ground on PCB                                                                                                                                                                                |  |

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION - INTERNAL USE ONLY

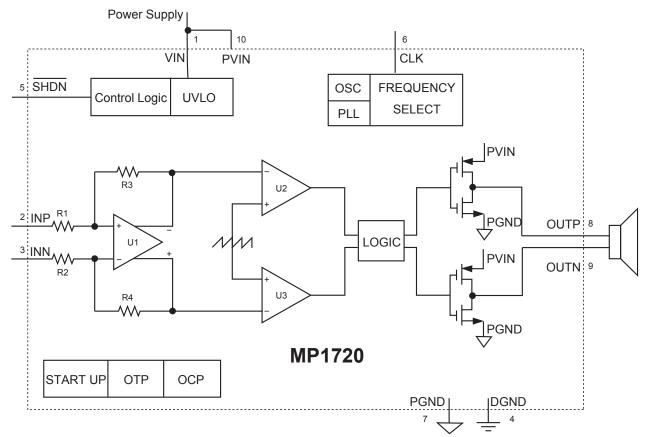

### FUNCTIONAL BLOCK DIAGRAM

Figure 1—MP1720 Functional Block Diagram

## TYPICAL PERFORMANCE CHARACTERISTICS

### **TEST SET-UP GRAPH**

#### Notes:

- 6) The 70kHz low-pass filter is required even if the analyzer has a low-pass filter.

- 7) For PSRR test, Please remove the 10uF decoupling capacitor and just keep the small decoupling capacitors for recovery switching currents.

- 8) CIN was shorted for any Common-Mode input voltage measurement.

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

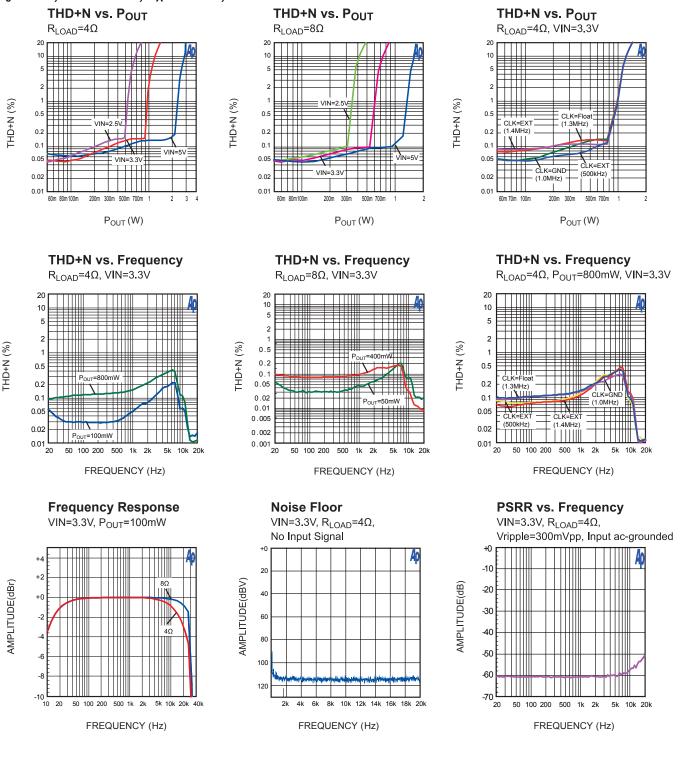

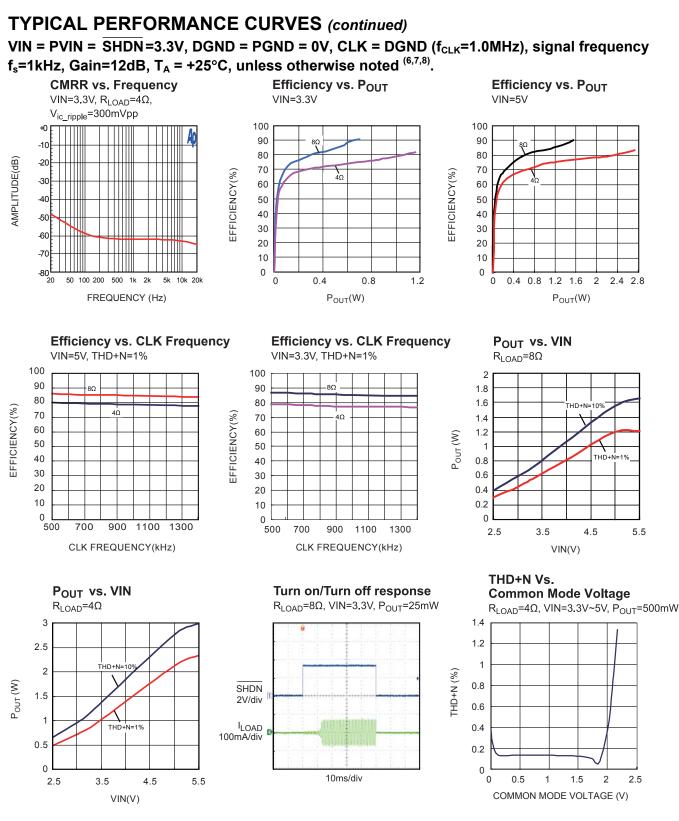

## **TYPICAL PERFORMANCE CURVES**

VIN = PVIN =  $\overline{SHDN}$  =3.3V, DGND = PGND = 0V, CLK = DGND (f<sub>CLK</sub>=1.0MHz), signal frequency f<sub>s</sub>=1kHz, Gain=12dB, T<sub>A</sub> = +25°C, unless otherwise noted <sup>(6,7,8)</sup>.

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

8

#### MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

#### OPERATION

The MP1720 is a high efficiency Class D audio power amplifier, low cost which can operate well without output LC filter, low EMI which can pass FCC-Radiated Emissions Standards with 24inch unshielded twisted-pair-speaker Cable without output filter. It has fully differential input and output. And this device can still be used with a single-ended input; but for some noisy environment the MP1720 should be used with differential inputs to ensure maximum noise rejection.

MP1720 Functional Block Diagram is shown as Figure 1. The amplifier detects the input signal and gets the input differential voltage, which would be combined with the DC bias voltage to generate the complementary voltage. The complementary voltage is compared with the sawtooth waveform. The output of the comparators (U2, U3) would trip when the input magnitude of the sawtooth exceeds the complementary voltage. When no signal is inputted, the output of both comparators are the pulse with a fixed turn on time, and zero output is got from the difference of two channel output (V<sub>OUTP</sub>-V<sub>OUTN</sub>). As the larger positive signal is inputted, the output duty of one comparator would be larger while another remains the fixed turn on time or less time, so larger output is got from the difference of two channel output (VOLTE-V<sub>OUTN</sub>). And there is opposite duty adjustment when the larger negative signal is inputted.

#### **CLK Operating Modes**

The MP1720 offers two kinds of operate frequency solution: internal fixed clock setting or be synchronized to an external clock. Allowing the switching frequency to be flexibly adjusted can avoid the frequency or harmonics fall in sensitive frequency bands.

#### 1) Internal clock Mode

The MP1720 have two kinds of internal clock selection. Setting CLK = DGND, the switching frequency is 1.0MHz. Setting CLK = FLOAT, the switching frequency is 1.3MHz.

#### 2) External Clock Mode

The MP1720 CLK input allows the amplifier to be synchronized to an external TTL clock, which can push the spectral components of the switching harmonics off sensitive frequency bands. This external TTL clock frequency range is very wide and frequency from 0.5MHz to 1.4MHz is recommended.

| CLK=GND     | f <sub>CLK</sub> =1.0MHz                   |

|-------------|--------------------------------------------|

| CLK=FLOAT   | f <sub>CLK</sub> =1.3MHz                   |

| CLK=Clocked | f <sub>CLK</sub> =external clock frequency |

#### Input configuration

The MP1720 is a mono BTL Class-D amplifier with differential inputs and outputs, and this device can still be used with a single-ended input

#### 1) Differential Input

For some noisy environment, the MP1720 should be used with differential inputs. The fully differential amplifier allows the inputs to be biased at voltage other than mid-supply. The input coupling capacitors are not required if the design uses a differential source that is biased from 0.2 V to 1.9V (please see TPC: THD+N vs. Common mode voltage). Although the input coupling capacitor is saved, the low frequency noise would be amplified to the speaker.

If the input signal is not biased within the recommended common-mode input range, the input coupling capacitors are needed to pass only the AC audio signal to the input of the amplifier as a high pass filter.

#### 2) Single-Ended Input

The MP1720 also can be configured as a singleended input amplifier. Input coupling capacitor is needed to create a high-pass filter with the input resistor and get the low frequency rejection.

Note: The voltage at each input pin (INP or INN) should be not lower than -0.5V, so the input signal voltage and the maximum output power would be limited, especially for the low gain part. For the high output power applications, the higher gain versions or the differential input is recommended.

#### MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

The peak-to-peak range of limited input voltage on each input pin V<sub>LIMIT(PP)</sub> can be calculated by the DC bias voltage  $V_{BIAS}$  as the following formula.

$$V_{\text{LIMIT (PP)}} = 2^* (V_{\text{BIAS}} + 0.5)$$

(1)

Take the application with input coupling capacitor as an example, the input DC bias voltage  $V_{BIAS}$ on each input pin is set internally (detailed value please see Input Bias Voltage in the EC table). For different gain options, the calculated maximum input signal and the tested maximum output power, with SE input or differential input, are shown in the Table 2.

#### Table 2—Maximum Input voltage and **Maximum Output Power**

|                | SE                                        | E input                      | Differential input                        |                              |  |

|----------------|-------------------------------------------|------------------------------|-------------------------------------------|------------------------------|--|

| Part           | V <sub>IN_max</sub><br>(V <sub>PP</sub> ) | P <sub>out</sub> _max<br>(W) | V <sub>IN_max</sub><br>(V <sub>PP</sub> ) | P <sub>out</sub> _max<br>(W) |  |

| MP1720-3       | 2.99                                      | 0.52                         | 5.98                                      | 1.9                          |  |

| MP1720-6       | 2.88                                      | 0.93                         | 5.76                                      | 2.7 @ 10%<br>THD+N           |  |

| MP1720-9       | 2.72                                      | 1.74                         | 5.44                                      | 2.7 @ 10%<br>THD+N           |  |

| MP1720-<br>12  | 2.568                                     | 2.62                         | 5.136                                     | 2.7 @ 10%<br>THD+N           |  |

| MP1720-<br>216 | 1.93                                      | 2.7 @ 10%<br>THD+N           | 3.86                                      | 2.7 @ 10%<br>THD+N           |  |

Test condition:VIN=PVIN=5V;  $4\Omega$  load.

#### **Shutdown Function**

The MP1720 SHDN input is a low-active control. To shutdown MP1720, drive SHDN low-level voltage. To enable MP1720, drive SHDN highlevel voltage. Shutdown function can place the MP1720 in a low-power (0.1µA) shutdown mode and reduce power consumption and extend battery life.

**Thermal Shutdown/ Short Circuit Protection** The MP1720 provides internal over thermal protection and short-circuit protection. The amplifier would be disabled to prevent damage to the IC if the junction temperature surpasses +125°C. The junction temperature must fall below +112°C before normal operation resumes. The currents of both the high-side and low-side MOSFETs are measured. If the current exceeds an internally preset value, all MOSFETs will be turned off. After the over thermal or short circuit fault is monitored, the MP1720 remains disabled status for a minimum of 50µs until normal operation resumes.

#### **Pop Suppression**

After driving SHDN pin high, there is a 15ms Start-up time to eliminate the startup pop. During this period, an internal circuitry would charges the bias voltages of the device to a certain level to prevent the startup click or pop. And after driving SHDN pin low, the all outputs will be set to high impedance immediately

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

### **APPLICATION INFORMATION**

### COMPONENT SELECTION

The MP1720 uses a minimum number of external components to complete a fully bridged Class D audio amplifier. Use the following sections to customize the amplifier for your particular application.

#### 1) Input Coupling Capacitors (C<sub>IN</sub>)

The MP1720 is a mono BTL Class-D amplifier with differential outputs and inputs. If the input signal is not biased within the recommended common-mode input range or if using a single-ended source, the input coupling capacitors are used to pass only the AC audio signal to the input of the amplifier as a high pass filter. Choose an input coupling capacitor such that the corner frequency  $f_{\rm IN}$  is less than the desired pass-band frequency. The formula for the corner frequency is:

$$f_{IN} = \frac{1}{2\pi R_{IN} C_{IN}}$$

(2)

$R_{IN}$  is 15k $\Omega$  for MP1720. Speakers in wireless handsets usually can't respond well to low frequencies, so for this application the corner frequency can be set to block the low frequencies.

The input coupling capacitance is calculated as:

$$C_{IN} = \frac{1}{2\pi R_{IN} f_{IN}}$$

(3)

If the corner frequency is within the audible band, the capacitors should have a tolerance of  $\pm 10\%$ or better, because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.

Tantalum or aluminum electrolytic capacitor with low-voltage coefficients is recommended, or the largest package ceramics capacitor to minimize voltage coefficient effects, for example X7R dielectrics is better than Y5V or Z5U.

### 2) Power Supply Decoupling Capacitor (C<sub>s</sub>)

The class-D audio amplifier requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD+N) is low. To carry the higher frequency transient current, spikes, or digital hash on the line, a good low

ESR ceramic capacitor is necessary. Place a  $1\mu$ F decoupling capacitor as close as possible to the device VCC lead. It is very important for the efficiency of the class-D amplifier, because any resistance or inductance in the trace between the capacitor and the device may cause a loss. A  $10\mu$ F or greater capacitor placed near the audio power amplifier would also help for filtering lower-frequency noise

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION - INTERNAL USE ONLY

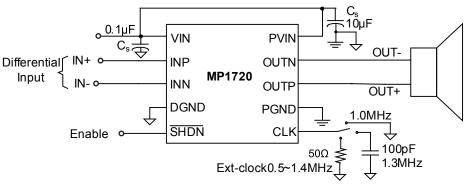

### **TYPICAL APPLICATION CIRCUIT**

Figure 2—MP1720 Application Schematic with Differential Input

(Input DC-biased voltage is within the recommended common-mode voltage range)

Figure 3—MP1720 Application Schematic with Differential Input

(Input DC-biased voltage is out of the recommended common-mode voltage range)

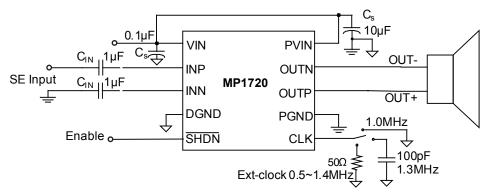

Figure 4—MP1720 Application Schematic with Single Ended Input

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION - INTERNAL USE ONLY

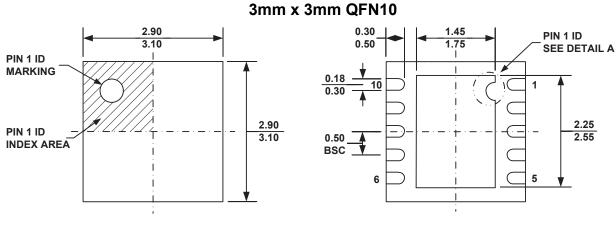

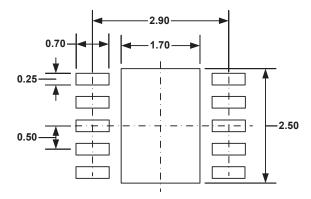

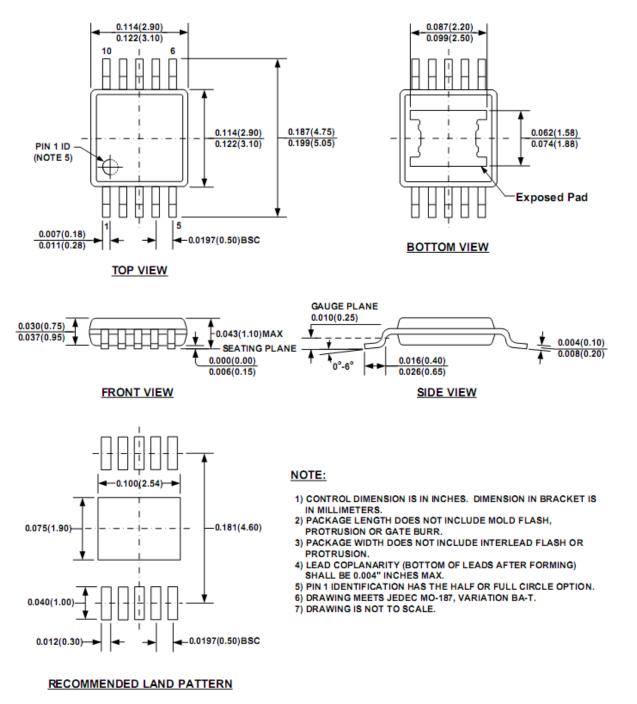

### PACKAGE INFORMATION

TOP VIEW

BOTTOM VIEW

SIDE VIEW

PIN 1 ID OPTION B R0.20 TYP.

DETAIL A

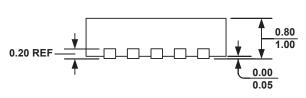

**RECOMMENDED LAND PATTERN**

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFORMS TO JEDEC MO-229, VARIATION VEED-5.

- 5) DRAWING IS NOT TO SCALE.

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION – INTERNAL USE ONLY

**MSOP-EP**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.