### High Efficiency 8-Channel LED Driver with I<sup>2</sup>C Interface and Phase-Shifted PWM Dimming

### **POWER MANAGEMENT**

### Features

- V<sub>IN</sub> Range 4.5V to 27V, V<sub>OUT</sub> Range Up to 50V

- Step-up (Boost) Controller

- Ultra-Fast Transient Response

- Integrated Soft-start

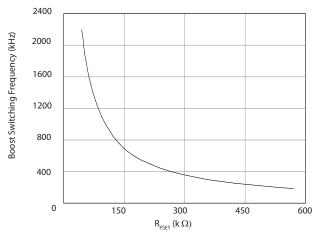

- Programmable Switching Frequency

- Linear Current Sinks

- 8 Strings, up to 50mA/String

- Current Matching ±1%

- Current Accuracy ±2%

- PWM Dimming

- String-by-String Phase Shifting

- Input Dimming Frequency 100Hz-30kHz

- User Selectable 9 or 10 Bits Dimming Resolution

- Optional Synchronization to VSYNC/HSYNC Signal

- Optional External p-MOSFET Disconnect Switch

- True Load Disconnect and Inrush Current Limiting

- I<sup>2</sup>C Interface

- Fault Status Open/Short LED, UVLO, OTP

- Device Control SYNC Freq, PLL Setting

- Protection Features

- Open/Shorted LED(s) and adjustable OVP

- Over-Temperature and UVLO Shutdown Protection

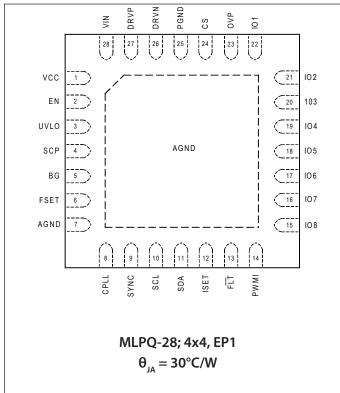

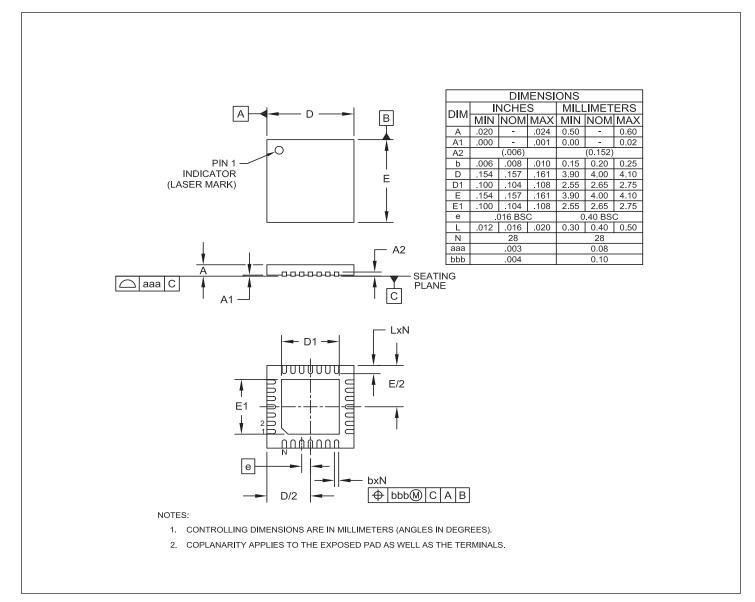

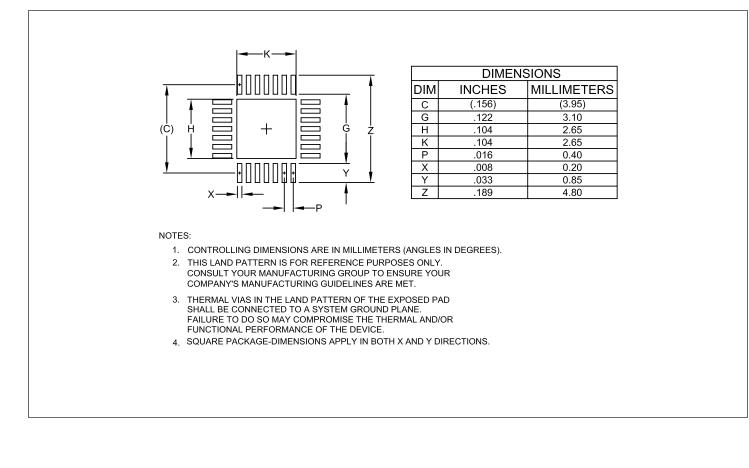

- 4 X 4 X 0.6 (mm) 28-pin QFN Package

### Applications

Notebook PCs, UMPC, LCD Monitors, and Tablet PCs

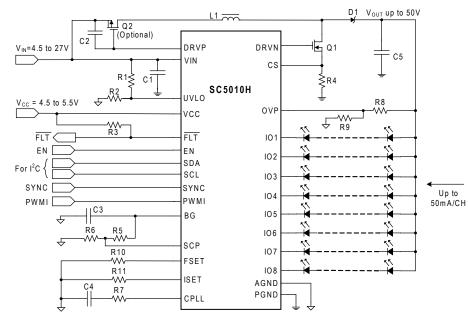

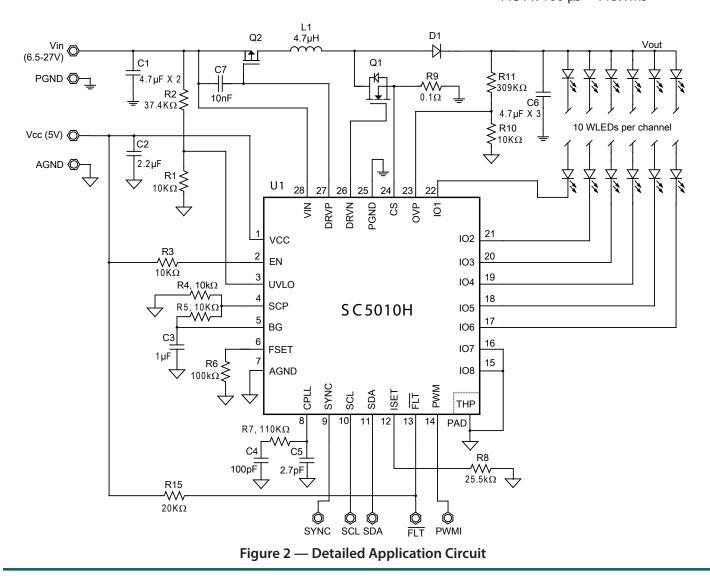

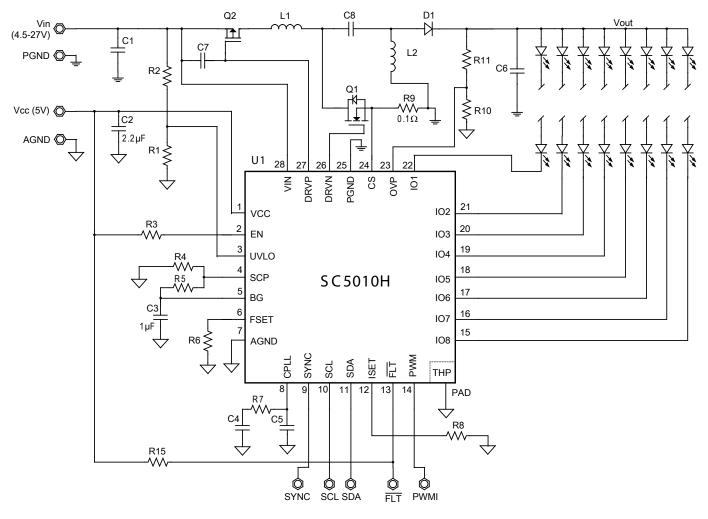

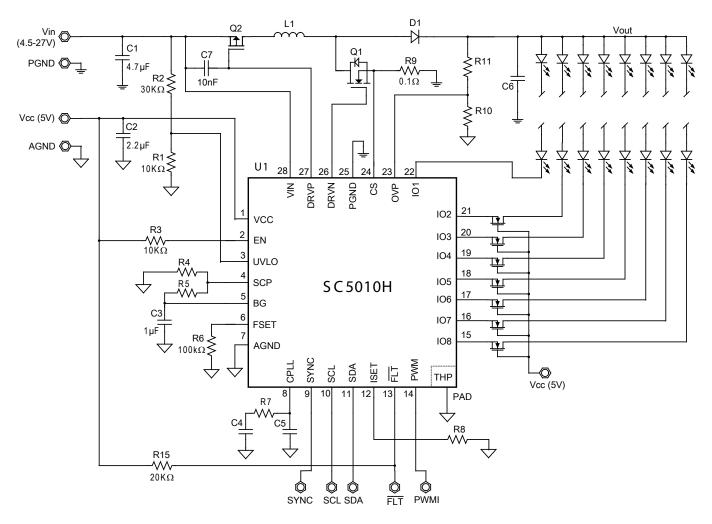

### **Typical Application Circuit**

### Description

The SC5010H is an 8-channel high-precision, high-efficiency step-up (Boost) LED driver for backlight applications. It features wide input voltage range (4.5V to 27V), flexible output configuration, wide analog and PWM dimming range, phase shifting and fading. It also features video signal synchronization (VSYNC), I<sup>2</sup>C interface, and numerous protection features. An optional disconnect p-MOSFET provides true load disconnection and inrush current limiting.

The boost controller, with programmable switching frequency from 200kHz to 2.2MHz, maximizes efficiency by dynamically minimizing the output voltage while maintaining LED string current accuracy. It provides excellent line and load response with no external compensation components. Each linear current sink is matched within  $\pm 1\%$  for superb lighting uniformity, and the accuracy of each string current is  $\pm 2\%$ . An external resistor adjusts the current from 10-50mA per string. It also features PWM dimming resolution of 9 or 10 bits (user selectable) over dimming frequency from 100Hz to 20kHz, synchronized to the SYNC signal or the boost oscillator. String-by-string phase shifting reduces the demand on the input/output capacitance, decreases EMI, and improves dimming linearity.

SC5010H is available in a low-profile, thermally enhanced, 4 X 4 X 0.6(mm) QFN 28-pin package.

### **Pin Configuration**

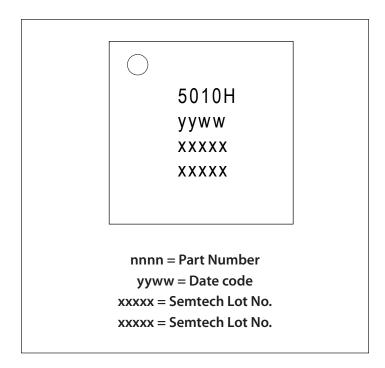

### **Marking Information**

### **Ordering Information**

| Device                         | Package          |

|--------------------------------|------------------|

| SC5010HULTRT <sup>(1)(2)</sup> | MLPQ-UT-28 4×4   |

| SC5010HEVB                     | Evaluation Board |

Notes:

(1) Available in tape and reel only. A reel contains 3,000 devices.

(2) Lead-free packaging only. Device is WEEE and RoHS compliant, and halogen-free.

### **Absolute Maximum Ratings**

| VCC Pin (V)0.3 to +6.0                                                              |

|-------------------------------------------------------------------------------------|

| VIN, DRVP, IO1 to IO8(V)                                                            |

| DRVN, OVP, CS, EN, UVLO, SCP, BG, $\overline{FLT}$ (V) $\ldots~$ -0.3 to $$ +6.0 $$ |

| FSET, CPLL, SYNC, SCL, SDA, ISET, PWMI (V)0.3 to +6.0                               |

| PGND TO AGND (V)                                                                    |

| ESD Protection Level <sup>(1)</sup> (kV) 2.5                                        |

|                                                                                     |

### **Recommended Operating Conditions**

| Ambient Temperature Range (°C)40 $\leq T_{_{A}} \leq$ +85   |

|-------------------------------------------------------------|

| $VIN\left(V\right)$ 4.5 to 27                               |

| IO1 to IO8 Current per String (mA) $\ldots \ldots$ up to 50 |

### **Thermal Information**

| Thermal Resistance, Junction to Ambient <sup>(2)</sup> (°C/W) $\dots 30$ |  |  |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|--|--|

| Maximum Junction Temperature (°C)+150                                    |  |  |  |  |  |  |

| Storage Temperature Range (°C)65 to +150                                 |  |  |  |  |  |  |

| Peak IR Reflow Temperature (10s to 30s) (°C) +260                        |  |  |  |  |  |  |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

NOTES:

- (1) Tested according to JEDEC standard JESD22-A114-B.

- (2) Calculated from package in still air, mounted to 3 x 4.5 (in.), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

### Electrical Characteristics -

Unless noted otherwise,  $T_A = 25^{\circ}C$  for typical,  $-40^{\circ}C < T_A = T_J < 85^{\circ}C$  for min and max.  $V_{CC} = 5V$ ,  $R_{ISET} = 32.4 \text{ k}\Omega$ ,  $R_{FSET} = 100 \text{ k}\Omega$ ,  $V_{IN} = 12V$ .

| Parameter                                          | Symbol                    | Conditions                       | Min                  | Тур                  | Мах  | Units |

|----------------------------------------------------|---------------------------|----------------------------------|----------------------|----------------------|------|-------|

| Input Supply                                       | ·                         |                                  | -                    |                      |      |       |

| V <sub>cc</sub> Supply Voltage                     | V <sub>cc</sub>           |                                  | 4.5                  |                      | 5.5  | V     |

| V <sub>cc</sub> Under-Voltage Lockout Threshold    | V <sub>CC-UVLO(TH)</sub>  | V <sub>cc</sub> Voltage Rising   | 4.0                  | 4.2                  | 4.4  | V     |

| V <sub>cc</sub> Under-Voltage Lockout Hysteresis   | V <sub>CC-UVLO(HYS)</sub> | V <sub>cc</sub> Voltage Falling  |                      | 180                  |      | mV    |

| V <sub>cc</sub> Quiescent Supply Current           | I <sub>CC(Q)</sub>        | EN = 5V, Switching, No Load      |                      | 2                    |      | mA    |

| V <sub>cc</sub> Supply Current in Shutdown         | I <sub>CC(SD)</sub>       | EN = 0V                          |                      |                      | 1    | μΑ    |

| V <sub>IN</sub> Supply Current in Shutdown         | I <sub>VIN(SD)</sub>      | EN = 0V, VIN = 27V               |                      |                      | 1    | μΑ    |

| V <sub>UVLO</sub> Under-Voltage Lockout Threshold  | V <sub>UVLO(TH)</sub>     | UVLO Pin Voltage Rising          | 1.18                 | 1.23                 | 1.28 | V     |

| I <sub>UVLO</sub> Under-Voltage Lockout Hysteresis | I <sub>UVLO(HYS)</sub>    | UVLO Pin Voltage Falling         | 7                    | 10                   | 13   | μΑ    |

| V <sub>BG</sub> Bandgap Voltage                    | V <sub>BG</sub>           |                                  | 1.20                 | 1.23                 | 1.26 | V     |

| External FET Gate Drive                            |                           |                                  |                      |                      |      |       |

| DRVN High Level                                    | V <sub>DRVN(H)</sub>      | 100mA from DRVN to GND           | V <sub>cc</sub> -0.5 | V <sub>cc</sub> -0.2 |      | V     |

| DRVN Low Level                                     | V <sub>DRVN(L)</sub>      | -100mA from DRVN to $\rm V_{cc}$ |                      | 0.2                  | 0.5  | v     |

| DRVN On-Resistance                                 | R <sub>drvn</sub>         | DRVN high or Low                 |                      | 2                    | 5    | Ω     |

| DRVN Sink / Source Current                         | I <sub>DRVN</sub>         | DRVN forced to 2.5V              |                      | 1                    |      | A     |

# **Electrical Characteristics (continued)**

| Parameter                           | Symbol                 | Conditions                                                                              | Min  | Тур  | Мах  | Units |

|-------------------------------------|------------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| Boost Converter                     | ·                      |                                                                                         |      |      |      |       |

| CS Current Limit Threshold          | V <sub>CS(ILIM)</sub>  |                                                                                         | 0.36 | 0.40 | 0.44 | V     |

| Soft-start Time (1)                 | t <sub>ss</sub>        | From EN to end of soft start                                                            |      | 4.4  |      | ms    |

| Boost Oscillator Frequency          | F <sub>sw</sub>        | $R_{FSET} = 100k\Omega$                                                                 | 0.85 | 1    | 1.15 | MHz   |

| Boost Oscillator Frequency          | F <sub>osc</sub>       | R <sub>FSET</sub> Varies                                                                | 0.2  |      | 2.2  | MHz   |

| Maximum Duty Cycle                  | D <sub>MAX</sub>       |                                                                                         | 85   | 90   |      | %     |

| Output Disconnect Gate Drive        |                        |                                                                                         |      |      |      |       |

| DRVP Sink Current                   | I DRVP(L)              | DRVP = 12V                                                                              |      | 20   |      | μΑ    |

| DRVP clamp voltage                  | V <sub>CLAMP</sub>     | DRVP floating, $V_{CLAMP} = V_{IN} - V_{DRVP}$                                          | 5    | 7    | 8    | V     |

| DRVP Pin Leakage Current            | I                      | $V_{DRVP} = 27V, V_{EN} = 0V$                                                           |      | 0.1  | 1    | μΑ    |

| Control Signals: EN, PWMI, SYNC, SE | DA, SCL                |                                                                                         |      |      |      |       |

| High Voltage Threshold              | V <sub>IH</sub>        | $V_{cc} = 4.5V \text{ to } 5.5V$                                                        | 2.1  |      |      | V     |

| Low Voltage Threshold               | V <sub>IL</sub>        | $V_{cc} = 4.5V \text{ to } 5.5V$                                                        |      |      | 0.8  | V     |

| SDA Output Low                      | V <sub>SDA(L)</sub>    | -6mA from V <sub>cc</sub> to SDA                                                        |      |      | 0.3  | V     |

| Pin Leakage Current                 | Ι <sub>LEAK</sub>      | $V_{EN} = 0V, V_{VSYNC} = V_{PWMI} = V_{ISET} = V_{FSET} = V_{SDA} = V_{SDL}$<br>= 5.0V |      |      | 1    | μΑ    |

| PWM Dimming Input                   | ·                      |                                                                                         |      |      |      |       |

| PWMI Input Dimming Frequency        | F <sub>PWMI</sub>      |                                                                                         | 100  |      | 30k  | Hz    |

| SYNC Input Frequency                | F <sub>SYNC</sub>      |                                                                                         | 30   |      | 100k | Hz    |

|                                     |                        | 100Hz < F <sub>PWMI</sub> < 10kHz                                                       |      | 10   |      | bits  |

| PWMI Input Resolution               |                        | 10kHz < F <sub>PWMI</sub> < 20kHz                                                       |      | 9    |      | bits  |

| Over-Voltage Protection             | · ·                    |                                                                                         |      |      |      |       |

| OVP Trip Threshold Voltage          | V <sub>OVP(TRIG)</sub> | OVP Rising                                                                              | 1.18 | 1.23 | 1.28 | V     |

| OVP Hysteresis                      | V <sub>OVP(HYS)</sub>  | OVP Falling                                                                             |      | 10   |      | mV    |

| OVP Leakage Current                 | I <sub>OVP(LEAK)</sub> | OVP = 5V                                                                                |      | 0.1  | 1    | μΑ    |

# **Electrical Characteristics (continued)**

| Parameter                                        | Symbol Conditions       |                                                                                     | Min                 | Тур                 | Max                 | Units |  |

|--------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|-------|--|

| Current Sink (IO1 to IO8)                        | · ·                     |                                                                                     |                     |                     |                     |       |  |

| IOx Dimming Minimum Pulse Width                  | T <sub>PWM(MIN)</sub>   | F <sub>PWM(LED)</sub> = 100Hz - 30kHz                                               |                     | 300                 |                     | ns    |  |

| ISET pin voltage                                 | V <sub>ISET</sub>       |                                                                                     |                     | 1.23                |                     | V     |  |

| Regulation Voltage                               | V <sub>IOn(REG)</sub>   | Voltage of Regulating String                                                        |                     | 0.9                 |                     | V     |  |

| Current Sink Disable Threshold                   | V <sub>IOn(DIS)</sub>   | Checked at Power-up                                                                 | 0.6                 |                     |                     | V     |  |

| Current Sink Rise/Fall Time (1)                  | t <sub>RISE/FALL</sub>  | Rising edge from 10% to 90% of I <sub>O(n)</sub>                                    |                     | 25                  |                     | ns    |  |

| LED Current Accuracy                             | I <sub>On(ACC%)</sub>   | PWMI = 100%, T <sub>A</sub> = +25°C                                                 | 39.2                | 40                  | 40.8                | mA    |  |

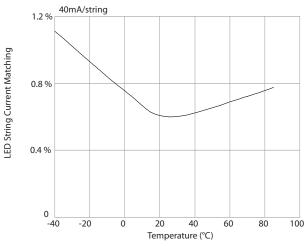

|                                                  |                         | PWMI = 100%, T <sub>A</sub> = +25 °C                                                |                     |                     | ±1                  | %     |  |

| LED Current Matching <sup>(2)</sup>              | On(MATCH)               | PWMI = 100%, $T_A = -40 \text{ °C to } +85 \text{ °C}$                              |                     |                     | ±2                  | %     |  |

| I <sub>on</sub> Off Leakage Current              | I <sub>On(LEAK)</sub>   | $PWMI = 0V, EN = 0V, V_{101} \sim V_{108} = 25V$                                    |                     | 0.1                 | 1                   | μΑ    |  |

|                                                  | _                       | FAST_FREQ = 0                                                                       |                     | 10                  |                     | kHz   |  |

| IO Switching Frequency                           | F <sub>PWM(IO)</sub>    | FAST_FREQ = 1 (Default Setting)                                                     |                     | 20                  |                     |       |  |

| Phase Delay Time between IO Pins<br>(IO1 to IO8) | t <sub>PD</sub>         | FAST_FREQ = 1 (default setting)<br>$t_{PD} = (1/8)^*(1/F_{PWM(IO)})$ , 8 Strings On |                     | 6.25                |                     | μs    |  |

|                                                  |                         | $F_{PWM(IO)} = 10kHz$                                                               |                     | 10                  |                     | b:+-  |  |

| PWM Output Resolution                            |                         | $F_{PWM(IO)} = 20kHz$                                                               |                     | 9                   |                     | bits  |  |

| Fault Protection                                 |                         |                                                                                     | ·                   |                     |                     |       |  |

| LED Short Circuit Protection Threshold           | V <sub>IOn(SCP)</sub>   | $R_4$ and $R_5^{(3)}$                                                               | 17xV <sub>SCP</sub> | 20xV <sub>SCP</sub> | 23xV <sub>SCP</sub> | V     |  |

| LED Open Circuit Protection Threshold            | V <sub>IO_OCP</sub>     |                                                                                     |                     | 0.2                 |                     | V     |  |

| LED Short Circuit Fault Delay                    | t <sub>SCP(DELAY)</sub> | $V_{ovP}$ set to 1.5V, FLT goes low                                                 |                     | 1                   |                     | μs    |  |

| FLT Pin Leakage Current                          | I<br>FLT(LEAK)          | $V_{EN} = 0V, V_{\overline{FLT}} = 5.0V$                                            | -1                  |                     | 1                   | μΑ    |  |

| FLT Output Low                                   | V <sub>FLT(LOW)</sub>   | -5mA from $\overline{\text{FLT}}$ to V <sub>cc</sub>                                |                     |                     | 0.3                 | V     |  |

| Over-Temperature Protection                      | ·                       |                                                                                     |                     |                     | I                   | -     |  |

| Thermal Shutdown Temperature                     |                         |                                                                                     |                     | 150                 |                     | °C    |  |

| Thermal Shutdown Hysteresis                      |                         |                                                                                     |                     | 10                  |                     | °C    |  |

### **Electrical Characteristics (continued)**

| Parameter                                                          | Symbol                 | Conditions | Min | Тур | Мах | Units |  |  |  |  |

|--------------------------------------------------------------------|------------------------|------------|-----|-----|-----|-------|--|--|--|--|

| I <sup>2</sup> C Control Interface: SDA, SCL Timing Specifications |                        |            |     |     |     |       |  |  |  |  |

| SCL Clock Frequency                                                | F <sub>SCL</sub>       |            |     |     | 400 | kHz   |  |  |  |  |

| SCL Clock Low Period                                               | t <sub>LOW(SCL)</sub>  |            | 1.3 |     |     | μs    |  |  |  |  |

| SCL Clock High Period                                              | t <sub>HIGH(SCL)</sub> |            | 0.6 |     |     | μs    |  |  |  |  |

| Hold Time Start Condition                                          | t <sub>HD(START)</sub> |            | 0.6 |     |     | μs    |  |  |  |  |

| SDA Setup Time                                                     | t <sub>su(SDA)</sub>   |            | 100 |     |     | ns    |  |  |  |  |

| SDA Hold Time                                                      | t <sub>HD(SDA)</sub>   |            | 0   |     | 0.9 | μs    |  |  |  |  |

| Setup Time Stop Condition                                          | t <sub>SU(STOP)</sub>  |            | 0.6 |     |     | μs    |  |  |  |  |

| Bus Free Time between Stop & Start                                 | t <sub>BF</sub>        |            | 1.3 |     |     | μs    |  |  |  |  |

Notes:

(1) Ensured by design and characterization, not production tested

(2) LED current matching for 8 channels is defined as the largest of the two numbers, i.e., (MAX-AVG)/AVG and (AVG-MIN)/AVG; where MAX is the maximum of LED channel current, MIN is the minimum LED channel current and AVG is the average of the 8 LED channel current.

(3) Refer to the detailed application circuit on page 21.

### **Typical Characteristics**

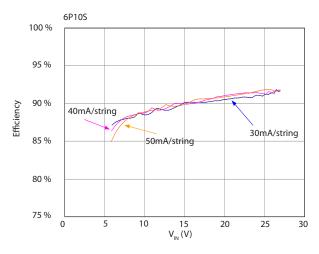

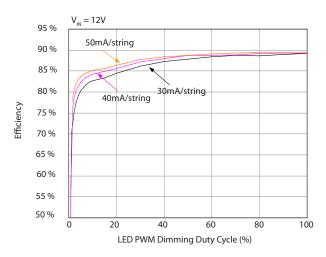

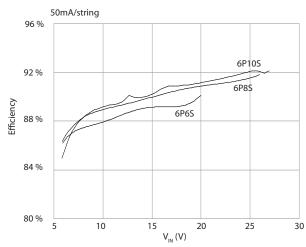

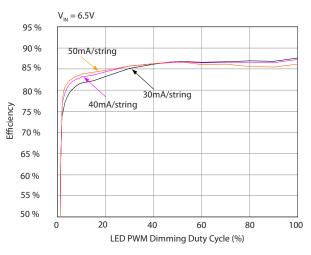

### Backlight Efficiency vs. Input Voltage

#### **Backlight Efficiency vs. LED String Current**

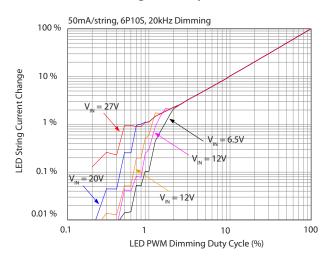

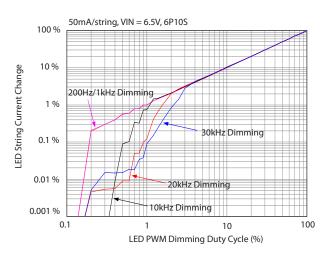

#### **PWM Dimming Linearity with Phase Shift**

### **Backlight Efficiency vs. LED String Current**

#### **PWM Dimming Linearity with Phase Shift**

## Backlight Efficiency vs. Input Voltage

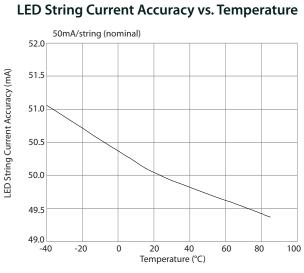

### LED String Current Matching vs. Temperature

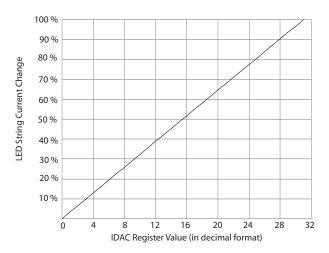

LED String Current Change vs. Analog **Dimming Control Register (IDAC) Value**

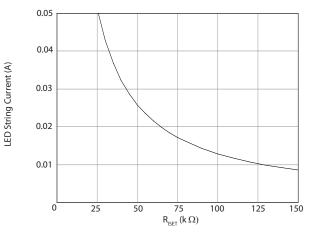

LED String Current vs. R<sub>ISET</sub>

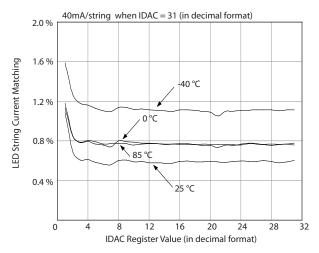

LED String Current Matching vs. Analog **Dimming Control Register (IDAC) Value**

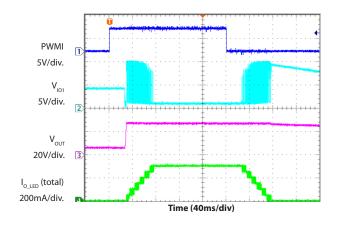

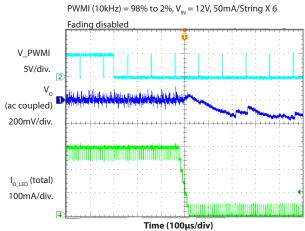

### LED Current Fade In/Out (Logarithmic)

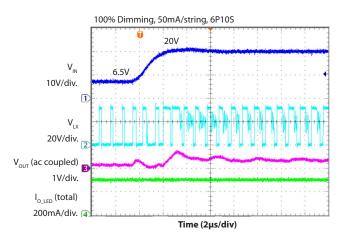

#### Line Transient Response

### LED Current Fade In/Out (Linear)

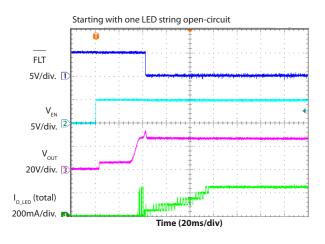

#### **LED Open Circuit Protection**

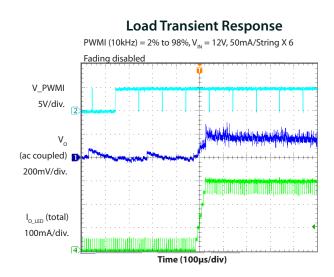

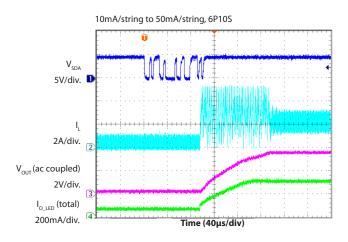

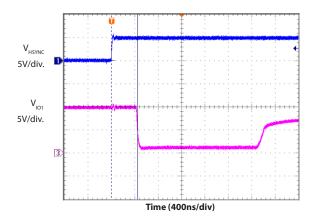

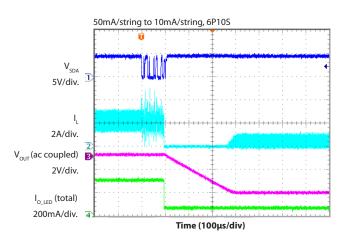

### Load Transient Response

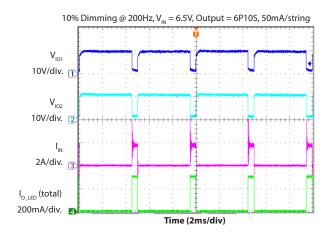

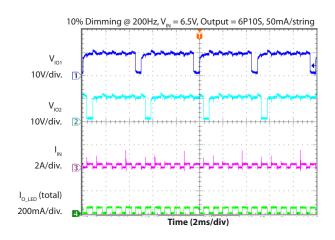

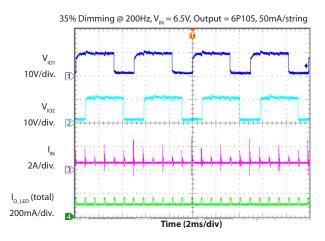

### LED Dimming Without Phase Shift

#### LED Dimming Without Phase Shift

LED Dimming Without Phase Shift

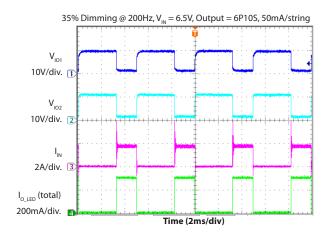

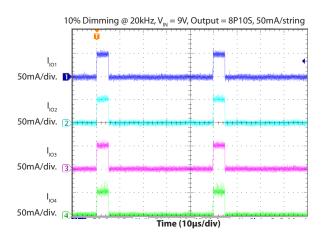

### LED Dimming With Phase Shift

### LED Dimming With Phase Shift

#### **LED Dimming With Phase Shift**

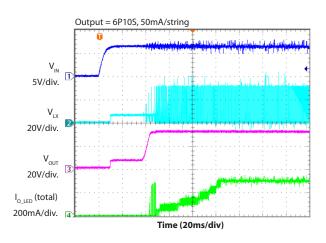

### Analog Dimming Transient via I<sup>2</sup>C

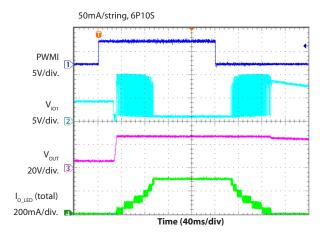

### **VIN Start Up**

### Analog Dimming Transient via I<sup>2</sup>C

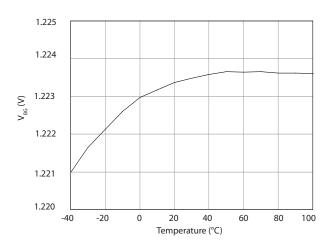

V<sub>BG</sub> vs. Temperature

# **Pin Descriptions**

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                         |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VCC      | Input bias voltage supply for the IC — accepts 4.5-5.5V inputs. Add a $1\mu$ F or larger ceramic bypass capacitor from this pin to ground.                                                                                                                                                                                                                                           |

| 2     | EN       | Logic high enable pin — pull logic high to enable the device or pull low to disable and maintain low shutdown current.                                                                                                                                                                                                                                                               |

| 3     | UVLO     | Input under-voltage lockout pin — Device is disabled when this pin is less than 1.23V (nominal). Add a resistor divider from this pin to the input voltage and AGND, respectively.                                                                                                                                                                                                   |

| 4     | SCP      | Short circuit LED protection programming pin. Shorted LED protection disables the individual channel when the current sink voltage exceeds the programmed voltage threshold. Adding resistor divider from this pin to BG and AGND programs the shorted-LED protection up to 20 X the V <sub>SCP</sub> voltage. Pulling the pin high to VCC disables the SCP feature on all channels. |

| 5     | BG       | 1.23V bandgap output pin — Connect a $1\mu$ F ceramic bypass capacitor from this pin to ground.                                                                                                                                                                                                                                                                                      |

| 6     | FSET     | Step-up (boost) frequency set pin — Connect a resistor from this pin to ground to set the frequency from 200kHz to 2.2MHz.                                                                                                                                                                                                                                                           |

| 7     | AGND     | Analog ground pin — tie this pin to analog (quiet) ground isolated from the step-up (boost) converter switching current path.                                                                                                                                                                                                                                                        |

| 8     | CPLL     | Compensation for the internal PLL — connect a compensation resistor and capacitor from this pin to ground. This pin can be left floating if not used.                                                                                                                                                                                                                                |

| 9     | SYNC     | SYNC input pin — feeding the SYNC signal (30Hz - 100kHz) to this input results in internal PLL being synchronized to the SYNC signal. This pin can be left floating if not used.                                                                                                                                                                                                     |

| 10    | SCL      | I <sup>2</sup> C serial clock input — this pin must be connected to ground if not used.                                                                                                                                                                                                                                                                                              |

| 11    | SDA      | I <sup>2</sup> C serial data input — this pin must be connected to ground if not used.                                                                                                                                                                                                                                                                                               |

| 12    | ISET     | LED current programming pin — connect an external resistor to ground to program the current in the LED strings<br>For more details please refer to LED String Peak Current Programming on page 16.                                                                                                                                                                                   |

| 13    | FLT      | Logic low fault status pin — open-drain output is latched low when fault condition is detected: Open/Short LED,<br>Shorted String, OVP or OTP. Fault status can be reset by removing fault condition(s) and toggling the EN, VCC or<br>UVLO pins. This pin can be left floating if not used.                                                                                         |

| 14    | PWMI     | PWM dimming control input                                                                                                                                                                                                                                                                                                                                                            |

| 15    | IO8      | Regulated current sink LED channel 8 — connect this pin to the cathode of the bottom LED in string 8. Connect pin to ground to disable this LED string.                                                                                                                                                                                                                              |

| 16    | 107      | Regulated current sink LED channel 7 — connect this pin to the cathode of the bottom LED in string 7.<br>Connect pin to ground to disable this LED string.                                                                                                                                                                                                                           |

| 17    | IO6      | Regulated current sink LED channel 6 — connect this pin to the cathode of the bottom LED in string 6.<br>Connect pin to ground to disable this LED string.                                                                                                                                                                                                                           |

| 18    | 105      | Regulated current sink LED channel 5 — connect this pin to the cathode of the bottom LED in string 5.<br>Connect pin to ground to disable this LED string.                                                                                                                                                                                                                           |

| 19    | 104      | Regulated current sink LED channel 4 — connect this pin to the cathode of the bottom LED in string 4. Connect pin to ground to disable this LED string.                                                                                                                                                                                                                              |

# Pin Descriptions (continued)

| Pin # | Pin Name | Pin Function                                                                                                                                                                           |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20    | IO3      | Regulated current sink LED channel 3 — connect this pin to the cathode of the bottom LED in string 3.<br>Connect pin to ground to disable this LED string.                             |

| 21    | 102      | Regulated current sink LED channel 2 — connect this pin to the cathode of the bottom LED in string 2.<br>Connect pin to ground to disable this LED string.                             |

| 22    | IO1      | Regulated current sink LED channel 1 — connect this pin to the cathode of the bottom LED in string 1.<br>Connect pin to ground to disable this LED string.                             |

| 23    | OVP      | Over-voltage feedback pin — over-voltage activated when pin exceeds 1.23V(typ). Use a resistor divider tied to the output and GND to set the OVP level.                                |

| 24    | CS       | Step-up (boost) switch current sense pin — Connect a resistor from this pin to ground for current sense - utilized in peak current mode control loop and over-current sense circuitry. |

| 25    | PGND     | Power ground — tie this pin to the power ground plane close to input and output decoupling capacitors.                                                                                 |

| 26    | DRVN     | Gate drive for the external step-up (boost) n-channel MOSFET.                                                                                                                          |

| 27    | DRVP     | Gate drive for the external p-channel MOSFET disconnect switch.                                                                                                                        |

| 28    | VIN      | Connect to the input power supply — accepts 4.5V - 27V input. Usually add 4.7µF or larger ceramic bypass capacitor from this pin to ground.                                            |

| PAD   | -        | Thermal pad for heat-sinking purposes — it is also AGND and should be connected to ground plane for proper circuit operation.                                                          |

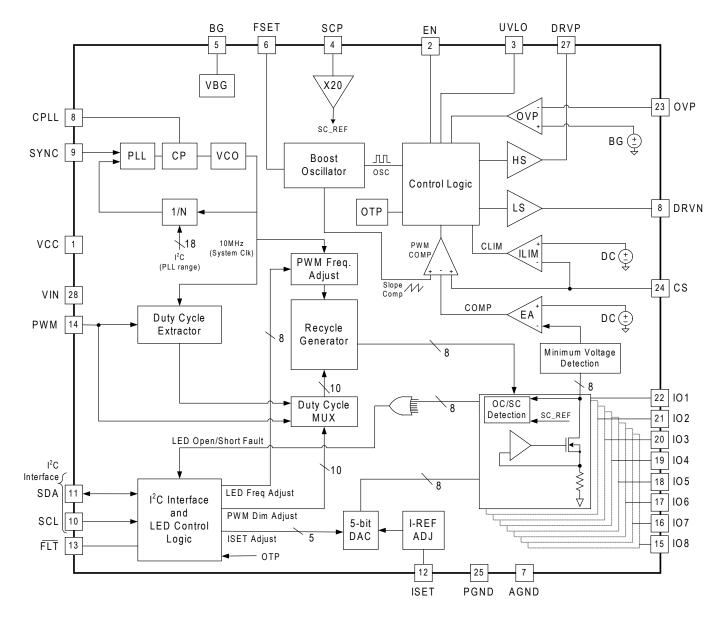

### **Block Diagram**

# SC5010H

### **Applications Information**

### **General Description**

The SC5010H contains a high frequency, current-mode, internally compensated boost controller and eight constant current sinks for driving LED strings. The LED current for all strings is programmed by an external resistor and the boost converter operates to maintain minimal required output voltage for regulating the LED current to the programmed value. Each string can support up to 50mA current. The unique control loop of the SC5010H allows fast transient response in dealing with line and load disturbances. The SC5010H operating with an external power MOSFET regulates the boost converter output voltage based on instantaneous requirement of the eight string current sources. This provides power to the entire lighting subsystem with increased efficiency and reduced component count. It supports PWM dimming frequencies from 100Hz to 30kHz and the supply current is reduced to typical 2mA when all LED strings are off.

### Start-Up

When the EN pin is pulled up high (>2.1V), the device is enabled and the UVLO and VCC pin voltages are checked. The VCC voltage has fixed under-voltage rising and falling trip points. If the VCC pin is higher than 4.2V and UVLO pin voltage is greater than 1.23V, the SC5010H goes into a startup sequence. The UVLO pin voltage can be used to program the input power source voltage VIN turn on threshold and its hysteresis (refer to the Detailed Application Circuit on page 21) as shown by the following equations:

$V_{IN_{TUMOn}}$  [V] = 1.23 X (R<sub>1</sub> + R<sub>2</sub>) / R<sub>1</sub>  $V_{IN_{Hysteresis}}$  [V] = 10<sup>-5</sup> X R<sub>2</sub>[Ω]

In the next phase, the SC5010H checks each IO pin to determine if the respective LED string is enabled. Each IO pin is pulled up with a 100 $\mu$ A current source. If any IO pin is connected to GND, it will be detected as an unused string, and will be turned off. This unused string checking procedure takes 1ms (typical). After this the SC5010H enters into a soft-start sequence.

The soft-start function helps to prevent excess inrush current through the input rail during startup. In the SC5010H, the soft-start is implemented by slowly ramping

up the reference voltage fed to the error amplifier. This closed loop start-up method allows the output voltage to ramp up without any overshoot. The duration of the soft-start in SC5010H is controlled by an internal timing circuit which is used during start-up and it's based on the boost converter switching frequency. For example, with switching frequency at 1MHz, it is typical 8ms and it becomes typical 4ms when the switching frequency is 2MHz.

If PWMI voltage goes low while the SC5010H is in soft start operation, the SC5010H switches to standby mode. Under such mode, the external power MOSFET and the LED current sources will be turned off immediately. The internal soft-start timer is turned off and the soft-start value is saved. When the PWMI voltage goes high again, the soft-start resumes from the previously saved value.

Each LED current source (IO1 to IO8) tries to regulate the LED current to its set point. The control loop will regulate the output voltage such that all the IO pin voltages are at least typical 0.9V.

#### Shutdown

When the EN pin is pulled down below 0.8V, the device enters into shutdown mode. In this mode, all the internal circuitry is turned off and the supply current is less than  $1\mu$ A(max).

In the scenario when the EN pin voltage is high, but either V<sub>IN</sub> or VCC voltage falls below their respective UVLO threshold, the SC5010H goes into a suspend mode. In this mode, all the internal circuitry except the reference and the oscillator are turned off.

#### **Thermal Shutdown (TSD)**

If the thermal shutdown temperature of 150°C is reached, the boost converter and all IO current sources are turned off. FLT pin is forced low in this situation. As temperature falls below the TSD trip point by 10°C, the SC5010H will restart following the startup sequence as described before. The FLT pin is latched and will stay low, it is reset by cycling the EN, VCC, or UVLO.

### **Boost Converter Operation**

The SC5010H includes a boost controller with programmable switching frequency. It applies current-mode control method with integrated compensation loop. The clock (see block diagram) from the oscillator sets the latch and turns on the external power MOSFET, which serves as the main power switch. The current flowing through this switch is sensed by the current sense resistor in series with the switch. The sensed switch current is summed with the slope-compensated ramp and fed into the modulating input of the PWM comparator. When the modulating ramp intersects the error amplifier output (COMP), the latch is reset and the power MOSFET is turned off. The sense resistor also sets the peak current limit of the power MOSFET, I<sub>ocp</sub> using the following equation:

$I_{_{\rm OCP}}[A] = 0.4 \ / \ R_{_{\rm CS}}[\Omega]$

The current-mode control system contains two loops. For the inner current loop, the Error Amplifier (EA) output (COMP) controls the peak inductor current. In the outer loop, the EA regulates the output voltage for driving the LED strings.

#### **Boost Converter Switching Frequency Selection**

The resistor between FSET and GND sets the boost converter switching frequency (200kHz to 2.2MHz) using the following equation:

$$f_{sw} [kHz] = 10^5 / R_{FSET} [k\Omega]$$

Higher switching frequency allows the use of low profile height inductor for space-constrained and cost-sensitive applications.

### **Over-Voltage Protection (OVP)**

SC5010H features programmable output over-voltage protection preventing damage to the IC and output capacitor in the event of LED string open-circuit. The boost converter output voltage is sensed at the OVP pin through resistor voltage divider. The OVP trip threshold (refer to detailed application circuit on page 21) can be calculated using the following equation.

Output OVP Trip Voltage  $[V] = 1.2 \text{ X} (R_{11} + R_{10}) / R_{10}$

When the OVP pin voltage exceeds 1.23V, the boost converter turns off and the FLT pin is pulled low. When the OVP pin voltage falls below the OVP threshold (falling), the boost converter restarts and the FLT pin is released. There is 10mV hysteresis between OVP pin threshold (falling) and OVP pin threshold (rising). This results in an output voltage hysteresis given by:

Output OVP Hysteresis[mV] = 10 X  $(R_{11} + R_{10}) / R_{10}$

### **LED Current Sink**

The SC5010H provides 8 current sinks and each can sink up to 50mA current. It incorporates LED string shortcircuit protection (trip level programmable and can be disabled as well), LED string open-circuit protection.

### LED String Peak Current Programming

LED string peak current (at 100% dimming) can be set by selecting resistor  $R_{ISET}$  connected between ISET and GND. The relationship between  $R_{ISET}$  resistance and single LED string peak current is calculated using the following equation:

$$I_{IED} [mA] = (1055 \text{ X } 1.23) / R_{ISET} [k\Omega]$$

The LED string current can be programmed up to 50mA.

### **Unused Strings**

The SC5010H may be operated with less than 8 strings. In this mode of operation, all unused IO pins should be connected to ground. During startup, these unused strings are detected and disabled while other active strings work normally.

### LED Short-Circuit Protection (SCP)

SC5010H features a programmable LED short protection. This allows the part to be customized based on the LED  $V_F$  mismatches between the LED strings. If one or more LEDs are detected as short-circuited, the corresponding string will be latched off. The voltages on all IO pins are monitored to check if any IO pin exceeds the SCP trip point (The IO voltage for LED string with faulty short-circuit LED(s) will be higher than other normal IO pin voltages). This LED Short-Circuit Protection (SCP) trip level (see detailed application circuit on page 21) is given by the following equation.

$V_{SCP Trip} [V] = 20 X (1.23 X R_4) / (R_4 + R_5)$

If any IO pin voltage exceeds the trip voltage, the IO current sink will be latched off and the FLT will go low. This latch can be reset by cycling UVLO, VCC or EN. Other LED strings are unaffected and continue in normal operation. This protection will be disabled if SCP is tied to VCC.

In many applications, LED strings are connected to the IO pins through a mechanical connector which cannot support an electrical connection at specific times. This connection might cause noise on the IO pins. If this noise is large enough, it may trigger false SCP mode. In this condition, a ceramic decoupling capacitors (100pF ~ 8.2nF) between IO pin to GND can help prevent the SC5010H from entering the protection mode by false trigger. This feature can be disabled by connecting SCP pin to VCC pin.

#### **LED Open-Circuit Protection**

If any LED string becomes open, the respective IO pin voltage will be pulled to GND. Consequently, the internal COMP node (output of error amplifier) is driven high, which causes the boost output voltage to increase. The output voltage will be eventually clamped to a voltage set by the OVP resistor divider. Under this condition, the faulty string is latched off and the FLT pin is pulled low. The boost voltage gets regulated to the voltage required to set all non-faulty IO pins above 0.9V (typ). The remaining strings remain in normal operation. The FLT and the fault-out LED current sink latch-off can be reset by cycling UVLO, VCC or EN.

### **LED Analog Dimming Control**

The LED current in SC5010H can be dimmed via the 5-bit analog dimming register (Register 0x02). The LED current can be adjusted in 32 steps from 0mA to the maximum value, determined by the  $R_{ISFT}$  resistor.

SC5010H has a unique DAC architecture which allows it to have excellent LED current accuracy and string-to-string matching over the entire DAC range.

Analog dimming method can be used in conjunction with PWM dimming to increase the dimming resolution. The fast loop response of SC5010H allows the LED current to transition to a new value within 100µs or so. Please refer to the graphs in the typical characteristics section.

### **LED PWM Dimming Control**

The SC5010H supports 3 modes of PWM dimming for controlling the brightness of the LEDs. It provides flexibility in setting the duty cycle and frequency of the LED PWM signal. The PWM dimming mode is set through the device control register (register address: 0x01) DCR [1:0] bits. Refer to Table 1 for more details.

#### Mode 1 — PWMI Direct Control

The PWMI input needs to be held high for normal operation. PWM dimming can be done by cycling the PWMI input at a given frequency where a "low" on the PWMI input turns off all IO current sinks and a "high" turns on all IO current sinks. The PWMI pin can be toggled by external circuitry to allow PWM dimming. In a typical application,

| PWM Dim-                                        | Register             | PWM               | LED PWM Output                                                                                               |                                                                                                            |                 |  |  |

|-------------------------------------------------|----------------------|-------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| ming Mode                                       | Settings<br>DCR[1:0] | Input<br>Source   | PWM Frequency                                                                                                | PWM Duty Cycle                                                                                             | Shift<br>Option |  |  |

| PWMI Direct<br>Control                          | 00                   | PWMI Pin<br>Input | Same as the PWMI input<br>(Range 100 Hz to 30kHz)                                                            | Same as the PWMI input                                                                                     | NO              |  |  |

| PWMI Indirect<br>Control<br>(Default<br>Option) | 01                   | PWMI Pin<br>Input | Set via the FREQ Register<br>(0x05) and FAST_FREQ bit<br>10kHz (max): FAST_FREQ=0<br>20kHz(max): FAST_FREQ=1 | Same as the duty cycle of the PWMI input<br>10 bits @ 10kHz output<br>9 bits @ 20kHz output                | YES             |  |  |

| l²C<br>Control                                  | 11                   | l²C<br>Control    | Set via the FREQ Register<br>(0x05) and FAST_FREQ bit<br>10kHz (max): FAST_FREQ=0<br>20kHz(max): FAST_FREQ=1 | Set via the Duty Cycle Control<br>Register (0x03, 0x04)<br>10 bits @ 10kHz output<br>9 bits @ 20kHz output | YES             |  |  |

### Table 1 — LED PWM Dimming Control Methods

a micro-controller sets a register or counter that varies the pulse width on a GPIO pin. The SC5010H allows dimming over a wide frequency range (100Hz-30kHz) in order to allow compatibility with a wide range of devices. This includes the newest dimming strategies that avoid the audio band by using high frequency PWM dimming. In this manner, a wide range of illumination can be generated while keeping the instantaneous LED current at its peak value for high efficiency and color temperature. The SC5010H provides 1000:1 dimming range at 1kHz PWM frequency. The LED current sinks turn on /off very rapidly (<25ns, typical). This allows wide dimming ratio. An additional advantage of PWM dimming comes to customers who prefer to avoid in-rush currents when filling the boost output capacitor. Apply the PWMI signal to the device at 10% duty for a millisecond or two, and in-rush current is reduced. This dimming time will vary based on the number of LEDs and the size of the output capacitor. This can be easily determined during testing and programmed into the micro-controller firmware.

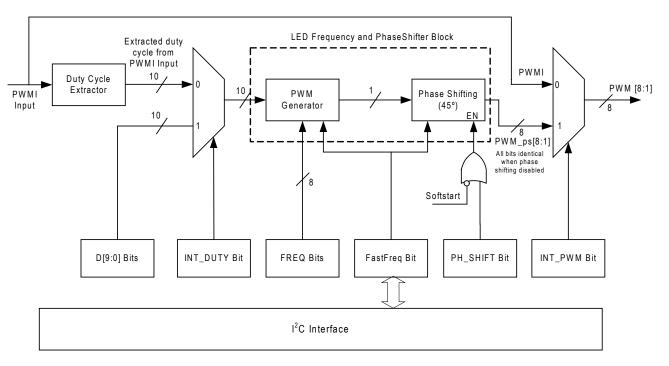

#### Mode 2 — Indirect Control

This is the default mode for LED PWM dimming in SC5010H. In this mode, the input signal applied on PWMI pin is passed through a duty cycle extractor block. The extractor measures the duty cycle of the PWMI input, and depending on the value of FAST\_FREQ, the duty cycle is converted to a 9bit value (FAST\_FREQ = 1) or a 10-bit value (FAST\_FREQ = 0). This value is then passed to the PWM generator block as shown in the Figure 1 below.

The LED PWM dimming frequency is set via the FREQ register (address 0x05) and the FAST\_FREQ bit.

With FAST\_FREQ = 0, low dimming frequency option is selected and the PWM dimming frequency will be according to the following equation.

PWM Dimming Frequency =  $\frac{10MHz}{1024 \times [FREQ[7:0]+1]}$ = 10kHz(max)

With FAST\_FREQ = 1, high dimming frequency option is selected and the PWM dimming frequency is shown by the following equation.

PWM Dimming Frequency =

$$\frac{10MHz}{512 \times [FREQ[7:0]+1]}$$

$$= 20kHz(max)$$

The default option is FAST\_FREQ = 1. This gives 9-bit duty cycle resolution and up to 20kHz dimming frequency

Figure 1— LED PWM Dimming Control

range. The PWMI input is usually generated by the system graphics processor. This mode allows the user to set the PWM output dimming frequency independent of the PWMI input.

If the PWMI signal has jitter, then SC5010H provides an option to filter it out. Hysteresis is also provided by selecting the WND[1:0] bits in the DCR register (address 0x01). WND[1:0] bits set the window comparator such that if a change in the duty cycle is detected which is smaller than the set window, then it is ignored.

#### Mode 3 — I<sup>2</sup>C Control

In this mode (refer to Figure 1 on page 18), both the output LED dimming duty cycle and the dimming frequency are set via the internal registers. PWMI pin should be connected to ground in this mode. In this mode, the LED dimming duty cycle is set via the duty cycle registers (address 0x03, 0x04); and the dimming frequency is set via the FREQ register (address 0x05) and the FAST\_FREQ bit.

With FAST\_FREQ = 0, the LED duty cycle can achieve 10-bit resolution, D[9:0], which is combined by two portions: (1) MSB portion - register address 0x03 [1:0] and (2) LSB portion - register address 0x04 [7:0] as shown below.

| 0>      | (03[1:0]                                | 0x04[7  | :0]     |         |         |         |         |         |         |  |

|---------|-----------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|--|

| 0x03[1] | 0x03[0]                                 | 0x04[7] | 0x04[6] | 0x04[5] | 0x04[4] | 0x04[3] | 0x04[2] | 0x04[1] | 0x04[0] |  |

|         | ↓ · · · · · · · · · · · · · · · · · · · |         |         |         |         |         |         |         |         |  |

| D[9]    | D[8]                                    | D[7]    | D[6]    | D[5]    | D[4]    | D[3]    | D[2]    | D[1]    | D[0]    |  |

And the dimming duty cycle with FAST\_FREQ = 0 can be calculated as:

LED Dimming Duty Cycle =  $\{D[9:0]_{decimal} + 1\}/2^{10}$

With FAST\_FREQ = 1, the LED duty cycle can achieve 9-bit resolution, D[9:1], which is combined by two portions: (1) MSB portion - register address 0x03 [1:0] and (2) LSB portion - register address 0x04 [7:1] as shown below.

| 0×      | 03[1:0] | 0x04[7  | :1]     |         |         |         |         |         | Not use |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x03[1] | 0x03[0] | 0x04[7] | 0x04[6] | 0x04[5] | 0x04[4] | 0x04[3] | 0x04[2] | 0x04[1] | 0x04[0] |

|         | ,       |         |         |         | +       |         |         |         |         |

| D[9]    | D[8]    | D[7]    | D[6]    | D[5]    | D[4]    | D[3]    | D[2]    | D[1]    | D[0]    |

|         |         |         |         |         |         |         |         |         |         |

And the dimming duty cycle with FAST\_FREQ = 1 can be calculated as:

LED Dimming Duty Cycle =  $\{D[9:1]_{decimal} + 1\}/2^9$

In both cases mentioned above, duty cycle is fixed to be 0 when D[9:0] is set as 0x00.

As for the PWM dimming frequency, it is controlled the same way as used in "Indirect Control" introduced in the previous page.

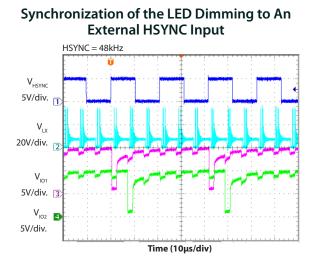

#### **Phase-Shifted PWM Dimming**

The SC5010H provides an option for the phase shifted LED PWM dimming. This option is available in both PWMI indirect control and I<sup>2</sup>C control. Phase-shift option is set by the PH\_SHIFT bit in the Device Control Register (register address 0x01). This option delays the turn-on of the LED strings based on the number of the strings in operation (the number of the strings in operation is determined during the start-up). The delay time can be calculated by the following equation:

$$T_{\phi-phase} = \frac{\frac{1}{f_{PWM}}}{N}$$

N = number of strings in operation  $f_{PWM} =$  LED PWM dimming frequency

Phase-shift mode is disabled during soft-start, this allows the output to ramp up to the correct voltage in a controlled fashion.

Phase-shifting reduces the peak input current, decreases EMI and improves the dimming linearity. The figures in the Typical Characteristic Section shows the reduction in the input current with phase shift feature enabled compared to the non-phase shifted mode of operation.

#### **Backlight Fade-in and Fade-out Options**

The SC5010H features an option for fade-in and fade-out brightness control, which allows smooth transition from one brightness level to another.

Registers associated with this fading functions are shown in this section.

1. Fade Option (register address 0x09) — sets fade

enable options, fade time, fade type.

2. Fade Rate (register address 0x0A) — sets fade step size option.

Fade option register allows user to select fading, choose between linear or logarithmic fading, and to set up the

fading time. The default setting is fading enabled with logarithmic mode. The fading time is determined by the LED PWM dimming frequency. Fade setting is shown in the table on page 21.

| Turna of                                     | User                                 |                                                                                  | Action                                                                      | on Fault                            | Recov                                                                                                      | ery                                        |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Type of<br>Fault                             | Disable?                             | Fault Criteria                                                                   | Device                                                                      | FLT pin (latching<br>/ non-latching | Condition(s)                                                                                               | FLT pin                                    |

| Input<br>Under-voltage                       | No                                   | V <sub>IN</sub> < 1 + R <sub>2</sub> /R <sub>1</sub> )<br>x 1.23 (rising)        | No Startup                                                                  | Not Active                          | V <sub>UVLO</sub> > 1.23V<br>(rising)                                                                      | High                                       |

| at VIN<br>(UVLO)                             | No                                   | $V_{IN} < (1 + R_2/R_1) \times 1.23V - I_{UVLO} \\ \times R_1 \text{ (falling)}$ | Shutdown                                                                    | Not active                          | V <sub>UVLO</sub> > 1.23V<br>(rising)                                                                      | High                                       |

| lnput<br>Under-volage                        | No                                   | VCC < 4.2V<br>(rising)                                                           | No Startup                                                                  | Not active                          | VCC > 4.2V<br>(rising)                                                                                     | High                                       |

| at VCC<br>(UVLO)                             | No                                   | VCC < 4.0V<br>(falling)                                                          | Shutdown                                                                    | Not active                          | VCC > 4.2V<br>(rising)                                                                                     | High                                       |

| Over-voltage<br>Protection No<br>(OVP)       |                                      | V <sub>ovp</sub> > 1.23V<br>(rising)                                             | Regulate to OVP<br>threshold:<br>I <sub>O(n)</sub> = "on"                   | Low<br>(non-latching)               | V <sub>ovp</sub> < 1.22V<br>(falling)                                                                      | High on re-<br>moval of fault<br>condition |

| Over-current<br>Protection<br>(OCP)          | Protection No V <sub>cs</sub> > 0.4V |                                                                                  | Limit Q1 FET drain<br>current < 0.4V/R3<br>(typ)                            | High                                | V <sub>cs</sub> > 0.4V                                                                                     | High                                       |

| Shorted                                      | Yes, tie<br>SCP to                   | $V_{IO(n)} > 20 \text{ x } V_{SCP}$                                              | Device on:<br>I <sub>O(n)</sub> = "off"<br>Other I <sub>O(AII)</sub> = "on" | Low<br>(latching)                   | Replace shorted<br>LED(s) and Toggle<br>EN, VCC or UVLO                                                    | High                                       |

| LED(s)                                       | VCC                                  | $V_{IO(AII)} > 20 \times V_{SCP}$                                                | Device latch-off;<br>I <sub>O(All)</sub> = "off"                            | Low<br>(latching)                   | Replace shorted<br>LED(s) and Toggle<br>EN, VCC or UVLO                                                    | High                                       |

| Open                                         | No                                   | V <sub>IO(n)</sub> < 0.1V<br>and OVP event                                       | Device on:<br>I <sub>O(n)</sub> = "off"<br>Other I <sub>O(All)</sub> = "on" | Low<br>(latching)                   | Replace open<br>LED(s) and Toggle<br>EN, VCC or UVLO                                                       | High                                       |

| LED(s)                                       | NO                                   | $V_{IO(AII)} < 0.1V$<br>and OVP event                                            | Device latch-off;<br>I <sub>O(All)</sub> = "off"                            | Low<br>(latching)                   | Replace open<br>LED(s) and Toggle<br>EN, VCC or UVLO                                                       | High                                       |

| Over-Tempera-<br>ture Protection No<br>(OTP) |                                      | TJ > 150°C (typ)                                                                 | Device off;<br>I <sub>O(All)</sub> = "off"                                  | Low<br>(latching)                   | Satisfy T <sub>HYS</sub> > 10°C;<br>Device on;<br>I <sub>O(All)</sub> = "on";<br>Toggle EN, VCC or<br>UVLO | High                                       |

### Table 2 — Fault Protection Descriptions

Note: Refer to the application circuit example on page 21.

An example for calculating the fading time is shown in this section. Assuming LED PWM dimming frequency is 10kHz, then 10 bits are assigned for 1024 duty cycle settings.

| Duty<br>Cycle<br>Zone | Duty Cycle<br>Range | Step<br>Increment | Step<br>Interval | Total Steps<br>within the<br>Range |

|-----------------------|---------------------|-------------------|------------------|------------------------------------|

| 1                     | 0 to 511            | 1                 | 2                | 512                                |

| 2                     | 512 to 767          | 1                 | 1                | 256                                |

| 3                     | 768 to 1024         | 2                 | 1                | 256                                |

Time required to go from 10% (102/1024) to 90% (922/1024) duty cycle can be calculated using the following equation:

$T_{PWM} = 100 \ \mu s$  (with 10kHz dimming frequency)

Cycle in Zone #1 = (511 - Starting Duty Cycle) x [(Zone #1 Step Interval) / (Zone #1 Step Increment)]

Cycle in Zone #2 = Total Stpes in Zone #2 x [(Zone #2 Step Interval) / (Zone #2 Step Increment)]

Cycle in Zone #3 = (End Duty Cycle - 768) x [(Zone #3 Step Interval) / (Zone #3 Step Increment)]

In this case, the total cycle will be:

Total cycle =  $2 \times (511-102) + 1 \times 256 + 0.5 \times (922 - 768)$ = 1151 Total Fading Time = Total Cycle x T<sub>PWM</sub> = 1151 x 100 µs = 115.1ms

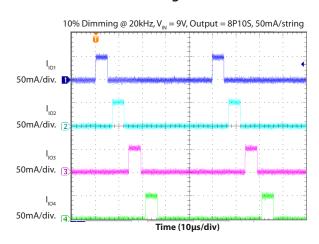

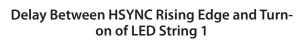

#### **Optional Synchronization to SYNC Input**

The SC5010H provides an option to synchronize the LED dimming to an external clock source connected to the SYNC pin. In certain applications, it may be beneficial to synchronize the LED drive signal to the LCD screen refresh signals such as VSYNC or HSYNC. This helps reduce or eliminate some of the problems associated with using LED backlights, such as flickering, shimmering, etc.

The phase lock loop available on the SC5010H can be programmed via I<sup>2</sup>C to synchronize the internal 10MHz oscillator to the SYNC input. Figures on page 11 show synchronization of SC5010H to a 48kHz HSYNC signal applied on SYNC pin. The turn-on of the LED string IO1 (falling edge of V<sub>IO1</sub>) is synchronized to the rising edge of the HSYNC input. The turn-on of rest of the strings will be delayed based on the phase shifting algorithm. Another figure shows the delay (~500ns) between HSYNC rising edge and turn-on of the LED string 1 (IO1).

#### **Input Disconnect**

The SC5010H incorporates a high voltage (up to 27V) p-MOSFET gate driver which can be used for controlling an external p-channel MOSFET. The external p-channel MOSFET provides load disconnection during shutdown or fault mode. It also provides input inrush current limiting during start-up. During shutdown, the DRVP pin is pulled up to VIN voltage via an internal  $1M\Omega$  resistor. At startup, the boost converter is held off and the DRVP pin is pulled low via an internal  $20\mu A$  (typ) current source. When the DRVP pin is pulled lower than the threshold voltage of the

Figure 3 — SEPIC Configuration

external p-channel MOSFET, the input current starts charging up the output capacitor to the input voltage. After that, the boost converter enters into soft start mode.

### **Fault Protection**

SC5010H provides fault detection for low supply voltage, LED related faults, missing V<sub>SYNC</sub> input, boost converter over-voltage and thermal shutdown. The open drain output pin ( $\overline{FLT}$ ) indicates a system fault. The nature of the fault can be read from the fault status resistor (register address: 0x00) via I<sup>2</sup>C interface. Refer to Table 2 for a description of the Fault Protection Modes.

### **Other Possible Configurations**

Depending on different application requirement, the SC5010H can also be easily configured to other topology such as SEPIC (Single-Ended Primary-Inductor Converter) configuration as shown in Figure 3.

#### **High Output Voltage Configuration**

If high output voltage application is required, an additional external cascode MOSFET can be added on each IO pin to meet such requirement, please refer to figure 4 for reference.

In this case, the upper limit on the output voltage is mainly determined by the rating of the external MOSFET, heat dissipation, etc.

Figure 4 — Cascode Configuration (for high output voltage application)

### **PCB Layout Considerations**

The placements of the power components outside the SC5010H should follow the layout guidelines of a general boost converter. The Detailed Application Circuit is used as an example.

- 1. Capacitor (C2) should be placed as close as possible to the VCC and AGND to achieve the best performance.

- 2. Capacitor (C1) is the input power filtering capacitor for the boost, it needs to be tied to PGND.

- 3. The converter power train inductor (L1) is the boost converter input inductor. Use wide and short traces connecting these components.

- 4. The output rectifying diode (D1) uses a Schottky diode for fast reverse recovery. Transistor (Q1) is the external switch. Resistor (R9) is the switch current sensing resistor. To minimize switching noise for the boost converter, the output capacitor (C6) should be placed such that the loop formed by Q1, D1, C6 and R9, is minimized. The output of the boost converter is used to power up the LEDs. Use wide and short trace connecting Pin DRVN and the gate of Q1. The GNDs for R9 and C6 should be PGND. These components should be close to the SC5010H.

- 5. Resistor (R8) is the output current adjusting resistor for IO1 through IO8 and should return to AGND. Place it next to the IC.

- 6. Resistor (R6) is the switching frequency adjusting resistor and should return to AGND. Place it next to the IC.

- 7. The decoupling capacitor (C3) for Pin BG should return to AGND. Place it next to the IC.

- 8. Resistors (R4, R5) form a divider to set the SCP level, R4 should return to AGND. Place it next to the IC.

- 9. Resistors (R2, R1) form a divider to set the UVLO level for  $V_{IN}$ . R1 should return to AGND. Place it next to the IC.

- 10. R11 and R10 form a divider to set the OVP level for VOUT, R10 should return to AGND. Place it next to the IC.

- 11. All the traces for components with AGND connection should avoid being routed close to the noisy areas.

- 12. An exposed pad is located at the bottom of the SC5010H for heat dissipation. A copper area underneath the pad is used for better heat dissipation. On the bottom layer of the PCB another copper area, connected through vias to the top layer, is used for

better thermal performance. The pad at the bottom of the SC5010H should be connected to AGND. AGND should be connected to PGND at single point for better noise immunity.

### **Components Selection**

#### **Inductor Selection**

The choice of the inductor affects the converter's steady state operation, transient response, and its loop stability. Special attention needs to be paid to three specifications of the inductor, its value, its DC resistance and saturation current. The inductor's inductance value also determines the inductor ripple current. The boost converter will operate in either CCM (Continuous Conduction Mode) or DCM (Discontinuous Conduction Mode) depending on its operating conditions. The inductor DC current or input current can be calculated using the following equation.

$$I_{IN} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta}$$

$$I_{IN} - Input \text{ current; } I_{OUT} - Output \text{ current; }$$

$$V_{OUT} - Boost \text{ output voltage; }$$

$$V_{IN} - Input \text{ voltage; }$$

$$n - Efficiency \text{ of the boost converter.}$$

Then the duty ratio under CCM is shown by the following equation.

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{IN}} + \mathsf{V}_{\mathsf{D}}}{\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{D}}}$$

$V_{_{D}}$  – Forward conduction drop of output rectifying diode

When the boost converter runs under DCM ( L <  $L_{boundary}$ ), it takes the advantages of small inductance and quick transient response; where as if the boost converter works under CCM (L >  $L_{boundary}$ ), normally the converter has higher efficiency.

When selecting an inductor, another factor to consider is the peak-to-peak inductor current ripple, which is given by the following equation.

### **Components Selection (continued)**

$$\Delta I_{L} = \frac{V_{IN} \times D}{f_{SW} \times L}$$

Usually this peak-to-peak inductor current ripple can be chosen between 30% to 50% of the maximum input DC current. This gives the best compromise between the inductor size and converter efficiency. The peak inductor current can be calculated using the following equation.

$$I_{L-peak} = I_{IN} + \frac{V_{IN} xD}{2x f_{SW} xL}$$

For most applications, an inductor with value of 2.2µH to 22µH should be acceptable, (refer to the Typical Application Circuit on page 21). The inductor peak current must be less than its saturation rating. When the inductor current is close to the saturation level, its inductance can decrease 20% to 35% from the 0A value depending on the vendor specifications. Using a small value inductor forces the converter in DCM, in which case the inductor current ramps down to zero before the end of each switching cycle. It reduces the boost converter's maximum output current and produces larger input voltage ripple. The DCR of the inductor plays a significant role for the total system efficiency and usually there is a trade-off between the DCR and size of the inductor. Table 3 lists some recommended inductors and their vendors.

Table 3 — Recommended Inductors

| Inductor               | Web site          |

|------------------------|-------------------|

| XFL4020, 2.2μΗ ~ 4.7μΗ | www.coilcraft.com |

### **Output Capacitor Selection**

The next design task is targeting the proper amount of output ripple voltage due to the constant-current LED loads. Usually X5R or X7R ceramic capacitor is recommended. The ceramic capacitor minimum capacitance needed for a given ripple can be estimated using the following equation.

$$C_{OUT} = \frac{(V_{OUT} - V_{IN}) \times I_{OUT}}{V_{OUT} \times f_{SW} \times V_{RIPPLE}}$$

V<sub>RIPPLE</sub> – Peak to peak output ripple.

The ripple voltage should be less than 200mV (pk-pk) to ensure good LED current sink regulation. For example, a typical application where 40mA/channel current is needed, the total output current for 8 channels will be 320mA, and typically a configuration of  $3x 4.7\mu$ F output capacitors is recommended.

During load transient, the output capacitor supplies or absorbs additional current before the inductor current reaches its steady state value. Larger capacitance helps with the overshoot/undershoots during load transient and loop stability.

#### **Input Capacitor Selection**

X5R or X7R ceramic capacitor is recommended for input bypass capacitor. A 1 $\mu$ F capacitor is sufficient for the VCC input. Bypass the VIN input with a 4.7 $\mu$ F or larger ceramic capacitor.

#### **Output Freewheeling Diode Selection**

Schottky diodes are the ideal choice for SC5010H due to their low forward voltage drop and fast switching speed. Table 4 shows several different Schottky diodes that work properly with the SC5010H. Verify that the diode has a voltage rating greater than the maximum possible output voltage. The diode conducts current only when the power switch is turned off. The diode must be rated to handle the average output current. A diode rated for 1A average current will be sufficient for most designs.

#### Table 4 — Recommended Rectifier Diodes

| Rectifier Diode | Vendor Web site |

|-----------------|-----------------|

| DFLS140         | www.diodes.com  |

#### **External Power MOSFET Selection**

The boost converter in SC5010H uses an external power MOSFET to regulate the output voltage and output power to drive LED loads. This boost switching structure has an advantage in that the SC5010H is not directly exposed to high voltage, only the external power MOSFET, freewheeling diode and the inductor will be exposed to the output voltage. The external power MOSFET should be selected with its voltage rating higher than the output voltage by minimum 30%. The current rating should be enough to handle the inductor peak current. Low R<sub>DS(ON)</sub> MOSFETs are preferred for achieving better efficiency.

### **Components Selection (continued)**

The GD (gate driver) on SC5010H provides 1A (peak) current driving capability which is suitable for most MOSFETs for high frequency operation. The average current required to drive the MOSFET is given by the following equation.

$$I_{GATE} = Q_{G} \times f_{SW}$$

$Q_{_{\rm G}}$  — Gate charge

The  $R_{DS(ON)}$  and its RMS current  $I_{S_{RMS}}$  of the power MOSFET will generate the conduction loss using the following equation.

$\mathsf{P}_{\mathsf{COND}} = \mathsf{I}_{\mathsf{S}_{\mathsf{RMS}}}^{2} \mathsf{x} \mathsf{R}_{\mathsf{DS(on)}}$

The MOSFET's switch loss can be calculated using the following equation.

$$P_{SW} = \frac{1}{2} \times V_{IN} \times I_{L PEAK} \times f_{SW} \times (T_{ON} + T_{OFF})$$

Where  $\rm T_{_{ON}}$  and  $\rm T_{_{OFF}}$  are the MOSFET's on and off time and they can be estimated by the following equations.

$$T_{ON} = t_r + \frac{Q_{gd}}{(5 - V_{plateau}) / (5 + R_g)}$$

$$T_{OFF} = t_f + \frac{Q_{gd}}{V_{plateau}/(5+R_g)}$$

Where  $t_r$ ,  $t_f$ ,  $Q_{gd}$  and  $V_{plateau}$  can usually be found from datasheet of the selected MOSFET.  $R_g$  is the resistance of the optional resistor connected in series on the gate of the MOSFET.

#### **Current Sensing Resistor Selection**

The switch current is sensed via the current sensing resistor,  $R_{SNS}$ . The sensed voltage at this pin is used to set the peak switch current limit and also used for steady state regulation of the inductor current. The current limit comparator has a trip voltage of 0.4V.  $R_{SNS}$  value is chosen to set the peak inductor and switch current using the following equation.

The power dissipation in  $\mathrm{R}_{_{\mathrm{SNS}}}$  can be calculated using the following equations.

$$P_{R_{SNS}} = I_{RMS}^{2} \times R_{SNS}$$

$$I_{RMS} = D \times [I_{O}/(1-D)]^{2}$$

$$I_{O} = Output DC Current, D = Duty Cycle$$

For the typical application circuit shown in the Detailed Application Circuit (page 21), the power dissipation on the sensing resistor is shown by the following equations.

Assuming  $V_{IN}$  (Min) = 6.5V and  $V_{OUT}$  = 30V, thus D = 78.3%,  $I_{O}$  = 50mA/string x 6 string = 300 (mA) = 0.3 (A)  $I_{RMS}$  = D x  $[I_{O}/(1-D)]^{2}$  = 78.3% x  $[0.3A/(1-78.3\%)]^{2}$ = 1.5 (A)  $P_{R,SNS}$  = 1.5<sup>2</sup> x 0.1 = 0.22 (W)

For this example, a 0.1  $\Omega$  1% thick-film chip resistor rated at 0.25W or higher power can be used.

#### **PLL Filter Component Selection**

The Detailed Application Circuit on page 21 shows the optimal R/C filter components for the PLL compensation. These are optimized for internal 1MHz switching frequency. Please contact Semtech application group if a different switching frequency is selected.

#### **Isolation MOSFET Selection**

The external p-channel MOSFET provides load disconnection during shutdown or fault condition. Select a MOSFET with low  $R_{DS(on)}$  to limit the power loss.

In order to implement inrush current limiting, a 10nF capacitor is connected between the gate and source terminal of the MOSFET.

If isolation is not required, then the DRVP pin can be left floating. Connect the VIN directly to the system input supply or, to the  $V_{cc}$  (5V) supply. Do not leave the VIN pin floating.

$$I_{SW(Peak)} = 0.4/R_{SNS}$$

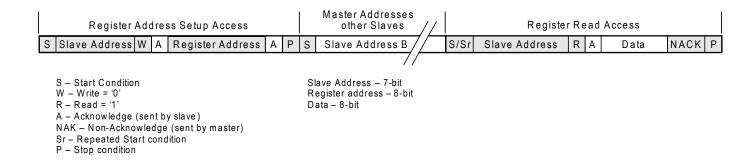

### Serial Interface

#### The I<sup>2</sup>C General Specification

The SC5010H is a read-write slave-mode I<sup>2</sup>C device and complies with the Philips I<sup>2</sup>C standard Version 2.1, dated January 2000. The SC5010H has 11 user-accessible internal 8-bit registers. The I<sup>2</sup>C interface has been designed for program flexibility, supporting direct format for write operation. Read operations are supported on both combined format and stop separated format. While there is no auto increment/decrement capability in the SC5010H I<sup>2</sup>C logic, a tight software loop can be designed to randomly access the next register independent of which register you begin accessing. The start and stop commands frame the data-packet and the repeat start condition is allowed if necessary.

#### Limitations to the I<sup>2</sup>C Specifications

The SC5010H only recognizes seven bit addressing. This means that ten bit addressing and CBUS communication are not compatible. The device can operate in either standard mode (100kbit/s) or fast mode (400kbit/s).

#### **Slave Address Assignment**

The seven bit slave address is 0101 111x. The eighth bit is the data direction bit. 0x5F is used for a write operation, and 0x5E is used for a read operation.

#### **Supported Formats**

The supported formats are described in the following subsections.

#### (1) Direct Format — Write

The simplest format for an I<sup>2</sup>C write is direct format. After the start condition [S], the slave address is sent, followed by an eighth bit indicating a write. The SC5010H I<sup>2</sup>C then acknowledges that it is being addressed, and the master responds with an 8 bit data byte consisting of the register address. The slave acknowledges and the master sends the appropriate 8 bit data byte. Once again, the slave acknowledges and the master terminates the transfer with the stop condition [P].