**OPT8320**

SBAS748 - DECEMBER 2015

# **OPT8320 3D Time-of-Flight Sensor**

#### **Features**

- Imaging Array:

- 80 × 60 Array

- 1/6" Sensor Format

- Pixel Pitch: 30 µm

- Frame Rate: Scalable Up to 1000-FPS Depth Output Rate with an Internal Raw Rate of 4000 FPS

- **Optical Properties:**

- Responsivity: 0.35 A/W at 850 nm

- Demodulation Contrast: 70% at 50 MHz

- Demodulation Frequency: 10 MHz to 100 MHz

- Output Interface:

- Digital Video Port (DVP): 8 Data Lanes, HD and VD Pins, and Clock

- Synchronous Serial Interface (SSI): 1 Data Lane, Clock, and Chip Select

- **Timing Generator:**

- Sensor Addressing Engine

- Modulation Control

- De-Aliasing

- Master, Slave Sync Operation

- High Dynamic Range Operation

- Depth Engine:

- Pixel Binning

- De-Aliasing

- Histogram

- Calibration

- Power Supply:

- 3.3-V I/O, Analog

- 1.8-V Analog, Digital, I/O

- 1.8-V Demodulation (Typical)

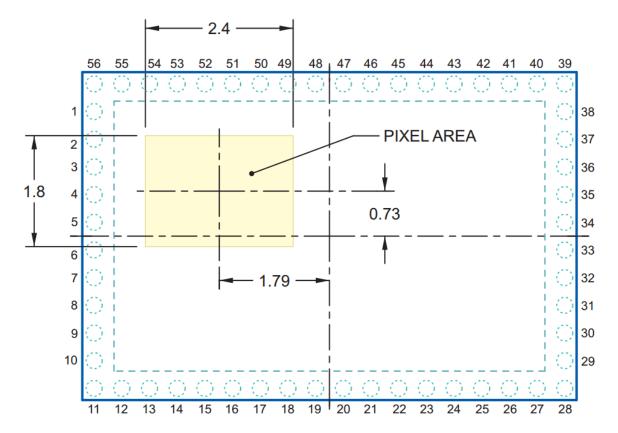

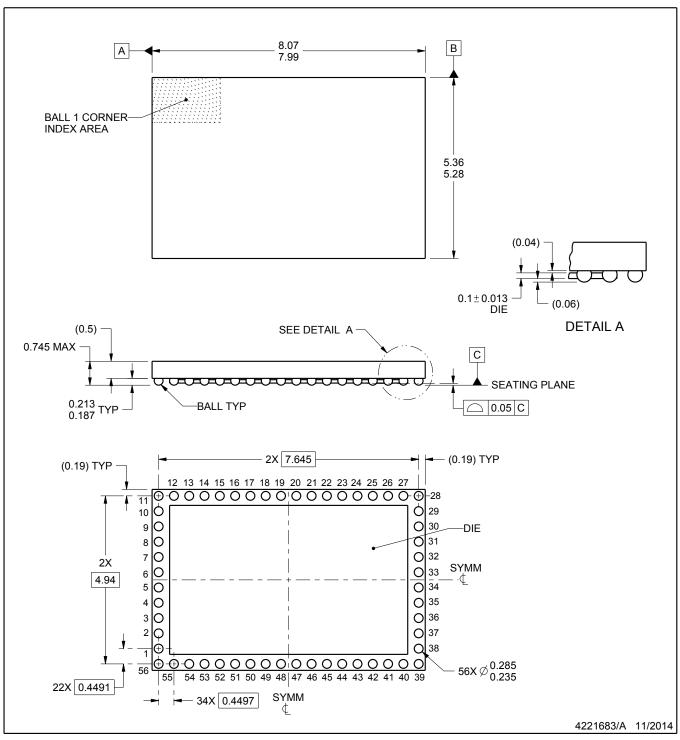

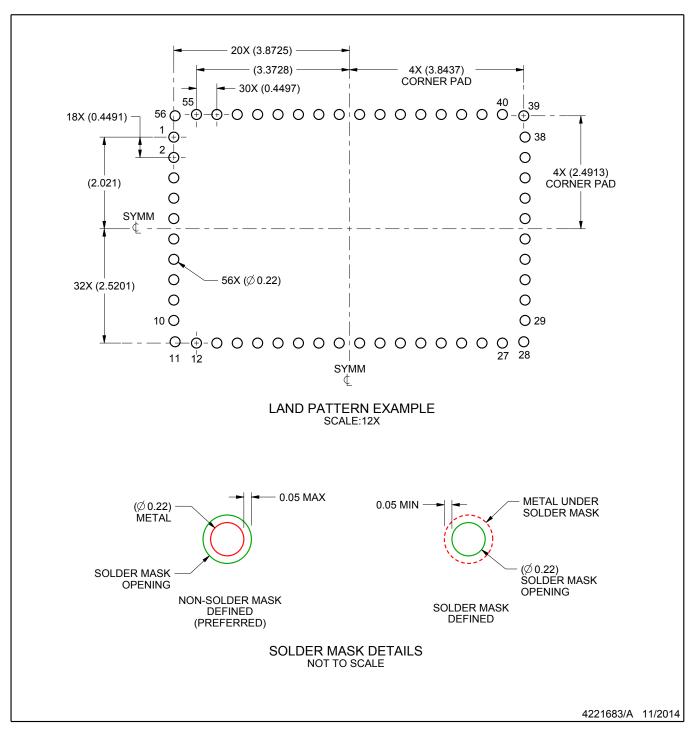

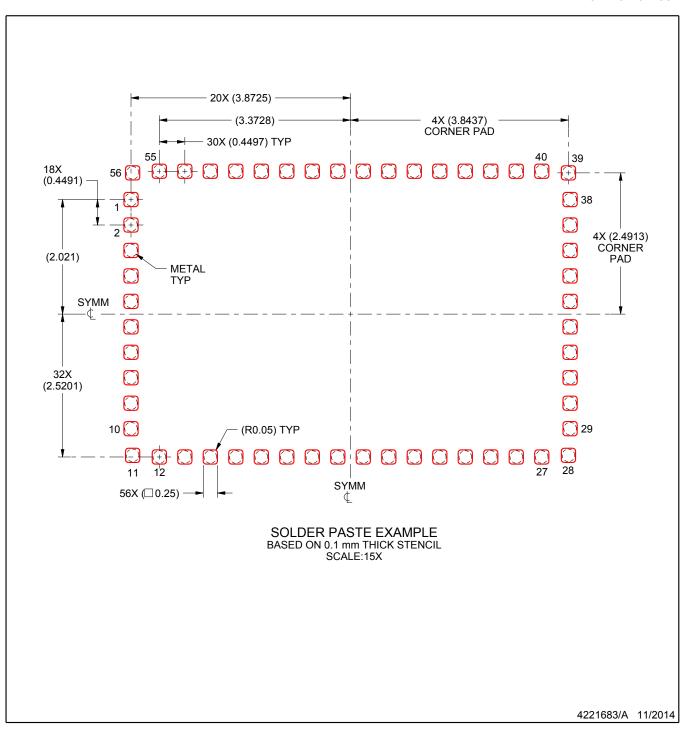

- Optimized Optical Package (COG-56):

- 8.03 mm × 5.32 mm × 0.745 mm

- Integrated Optical Band-Pass Filter (830 nm to 867 nm)

- Optical Fiducials for Easy Alignment

- Built-In Illumination Driver for Low-Power **Applications**

- Operating Temperature: 0°C to 70°C

# 2 Applications

- Depth Sensing:

- Location and Proximity Sensing

- 3D Scanning

- 3D Machine Vision

- Security and Surveillance

- **Gesture Controls**

- Augmented and Virtual Reality

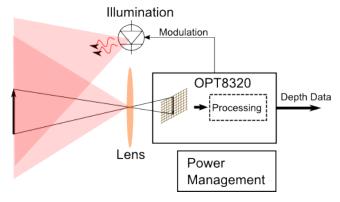

# 3 Description

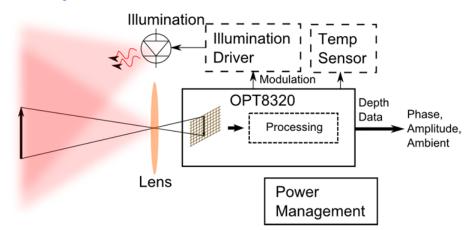

The OPT8320 time-of-flight (ToF) sensor is part of the TI 3D ToF image sensor family. The device is a high-performance, highly-integrated, complete system-on-chip (SoC) for array depth sensing, consisting of a versatile timing generator (TG), an optimally designed analog-to-digital converter (ADC), a depth engine, and an illumination driver.

The programmability of the built-in TG offers the flexibility to optimize for various depth-sensing performance metrics [such as power, motion robustness, signal-to-noise ratio (SNR), and ambient cancellation]. The built-in depth engine computes the depth data from the digitized sensor data. In addition to the phase data, the depth engine provides auxiliary information consisting of amplitude, ambient, and flags for each pixel and the full-array statistical information in the form of a histogram.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)                 |

|-------------|----------|---------------------------------|

| OPT8320     | COG (56) | 8.03 mm x 5.32 mm x<br>0.745 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

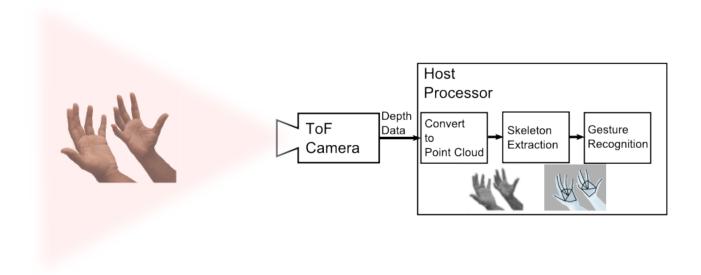

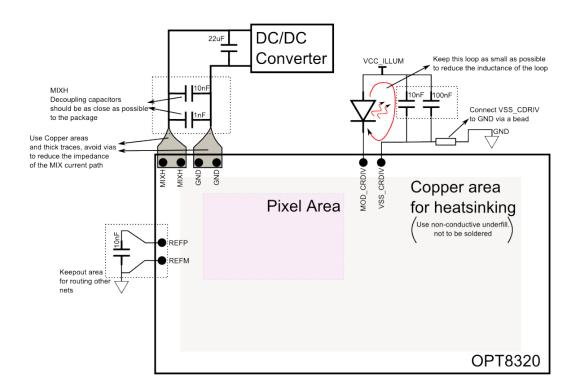

# **Application Block Diagram**

# **Table of Contents**

| 1 | Features 1                           | 7.5 Register Maps2                      |

|---|--------------------------------------|-----------------------------------------|

| 2 | Applications 1                       | 8 Application and Implementation 6      |

| 3 | Description 1                        | 8.1 Application Information 6           |

| 4 | Revision History2                    | 8.2 Typical Applications 6              |

| 5 | Pin Configuration and Functions      | 8.3 Initialization Set Up7              |

| 6 | Specifications5                      | 9 Power Supply Recommendations          |

| • | 6.1 Absolute Maximum Ratings         | 9.1 Example Power Consumption Numbers   |

|   | 6.2 ESD Ratings                      | 9.2 Power Trade-Off7                    |

|   | 6.3 Recommended Operating Conditions | 10 Layout 79                            |

|   | 6.4 Thermal Information              | 10.1 Layout Guidelines 7                |

|   | 6.5 Electrical Characteristics 6     | 10.2 Layout Example8                    |

|   | 6.6 Timing Requirements              | 10.3 Mechanical Assembly Guidelines 8   |

|   | 6.7 Switching Characteristics        | 11 Device and Documentation Support 8   |

|   | 6.8 Optical Characteristics8         | 11.1 Documentation Support8             |

|   | 6.9 Typical Characteristics9         | 11.2 Community Resources 8              |

| 7 | Detailed Description 10              | 11.3 Trademarks 8                       |

| - | 7.1 Overview 10                      | 11.4 Electrostatic Discharge Caution 8  |

|   | 7.2 Functional Block Diagram         | 11.5 Glossary 8                         |

|   | 7.3 Feature Description              | 12 Mechanical, Packaging, and Orderable |

|   | 7.4 Device Functional Modes          | Information 8                           |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2015 | *        | Initial release. |

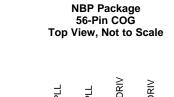

# **Pin Configuration and Functions**

Copyright © 2015, Texas Instruments Incorporated

# **Pin Functions**

| Pin Functions   |           |               |                   |                                                                 |  |  |  |

|-----------------|-----------|---------------|-------------------|-----------------------------------------------------------------|--|--|--|

| PIN             |           |               | I/O               |                                                                 |  |  |  |

| NAME            | NO.       | I/O           | VOLTAGE<br>DOMAIN | DESCRIPTION                                                     |  |  |  |

| AVDD            | 5         | Power         | _                 | Analog 1.8-V supply                                             |  |  |  |

| AVDD_PLL        | 49        | Power         | _                 | Analog 1.8-V PLL supply                                         |  |  |  |

| AVSS_PLL        | 48        | Power         | _                 | Analog PLL ground                                               |  |  |  |

| AVDDH           | 4         | Power         | _                 | Analog 3.3-V supply                                             |  |  |  |

| AVSS            | 6, 9      | Power         | _                 | Analog ground                                                   |  |  |  |

| DEBUG           | 21        | Bidirectional | IOVDD             | Debug port. Pullup to IOVDD with a 10-kΩ resistor.              |  |  |  |

| DVDD            | 19, 39    | Power         | _                 | Digital 1.8-V supply                                            |  |  |  |

| DVDDH           | 50        | Power         | _                 | Digital 3.3-V supply                                            |  |  |  |

| DVSS            | 18, 38    | Power         | _                 | Digital ground                                                  |  |  |  |

| GND             | 1, 53, 54 | Power         | _                 | Connect to ground                                               |  |  |  |

| GPO[0]          | 13        | Output        | IOVDD             | General-purpose output 0                                        |  |  |  |

| GPO[1]          | 14        | Output        | IOVDD             | General-purpose output 1                                        |  |  |  |

| HD              | 28        | Output        | IOVDD             | Indicates the row boundary                                      |  |  |  |

| I2C_MAS_SCL     | 40        | Output        | IOVDD             | Host I <sup>2</sup> C clock output                              |  |  |  |

| I2C_MAS_SDA     | 41        | Bidirectional | IOVDD             | Host I <sup>2</sup> C data                                      |  |  |  |

| I2C_SLV_ADDR[0] | 23        | Input         | IOVDD             | I <sup>2</sup> C address bit 0                                  |  |  |  |

| I2C_SLV_SCL     | 16        | Input         | IOVDD             | Slave I <sup>2</sup> C interface clock input                    |  |  |  |

| I2C_SLV_SDA     | 17        | Bidirectional | IOVDD             | Slave I <sup>2</sup> C Interface data                           |  |  |  |

| ILLUM_EN        | 45        | Output        | DVDDH             | Illumination enable                                             |  |  |  |

| ILLUM_FB        | 44        | Input         | DVDDH             | Feedback signal for illumination power control                  |  |  |  |

| ILLUM_N         | 51        | Bidirectional | DVDDH             | Illumination modulation signal                                  |  |  |  |

| ILLUM_P         | 52        | Bidirectional | DVDDH             | Illumination modulation signal                                  |  |  |  |

| ILLUM_PWM_CTRL  | 43        | Output        | DVDDH             | PWM signal for illumination power control                       |  |  |  |

| ILLUM_PWM_SYNC  | 42        | Output        | DVDDH             | PWM signal for illumination power control                       |  |  |  |

| IOVDD           | 24, 26    | Power         | _                 | IO voltage 1.8 V, 3.3 V                                         |  |  |  |

| IOVSS           | 25        | Power         | _                 | IO ground                                                       |  |  |  |

| MCLK            | 10        | Input         | IOVDD             | Main clock input for the device                                 |  |  |  |

| MIXH            | 55, 56    | Power         | _                 | Modulation voltage power pin                                    |  |  |  |

| MOD_CDRIV       | 47        | Output        | _                 | Illumination current driver                                     |  |  |  |

| OP_CLK          | 29        | Output        | IOVDD             | CMOS data bus clock output                                      |  |  |  |

| OP_DATA[0]      | 30        | Output        | IOVDD             | CMOS data out bit 0                                             |  |  |  |

| OP_DATA[1]      | 31        | Output        | IOVDD             | CMOS data out bit 1                                             |  |  |  |

| OP_DATA[2]      | 32        | Output        | IOVDD             | CMOS data out bit 2                                             |  |  |  |

| OP_DATA[3]      | 33        | Output        | IOVDD             | CMOS data out bit 3                                             |  |  |  |

| OP_DATA[4]      | 34        | Output        | IOVDD             | CMOS data out bit 4                                             |  |  |  |

| OP_DATA[5]      | 35        | Output        | IOVDD             | CMOS data out bit 5                                             |  |  |  |

| OP_DATA[6]      | 36        | Output        | IOVDD             | CMOS data out bit 6                                             |  |  |  |

| OP_DATA[7]      | 37        | Output        | IOVDD             | CMOS data out bit 7                                             |  |  |  |

| PVDD            | 3         | Power         | _                 | Pixel 3.3-V supply                                              |  |  |  |

| REFM            | 7         | Analog input  | _                 | Connect REFM to GND                                             |  |  |  |

| REFP            | 8         | Analog output |                   | ADC reference. Connect a 10-nF capacitor between REFP and REFM. |  |  |  |

| RESET           | 15        | Input         | IOVDD             | Reset; active low                                               |  |  |  |

| SLEEP           | 22        | Input         | IOVDD             | Power-down pin                                                  |  |  |  |

| SUB_BIAS        | 2         | Power         | _                 | Negative bias voltage                                           |  |  |  |

| Thermal pad     | •         | Power         | _                 | Exposed thermal pad. Do not solder.                             |  |  |  |

#### Pin Functions (continued)

| PIN       |     |         | I/O                        |                                    |

|-----------|-----|---------|----------------------------|------------------------------------|

| NAME      | NO. | I/O     | VOLTAGE DESCRIPTION DOMAIN |                                    |

| TP1       | 12  | Passive | IOVDD                      | Test point 1                       |

| TP2       | 11  | Passive | IOVDD                      | Test point 2                       |

| VD        | 27  | Output  | IOVDD                      | Indicates the frame boundary       |

| VD_IN     | 20  | Input   | IOVDD                      | External sync input                |

| VSS_CDRIV | 46  | Power   | _                          | Illumination current driver ground |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                | MIN  | MAX                      | UNIT |

|------------------|--------------------------------|------|--------------------------|------|

| IOVDD            | Digital I/O supply             | -0.3 | 4.0                      | V    |

| AVDDH            | Analog supply                  | -0.3 | 4.0                      | V    |

| DVDDH            | Digital I/O supply             | -0.3 | 4.0                      | V    |

| PVDD             | Pixel supply                   | -0.3 | 4.0                      | V    |

| AVDD             | Analog supply                  | -0.3 | 2.2                      | V    |

| VMIXH            | Mix supply                     | -0.3 | 2.5                      | V    |

| DVDD             | Digital supply                 | -0.3 | 2.2                      | V    |

| AVDD_PLL         | PLL supply                     | -0.3 | 2.2                      | V    |

| V <sub>I</sub>   | Input voltage at input pins    | -0.3 | VCC + 0.3 <sup>(2)</sup> | V    |

| TJ               | Operating junction temperature | 0    | 125                      | °C   |

| T <sub>stg</sub> | Storage temperature            | -40  | 125                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|        |                                            |                                                                     | VALUE | UNIT       |

|--------|--------------------------------------------|---------------------------------------------------------------------|-------|------------|

| V      | Floatroatatio discharge                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \ <u>/</u> |

| V(ESD) | V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V          |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                               | MIN | NOM        | MAX | UNIT |

|----------------|-------------------------------|-----|------------|-----|------|

| IOVDD          | Digital I/O supply            | 1.7 | 1.8 to 3.3 | 3.6 | V    |

| AVDDH          | Analog supply                 | 3.0 | 3.3        | 3.6 | V    |

| DVDDH          | Digital I/O supply            | 3.0 | 3.3        | 3.6 | V    |

| PVDD           | Pixel supply                  | 2.4 | 3.3        | 3.6 | V    |

| AVDD           | Analog supply                 | 1.7 | 1.8        | 1.9 | V    |

| VMIXH          | Mix supply                    | 0.8 | 1.5        | 2.0 | V    |

| DVDD           | Digital supply                | 1.7 | 1.8        | 1.9 | V    |

| AVDD_PLL       | PLL supply                    | 1.7 | 1.8        | 1.9 | V    |

| $V_{DRV}$      | MOD_CDRIV pin voltage         | 0.7 |            | 3.3 | V    |

| T <sub>A</sub> | Operating ambient temperature | 0   |            | 70  | °C   |

<sup>(2)</sup> VCC refers to the I/O bank voltage.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# TEXAS INSTRUMENTS

#### 6.4 Thermal Information

|                      |                                                                  |                   | OPT8320 |      |

|----------------------|------------------------------------------------------------------|-------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                                    |                   |         | UNIT |

|                      |                                                                  |                   | 56 PINS |      |

| Б                    | lunction to eachiest the surrel marietaness                      | Without underfill | 93.4    | 900  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                           | With underfill    | 44.0    | °C/W |

| $R_{\theta JC(top)}$ | R <sub>0,JC(top)</sub> Junction-to-case (top) thermal resistance |                   | 22.7    | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                             |                   | 61.6    | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter                       |                   | 7.2     | °C/W |

|                      | lunction to board observatorization necessary                    | Without underfill | 61.4    | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter                     | With underfill    | 11.9    | C/VV |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

all specifications at  $T_A = 25$ °C,  $V_{AVDDH} = 3.3$  V,  $V_{AVDD} = 1.8$  V,  $V_{VMIXH} = 1.8$  V,  $V_{DVDD} = 1.8$  V,  $V_{DVDDH} = 3.3$  V,  $V_{PVDD} = 3.3$  V,  $V_{SUB\_BIAS} = 0$  V, integration duty cycle = 20%, system clock frequency = 24 MHz,  $V_{IOVDD} = 1.8$  V, modulation frequency = 48 MHz, quads = 4, sub-frames = 4, frame-rate = 30 FPS, and 850-nm illumination (unless otherwise noted)

|                       | PARAMETER                                  | TEST CONDITIONS             | MIN | TYP  | MAX | UNIT    |

|-----------------------|--------------------------------------------|-----------------------------|-----|------|-----|---------|

| SENSOR                |                                            |                             |     |      |     |         |

| V                     | Rows                                       |                             |     |      | 60  | Rows    |

| Н                     | Columns                                    |                             |     |      | 80  | Columns |

| P <sub>P</sub>        | Pixel pitch                                |                             |     | 30   |     | μm      |

| ILLUMINA              | TION DRIVER                                |                             |     |      |     |         |

| I <sub>DRV</sub>      | Max built-in illumination driver current   |                             |     | 150  |     | mA      |

| f <sub>DRV</sub>      | Max Built-in illumination driver frequency |                             |     | 100  |     | MHz     |

| ILLUMINA              | TION POWER CONTROL                         |                             |     |      |     |         |

|                       | Minimum pulse duration                     |                             |     | 10.4 |     | ns      |

|                       | Starting duty cycle                        |                             |     | 50%  |     |         |

| POWER (               | Normal Operation)                          |                             |     |      |     |         |

| I <sub>AVDD_PLL</sub> | PLL supply current                         |                             |     | 4    |     | mA      |

|                       | Analog gunnly gurrent                      | Without dynamic power-down  |     | 20.7 |     | mA      |

| I <sub>AVDD</sub>     | Analog supply current                      | With dynamic power-down     |     | 6.7  |     | mA      |

| I <sub>DVDDH</sub>    | 3.3-V digital supply current               |                             |     | 0.3  |     | mA      |

|                       | 2.2. V analog august, august               | Without dynamic power-down  |     | 5.5  |     | A       |

| I <sub>AVDDH</sub>    | OH 3.3-V analog supply current             | With dynamic power-down     |     | 1.5  |     | mA      |

| I <sub>PVDD</sub>     | Pixel VDD current                          |                             |     | 0.5  |     | mA      |

|                       | Demodulation current                       | 10% integration duty cycle  |     | 56   |     | A       |

| I <sub>VMIXH</sub>    | Demodulation current                       | 100% integration duty cycle |     | 560  |     | mA      |

| I <sub>IOVDD</sub>    | I/O supply current (CMOS mode)             |                             |     | 4.2  |     | mA      |

| $I_{DVDD}$            | Digital supply current                     |                             |     | 19.7 |     | mA      |

| POWER (               | Standby)                                   | -                           | _   |      |     |         |

| I <sub>IOVDD</sub>    | I/O supply current                         |                             |     | 1    |     | mA      |

| I <sub>AVDD_PLL</sub> | PLL supply current                         |                             |     | 100  |     | μΑ      |

| I <sub>AVDD</sub>     | Analog supply current                      |                             |     | 1    |     | mA      |

| I <sub>DVDD</sub>     | Digital supply current                     |                             |     | 4    |     | mA      |

| I <sub>DVDDH</sub>    | 3.3-V digital supply current               |                             |     | 50   |     | μA      |

| I <sub>AVDDH</sub>    | 3.3-V analog supply current                |                             |     | 200  |     | μΑ      |

| $I_{VMIXH}$           | Demodulation current                       |                             |     | 0    |     | mA      |

| I <sub>PVDD</sub>     | Pixel VDD current                          |                             |     | 100  |     | μA      |

# **Electrical Characteristics (continued)**

all specifications at  $T_A = 25$ °C,  $V_{AVDDH} = 3.3$  V,  $V_{AVDD} = 1.8$  V,  $V_{VMIXH} = 1.8$  V,  $V_{DVDD} = 1.8$  V,  $V_{DVDDH} = 3.3$  V,  $V_{PVDD} = 3.3$  V,  $V_{SUB\_BIAS} = 0$  V, integration duty cycle = 20%, system clock frequency = 24 MHz,  $V_{IOVDD} = 1.8$  V, modulation frequency = 48 MHz, quads = 4, sub-frames = 4, frame-rate = 30 FPS, and 850-nm illumination (unless otherwise noted)

|                 | PARAMETER                     | TEST CONDITIONS                        | MIN                      | TYP                          | MAX                | UNIT |

|-----------------|-------------------------------|----------------------------------------|--------------------------|------------------------------|--------------------|------|

| CMOS            | INPUTS/OUTPUTS                |                                        |                          |                              |                    |      |

| V <sub>IH</sub> | Input high-level threshold    |                                        | 0.7 × VCC <sup>(1)</sup> |                              |                    | V    |

| V <sub>IL</sub> | Input low-level threshold     |                                        |                          | 0.3 × V                      | 'CC <sup>(1)</sup> | V    |

|                 | ***                           | I <sub>OH</sub> = −2 mA                |                          | VCC <sup>(1)</sup> –<br>0.45 |                    | .,   |

| V <sub>OH</sub> | Min Output high level         | I <sub>OH</sub> = -8 mA                |                          | VCC <sup>(1)</sup> –<br>0.5  |                    | V    |

| 1/              | May Output law laval          | I <sub>OL</sub> = 2 mA                 |                          | 0.35                         |                    | V    |

| $V_{OL}$        | Max Output low level          | I <sub>OL</sub> = 8 mA                 |                          | 0.65                         |                    | V    |

|                 |                               | Pins with pullup, pulldown resistor    |                          |                              | ±50                |      |

| I <sub>I</sub>  | Input pin leakage current     | Pins without pullup, pulldown resistor |                          |                              | ±10                | μΑ   |

| Cı              | Input capacitance             |                                        |                          | 5                            |                    | pF   |

| I <sub>OH</sub> | Max output current high level |                                        |                          | 10                           |                    | mA   |

| I <sub>OL</sub> | Max output current low level  |                                        |                          | 10                           |                    | mA   |

<sup>(1)</sup> VCC is equal to IOVDD or DVDDH, based on the I/O bank listed in the table.

# 6.6 Timing Requirements

|                                  | MIN             | NOM | MAX | UNIT |

|----------------------------------|-----------------|-----|-----|------|

| MCLK duty cycle                  | 48%             |     | 52% |      |

| MCLK frequency                   |                 | 24  |     | MHz  |

| VD_IN pulse duration             | 2 x MCLK period |     |     |      |

| RESET low pulse duration (reset) | 100             |     |     | ns   |

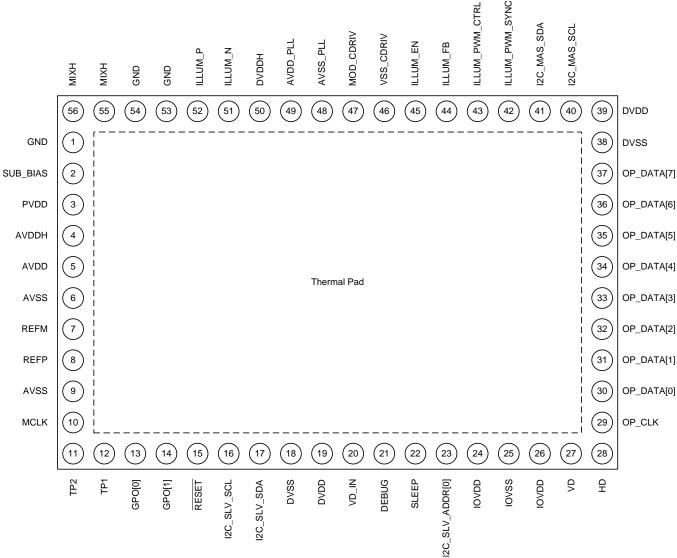

# 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted);  $V_{DVDD} = 1.8 \text{ V}$ ,  $V_{DVDDH} = 3.3 \text{ V}$ , and  $V_{IOVDD} = 1.8 \text{ V}$

|                                                 | PARAMETER                                      | TEST CONDITIONS                                  | MIN | TYP  | MAX | UNIT |  |

|-------------------------------------------------|------------------------------------------------|--------------------------------------------------|-----|------|-----|------|--|

| PARALLEL CMOS MODE (V <sub>IOVDD</sub> = 1.8 V) |                                                |                                                  |     |      |     |      |  |

| t <sub>SU</sub>                                 | Data setup time                                | Data valid to zero crossing of CLKOUT            |     | 18.4 |     | ns   |  |

| t <sub>H</sub>                                  | Data hold time                                 | Zero crossing of CLKOUT to data becoming invalid |     | 21.1 |     | ns   |  |

| t <sub>FALL</sub> , t <sub>RISE</sub>           | Data fall time, data rise time                 | Rise time measured from 30% to 70% of IOVDD      |     | 1.75 |     | ns   |  |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub>  | Output clock rise time, output clock fall time | Rise time measured from 30% to 70% of IOVDD      |     | 1.72 |     | ns   |  |

| PARALLEL C                                      | MOS MODE (V <sub>IOVDD</sub> = 3.3 V)          |                                                  |     |      |     |      |  |

| t <sub>SU</sub>                                 | Data setup time                                | Data valid to zero crossing of CLKOUT            |     | 18.3 |     | ns   |  |

| t <sub>H</sub>                                  | Data hold time                                 | Zero crossing of CLKOUT to data becoming invalid |     | 21.4 |     | ns   |  |

| t <sub>FALL</sub> , t <sub>RISE</sub>           | Data fall time, data rise time                 | Rise time measured from 30% to 70% of IOVDD      |     | 1.32 |     | ns   |  |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub>  | Output clock rise time, output clock fall time | Rise time measured from 30% to 70% of IOVDD      |     | 1.39 |     | ns   |  |

SBAS748 – DECEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

# 6.8 Optical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                    | TEST CONDITIONS    | MIN | TYP           | MAX | UNIT    |

|---------------------------|----------------------------------------------|--------------------|-----|---------------|-----|---------|

|                           | Glass side                                   |                    |     | Тор           |     | Side    |

| Passband                  |                                              | 0° incident angle  |     | 813 to 893    |     | nm      |

| (50% relative transmittal | (50% relative transmittance <sup>(1)</sup> ) | 30° incident angle |     | 798 to 877    |     | nm      |

| Passband                  | Passband                                     | 0° incident angle  |     | 830 to 881    |     | nm      |

|                           | (90% relative transmittance <sup>(1)</sup> ) | 30° incident angle |     | 838 to 867    |     | nm      |

| AOI                       | Recommended angle of incidence               |                    | 0   |               | 35  | Degrees |

|                           | Maximum absolute transmittance               | 0° incident angle  |     | 87.34% at 863 |     | nm      |

|                           | Maximum absolute transmittance               | 30° incident angle |     | 81.89% at 855 |     | nm      |

(1) Relative transmittance is a ratio of transmittance to maximum absolute transmittance at the same angle of incidence.

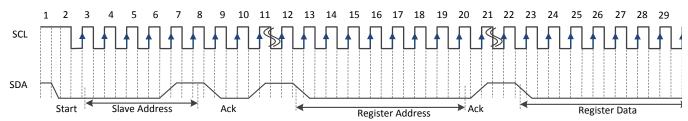

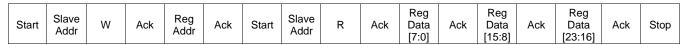

NOTE: In SSI output mode, clock polarity is inverted when compared to DVP mode.

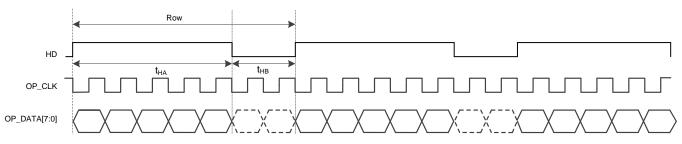

Figure 1. Output Block Timing Diagram

Submit Documentation Feedback

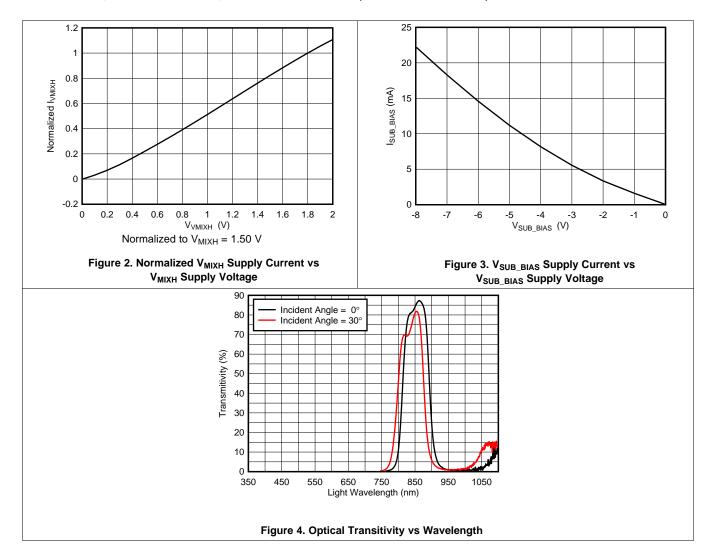

# 6.9 Typical Characteristics

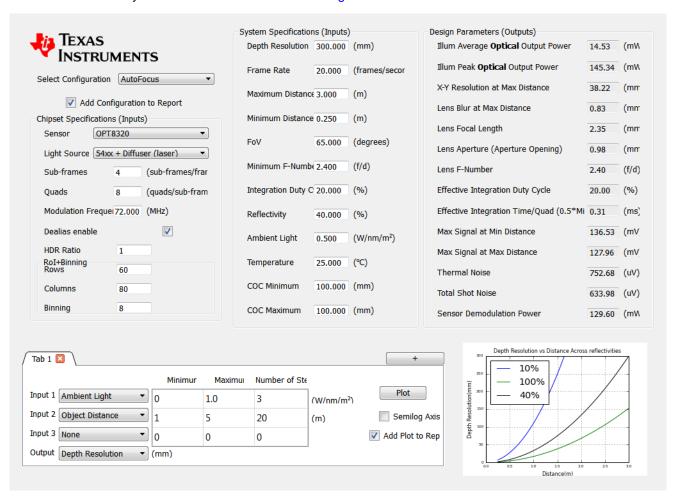

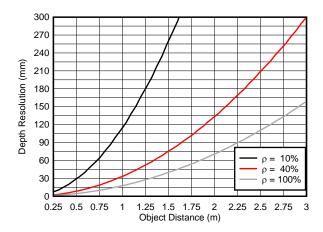

all specifications at  $T_A = 25$ °C,  $V_{AVDDH} = 3.3$  V,  $V_{AVDD} = 1.8$  V,  $V_{VMIXH} = 1.8$  V,  $V_{DVDD} = 1.8$  V,  $V_{DVDDH} = 3.3$  V,  $V_{PVDD} = 3.3$  V,  $V_{SUB\_BIAS} = 0$  V, integration duty cycle = 20%, system clock frequency = 24 MHz, modulation frequency = 48 MHz, quads = 4, sub-frames = 4, frame-rate = 30 FPS, and 850-nm illumination (unless otherwise noted)

SBAS748 – DECEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

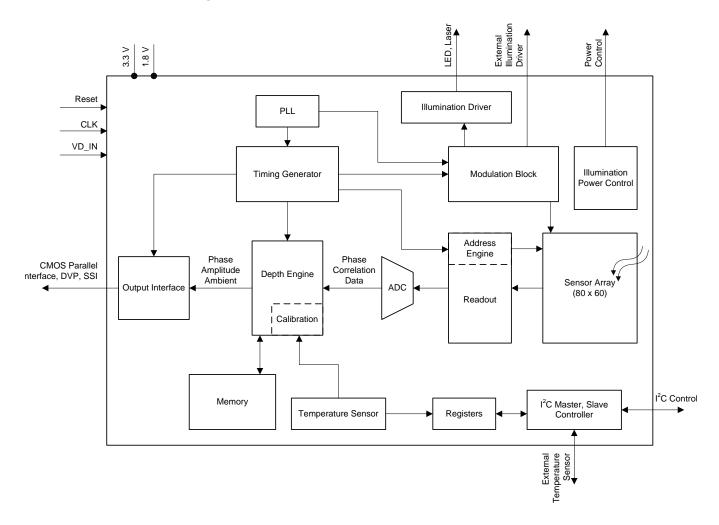

# 7 Detailed Description

#### 7.1 Overview

The OPT8320 system-on-chip (SoC) has the following blocks:

- Timing generator: generates the sequencing signals for the sensor, illumination, and depth processor

- Sensor: the pixel array

- Addressing engine

- Analog-to-digital converter (ADC)

- Modulation block

- · Illumination driver

- · Depth engine: calculates phase and amplitude

- Internal memory for depth computation

- Illumination power control

- · Output data interface module

- I<sup>2</sup>C slave for configuring the device registers via the host processor

- I<sup>2</sup>C master for temperature sensing

# 7.2 Functional Block Diagram

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

### 7.3 Feature Description

### 7.3.1 Timing Generator

The timing generator (TG) generates the timing sequence for each frame. The TG includes frame rate control, quad sequencing, and integration time control.

#### 7.3.1.1 Basic Frame Structure

Each frame is divided into sub-frames used for internal averaging, as shown in Table 1.

**Table 1. Frame Structure**

| FRAME       |             |     |             |                 |  |  |

|-------------|-------------|-----|-------------|-----------------|--|--|

| Sub-frame 1 | Sub-frame 2 | ••• | Sub-frame n | Frame dead time |  |  |

Each sub-frame is divided into quads, as shown in Table 2. Each quad can have a different phase between the illumination and sensor modulation signals.

#### **Table 2. Sub-Frame Division**

| SUB-FRAME |        |        |  |        |  |

|-----------|--------|--------|--|--------|--|

| Quad 1    | Quad 2 | Quad 3 |  | Quad n |  |

Each quad is further split into four stages, as shown in Table 3. These stages are described in Table 3.

#### **Table 3. Quad Stages**

| QUAD              |  |         |                |  |  |

|-------------------|--|---------|----------------|--|--|

| Reset Integration |  | Readout | Quad dead time |  |  |

The description of the quad stages is given in Table 4.

#### **Table 4. Quad Stage Descriptions**

| QUAD STAGE  | DESCRIPTION                                                                                                                      |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Reset       | The sensor is reset to clear the accumulated signal                                                                              |  |  |  |

| Integration | The pixel array and illumination are modulated by the modulation block. The sensor captures the raw time-of-flight (ToF) signal. |  |  |  |

| Readout     | The raw pixel data in the selected region of interest is readout from the sensor on to the ADC and then by the depth engine.     |  |  |  |

| Dead        | The sensor is inactive. The ADC enters a low-power mode.                                                                         |  |  |  |

# TEXAS INSTRUMENTS

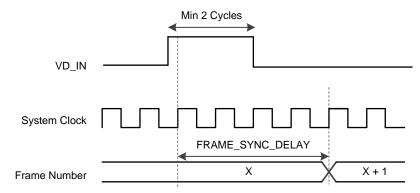

#### 7.3.1.2 System Clock

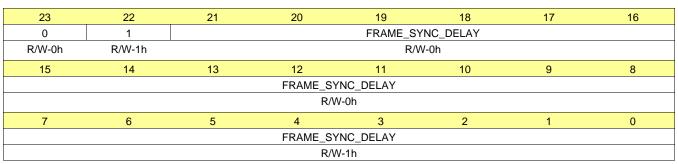

FRAME\_SYNC\_DELAY

The input clock to the system must be 24 MHz. By default, the TG functions at the same frequency as the input frequency. Therefore, the system clock frequency (SYS\_CLK\_FREQ) is equal to the input frequency at the MCLK pin.

#### 7.3.1.3 Frame Rate Control and Sub-Frames

1

The OPT8320 supports master and slave modes of operation for the start of frame timing. The parameters shown in Table 5 control the master and slave behavior.

**DEFAULT PARAMETER DESCRIPTION** Start the timing generator and, thus, the full chipset operation. TG\_EN 0 = Disable the timing generator 0 1 = Enable the timing generator Puts the timing controller in slave mode. The timing controller waits for an external SLAVE\_MODE 0 sync through the VD\_IN pin for the start of frames. By default, the timing controller is in master mode. Puts the timing controller in SYNC\_MODE. The timing controller synchronizes with an external input through the VD\_IN pin for the start of frames, but does not 0 SYNC\_MODE depend on the input. If both SLAVE\_MODE and SYNC\_MODE are enabled,

SYNC\_MODE takes higher priority. By default, this mode is disabled.

of frame. The delay must be at least one cycle.

The programmable delay between the external VD\_IN pulse and the internal start

**Table 5. Master and Slave Parameters**

In slave mode or sync mode, a positive pulse on the VD\_IN pin can be used for synchronization. The pulse must be a minimum of two system clocks cycles wide in order to be recognized correctly, as shown in Figure 5. In slave mode, if another pulse is received before the end of the previous frame, the pulse is ignored. In sync mode, because a pulse can be received by the OPT8320 anytime within a frame, the frame during which the pulse is received is aborted and therefore disruption of output data is possible, resulting in a loss of information.

Figure 5. VD\_IN Timing Diagram

When the OPT8320 is operated in master mode or sync mode, the frame rate is controlled using the parameters shown in Table 6. In the OPT8320, the number of quads (QUAD\_CNT\_MAX) are fixed to four. Using the functionality of alternate frames, two kinds of frames are possible with a different set of sub-frames, integration duty cycle, and modulation frequency. The resulting information can be also combined to give out a single dealiased frame. When alternate frames are enabled, every alternate frame with the different set of timing parameters is called the supplementary frame.

|       | _ | _     | _    | _      |       |

|-------|---|-------|------|--------|-------|

| Tabla | _ | Erama | Data | Parame | ntarc |

|       |   |       |      |        |       |

| PARAMETER              | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALT_FRM_EN             | 0       | When set to 1, enables alternate frames with a different set of sub-frames, integration duty cycle, and frequency.                                                                                                                                                                                                              |

| SUB_FRAME_CNT_MAX1     | 16      | Total number of sub-frames in each frame for the base frame. Only values that are powers of 2 are valid. Behavior is unpredictable when set to other values.                                                                                                                                                                    |

| SUB_FRAME_CNT_MAX2     | 4       | Total number of sub-frames in each frame for the supplementary frame. Only values that are powers of 2 are valid. Behavior is unpredictable when set to other values.                                                                                                                                                           |

| PIX_CNT_MAX            | 12500   | The number of system clock cycles in one frame divided by the product of QUAD_CNT_MAX and SUB_FRAME_CNT_MAX.                                                                                                                                                                                                                    |

| PIX_CNT_MAX_SET_FAILED | 0       | Read-only flag that indicates if the last setting of the PIX_CNT_MAX value is successful. If the PIX_CNT_MAX is smaller than the minimum size required to accommodate the reset and readout time, PIX_CNT_MAX_SET_FAILED is set.                                                                                                |

| LUMPED_DEAD_TIME       | 0       | Dead time can be either distributed equally among all quads or can be lumped at the end of each frame. Distributed quad dead time is typically better for phase offset cancellation. Lumped frame dead time is typically better for reducing motion artefacts and power consumption. By default, distributed dead time is used. |

Dead time is automatically calculated by the device based on the values of the integration duty cycle and readout time. If LUMPED\_DEAD\_TIME is set to 0, the dead time for each quad in relation to the number of system clocks is given by Equation 1:

Quad Dead Time =

$$PIX\_CNT\_MAX \times (1-Integration\ Duty\ Cycle) - (Sensor\ Reset\ Time + Readout\ Time)$$

(1)

If LUMPED\_DEAD\_TIME is set to 1, then the dead time for each frame in relation to the number of system clocks is given by Equation 2:

$$Frame \ Dead \ Time = SUB\_FRAME\_CNT\_MAX \times QUAD\_CNT\_MAX \times \\ \Big[ PIX\_CNT\_MAX \times \big(1 - Integration \ Duty \ Cycle \big) - \big( Sensor \ Reset \ Time + Readout \ Time \big) \Big]$$

$$(2)$$

Sensor reset time is equal to 720 system clock cycles. The readout time is given by Equation 9.

The calculation of PIX CNT MAX for when ALT FRM EN is 0 is given by Equation 3:

$$PIX\_CNT\_MAX = \frac{SYS\_CLK\_FREQ}{FRAME\_RATE \times QUAD\_CNT\_MAX \times SUB\_FRAME\_CNT\_MAX}$$

(3)

When ALT\_FRM\_EN is set to 1, alternate frames can have different frame times depending on the number of sub-frames (parameters are described in Table 6). Also, in most cases alternate frames are combined to form a single frame either internally or externally. In such cases, the frame rate is given by Equation 4:

$$De-Aliasing\ Frame\ Rate = SET\_FRAME\_RATE \times \left(\frac{SUB\_FRM\_CNT\_MAX1}{SUB\_FRM\_CNT\_MAX1 + SUB\_FRM\_CNT\_MAX2}\right) \tag{4}$$

# TEXAS INSTRUMENTS

#### 7.3.1.4 Integration Time

Integration time is the time that the sensor demodulation and the illumination modulation are active. The configurable parameters are listed in Table 7.

**Table 7. Integration Time Parameters**

| PARAMETER                      | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTG_DUTY_CYCLE                | 13      | This parameter controls the ratio of integration time to total frame time.                                                                                                                                                                                                                                                                                                                                       |

| INTG_DUTY_CYCLE_<br>SET_FAILED | 0       | This flag indicates if the INTG_DUTY_CYCLE setting has taken effect. If the INTG_DUTY_CYCLE is not feasible for a given set of conditions, this flag is set. This flag is cleared when a feasible value of INTG_DUTY_CYCLE is programmed. If this flag is set, a lower value of INTG_DUTY_CYCLE must be programmed and the value of the flag checked again. This process must be repeated until the flag clears. |

The INTG\_DUTY\_CYCLE registers allows 64 settings from 0 to 63. The relationship between effective integration duty cycle of the base frame and the register value is given by Equation 5:

$$INTG\_DUTY\_CYCLE = \frac{Integration\ Duty\ Cycle \times 64}{100}$$

(5)

Internally, the INTG\_DUTY\_CYCLE value is clamped to a minimum of 1. Maximum integration duty cycle is given by Equation 6:

Maximum Integration Duty Cycle =

$$\frac{PIX\_CNT\_MAX - (Reset\ Time + Readout\ Time)}{PIX\_CNT\_MAX}$$

(6)

The INTG\_DUTY\_CYCLE parameter must be reprogrammed whenever any of the registers related to frame rate control or region of interest are programmed. The related registers are:

- SUB\_FRAME\_CNT\_MAX1

- SUB\_FRAME\_CNT\_MAX2

- PIX\_CNT\_MAX

- LUMPED\_DEAD\_TIME

- ROW\_START

- COL START

- ROW END

- COL\_END

When the OPT8320 is in slave mode, the duty cycle still corresponds to the frame length calculated as per the internal registers and not as per the period of the external sync signal. The sync signal period must be large enough to make sure that the frame data are streamed successfully. When the sync signal period is larger than the internal frame period, the actual integration duty cycle is less than the programmed value.

#### 7.3.1.4.1 High Dynamic Range Functionality

When frame alternation is enabled, alternate frames can use different integration times. The supplementary frame integration time is scaled down as compared to the base frame by a factor. The relevant parameters are listed in Table 8.

**Table 8. High Dynamic Range Functionality Parameter**

| PARAMETER NAME     | DEFAULT | DESCRIPTION                                                                                                                                                      |

|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUP_FRM_INTG_SCALE | 63      | Denotes the percentage of INTG_PHASE in the supplementary frame in terms of the base frame. INTG_DUTY_CYCLE2 = INTG_DUTY_CYCLE1 x (SUP_FRM_INTG_SCALE + 1) / 64. |

The supplementary frame integration time is given in Equation 7:

Supplementary Frame Integration Time =

Base Frame Integration Time

$$\times \frac{SUP\_FRM\_INTG\_SCALE + 1}{64}$$

(7)

#### 7.3.2 Pixel Array

www.ti.com

The pixel array consists of 80 x 60 demodulating pixels. With a 30-µm x 30-µm pixel size, the pixels exhibit excellent dynamic range. The pixels also have a built-in shutter feature that helps in achieving higher ambient robustness. For convenience, either the entire or part of the pixel array can be readout through register configurations.

#### 7.3.2.1 Region of Interest (ROI)

A subset of the sensor array can be readout to enhance frame rate or to reduce the power consumption of the ToF system. An ROI is comprised of a set of row and column limits. The row and column counts start from zero. Both row and column limits can be any of the valid row numbers for the given sensor size. The relevant parameters are listed in Table 9.

Table 9. ROI Parameters

| PARAMETER | DEFAULT | DESCRIPTION                              |

|-----------|---------|------------------------------------------|

| ROW_START | 0       | Start address for the row address bus    |

| COL_START | 0       | Start address for the column address bus |

| ROW_END   | 59      | End address for the row address bus      |

| COL_END   | 79      | End address for the column address bus   |

Sensor readout time is affected by ROI. A minimum row-to-row switching time of half the row readout time is enforced internally. Thus, reducing the column count to less than half of the total number of columns for a given sensor does not lead to a reduction in sensor readout time. For a number of columns greater than the total number of columns divided by 2, use Equation 8:

Readout Time = Preparation Time +

$$[(Rows + 1) \times (Cols + 1)]$$

(Measured in System Clock Cycles)

For a number of columns less than half of the total number of columns, use Equation 9:

Readout Time = Preparation Time +

$$[(Rows + 1) \times (Total Cols/2 + 1)]$$

(Measured in System Clock Cycles)

where:

# (9)

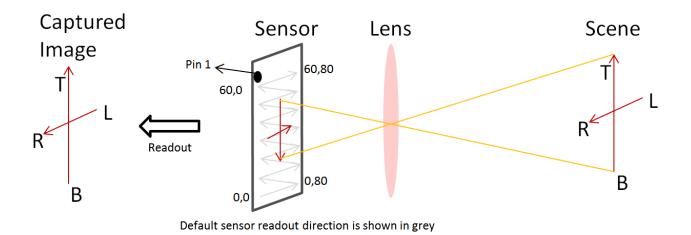

#### 7.3.2.2 Readout Sequence

The readout sequence can be controlled to achieve mirroring along horizontal or vertical axis. The programmable parameters are listed in Table 10.

**Table 10. Readout Sequence Parameters**

| PARAMETER      | DEFAULT | DESCRIPTION                       |

|----------------|---------|-----------------------------------|

| DOW DDOLLT DID | 0       | 0 = Vertical inversion disabled   |

| ROW_RDOUT_DIR  | U       | 1 = Vertical inversion enabled    |

| OOL DROUT DID  |         | 0 = Horizontal inversion disabled |

| COL_RDOUT_DIR  | U       | 1 = Horizontal inversion enabled  |

# TEXAS INSTRUMENTS

#### 7.3.2.3 Shutter Operation

Shutter operation can be used to control the exposure to ambient light. The shutter switch separates the charge storage node from the pixel charge collection node. The shutter can be programmed to become inactive (switch is on) at the start of integration and become active (switch is off) at the end of integration time to avoid collection of unwanted ambient light during the sensor readout. The behavior of the shutter switch is shown in Table 11.

**Table 11. Shutter Operation**

|                                                                            | QUAD STATE |             |         |                   |

|----------------------------------------------------------------------------|------------|-------------|---------|-------------------|

| OPERATION                                                                  | RESET      | INTEGRATION | READOUT | QUAD DEAD<br>TIME |

| State of the shutter software with the shutter operation enabled (default) | On         | On          | Off     | Off               |

| State of the shutter software with the shutter operation disabled          | On         | On          | On      | On                |

The SHUTTER\_EN parameter enables or disables the shutter operation. The SHUTTER\_EN description is given in Table 12.

**Table 12. Shutter Operation Registers**

| PARAMETER  | DEFAULT | DESCRIPTION                           |

|------------|---------|---------------------------------------|

| SHUTTER_EN | 0       | Set to 1 to enable shutter operation. |

#### 7.3.3 Modulation Block

The OPT8320 modulation block provides the high-frequency demodulation to the pixels as well as the illumination module. The modulation block controls the phase between the modulation signals connected to the pixels and the illumination module from quad to quad.

#### 7.3.3.1 Sensor Output Signals

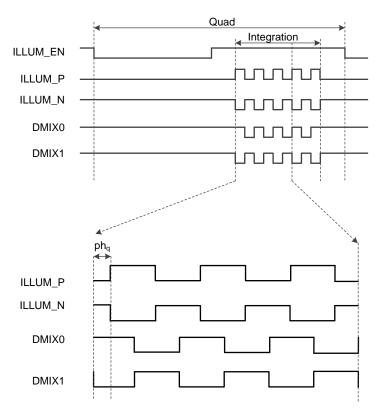

The phase between illumination modulation and the sensor demodulation signals is stepped automatically as per the quad number illustrated in Figure 6. Because the OPT8320 uses four quads per modulation frequency, the phase is typically stepped between 0°, 90°, 180°, and 270°. The phase stepping sequence of the sensor is programmable through the OPT8320 registers. A different sequence can be enabled for odd and even subframes. Also, the phase registers for the base frequency and de-aliasing frequency are separately programmable. The OPT8320 output signals are listed in Table 13.

Figure 6. Integration Timing Diagram

**Table 13. Sensor Output Signals**

| PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                           |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILLUM_P  | High-frequency input to the illumination driver, noninverting. Modulates during integration time. Held low by default during rest of the time.                                                                                                                        |

| ILLUM_N  | High-frequency input to the illumination driver, inverting. Modulates during integration time. Held high by default during rest of the time.                                                                                                                          |

| ILLUM_EN | If an external driver is used for driving the illumination current, this signal can be used to switch the driver between active and standby mode. Normally, this signal is active high just before the integration time and goes low just after the integration time. |

The programmable parameters are listed in Table 14 and Table 15.

### **Table 14. Pin Programmability**

| PARAMETER         | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                          |

|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODULATION_HOLD   | 0       | Disable modulation during the integration period. Set to 0 for normal operation.                                                                                                                                                                     |

| DEMOD_STATIC_POL  | 0       | DC state of illumination pins during the integration period if MODULATION_HOLD = 1.                                                                                                                                                                  |

| ILLUM_STATIC_POL  | 0       | DC state of illumination pins during the integration period if MODULATION_HOLD = 1. ILLUM_P = ILLUM_STATIC_POL, ILLUM_N = not (ILLUM_STATIC_POL).                                                                                                    |

| ILLUM_EN_EARLY    | 0       | Activates the illumination enable signal 15 $\mu s$ before the integration period starts when set to 1.                                                                                                                                              |

| ILLUM_DC_CORR_DIR | 0       | Sets the direction of the duty cycle correction for illumination output waveforms.  Note that when duty cycle is increased, the ILLUM_P duty cycle increases and the ILLUM_N duty cycle decreases.  0 = Increases duty cycle  1 = Reduces duty cycle |

| ILLUM_DC_CORR     | 0       | The illumination duty cycle can be corrected in steps of approximately 450 ps. The maximum value of this register is 11 (0Bh), resulting in a total correction of approximately ±5 ns.                                                               |

#### **Table 15. Phase Sequence Programmability**

| PARAMETER       | DEFAULT | DESCRIPTION                                                       |

|-----------------|---------|-------------------------------------------------------------------|

| QUAD_HOP_EN     | 0       | Enables a different sequence of quads for odd and even sub-frames |

| QUAD_HOP_OFFSET | 0       | The offset of the quad sequence for alternate sub-frames          |

The relative phase of the illumination modulation with respect to sensor modulation (Ph<sub>q</sub> for any quad) can be calculated as shown in Equation 10:

$$Ph_q = 360 \times \frac{Quad\ Number}{QUAD\_CNT\_MAX}$$

(10)

Note that the quad number is offset by the quad hop offset for that sub-frame.

The effective quad number = quad number + quad hop offset.

#### 7.3.3.2 Modulation Frequency

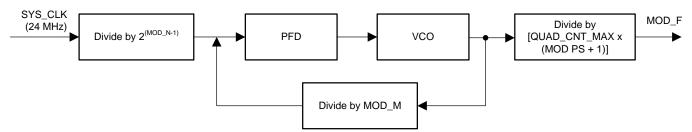

The OPT8320 sensor has an internal PLL for generating the base modulation frequency (MOD\_F) and the supplementary frame frequency. The formula for calculating the modulation frequency is given in Equation 11:

$$MOD\_F = \frac{MOD\_M \times 24 \text{ MHz}}{2^{(MOD\_N-1)} \times QUAD\_CNT\_MAX \times (1 + MOD\_PS)}$$

(11)

The internal VCO frequency is given by Equation 12:

$$VCO\_FREQ = \frac{MOD\_M \times 24 \text{ MHz}}{2^{(MOD\_N-1)}}$$

(12)

MOD\_M and MOD\_N must be chosen to meet the internal VCO frequency range limitation. The internal VCO can operate between 300 MHz and 600 MHz. The PLL block diagram is shown in Figure 7.

Figure 7. Modulation PLL Block Diagram

To enable accurate setting of the desired modulation frequency, MOD\_M is split into an integer and a fractional part. The effective MOD\_M is given by Equation 13:

$$Effective\ MOD\_M = MOD\_M + \frac{MOD\_M\_FRAC}{2^{16}}$$

(13)

The programmable parameters are listed in Table 16. The default base modulation frequency on start-up is 48 MHz.

| rable 10.1 rogrammable rarameters |         |                                                                       |

|-----------------------------------|---------|-----------------------------------------------------------------------|

| PARAMETER                         | DEFAULT | DESCRIPTION                                                           |

| MOD_M                             | 16      | VCO multiplier                                                        |

| MOD_M_FRAC                        | 0       | VCO multiplier                                                        |

| MOD_N                             | 1       | VCO divider                                                           |

| MOD_PS                            | 1       | Divider for generation of the base modulation frequency               |

| MOD_PLL_UPDATE                    | 0       | Set this bit to 1 and back to 0 for updating any modulation frequency |

**Table 16. Programmable Parameters**

#### 7.3.4 Depth Engine

The depth engine calculates the phase and amplitude information using the digitized data obtained from the sensor block. The depth engine uses an internal RAM to temporarily store the data obtained and to process data. The data engine has the following features:

- · Phase, amplitude calculation

- Binning

- De-aliasing

- Histogram computation

- Phase offset correction

- · Temperature correction

- Nonlinearity correction

# TEXAS INSTRUMENTS

#### 7.3.4.1 Phase Data

The computed phase for each pixel is proportional to the distance of the corresponding object in the scene. For a phase varying from  $0 \pi$  to  $2 \pi$ , the distance varies from 0 to R, where R is the unambiguous range. The equations describing the relationship between phase and distance are given in Equation 14 and Equation 15.

$$d = \frac{Phase \times R}{2\pi}$$

$$R = \frac{C}{2F}$$

(14)

where

- · C is the speed of light

- F is the modulation frequency (15)

At the output of the depth processor block, the phase of 2  $\pi$  is typically represented by a full 12-bit code (that is,  $2^{12}$ ). If the application requires the distance (in meters) of the points in the scene, this value must be calculated from the OPT8320 output using Equation 16:

$$d = \frac{Phase \times R}{2^{12}} \tag{16}$$

Equation 16 assumes that the phase has no offset. If offset correction is not done within the OPT8320, the formula is as shown in Equation 17:

$$d = \frac{(Phase - Offset) \times R}{2^{12}} \tag{17}$$

#### 7.3.4.2 De-Aliasing

The unambiguous range of a ToF system is defined by the modulation frequency (F). The unambiguous range is given by Equation 18:

$$R = \frac{C}{2F}$$

where

For example, for a modulation frequency of 50 MHz, R=3m in open air. If the total range of the application is beyond the unambiguous range for a given modulation frequency, de-aliasing can be enabled to extend the unambiguous range. The OPT8320 employs a dual modulation frequency technique to extend the unambiguous range. Two different frames are used to phase data corresponding to base frequency and supplementary frequency. The supplementary frequency is chosen to be lower than the base frequency and sets the unambiguous range. For example, if the base frequency is F, the supplementary frequency is chosen to be F/4 to increase the unambiguous range by four times. The data from the two frames can then be combined to obtain the unambiguous phase. To provide a full 16-bit phase after range extension, the flag bits in the data stream are replaced by the MSBs of the de-aliased phase automatically when de-aliasing is enabled.

#### 7.3.4.2.1 Procedure for Enabling De-Aliasing Mode

- 1. Disable the timing generator by setting the TG\_EN parameter to 0.

- 2. Set the ALT FRM EN parameter to enable alternate frames.

- 3. Set the ALT\_FREQ\_SEL parameter to select the range extension ratio.

- 4. Set the phase calibration parameters for each frequency as described in the *Phase Offset Correction* section.

- 5. Set SUB\_FRAME\_CNT\_MAX1 and SUB\_FRAME\_CNT\_MAX2 for the base and supplementary frames.

- 6. Set the PIX\_CNT\_MAX parameter to meet the frame rate requirements.

- 7. Set INTG\_DUTY\_CYCLE and SUP\_FRM\_INTG\_SCALE to set the integration time for the base and supplementary frames.

8. Set the DEALIAS\_EN parameter to 1 to combine the frames. Note that if the DEALIAS\_EN parameter is not set, the base and supplementary frame data are given out as is. If the DEALIAS\_EN parameter is set, the base and supplementary frame data are combined to give out de-aliased data and the effective frame rate must be recalculated as per Equation 4.

9. Enable the timing generator using the TG\_ENABLE parameter.

#### 7.3.4.3 Binning

Multiple pixel data can be averaged to form a single large pixel data. This feature is useful in cases where the application requires less pixel resolution but needs better phase noise performance. Rows and columns can be binned in powers of 2. The programmable parameters are listed in Table 17.

**Table 17. Binning Parameters**

| PARAMETER     | DEFAULT | DESCRIPTION                                                         |

|---------------|---------|---------------------------------------------------------------------|

| ROWS_TO_MERGE | 0       | number of rows to merge for binning = 2 <sup>ROWS_TO_MERGE</sup>    |

| COLS_TO_MERGE | 0       | Number of columns to merge for binning = 2 <sup>COLS_TO_MERGE</sup> |

# 7.3.4.4 Auxiliary Depth Data

Amplitude data represents the amplitude of the received signal at each pixel. If the amplitude is higher, signal amplitude is higher and thus the phase SNR is higher. The amplitude output value is given by Equation 19:

$$Amplitude = 4\sqrt{2} \times \left(2^{12} \times Signal \, Amplitude \times 0.825\right)$$

where

the signal amplitude is the amplitude of the single-ended modulating signal (A or B) generated on the pixel in each quad

When binning is enabled, the signal amplitude is the vector sum of the signals of all the binned pixels divided by the nearest power of 2 that is greater than the number of pixels binned together.

Ambient data are an indicator of the non-modulating component of voltage on the pixels. Ambient data are the sum of the ambient light, pixel offsets, and the non-demodulated component of the ToF illumination. The output ambient data values decrease with increase in voltage. Therefore, near-zero values indicate pixel saturation.

The OPT8320 provides masking of data based on the amplitude and single-ended voltage values in a pixel for the purpose of basic filtering. The related parameters are listed in Table 18.

**Table 18. Auxiliary Depth Data Parameters**

| PARAMETER            | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                       |

|----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMPLITUDE_THRESHOLD  | 0       | If the amplitude of the pixel is lower than this number, the pixel phase data are set to 000h                                                                                                                                                                     |

| IQ_SCALE             | 0       | Left shifts the acquired sensor data by the configured value. The scaling results in an equivalent scaling in amplitude. Care must be taken to avoid bit overflow in the depth engine because this scaling is done before the computation of phase and amplitude. |

| IQ_SCALE_EN          | 0       | When set to '1', enable scaling of I and Q according to the iq_scale register                                                                                                                                                                                     |

| SATURATION_THRESHOLD | 0       | The saturation flag is set if the ambient value of the pixel is less than or equal to this value. Also, pixel phase data are set to 000h.                                                                                                                         |

Flags[3:0] indicate important pixel data reliability parameters. The flags are described in Table 19.

#### Table 19. Flag Data

| FLAG BIT | DEFAULT                                           | DEALIAS_EN = 1 |

|----------|---------------------------------------------------|----------------|

| Flag[3]  | 0 = No pixel saturation<br>1 = Pixel is saturated | Phase[15]      |

| Flag[2]  | Reserved. Set to 0.                               | Phase[14]      |

| Flag[1]  | Frame counter[1]                                  | Phase[13]      |

| Flag[0]  | Frame counter[0]                                  | Phase[12]      |

When de-aliasing is enabled, an additional option to provide flags instead of ambient data is provided using the MV\_FLAGS\_TO\_AMBIENT parameter.

#### 7.3.4.5 Phase Offset Correction

Time delay between sensor modulation and the illumination modulation manifests as phase offset. The offset must be calibrated individually for each system because this delay can vary from one system to another. The measured offset can be programmed into a PHASE\_CORR parameter in the OPT8320 registers. The device adds the PHASE\_CORR parameter to the computed phase. The programmable parameters are listed in Table 20.

**Table 20. Phase Offset Correction Parameters**

| PARAMETER           | DESCRIPTION                                                                                    |

|---------------------|------------------------------------------------------------------------------------------------|

| PHASE_CORR_1        | Phase offset correction for the base frame                                                     |

| PHASE_CORR_2        | Phase offset correction for the supplementary frame                                            |

| DISABLE_OFFSET_CORR | Disables phase offset correction in the device. Phase offset correction is enabled by default. |

System delays in the illumination and sensor modulation path can vary differently as a result of temperature variations. This variation leads to a change in the measured phase. To compensate for phase change versus temperature, the OPT8320 uses two programmable temperature coefficients. The built-in temperature sensor in the OPT8320 is used for measuring the ToF sensor temperature, and an external I<sup>2</sup>C interface-based temperature sensor is used for measuring the illumination driver temperature. The programmable parameters are listed in Table 21.

**Table 21. Temperature Coefficient Parameters**

| PARAMETER         | DESCRIPTION                                                                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TILLUM_CALIB      | Illumination driver temperature when PHASE_CORR is measured.                                                                                     |

| TSENSOR_CALIB     | Sensor temperature when PHASE_CORR is measured.                                                                                                  |

| COEFF_ILLUM       | Phase versus temperature coefficients for the illumination driver for the base frame.                                                            |

| COEFF_SENSOR      | Phase versus temperature coefficients for the sensor for the base frame.                                                                         |

| DISABLE_TEMP_CORR | Disables phase offset correction resulting from temperature. (Temperature correction is enabled by default.)                                     |

| CALIB_PREC        | Adjusts the precision of temperature correction. Coefficients are scaled by CALIB_PREC. Internal COEFF = [programmed COEFF << (CALIB_PREC - 8)]. |

Phase correction resulting from temperature variation is calculated by the OPT8320, and is shown in Equation 20:

PHASE\_CORR\_TEMP =

$COEFF\_ILLUM \times (TILLUM\_TILLUM\_CALIB) + COEFF\_SENSOR \times (TSENSOR\_TSENSOR\_CALIB)$

Calibration Scale

where

• calibration scale is calculated as per Table 21.

(20)

When de-aliasing is not used, the final phase value given out by the OPT8320 is calculated by Equation 21:

Corrected Phase =

(21)

When de-aliasing is used, phase correction on individual frequency measurements is applied before combining the phase information to compute the final unambiguous phase. The OPT8320 provides separate correction blocks for measurements using each frequency because individual frequency measurements can have different offsets and temperature coefficients. The temperature coefficients for the supplementary frequency are internally computed using the coefficients for the base frequency. When de-aliasing is used, for the purpose of calibration, streaming of individual frequency data can be enabled in place of de-aliased data by setting the DEALIAS\_EN parameter to 0.

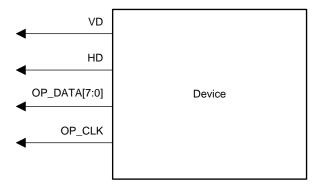

#### 7.3.5 Output Data Interface

The OPT8320 has a programmable parallel CMOS output interface module that gives an option to interface the device to a wide variety of host processors. The output signals are shown in Figure 8 and listed in Table 22.

Figure 8. Output Block Diagram

**Table 22. Output Interface**

| PIN NAMES    | DESCRIPTION                                                                                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP_CLK       | Output interface clock. All output interface signals transition on the configured (positive or negative) edge of this clock.                                                                              |

| OP_DATA[7:0] | Output CMOS data pins. By default, all pins are used for transfer of data. In 4-lane mode, only DATA[3:0] are used. In 1-lane SSI mode, DATA[3] is used as OP_CS and DATA[4] is used as the data out pin. |

| HD           | This signal is used as the horizontal sync in DVP mode to indicate row data transfer.                                                                                                                     |

| VD           | Frame sync. This pin is used to indicate the beginning of a new frame.                                                                                                                                    |

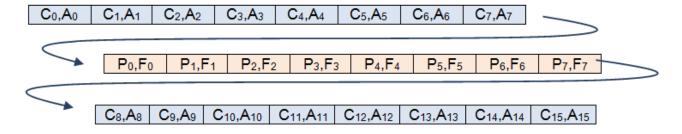

#### 7.3.5.1 Output Data Format

The depth information can be arranged in various configurations as per the host application requirements using register controls.

#### 7.3.5.1.1 Arrangement of Bytes

Each pixel data are represented using 32 bits of data. This data can be broken down into:

- 12 bits of amplitude (C) data

- 4 bits of ambient (A) data

- 12 bits of phase (P) data

- 4 bits of flags (F) data

The structure of the 32-bit data is shown in Table 23.

BYTE 3 BYTE 2 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 PHASE[11:0] FLAGS[3:0] BYTE 1 BYTE 0 14 12 10 9 7 6 5 4 2 0 15 13 11 8 AMBIENT[3:0] AMPLITUDE[11:0]

Table 23. 4-Byte Mode Word Structure

Ambient and amplitude information together form a 16-bit word with ambient data in the MSBs. Flags and phase information together form a 16-bit word with flags data in the MSBs. Data are grouped in sets of eight words to enable efficient arithmetic at the host processor. Within the 16-bit words, the least significant byte is output first, as shown in Figure 9.

Figure 9. Group-by-8 Mode

# 7.3.5.2 Data Output Waveforms

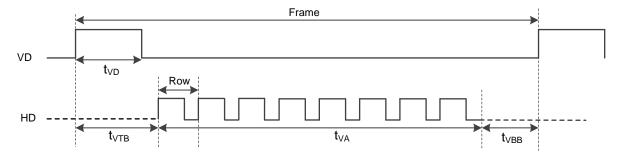

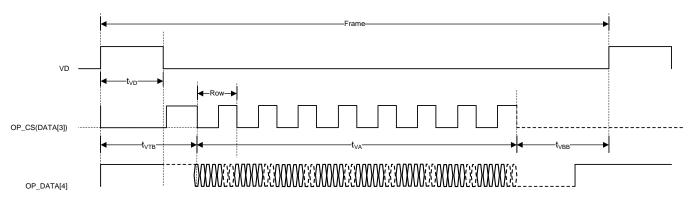

The VD output toggles after the end of the last quad readout in every frame. Depending on the configured output mode, the relation of VD with the data output changes. This section describes the output waveforms for the supported output modes.

#### 7.3.5.2.1 8-Lane Mode: DVP

DVP mode outputs the array data row by row. A frame marker and a row marker are used to indicate the frame and row boundaries respectively. Output data order is least significant byte first. The output timing is shown in Figure 10 and Figure 11.

Figure 10. DVP Frame Format

Figure 11. DVP Line Format

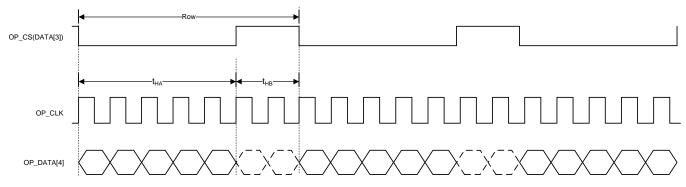

The timing notations are listed in Table 24 and the relevant parameters are listed in Table 25.

**Table 24. DVP Timing Notations**

| TIMING NOTATION  | DESCRIPTION                   | PROGRAMMABLE OR CALCULATED                                     |

|------------------|-------------------------------|----------------------------------------------------------------|

| t <sub>VD</sub>  | Vertical sync time            | Programmable using the VD_ACTIVE parameter                     |

| t <sub>VTB</sub> | Vertical top blanking time    | Programmable using the FRM_BLANK_SIZE and VD_ACTIVE parameters |

| t <sub>VA</sub>  | Vertical active time          | Calculated from ROI and binning settings                       |

| t <sub>VBB</sub> | Vertical bottom blanking time | Internally always set to 0                                     |

| t <sub>HA</sub>  | Horizontal active time        | Calculated from ROI and binning settings                       |

| t <sub>HB</sub>  | Horizontal blanking time      | Programmable using the LINE_BLANK_SIZE parameter               |

#### **Table 25. DVP Parameters**

| PARAMETER   | DESCRIPTION                                                           |

|-------------|-----------------------------------------------------------------------|

| HD_POL      | Polarity of the HD signal.                                            |

| VD_POL      | Polarity of the VD signal.                                            |

| OP_MODE     | 0 = DVP mode<br>1 = Serial mode                                       |

| OP_CS_POL   | Polarity of the OP_CS signal.  0 = Active low  1 = Active high        |

| OP_CLK_FREQ | Output clock frequency.  0 = 24 MHz  1 = 12 MHz  2 = 6 MHz  3 = 3 MHz |

#### 7.3.5.2.2 1-Lane Mode: SSI

Chip select (OP\_CS) indicates the validity of the data presented on the OP\_DATAx (where x = 0 to 7) pin. For example, if a block-blanking period of two clocks and a block size of four bytes are programmed, OP\_CS remains inactive for two clocks and remains active for 32 clock cycles. The timing for this mode is shown in Figure 12 and Figure 13. The related notations are listed in Table 24. The related register controls are listed in Table 25.

A continuing sequence of bytes containing FFh is inserted in the beginning of each frame to indicate the start of frame in this mode. The valid data of the first pixel are the set of bytes following the last FFh in the beginning of the frame.

Figure 12. 1-Lane SSI Mode Frame Timing Diagram

Figure 13. 1-Lane SSI Mode Line Timing Diagram

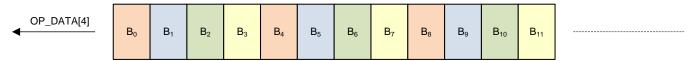

#### 7.3.5.2.2.1 Serialization Logic in 1-Lane Mode

Each byte of data is serialized and sent out on OP\_DATA[4]. Within each byte, the LSB is sent out first. The serialization logic is diagrammatically shown in Figure 14.

Figure 14. Serialization in 1-Lane SSI Mode

#### 7.3.6 Temperature Sensor

The device has an internal temperature sensor to monitor the temperature of the sensor core. The output of the temperature sensor is accessible from a register (*TEMP\_SENSOR*). The sensor temperature can be used for the built-in temperature calibration. Temperature data are automatically updated every frame.

#### 7.3.7 Slave I<sup>2</sup>C Interface

The sensor can be configured by the host processor through an I<sup>2</sup>C interface. All registers have update mechanism controls. For example, the registers that affect frame size (such as ROI) are updated only on frame VD. The update control mechanism makes register writes easy because the write operation can happen at any point of time without taking into account the state of the sensor.