## **TLV320AIC23** Stereo Audio CODEC, 8- to 96-kHz, With Integrated Headphone Amplifier

# Data Manual

MAY 2002

**Digital Audio Products**

SLWS106D

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

## Contents

| Se | ection |           | Title                                         | Page |

|----|--------|-----------|-----------------------------------------------|------|

| 1  | Introd | luction . |                                               | 1–1  |

|    | 1.1    |           | 9S                                            | 1–1  |

|    | 1.2    |           | nal Block Diagram                             | 1–3  |

|    | 1.3    |           | al Assignments                                | 1–4  |

|    | 1.4    | Orderin   | g Information                                 | 1–4  |

|    | 1.5    | Termina   | al Functions                                  | 1–5  |

| 2  | Speci  | fications | 5                                             | 2–1  |

|    | 2.1    |           | e Maximum Ratings Over Operating Free-Air     | 0.4  |

|    | 0.0    |           | ature Range                                   | 2–1  |

|    | 2.2    |           | mended Operating Conditions                   | 2–1  |

|    | 2.3    | Conditio  | al Characteristics Over Recommended Operating | 2–2  |

|    |        | 2.3.1     | ADC                                           | 2–2  |

|    |        | 2.3.2     | DAC                                           | 2–3  |

|    |        | 2.3.3     | Analog Line Input to Line Output              | 2–3  |

|    |        | 2.3.4     | Stereo Headphone Output                       | 2–4  |

|    |        | 2.3.5     | Analog Reference Levels                       | 2–4  |

|    |        | 2.3.6     | Digital I/O                                   | 2–4  |

|    |        | 2.3.7     | Supply Current                                | 2–4  |

|    | 2.4    | Digital-I | nterface Timing                               | 2–5  |

|    |        | 2.4.1     | Audio Interface (Master Mode)                 | 2–5  |

|    |        | 2.4.2     | Audio Interface (Slave-Mode)                  | 2–6  |

|    |        | 2.4.3     | Three-Wire Control Interface                  | 2–7  |

|    |        | 2.4.4     | Two-Wire Control Interface                    | 2–7  |

| 3  |        |           | e AIC23                                       | 3–1  |

|    | 3.1    |           | Interfaces                                    | 3–1  |

|    |        | 3.1.1     | SPI                                           | 3–1  |

|    |        | 3.1.2     | 2-Wire                                        | 3–1  |

|    |        | 3.1.3     | Register Map                                  | 3–2  |

|    | 3.2    |           | Interface                                     | 3–5  |

|    |        | 3.2.1     | Line Inputs                                   | 3–5  |

|    |        | 3.2.2     | Microphone Input                              | 3–5  |

|    |        | 3.2.3     | Line Outputs                                  | 3–6  |

|    |        | 3.2.4     | Headphone Output                              | 3-6  |

|    |        | 3.2.5     | Analog Bypass Mode                            | 3–7  |

|    |        | 3.2.6     | Sidetone Insertion                            | 3–7  |

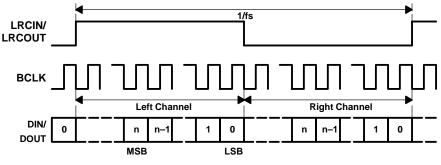

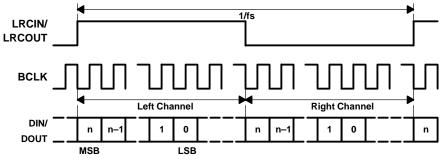

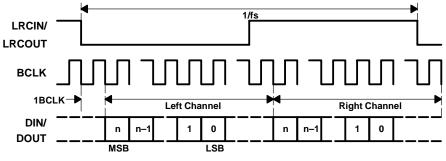

| 3.3    | Digita  | I Audio Interface              | 3–7  |

|--------|---------|--------------------------------|------|

|        | 3.3.1   | Digital Audio-Interface Modes  | 3–7  |

|        | 3.3.2   | Audio Sampling Rates           | 3–9  |

|        | 3.3.3   | Digital Filter Characteristics | 3–11 |

| A Mech | nanical | Data                           | A–1  |

|        |         |                                |      |

# List of Illustrations

| Figur | re Title                                                                                     | Page |

|-------|----------------------------------------------------------------------------------------------|------|

| 2–1   | System-Clock Timing Requirements                                                             | 2–5  |

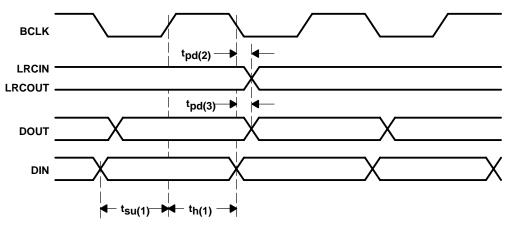

| 2–2   | Master-Mode Timing Requirements                                                              | 2–5  |

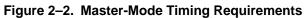

| 2–3   | Slave-Mode Timing Requirements                                                               | 2–6  |

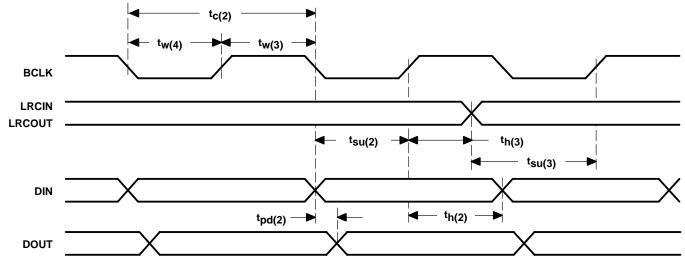

| 2–4   | Three-Wire Control Interface Timing Requirements                                             | 2–7  |

| 2–5   | Two-Wire Control Interface Timing Requirements                                               | 2–7  |

| 3–1   | SPI Timing                                                                                   | 3–1  |

| 3–2   | 2-Wire Compatible Timing                                                                     | 3–2  |

| 3–3   | Analog Line Input Circuit                                                                    | 3–5  |

| 3–4   | Microphone Input Circuit                                                                     | 3–6  |

| 3–5   | Right-Justified Mode Timing                                                                  | 3–7  |

| 3–6   | Left-Justified Mode Timing                                                                   | 3–8  |

| 3–7   | I2S Mode Timing                                                                              | 3–8  |

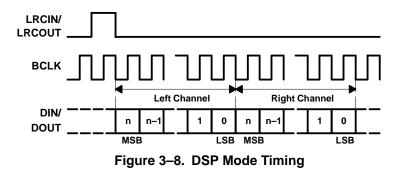

| 3–8   | DSP Mode Timing                                                                              | 3–8  |

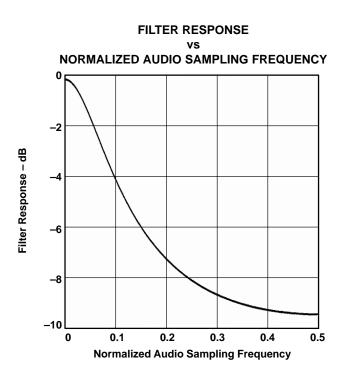

| 3–9   | Digital De-Emphasis Filter Response – 44.1 kHz Sampling                                      | 3–12 |

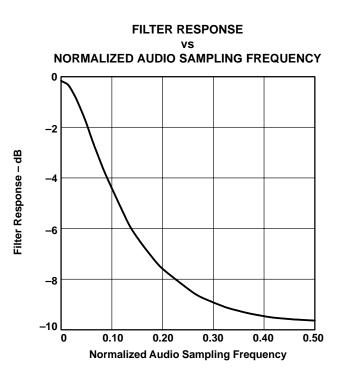

| 3–10  | Digital De-Emphasis Filter Response – 48 kHz Sampling                                        | 3–12 |

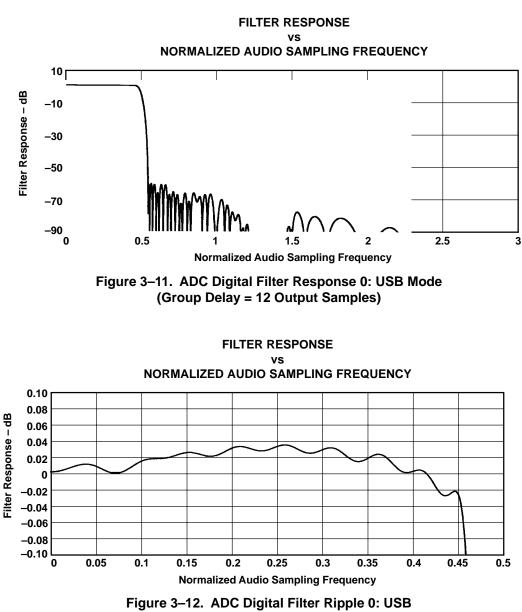

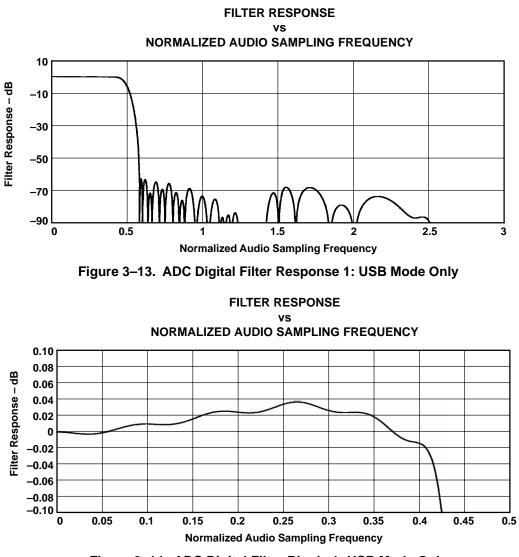

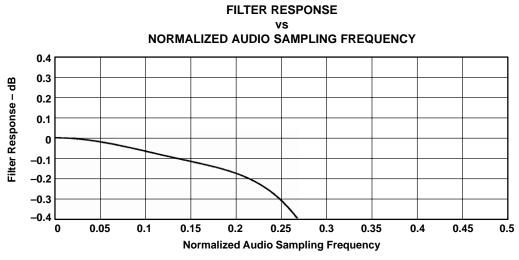

| 3–11  | ADC Digital Filter Response 0: USB Mode                                                      |      |

|       | (Group Delay = 12 Output Samples)                                                            | 3–13 |

| 3–12  | ADC Digital Filter Ripple 0: USB                                                             | 0.40 |

| 0.40  | (Group Delay = 20 Output Samples)                                                            |      |

|       | ADC Digital Filter Response 1: USB Mode Only                                                 |      |

|       | ADC Digital Filter Ripple 1: USB Mode Only                                                   | 3–14 |

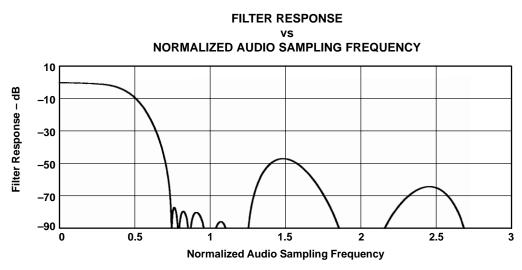

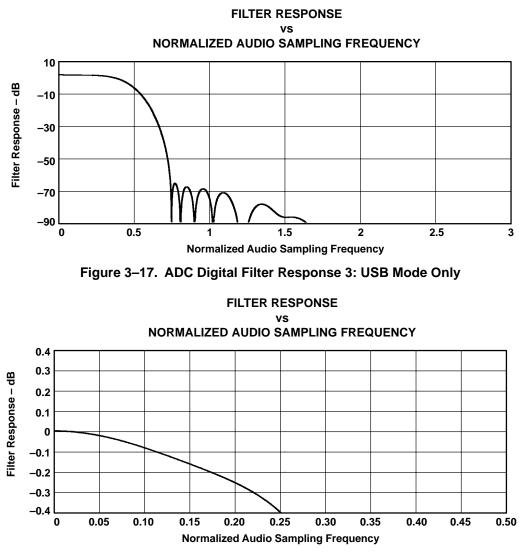

| 3–15  | ADC Digital Filter Response 2: USB mode and Normal Modes<br>(Group Delay = 3 Output Samples) | 3_15 |

| 3_16  | ADC Digital Filter Ripple 2: USB Mode and Normal Modes                                       |      |

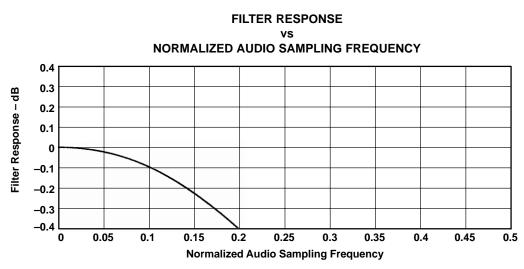

|       | ADC Digital Filter Response 3: USB Mode Only                                                 |      |

|       | ADC Digital Filter Ripple 3: USB Mode Only                                                   |      |

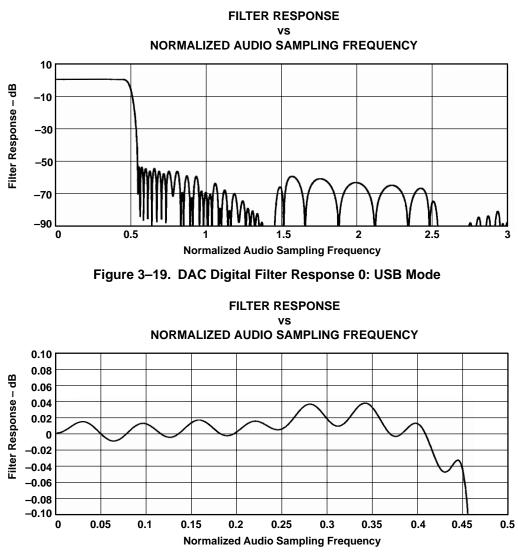

|       | DAC Digital Filter Response 0: USB Mode                                                      |      |

|       | DAC Digital Filter Ripple 0: USB Mode                                                        |      |

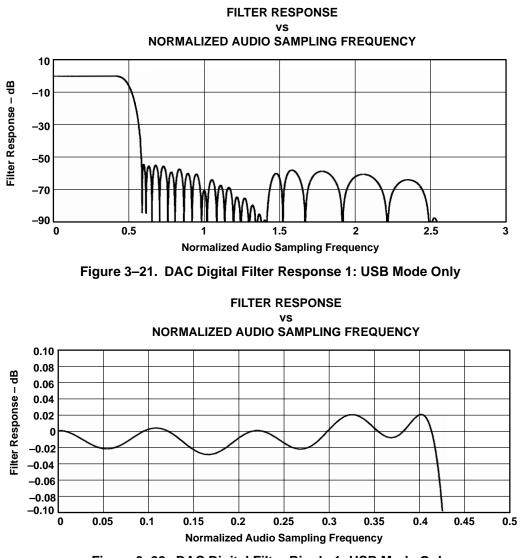

|       | DAC Digital Filter Response 1: USB Mode Only                                                 |      |

|       | DAC Digital Filter Ripple 1: USB Mode Only                                                   |      |

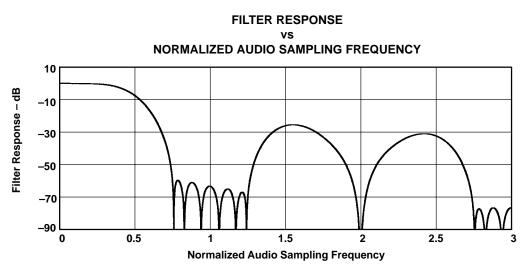

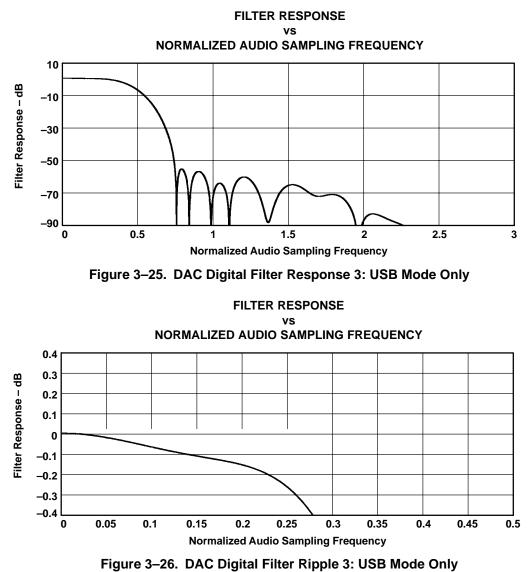

|       | DAC Digital Filter Response 2: USB Mode and Normal Modes                                     |      |

|       | DAC Digital Filter Ripple 2: USB Mode and Normal Modes                                       |      |

|       | DAC Digital Filter Response 3: USB Mode Only                                                 |      |

|       | DAC Digital Filter Ripple 3: USB Mode Only                                                   |      |

| 5 20  |                                                                                              | 5 20 |

## **1** Introduction

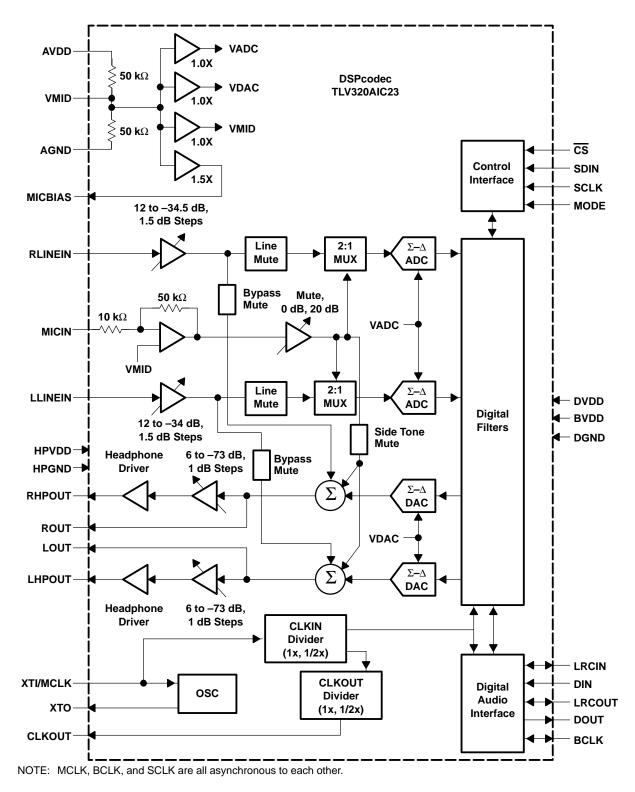

The TLV320AIC23 is a high-performance stereo audio codec with highly integrated analog functionality. The analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) within the TLV320AIC23 use multibit sigma-delta technology with integrated oversampling digital interpolation filters. Data-transfer word lengths of 16, 20, 24, and 32 bits, with sample rates from 8 kHz to 96 kHz, are supported. The ADC sigma-delta modulator features third-order multibit architecture with up to 90-dBA signal-to-noise ratio (SNR) at audio sampling rates up to 96 kHz, enabling high-fidelity audio recording in a compact, power-saving design. The DAC sigma-delta modulator features a second-order multibit architecture with up to 100-dBA SNR at audio sampling rates up to 96 kHz, enabling high-quality digital audio-playback capability, while consuming less than 23 mW during playback only. The TLV320AIC23 is the ideal analog input/output (I/O) choice for portable digital audio-player and recorder applications, such as MP3 digital audio players.

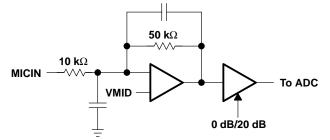

Integrated analog features consist of stereo-line inputs with an analog bypass path, a stereo headphone amplifier, with analog volume control and mute, and a complete electret-microphone-capsule biasing and buffering solution. The headphone amplifier is capable of delivering 30 mW per channel into  $32 \Omega$ . The analog bypass path allows use of the stereo-line inputs and the headphone amplifier with analog volume control, while completely bypassing the codec, thus enabling further design flexibility, such as integrated FM tuners. A microphone bias-voltage output provides a low-noise current source for electret-capsule biasing. The AIC23 has an integrated adjustable microphone amplifier (gain adjustable from 1 to 5) and a programmable gain microphone amplifier (0 dB or 20 dB). The microphone signal can be mixed with the output signals if a sidetone is required.

While the TLV320AIC23 supports the industry-standard oversampling rates of 256  $f_s$  and 384  $f_s$ , unique oversampling rates of 250  $f_s$  and 272  $f_s$  are provided, which optimize interface considerations in designs using TI C54x digital signal processors (DSPs) and universal serial bus (USB) data interfaces. A single 12-MHz crystal can supply clocking to the DSP, USB, and codec. The TLV320AIC23 features an internal oscillator that, when connected to a 12-MHz external crystal, provides a system clock to the DSP and other peripherals at either 12 MHz or 6 MHz, using an internal clock buffer and selectable divider. Audio sample rates of 48 kHz and compact-disc (CD) standard 44.1 kHz are supported directly from a 12-MHz master clock with 250  $f_s$  and 272  $f_s$  oversampling rates.

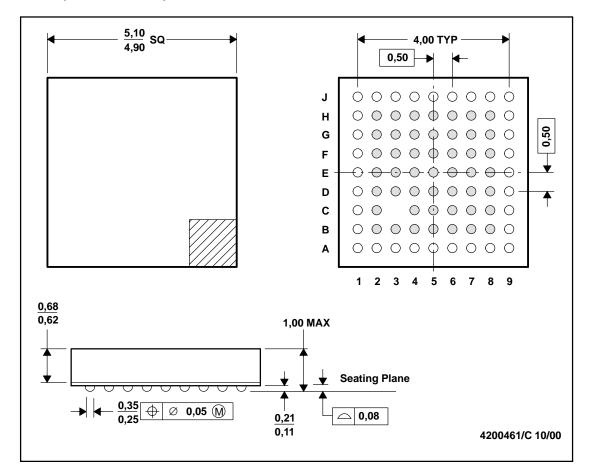

Low power consumption and flexible power management allow selective shutdown of codec functions, thus extending battery life in portable applications. This design solution, coupled with the industry's smallest package, the TI proprietary MicroStar Junior<sup>™</sup> using only 25 mm<sup>2</sup> of board area, makes powerful portable stereo audio designs easily realizable in a cost-effective, space-saving total analog I/O solution: the TLV320AIC23.

## 1.1 Features

- High-Performance Stereo Codec

- 90-dB SNR Multibit Sigma-Delta ADC (A-weighted at 48 kHz)

- 100-dB SNR Multibit Sigma-Delta DAC (A-weighted at 48 kHz)

- 1.42 V 3.6 V Core Digital Supply: Compatible With TI C54x DSP Core Voltages

- 2.7 V 3.6 V Buffer and Analog Supply: Compatible Both TI C54x DSP Buffer Voltages

- 8-kHz 96-kHz Sampling-Frequency Support

- Software Control Via TI McBSP-Compatible Multiprotocol Serial Port

- 2-wire-Compatible and SPI-Compatible Serial-Port Protocols

- Glueless Interface to TI McBSPs

- Audio-Data Input/Output Via TI McBSP-Compatible Programmable Audio Interface

- I<sup>2</sup>S-Compatible Interface Requiring Only One McBSP for both ADC and DAC

- Standard I<sup>2</sup>S, MSB, or LSB Justified-Data Transfers

- 16/20/24/32-Bit Word Lengths

MicroStar Junior is a trademark of Texas Instruments.

- Audio Master/Slave Timing Capability Optimized for TI DSPs (250/272 fs), USB mode

- Industry-Standard Master/Slave Support Provided Also (256/384  $f_s$ ), Normal mode

- Glueless Interface to TI McBSPs

- Integrated Total Electret-Microphone Biasing and Buffering Solution

- Low-Noise MICBIAS pin at 3/4 AVDD for Biasing of Electret Capsules

- Integrated Buffer Amplifier With Tunable Fixed Gain of 1 to 5

- Additional Control-Register Selectable Buffer Gain of 0 dB or 20 dB

- Stereo-Line Inputs

- Integrated Programmable Gain Amplifier

- Analog Bypass Path of Codec

- ADC Multiplexed Input for Stereo-Line Inputs and Microphone

- Stereo-Line Outputs

- Analog Stereo Mixer for DAC and Analog Bypass Path

- Analog Volume Control With Mute

- Highly Efficient Linear Headphone Amplifier

- 30 mW into 32  $\Omega$  From a 3.3-V Analog Supply Voltage

- Flexible Power Management Under Total Software Control

- 23-mW Power Consumption During Playback Mode

- Standby Power Consumption <150 μW</li>

- Power-Down Power Consumption <15  $\mu$ W

- Industry's Smallest Package: 32-Pin TI Proprietary MicroStar Junior™

- 25 mm<sup>2</sup> Total Board Area

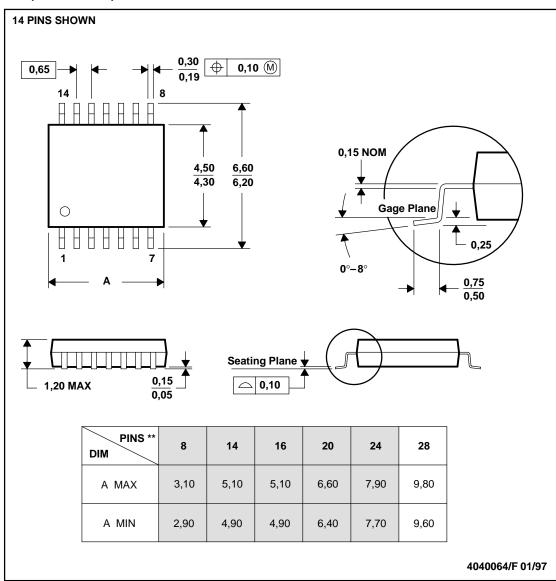

- 28-Pin TSSOP Also Is Available (62 mm<sup>2</sup> Total Board Area)

- Ideally Suitable for Portable Solid-State Audio Players and Recorders

## 1.2 Functional Block Diagram

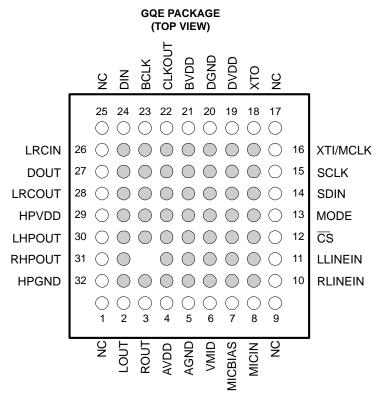

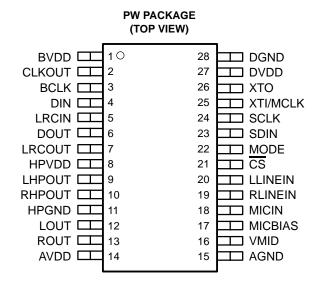

## **1.3 Terminal Assignments**

NC - No internal connection

## 1.4 Ordering Information

|               | PACKAGE                        |                    |  |  |

|---------------|--------------------------------|--------------------|--|--|

| TA            | 32-Pin<br>MicroStar Junior GQE | 28-Pin<br>TSSOP PW |  |  |

| -10°C to 70°C | TLV320AIC23GQE                 | TLV320AIC23PW      |  |  |

| –40°C to 85°C | TLV320AIC23IGQE                | TLV320AIC23IPW     |  |  |

## **1.5 Terminal Functions**

| TERMINAL<br>NO.<br>GOE PW |                |    |     |                                                                                                                                                                                                                               |

|---------------------------|----------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                      | NC             |    | 1/0 | DESCRIPTION                                                                                                                                                                                                                   |

|                           | GQE            | PW |     |                                                                                                                                                                                                                               |

| AGND                      | 5              | 15 |     | Analog supply return                                                                                                                                                                                                          |

| AVDD                      | 4              | 14 |     | Analog supply input. Voltage level is 3.3 V nominal.                                                                                                                                                                          |

| BCLK                      | 23             | 3  | I/O | I <sup>2</sup> S serial-bit clock. In audio master mode, the AIC23 generates this signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                                    |

| BVDD                      | 21             | 1  |     | Buffer supply input. Voltage range is from 2.7 V to 3.6 V.                                                                                                                                                                    |

| CLKOUT                    | 22             | 2  | 0   | Clock output. This is a buffered version of the XTI input and is available in 1X or 1/2X frequencies of XTI.<br>Bit 07 in the sample rate control register controls frequency selection.                                      |

| CS                        | 12             | 21 | I   | Control port input latch/address select. For SPI control mode this input acts as the data latch control. For 2-wire control mode this input defines the seventh bit in the device address field. See Section 3.1 for details. |

| DIN                       | 24             | 4  | I   | I <sup>2</sup> S format serial data input to the sigma-delta stereo DAC                                                                                                                                                       |

| DGND                      | 20             | 28 |     | Digital supply return                                                                                                                                                                                                         |

| DOUT                      | 27             | 6  | 0   | I <sup>2</sup> S format serial data output from the sigma-delta stereo ADC                                                                                                                                                    |

| DVDD                      | 19             | 27 |     | Digital supply input. Voltage range is 1.4 V to 3.6 V.                                                                                                                                                                        |

| HPGND                     | 32             | 11 |     | Analog headphone amplifier supply return                                                                                                                                                                                      |

| HPVDD                     | 29             | 8  |     | Analog headphone amplifier supply input. Voltage level is 3.3 V nominal.                                                                                                                                                      |

| LHPOUT                    | 30             | 9  | 0   | Left stereo mixer-channel amplified headphone output. Nominal 0-dB output level is 1 V <sub>RMS</sub> . Gain of –73 dB to 6 dB is provided in 1-dB steps.                                                                     |

| LLINEIN                   | 11             | 20 | I   | Left stereo-line input channel. Nominal 0-dB input level is 1 V <sub>RMS</sub> . Gain of –34.5 dB to 12 dB is provided in 1.5-dB steps.                                                                                       |

| LOUT                      | 2              | 12 | 0   | Left stereo mixer-channel line output. Nominal output level is 1.0 V <sub>RMS</sub> .                                                                                                                                         |

| LRCIN                     | 26             | 5  | I/O | I <sup>2</sup> S DAC-word clock signal. In audio master mode, the AIC23 generates this framing signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                       |

| LRCOUT                    | 28             | 7  | I/O | I <sup>2</sup> S ADC-word clock signal. In audio master mode, the AIC23 generates this framing signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                       |

| MICBIAS                   | 7              | 17 | 0   | Buffered low-noise-voltage output suitable for electret-microphone-capsule biasing. Voltage level is 3/4 AVDD nominal.                                                                                                        |

| MICIN                     | 8              | 18 | I   | Buffered amplifier input suitable for use with electret-microphone capsules. Without external resistors a default gain of 5 is provided. See Section 2.3.1.2 for details.                                                     |

| MODE                      | 13             | 22 | I   | Serial-interface-mode input. See Section 3.1 for details.                                                                                                                                                                     |

| NC                        | 1, 9<br>17, 25 |    |     | Not Used—No internal connection                                                                                                                                                                                               |

| RHPOUT                    | 31             | 10 | 0   | Right stereo mixer-channel amplified headphone output. Nominal 0-dB output level is 1 V <sub>RMS</sub> . Gain of<br>-73 dB to 6 dB is provided in 1-dB steps.                                                                 |

| RLINEIN                   | 10             | 19 | I   | Right stereo-line input channel. Nominal 0-dB input level is 1 V <sub>RMS</sub> . Gain of –34.5 dB to 12 dB is provided in 1.5-dB steps.                                                                                      |

| ROUT                      | 3              | 13 | 0   | Right stereo mixer-channel line output. Nominal output level is 1.0 V <sub>RMS</sub> .                                                                                                                                        |

| SCLK                      | 15             | 24 | I   | Control-port serial-data clock. For SPI and 2-wire control modes this is the serial-clock input. See Section 3.1 for details.                                                                                                 |

| SDIN                      | 14             | 23 | I   | Control-port serial-data input. For SPI and 2-wire control modes this is the serial-data input and also is used to select the control protocol after reset. See Section 3.1 for details.                                      |

| VMID                      | 6              | 16 | I   | Midrail voltage decoupling input. $10-\mu$ F and $0.1-\mu$ F capacitors should be connected in parallel to this terminal for noise filtering. Voltage level is 1/2 AVDD nominal.                                              |

| XTI/MCLK                  | 16             | 25 | 1   | Crystal or external-clock input. Used for derivation of all internal clocks on the AIC23.                                                                                                                                     |

| ХТО                       | 18             | 26 | 0   | Crystal output. Connect to external crystal for applications where the AIC23 is the audio timing master.<br>Not used in applications where external clock source is used.                                                     |

## 2 Specifications

# 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, AV <sub>DD</sub> to AGND, DV <sub>DD</sub> to DGND, BV <sub>DD</sub> to DGND, HPV <sub>DD</sub> to | o HPGND                              |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| (see Note 1)                                                                                                             | 0.3 V to + 3.63 V                    |

| Analog supply return to digital supply return, AGND to DGND                                                              | –0.3 V to + 3 .63 V                  |

| Input voltage range, all input signals: Digital                                                                          | 0.3 V to DV <sub>DD</sub> + 0.3 V    |

| Analog                                                                                                                   | . –0.3 V to AV <sub>DD</sub> + 0.3 V |

| Case temperature for 10 seconds                                                                                          | 240°C                                |

| Operating free-air temperature range, T <sub>A</sub>                                                                     | –10°C to 70°C                        |

| Storage temperature range, T <sub>stg</sub>                                                                              | –65°C to 150°C                       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: DVDD may not exceed BVDD + 0.3V; BVDD may not exceed AVDD + 0.3V or HPVDD + 0.3.

## 2.2 Recommended Operating Conditions

|                                                                          | MIN  | NOM | MAX   | UNIT             |

|--------------------------------------------------------------------------|------|-----|-------|------------------|

| Analog supply voltage, AV <sub>DD</sub> , HPV <sub>DD</sub> (see Note 2) | 2.7  | 3.3 | 3.6   | V                |

| Digital buffer supply voltage, BV <sub>DD</sub> (see Note 2)             | 2.7  | 3.3 | 3.6   | V                |

| Digital core supply voltage, DV <sub>DD</sub> (see Note 2)               | 1.42 | 1.5 | 3.6   | V                |

| Analog input voltage, full scale – 0dB (AV <sub>DD</sub> = 3.3 V)        |      | 1   |       | V <sub>RMS</sub> |

| Stereo-line output load resistance                                       | 10   |     |       | kΩ               |

| Headphone-amplifier output load resistance                               | 0    |     |       | Ω                |

| CLKOUT digital output load capacitance                                   |      | 20  |       | pF               |

| All other digital output load capacitance                                |      | 10  |       | pF               |

| Stereo-line output load capacitance                                      |      | 50  |       | pF               |

| XTI master clock Input                                                   |      |     | 18.43 | MHz              |

| ADC or DAC conversion rate                                               |      |     | 96    | kHz              |

| Operating free-air temperature, T <sub>A</sub>                           | -10  |     | 70    | °C               |

NOTE 2: Digital voltage values are with respect to DGND; analog voltage values are with respect to AGND.

# 2.3 Electrical Characteristics Over Recommended Operating Conditions, $AV_{DD}$ , $HPV_{DD}$ , $BV_{DD} = 3.3$ V, $DV_{DD} = 1.5$ V, Slave Mode, XTI/MCLK = 256fs, $f_s = 48$ kHz (unless otherwise stated)

## 2.3.1 ADC

#### 2.3.1.1 Line Input to ADC

| PARAMETER                                                 | TEST CONDITIONS                                     | MIN   | TYP | MAX | UNIT |

|-----------------------------------------------------------|-----------------------------------------------------|-------|-----|-----|------|

| Input signal level (0 dB)                                 |                                                     |       | 1   |     | VRMS |

| Signal-to-noise ratio, A-weighted, 0-dB gain (see Notes 3 | f <sub>S</sub> = 48 kHz (3.3 V)                     | 85    | 90  |     | dB   |

| and 4)                                                    | f <sub>S</sub> = 48 kHz (2.7 V)                     |       | 90  |     | αв   |

| Dynamic range, A-weighted, –60-dB full-scale input (see   | $AV_{DD} = 3.3 V$                                   | 85    | 90  |     | dB   |

| Note 4)                                                   | $AV_{DD} = 2.7 V$                                   |       | 90  |     | uБ   |

| Total hormonic distortion 1 dD input 0 dD agin            | $AV_{DD} = 3.3 V$                                   |       | -80 |     | ٦Þ   |

| Total harmonic distortion, -1-dB input, 0-dB gain         | AV                                                  |       |     |     |      |

| Power supply rejection ratio                              | 1 kHz, 100 mV <sub>pp</sub>                         |       | 50  |     | dB   |

| ADC channel separation                                    | 1 kHz input tone                                    |       | 90  |     | dB   |

| Programmable gain                                         | 1 kHz input tone, R <sub>SOURCE</sub> < 50 $\Omega$ | -34.5 |     | 12  | dB   |

| Programmable gain step size                               | Monotonic                                           |       | 1.5 |     | dB   |

| Mute attenuation                                          | 0 dB, 1 kHz input tone                              |       | 80  |     | dB   |

|                                                           | 12 dB Input gain                                    | 10    |     | 20  | ko   |

| Input resistance                                          | 0 dB input gain                                     | 30    | 35  |     | kΩ   |

| Input capacitance                                         |                                                     |       | 10  |     | pF   |

NOTES: 3. Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

4. All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

# 2.3.1.2 Microphone Input to ADC, 0-dB Gain, $f_s = 8 \text{ kHz}$ (40-K $\Omega$ Source Impedance, see Section 1.2, *Functional Block Diagram*)

| PARAMETER                                                        | TEST CONDITIONS                                 | MIN | TYP | MAX                                                                | UNIT             |  |

|------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------------------------------------------------------|------------------|--|

| Input signal level (0 dB)                                        |                                                 |     | 1.0 |                                                                    | V <sub>RMS</sub> |  |

| Signal-to-noise ratio, A-weighted, 0-dB gain (see Notes 3 and 4) | $AV_{DD} = 3.3 V$                               | 80  | 85  |                                                                    | dB               |  |

| Signal-to-holse fatto, A-weighted, 0-db gain (see Notes 3 and 4) | $AV_{DD} = 2.7 V$                               |     | 84  |                                                                    | uБ               |  |

| Dynamic range, A-weighted, -60-dB full-scale input (see Note 4)  | $AV_{DD} = 3.3 V$                               | 80  | 85  |                                                                    | dB               |  |

| Dynamic range, A-weighted, -00-db ruii-scale input (see Note 4)  | $AV_{DD} = 2.7 V$                               |     | 84  |                                                                    | uБ               |  |

| Total harmonic distantion 1 dD input 0 dD anin                   | $AV_{DD} = 3.3 V$                               |     | -60 |                                                                    | dB               |  |

| Total harmonic distortion, -1-dB input, 0-dB gain                | $AV_{DD} = 2.7 V$                               |     | -60 | 0<br>5<br>4<br>5<br>4<br>0<br>0<br>0<br>0<br>0<br>4<br>0<br>4<br>4 | uВ               |  |

| Power supply rejection ratio                                     | 1 kHz, 100 mV <sub>pp</sub>                     |     | 50  |                                                                    | dB               |  |

| Programmable gain boost                                          | 1 kHz input tone, RSOURCE < 50 $\Omega$         |     | 20  |                                                                    | dB               |  |

| Microphone-path gain                                             | MICBOOST = 0, R <sub>SOURCE</sub> < 50 $\Omega$ |     | 14  |                                                                    | dB               |  |

| Mute attenuation                                                 | 0 dB, 1 kHz input tone                          | 60  | 80  |                                                                    | dB               |  |

| Input resistance                                                 |                                                 | 8   | 14  |                                                                    | kΩ               |  |

| Input capacitance                                                |                                                 |     | 10  |                                                                    | pF               |  |

NOTES: 3. Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

4. All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

#### 2.3.1.3 Microphone Bias

| PARAMETER            | TEST CONDITIONS | MIN              | TYP      | MAX              | UNIT   |

|----------------------|-----------------|------------------|----------|------------------|--------|

| Bias voltage         |                 | 3/4 AVDD – 100 m | 3/4 AVDD | 3/4 AVDD + 100 m | V      |

| Bias-current source  |                 |                  |          | 3                | mA     |

| Output noise voltage | 1 kHz to 20 kHz |                  | 25       |                  | nV/√Hz |

#### 2.3.2 DAC

#### 2.3.2.1 Line Output, Load = 10 k $\Omega$ , 50 pF

| PARAMETER                                                            | TEST CO                    | ONDITIONS               | MIN | TYP | MAX | UNIT |  |

|----------------------------------------------------------------------|----------------------------|-------------------------|-----|-----|-----|------|--|

| 0-dB full-scale output voltage (FFFFF)                               |                            |                         |     | 1.0 |     | VRMS |  |

| Signal-to-noise ratio, A-weighted, 0-dB gain (see Notes 3, 4, and 5) | AV <sub>DD</sub> = 3.3 V   | f <sub>S</sub> = 48kHz  | 90  | 100 |     | dB   |  |

| Signal-to-hoise ratio, A-weighted, 0-dB gain (see Notes 3, 4, and 5) | AV <sub>DD</sub> = 2.7 V   | f <sub>S</sub> = 48 kHz |     | 100 |     | uБ   |  |

| Dynamic range, A-weighted (see Note 4)                               | AV <sub>DD</sub> = 3.3 V   |                         | 85  | 90  |     | dB   |  |

| Dynamic range, A-weighted (see Note 4)                               | $AV_{DD} = 2.7 V$          |                         |     | TBD |     | uВ   |  |

|                                                                      | AV = 3.3 V                 | 1 kHz, 0 dB             |     | -88 | -80 | dB   |  |

| Total harmonic distortion                                            | AvDD = 3.3 v               | 1 kHz, –3 dB            |     | -92 | -86 | uВ   |  |

|                                                                      | AV = 2.7 V                 | 1 kHz, 0 dB             |     | -85 |     | dB   |  |

|                                                                      | AVDD = 2.7 V               | 1 kHz, –3 dB            |     | -88 |     | uБ   |  |

| Power supply rejection ratio                                         | 1 kHz, 100 mV <sub>p</sub> | p                       |     | 50  |     | dB   |  |

| DAC channel separation                                               |                            |                         |     | 100 |     | dB   |  |

NOTES: 3. Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

4. All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

5. Ratio of output level with 1-kHz full-scale input, to the output level with all zeros into the digital input, measured A-weighted over a 20-Hz to 20-kHz bandwidth.

## 2.3.3 Analog Line Input to Line Output (Bypass)

| PARAMETER                                                        | TEST CO                  | ONDITIONS            | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------|--------------------------|----------------------|-----|-----|-----|------|

| 0-dB full-scale output voltage                                   |                          |                      |     | 1.0 |     | VRMS |

| Signal to paigo ratio. A weighted 0 dP gain (and Noton 2 and 4)  | AV <sub>DD</sub> = 3.3 V |                      | 90  | 95  |     | dB   |

| Signal-to-noise ratio, A-weighted, 0-dB gain (see Notes 3 and 4) | AV <sub>DD</sub> = 2.7 V | -                    |     | 95  |     | uБ   |

|                                                                  |                          | 1 kHz, 0 dB          |     | -86 | -80 | dB   |

| Total harmonic distortion                                        | AV <sub>DD</sub> = 3.3 V | 1 kHz, -3 dB -92 -86 | uВ  |     |     |      |

| Total harmonic distortion                                        |                          | 1 kHz, 0 dB          |     | -86 |     | - Ch |

|                                                                  | $AV_{DD} = 2.7 V$        | 1 kHz, –3 dB         |     | -92 |     | dB   |

| Power supply rejection ratio                                     | 1 kHz, 100 mVp           | р                    |     | 50  |     | dB   |

| DAC channel separation (left to right)                           | 1 kHz, 0 dB              |                      |     | 80  |     | dB   |

NOTES: 3. Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

4. All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

## 2.3.4 Stereo Headphone Output

| PARAMETER                                      | TEST CO                     | TEST CONDITIONS          |  | TYP | MAX | UNIT             |

|------------------------------------------------|-----------------------------|--------------------------|--|-----|-----|------------------|

| 0-dB full-scale output voltage                 |                             |                          |  | 1.0 |     | V <sub>RMS</sub> |

| Maximum output power, PO                       | RL = 32 Ω                   |                          |  | 30  |     |                  |

|                                                | RL = 16 Ω                   | R <sub>L</sub> = 16 Ω    |  | 40  |     | mW               |

| Signal-to-noise ratio, A-weighted (see Note 4) | AV <sub>DD</sub> = 3.3 V    | AV <sub>DD</sub> = 3.3 V |  | 97  |     | dB               |

| Total harmonic distortion                      | AV <sub>DD</sub> = 3.3 V,   | P <sub>O</sub> = 10 mW   |  |     | 0.1 | %                |

|                                                | 1 kHz output                | P <sub>O</sub> = 20 mW   |  |     | 1.0 | 70               |

| Power supply rejection ratio                   | 1 kHz, 100 mV <sub>pp</sub> | -                        |  | 50  |     | dB               |

| Programmable gain                              | 1 kHz output                | 1 kHz output             |  |     | 6   | dB               |

| Programmable-gain step size                    |                             |                          |  | 1   |     | dB               |

| Mute attenuation                               | 1 kHz output                |                          |  | 80  |     | dB               |

NOTE 4: All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

## 2.3.5 Analog Reference Levels

| PARAMETER          | MIN            | TYP | MAX            | UNIT |

|--------------------|----------------|-----|----------------|------|

| Reference voltage  | AVDD/2 – 50 mV |     | AVDD/2 + 50 mV | V    |

| Divider resistance | 40             | 50  | 60             | kΩ   |

## 2.3.6 Digital I/O

|     | PARAMETER         | MIN                 | TYP | MAX                 | UNIT |

|-----|-------------------|---------------------|-----|---------------------|------|

| VIL | Input low level   |                     |     | $0.3 	imes BV_{DD}$ | V    |

| VIH | Input high level  | $0.7 	imes BV_{DD}$ |     |                     | V    |

| VOL | Output low level  |                     |     | $0.1 	imes BV_{DD}$ | V    |

| VOH | Output high level | $0.9 	imes BV_{DD}$ |     |                     | V    |

## 2.3.7 Supply Current

|      | PARAMETER                                |                                                             |                     | MIN | TYP  | MAX | UNIT |

|------|------------------------------------------|-------------------------------------------------------------|---------------------|-----|------|-----|------|

|      |                                          | Record and playback (all ac                                 | tive)               |     | 23   |     |      |

|      |                                          | Record and playback (osc, clk, and MIC output powered down) |                     |     | 18   |     |      |

|      |                                          | Line playback only                                          |                     |     | 7    |     |      |

| Ітот | Total supply current,<br>No input signal | Record only                                                 |                     |     | 13   |     | mA   |

|      | No input signal                          | Analog bypass (line in to line                              | e out)              |     | 4    |     |      |

|      |                                          | Power down                                                  | Oscillator enabled  |     | 1.5  |     |      |

|      |                                          |                                                             | Oscillator disabled |     | 0.01 |     |      |

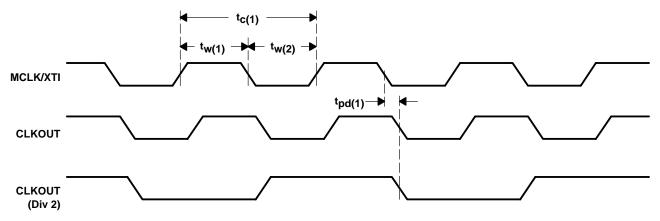

## 2.4 Digital-Interface Timing

|                    | PARAMETER                                    |      | MIN    | TYP MAX | UNIT |

|--------------------|----------------------------------------------|------|--------|---------|------|

| tw(1)              | System-clock pulse duration, MCLK/XTI        | High | 18     |         | 20   |

| tw(2)              |                                              | Low  | 18     |         | ns   |

| <sup>t</sup> c(1)  |                                              |      | 54     |         | ns   |

|                    | Duty cycle, MCLK/XTI                         |      | 40/60% | 60/40%  |      |

| <sup>t</sup> pd(1) | t <sub>pd(1)</sub> Propagation delay, CLKOUT |      | 0      | 10      | ns   |

## Figure 2–1. System-Clock Timing Requirements

## 2.4.1 Audio Interface (Master Mode)

|                    | PARAMETER                       | MIN | ΤΥΡ ΜΑΧ | UNIT |

|--------------------|---------------------------------|-----|---------|------|

| tpd(2)             | Propagation delay, LRCIN/LRCOUT | 0   | 10      | ns   |

| tpd(3)             | Propagation delay, DOUT         | 0   | 10      | ns   |

| t <sub>su(1)</sub> | Setup time, DIN                 | 10  |         | ns   |

| <sup>t</sup> h(1)  | Hold time, DIN                  | 10  |         | ns   |

## 2.4.2 Audio Interface (Slave-Mode)

|                    | PARAMETER               |      | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------|------|-----|-----|-----|------|

| <sup>t</sup> w(3)  | Pulse duration, BCLK    | High | 20  |     |     | ns   |

| tw(4)              | Fuise unation, DOLN     | Low  | 20  |     |     | 115  |

| t <sub>c(2)</sub>  |                         |      | 50  |     |     | ns   |

| tpd(4)             | Propagation delay, DOUT | -    | 0   |     | 10  | ns   |

| t <sub>su(2)</sub> | Setup time, DIN         |      | 10  |     |     | ns   |

| t <sub>h(2)</sub>  | Hold time, DIN          |      | 10  |     |     | ns   |

| t <sub>su(3)</sub> | Setup time, LRCIN       |      | 10  |     |     | ns   |

| th(3)              |                         |      | 10  |     |     | ns   |

Figure 2–3. Slave-Mode Timing Requirements

## 2.4.3 Three-Wire Control Interface (SDIN)

|                    | PARAMETER                                                    |      | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------------------|------|-----|-----|-----|------|

| <sup>t</sup> w(5)  | Clock pulse duration, SCLK                                   | High | 20  |     |     | ns   |

| t <sub>w(6)</sub>  | Clock pulse duration, SOLK                                   | Low  | 20  |     |     | 115  |

| t <sub>c(3)</sub>  | t <sub>c(3)</sub> Clock period, SCLK                         |      | 80  |     |     | ns   |

| t <sub>su(4)</sub> | t <sub>SU(4)</sub> Clock rising edge to CS rising edge, SCLK |      | 60  |     |     | ns   |

| t <sub>su(5)</sub> | t <sub>SU(5)</sub> Setup time, SDIN to SCLK                  |      | 20  |     |     | ns   |

| t <sub>h(4)</sub>  |                                                              |      | 20  |     |     | ns   |

| t <sub>w(7)</sub>  | Pulse duration, $\overline{CS}$                              | High | 20  |     |     | 00   |

| t <sub>w(8)</sub>  |                                                              | Low  | 20  |     |     | ns   |

Figure 2–4. Three-Wire Control Interface Timing Requirements

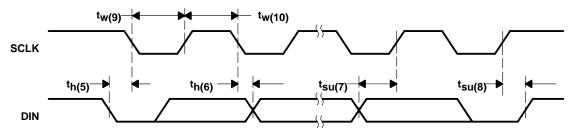

## 2.4.4 Two-Wire Control Interface

|                    | PARAMETER                                      |      | MIN | TYP | MAX | UNIT |    |

|--------------------|------------------------------------------------|------|-----|-----|-----|------|----|

| t <sub>w(9)</sub>  | Clock pulse duration, SCLK                     | High |     | 1.3 |     |      | μs |

| <sup>t</sup> w(10) | Clock pulse duration, SCLK                     | Low  |     | 600 |     |      | ns |

| f(sf)              | f(sf) Clock frequency, SCLK                    |      | 0   |     | 400 | kHz  |    |

| t <sub>h(5)</sub>  | t <sub>h(5)</sub> Hold time (start condition)  |      | 600 |     |     | ns   |    |

| t <sub>su(6)</sub> | Setup time (start condition)                   |      |     | 600 |     |      | ns |

| <sup>t</sup> h(6)  |                                                |      |     |     | 900 | ns   |    |

| t <sub>su(7)</sub> | Data setup time                                |      |     | 100 |     |      | ns |

| tr                 |                                                |      |     |     | 300 | ns   |    |

| t <sub>f</sub>     | tf Fall time, SDIN, SCLK                       |      |     |     | 300 | ns   |    |

| t <sub>su(8)</sub> | t <sub>su(8)</sub> Setup time (stop condition) |      | 600 |     |     | ns   |    |

Figure 2–5. Two-Wire Control Interface Timing Requirements

## 3 How to Use the TLV320AIC23

## 3.1 Control Interfaces

The TLV320AIC23 has many programmable features. The control interface is used to program the registers of the device. The control interface complies with SPI (three-wire operation) and two-wire operation specifications. The state of the MODE terminal selects the control interface type. The MODE pin must be hardwired to the required level.

| MODE | INTERFACE |

|------|-----------|

| 0    | 2-wire    |

| 1    | SPI       |

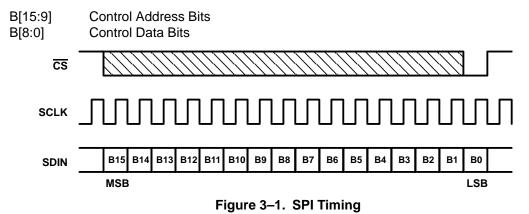

## 3.1.1 SPI

In SPI mode, SDIN carries the serial data, SCLK is the serial clock and  $\overline{CS}$  latches the data word into the TLV320AIC23. The interface is compatible with microcontrollers and DSPs with an SPI interface.

A control word consists of 16 bits, starting with the MSB. The data bits are latched on the rising edge of SCLK. A rising edge on  $\overline{CS}$  after the 16th rising clock edge latches the data word into the AIC (see Figure 3-1).

The control word is divided into two parts. The first part is the address block, the second part is the data block:

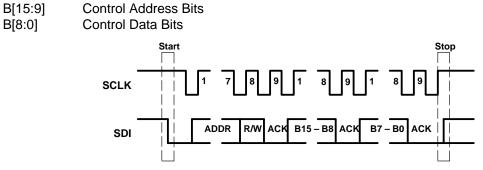

## 3.1.2 2-Wire

In 2-wire mode, the data transfer uses SDIN for the serial data and SCLK for the serial clock. The start condition is a falling edge on SDIN while SCLK is high. The seven bits following the start condition determine which device on the 2-wire bus receives the data. R/W determines the direction of the data transfer. The TLV320AIC23 is a write only device and responds only if R/W is 0. The device operates only as a slave device whose address is selected by setting the state of the CS pin as follows.

| CS STATE<br>(Default = 0) | ADDRESS |

|---------------------------|---------|

| 0                         | 0011010 |

| 1                         | 0011011 |

The device that recognizes the address responds by pulling SDIN low during the ninth clock cycle, acknowledging the data transfer. The control follows in the next two eight-bit blocks. The stop condition after the data transfer is a rising edge on SDIN when SCLK is high (see Figure 3-2).

The 16-bit control word is divided into two parts. The first part is the address block, the second part is the data block:

Figure 3–2. 2-Wire Compatible Timing

## 3.1.3 Register Map

The TLV320AIC23 has the following set of registers, which are used to program the modes of operation.

| ADDRESS | REGISTER                                |

|---------|-----------------------------------------|

| 0000000 | Left line input channel volume control  |

| 0000001 | Right line input channel volume control |

| 0000010 | Left channel headphone volume control   |

| 0000011 | Right channel headphone volume control  |

| 0000100 | Analog audio path control               |

| 0000101 | Digital audio path control              |

| 0000110 | Power down control                      |

| 0000111 | Digital audio interface format          |

| 0001000 | Sample rate control                     |

| 0001001 | Digital interface activation            |

| 0001111 | Reset register                          |

Left line input channel volume control (Address: 000000)

| BIT      | D8  | D7  | D6 | D5 | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|----|----|------|------|------|------|------|

| Function | LRS | LIM | Х  | Х  | LIV4 | LIV3 | LIV2 | LIV1 | LIV0 |

| Default  | 0   | 1   | 0  | 0  | 1    | 0    | 1    | 1    | 1    |

| LRS      | Left/right line simultaneou | us volume/mute u   | update            |

|----------|-----------------------------|--------------------|-------------------|

|          | Simultaneous update         | 0 = Disabled       | 1 = Enabled       |

| LIM      | Left line input mute        | 0 = Normal         | 1 = Muted         |

| LIV[4:0] | Left line input volume cor  | ntrol (10111 = 0 d | lB default)       |

|          | 11111 = +12 dB down to (    | 00000 = -34.5 dB   | 3 in 1.5-dB steps |

| Х        | Reserved                    |                    |                   |

|          |     |     |    |    | ,    |      |      |      |      |

|----------|-----|-----|----|----|------|------|------|------|------|

| BIT      | D8  | D7  | D6 | D5 | D4   | D3   | D2   | D1   | D0   |

| Function | RLS | RIM | Х  | Х  | RIV4 | RIV3 | RIV2 | RIV1 | RIV0 |

| Default  | 0   | 1   | 0  | 0  | 1    | 0    | 1    | 1    | 1    |

Right Line Input Channel Volume Control (Address: 0000001)

RLS Right/left line simultaneous volume/mute update Simultaneous update 0 = Disabled 1 = Enabled RIM Right line input mute 0 = Normal 1 = Muted Right line input volume control (10111 = 0 dB default) RIV[4:0] 11111 = +12 dB down to 00000 = -34.5 dB in 1.5-dB steps Reserved

Х

Left Channel Headphone Volume Control (Address: 0000010)

| BIT      | D8  | D7  | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|------|------|------|------|------|------|------|

| Function | LRS | LZC | LHV6 | LHV5 | LHV4 | LHV3 | LHV2 | LHV1 | LHV0 |

| Default  | 0   | 1   | 1    | 1    | 1    | 1    | 0    | 0    | 1    |

| LRS      | Left/right headphone cha | annel simultaneou  | us volume/mute update                         |

|----------|--------------------------|--------------------|-----------------------------------------------|

|          | Simultaneous update      | 0 = Disabled       | 1 = Enabled                                   |

| LZC      | Left-channel zero-cross  | detect             |                                               |

|          | Zero-cross detect        | 0 = Off            | 1 = On                                        |

| LHV[6:0] | Left Headphone volume    | control (1111001   | = 0 dB default)                               |

|          | 1111111 = +6 dB, 79 step | s between +6 dE    | B and -73 dB (mute), 0110000 = -73 dB (mute), |

|          | any thing below 0110000  | ) does nothing – y | you are still muted                           |

Right Channel Headphone Volume Control (Address: 0000011)

| BIT      | D8  | D7  | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|------|------|------|------|------|------|------|

| Function | RLS | RZC | RHV6 | RHV5 | RHV4 | RHV3 | RHV2 | RHV1 | RHV0 |

| Default  | 0   | 1   | 1    | 1    | 1    | 1    | 0    | 0    | 1    |

| RLS      | Right/left headphone cha | annel simultaneou  | us volume/mute Update                       |

|----------|--------------------------|--------------------|---------------------------------------------|

|          | Simultaneous update      | 0 = Disabled       | 1 = Enabled                                 |

| RZC      | Right-channel zero-cross | s detect           |                                             |

|          | Zero-cross detect        | 0 = Off            | 1 = On                                      |

| RHV[6:0] | Right headphone volume   | e control (1111001 | I = 0 dB default)                           |

|          | 1111111 = +6 dB, 79 step | s between +6 dB    | and -73 dB (mute), 0110000 = -73 dB (mute), |

|          | any thing below 0110000  | does nothing – y   | vou are still muted                         |

Analog Audio Path Control (Address: 0000100)

| BIT                                                    | D8                                | D7                                                                                           | D6                         | D5                                                                               | D4                                                                                | D3                                       | D2       | D1         | D0   |

|--------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------|----------|------------|------|

| Function                                               | Х                                 | STA1                                                                                         | STA0                       | STE                                                                              | DAC                                                                               | BYP                                      | INSEL    | MICM       | MICB |

| Default                                                | 0                                 | 0                                                                                            | 0                          | 0                                                                                | 1                                                                                 | 1                                        | 0        | 1          | 0    |

| STA[1:0]<br>STE<br>DAC<br>BYP<br>INSEL<br>MICM<br>MICB | Side<br>DAC<br>Byp<br>Inpu<br>Mic | etone attent<br>etone enabl<br>C select<br>pass<br>ut select for<br>rophone mu<br>rophone bo | e 0<br>0<br>ADC 0<br>ite 0 | 0 = -6 dB<br>= Disabled<br>= DAC off<br>= Disabled<br>= Line<br>= Normal<br>=OdB | 01 = -9 0<br>1 = Enab<br>1 = DAC<br>1 = Enab<br>1 = Micro<br>1 = Mute<br>1 = 20dE | bled<br>selected<br>bled<br>ophone<br>ed | = –12 dB | 11 = -15 c | IB   |

# Digital Audio Path Control (Address: 0000101)BITD8D7D6

|                                                            | 1                                                                                            | itrol (Addres                                                                  | i                                                                                                            | ,<br>                                                                                                                                                                   |                                                                                                            |                                                                                                          |                                         |                          | i           |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|-------------|

| BIT                                                        | D8                                                                                           | D7                                                                             | D6                                                                                                           | D5                                                                                                                                                                      | D4                                                                                                         | D3                                                                                                       | D2                                      | D1                       | D0          |

| Function                                                   | Х                                                                                            | Х                                                                              | Х                                                                                                            | Х                                                                                                                                                                       | Х                                                                                                          | DACM                                                                                                     | DEEMP1                                  | DEEMP0                   | ADCHP       |

| Default                                                    | 0                                                                                            | 0                                                                              | 0                                                                                                            | 0                                                                                                                                                                       | 0                                                                                                          | 0                                                                                                        | 1                                       | 0                        | 0           |

| DACM<br>DEEMP[1:0<br>ADCHP<br>X<br>Power Dow               | 0] De-<br>AD<br>Res                                                                          | C soft mute<br>emphasis c<br>C high-pass<br>served<br>Address: 00              | ontrol 00<br>filter 0                                                                                        | = Disabled<br>) = Disablec<br>= Disabled                                                                                                                                | 1 = Enat<br>01 = 32  <br>1 = Enat                                                                          | kHz 10 =                                                                                                 | = 44.1 kHz                              | 11 = 48 kł               | Ηz          |

| BIT                                                        | D8                                                                                           | D7                                                                             | D6                                                                                                           | D5                                                                                                                                                                      | D4                                                                                                         | D3                                                                                                       | D2                                      | D1                       | D0          |

| Function                                                   | X                                                                                            | OFF                                                                            | CLK                                                                                                          | OSC                                                                                                                                                                     | OUT                                                                                                        | DAC                                                                                                      | ADC                                     | MIC                      | LINE        |

| Default                                                    | 0                                                                                            | 0                                                                              | 0                                                                                                            | 0                                                                                                                                                                       | 0                                                                                                          | 0                                                                                                        | 1                                       | 1                        | 1           |

| OFF<br>CLK<br>OSC<br>OUT<br>DAC<br>ADC<br>MIC<br>LINE<br>X | Device p<br>Clock<br>Oscillato<br>Outputs<br>DAC<br>ADC<br>Micropho<br>Line inpu<br>Reserved | r<br>one input<br>ut                                                           | 0 = On<br>0 = On<br>0 = On<br>0 = On<br>0 = On<br>0 = On<br>0 = On                                           | 1 = 0<br>1 = 0                                                                                                    | ff<br>ff<br>ff<br>ff<br>ff                                                                                 |                                                                                                          |                                         |                          |             |

| Digital Audi                                               | io Interface                                                                                 | Format (Ad                                                                     | dress: 0000                                                                                                  | )111)                                                                                                                                                                   |                                                                                                            |                                                                                                          |                                         |                          |             |

| BIT                                                        | D8                                                                                           | D7                                                                             | D6                                                                                                           | D5                                                                                                                                                                      | D4                                                                                                         | D3                                                                                                       | D2                                      | D1                       | D0          |

| Function                                                   | Х                                                                                            | Х                                                                              | MS                                                                                                           | LRSWAP                                                                                                                                                                  | LRP                                                                                                        | IWL1                                                                                                     | IWL0                                    | FOR1                     | FOR0        |

| Default                                                    | 0                                                                                            | 0                                                                              | 0                                                                                                            | 0                                                                                                                                                                       | 0                                                                                                          | 0                                                                                                        | 0                                       | 0                        | 1           |

| MS<br>LRSWAP<br>LRP<br>IWL[1:0]<br>FOR[1:0]<br>X           | DA<br>DA<br>Inp<br>Dat                                                                       | ster/slave m<br>C left/right s<br>C left/right p<br>ut bit length<br>ta format | wap 0 :<br>hase 0 :<br>DS<br>1 :<br>DS<br>0 :<br>0 :<br>0 :<br>0 :<br>0 :<br>0 :<br>0 :<br>0 :<br>0 :<br>0 : | = Slave<br>= Disabled<br>= Right cha<br>= Right cha<br>SP mode<br>= MSB is av<br>= MSB is av<br>= 16 bit<br>= DSP forr<br>) = $I^2S$ form<br>= MSB firs<br>) = MSB firs | nnel on, LR<br>railable on 2<br>vailable on<br>01 = 20 l<br>nat, frame s<br>at, MSB firs<br>t, left aligne | oled<br>CIN high<br>CIN low<br>2nd BCLK ri<br>1st BCLK ri<br>bit 10 =<br>sync followe<br>st, left – 1 al | sing edge a<br>= 24 bit<br>ed by two da | fter LRCIN<br>11 = 32 bi | rising edge |

| NOTES: 1.<br>2.<br>3.                                      | In Master mod<br>supplied to the<br>In normal mo<br>BCLK = MCLI<br>In USB mode               | de, the TLV320<br>e TLV320AIC23<br>de, BCLK = M                                | 3.<br>CLK/4 for all s<br>CLK                                                                                 |                                                                                                                                                                         |                                                                                                            |                                                                                                          |                                         |                          |             |

| віт І                                                      | D8                                                                                           | D7                                                                             | D6                                                                                                           | D5                                                                                                                                                                      | D4                                                                                                         | D3                                                                                                       | D2                                      | D1                       | D0          |

| Function                                                   | X                                                                                            | CLKOUT                                                                         | CLKIN                                                                                                        | SR3                                                                                                                                                                     | SR2                                                                                                        | SR1                                                                                                      | SR0                                     | BOSR                     | USB/Normal  |

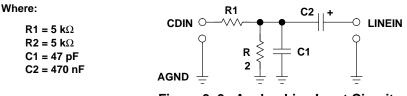

| Default                                                    | 0                                                                                            | 0                                                                              | 0                                                                                                            | 1                                                                                                                                                                       | 0                                                                                                          | 0                                                                                                        | 0                                       | 0                        | 0           |