www.ti.com

# **CLOCK- AND POWER-MANAGEMENT IC FOR RF SYSTEM**

Actual Size 5 mm x 5 mm

#### **FEATURES**

- High Efficiency, 550-mA, Adjustable-Output **Buck Boost DC-DC Converter**

- 6 High Performance LDO With Low Power Mode

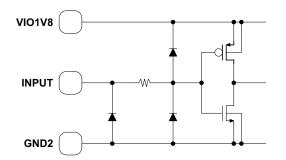

- 2 Analog Switches

- 2 High Performance LDO

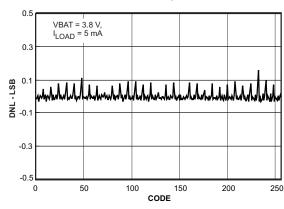

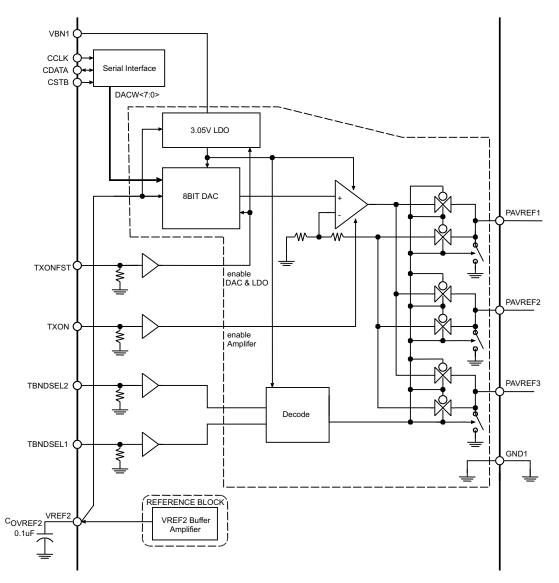

- 3-Channel Selectable Output, 8-Bit Resolution D/A Converter

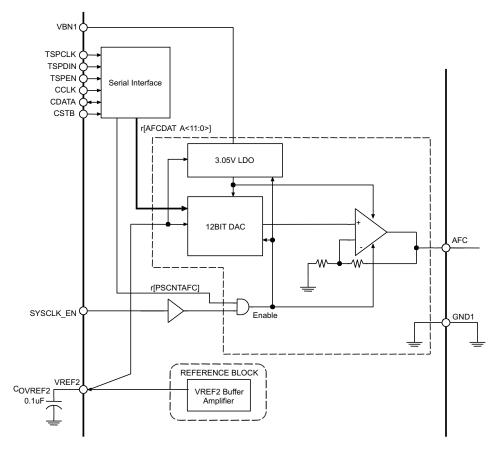

- 12-Bit Resolution D/A Converter

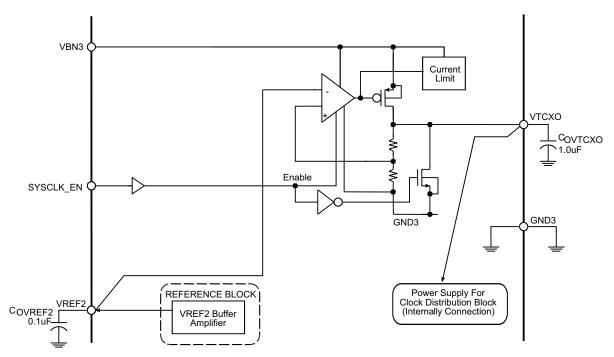

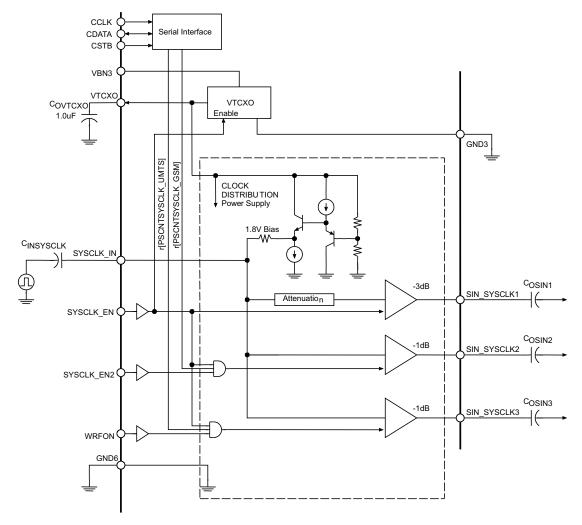

- 3-Channel Clock Buffer of 26 MHz VCTCXO For Clock Reference

- 2 Serial Interface With 3-Wire

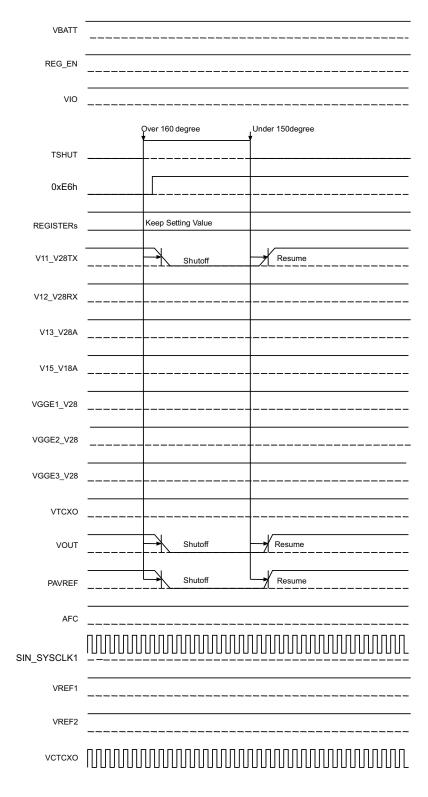

- **Thermal Shut Down Protection**

- Hot-Die Detection For Die Temperature Alert

- 5 mm × 5 mm, 0.5 mm Pitch MicroStar Junior™ Package

#### **APPLICATIONS**

- UMTS/WCDMA/GSM Cellular Phone

- **Smart Phones**

- Wireless Modems

#### DESCRIPTION

The TPS65040 is an advanced RF management chip for cellular phones, providing a highly optimized solution for UMTS/WCDMA/GSM power amplifier applications. This solution improves efficiency by voltage control of the power amplifiers, saving power to prolong battery life. The TPS65040 features buck boost DC/DC converters suited for applications requiring up to 550-mA output current while dynamically adjusting output voltage from 0.8 V to 4.2 V with a fast settling time, high performance 8-channel LDO regulators, 8bit DAC, 12bit ADC and clock distribution buffers of 26 MHz VCTCXO. Each block can be controlled by serial interface and external pins. The TPS65040 offers material cost savings and small size, using a compact 5 mm  $\times$  5 mm MicroStar Junior™ package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# TPS65040 OUTPUT<sup>(1)</sup> AND OPERATIONAL RANGE

| PIN NAME    | PIN NO. | TYPE                                       | V <sub>OUT</sub> (V) | I <sub>OUT</sub> MAX (mA) |

|-------------|---------|--------------------------------------------|----------------------|---------------------------|

| VOUT        | A8, B8  | Buck boost DC/DC converter                 | 0.8~4.2              | 550                       |

| V11_V28TX   | G1      | Normal mode (high PSRR LDO)                | 2.85                 | 130 (2)                   |

| PA_VDD      | F2      | Switch output of V11_V28TX                 | 2.85                 | 20                        |

| V12_V28RX   | E1      | Low power mode/normal mode (high PSRR LDO) | 2.85                 | 95 <sup>(3)</sup>         |

| V_LNA_FEM   | E2      | Switch output of V12_V28RX                 | 2.85                 | 30                        |

| V13_V28A    | D1      | Low power mode/normal mode (high PSRR LDO) | 2.85                 | 50                        |

| V15_V18A    | C2      | Low power mode/normal mode (high PSRR LDO) | 1.85                 | 15                        |

| VGGE1_V28   | H9      | Low power mode/normal mode (high PSRR LDO) | 2.85                 | 150                       |

| VGGE2_V28   | G9      | Low power mode/normal mode (high PSRR LDO) | 2.85                 | 150                       |

| VGGE3_V28   | F9      | Low power mode/normal mode (high PSRR LDO) | 2.85                 | 100                       |

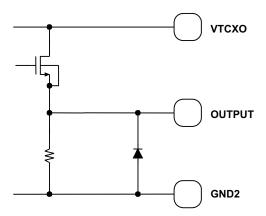

| VTCXO       | J2      | Normal mode (high PSRR LDO)                | 2.85                 | 20                        |

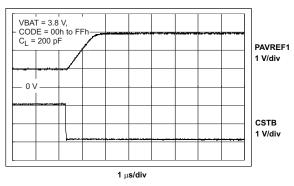

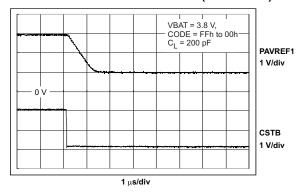

| PAVREF1     | А3      | 8-bit DAC output                           | 0.95~2.9             | 5                         |

| PAVREF2     | A2      | 8-bit DAC output                           | 0.95~2.9             | 5                         |

| PAVREF3     | B1      | 8-bit DAC output                           | 0.95~2.9             | 5                         |

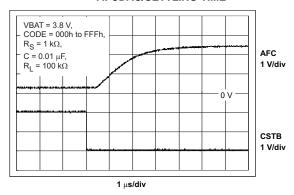

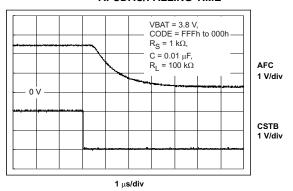

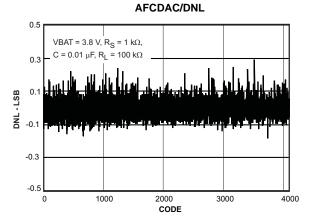

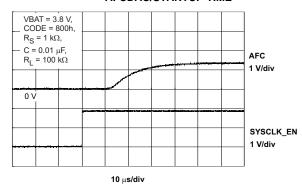

| AFC         | J3      | 12-bit DAC output                          | 0.25~2.45            | 0.025                     |

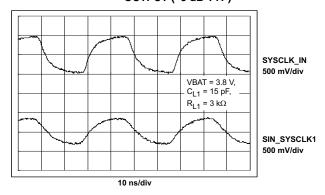

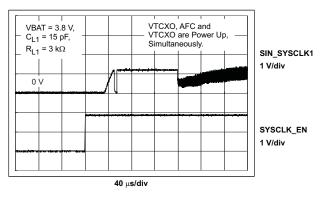

| SIN_SYSCLK1 | J5      | Clock distribution with -3 dB gain         |                      | _                         |

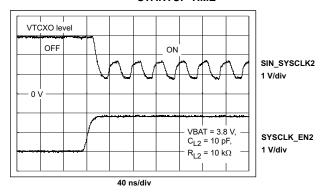

| SIN_SYSCLK2 | J6      | Clock distribution with -1 dB gain         |                      | _                         |

| SIN_SYSCLK3 | J7      | Clock distribution with -1 dB gain         |                      | _                         |

<sup>(1)</sup> All outputs can be controlled by serial interface, except VTCXO, PAVREF1, PAVREF2 and PAVREF3.

<sup>(2)</sup> When the PA\_VDD has load current, the maximum load current of V11\_V28TX is decreased from 130 mA by the value of I<sub>OUT</sub> of PA\_VDD

<sup>(3)</sup> When the V\_LNA\_FEM has load current, the maximum load current of V12\_V28RX is decreased from 95 mA by the value of I<sub>OUT</sub> of V\_LNA\_FEM.

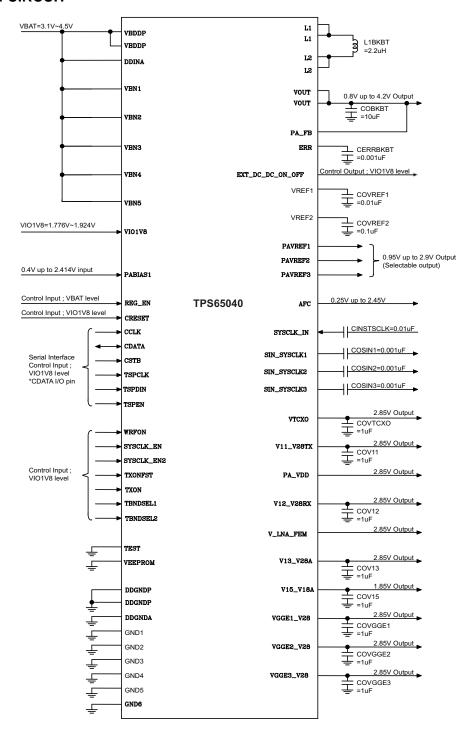

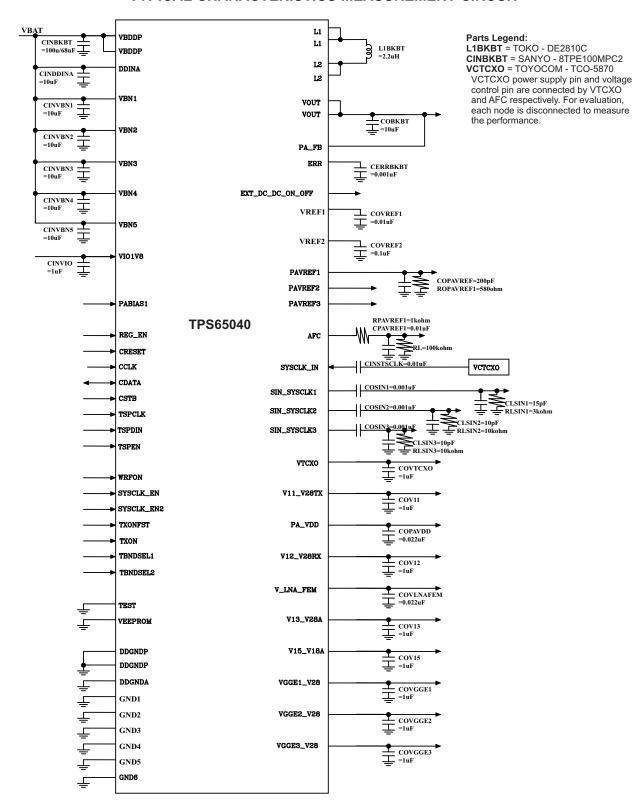

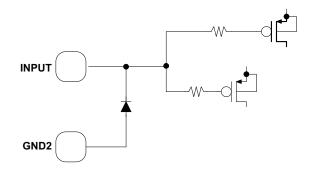

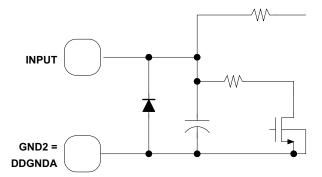

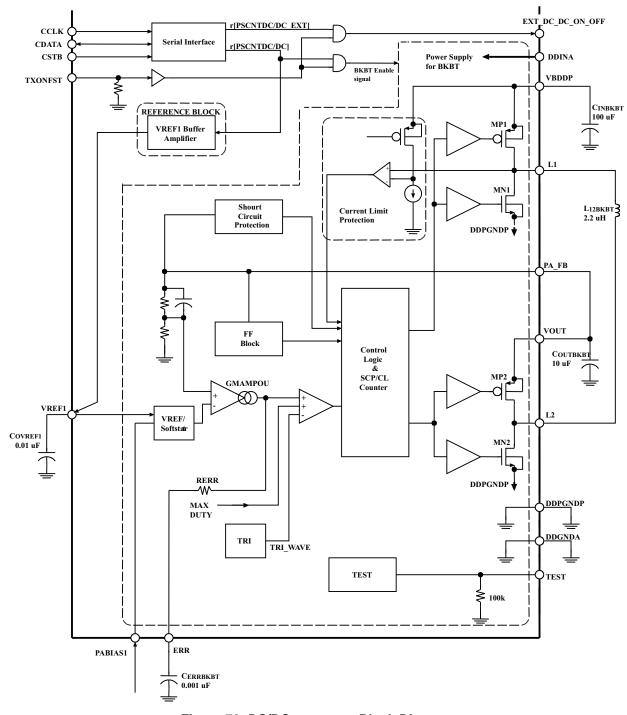

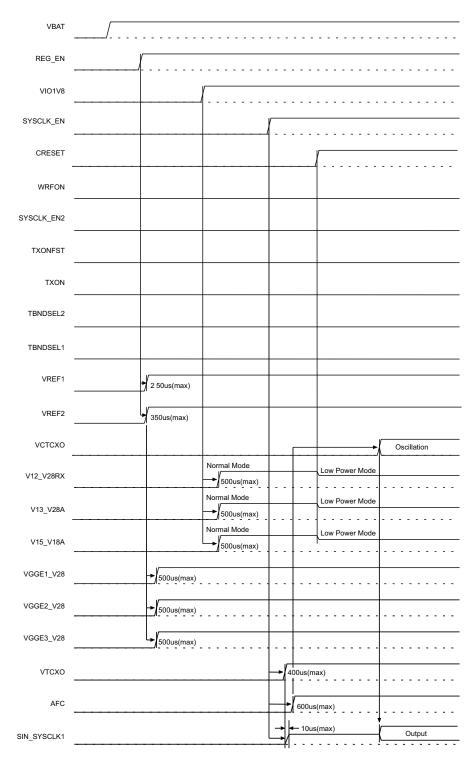

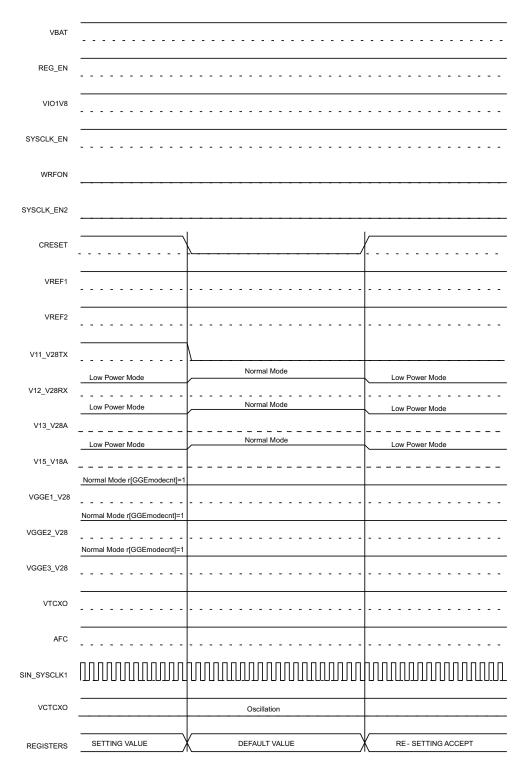

### **APPLICATION CIRCUIT**

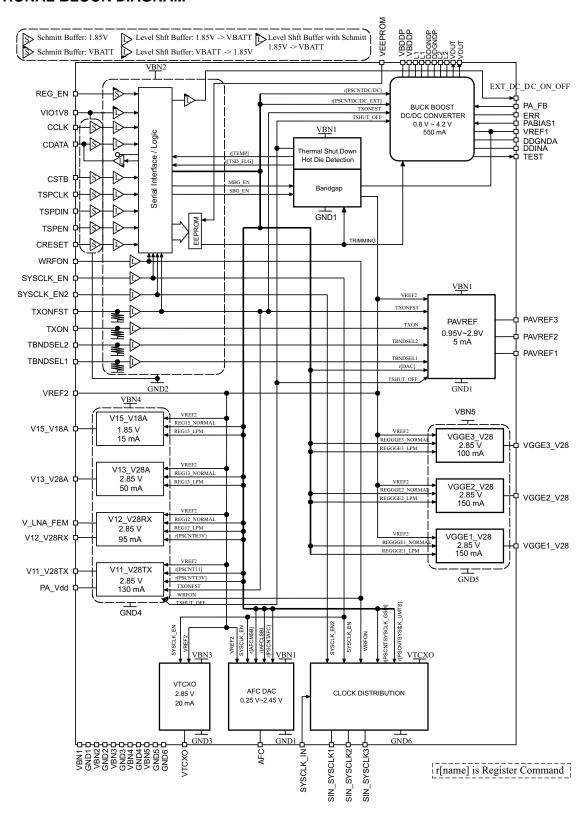

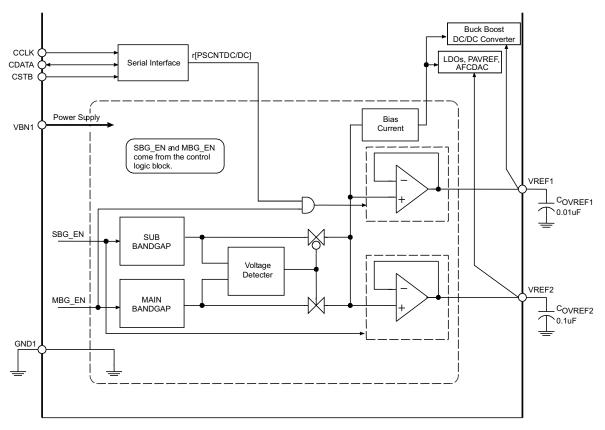

### **FUNCTIONAL BLOCK DIAGRAM**

#### ORDERING INFORMATION

| PART NUMBER | T <sub>A</sub> | PACKAGE <sup>(1)</sup>   | ORDERING    | PACKAGE MARKING |

|-------------|----------------|--------------------------|-------------|-----------------|

| TPS65040    | −30°C to 85°C  | 71-pin MicroStar Junior™ | TPS65040ZQE | PS65040         |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1)

|                    |                                                                       | VALUE              | UNIT |

|--------------------|-----------------------------------------------------------------------|--------------------|------|

|                    | VIO1V8 pin with respect to GND2                                       | -0.3 to 3.3        | V    |

| 111000             | V                                                                     |                    |      |

|                    | VBN2 pin with respect to GND2                                         | -0.3 to 5.5        | V    |

| Cumply valtage     | VBN3 pin with respect to GND3                                         | -0.3 to 5.5        | V    |

| Supply voltage     | VBN4 pin with respect to GND4                                         | -0.3 to 5.5        | V    |

|                    | VBN5 pin with respect to GND5                                         | -0.3 to 5.5        | V    |

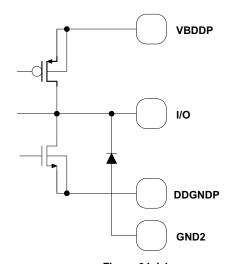

|                    | VBDDP <sup>(2)</sup> pin with respect to DDGNDP <sup>(2)</sup>        | -0.3 to 5.5        | V    |

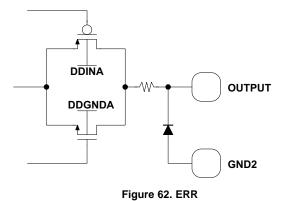

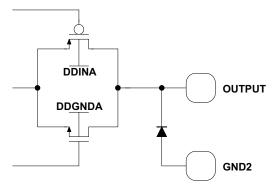

|                    | DDINA pin with respect to DDGNDA                                      | -0.3 to 5.5        | V    |

| Input voltage rang | e on REG_EN pin with respect to GND2                                  | -0.3 to 5.5        | V    |

| Input voltage rang | e on PABIAS1, PA_FB and ERR pins with respect to DDGNDA               | -0.3 to 5.5        | V    |

| Input voltage rang | e <sup>(2)</sup> on L1 and L2 pins with respect to DDGNDP             | -0.3 to 5.5        | V    |

| Input voltage rang | e on other pins <sup>(3)</sup>                                        | -0.3 to 5.5        | V    |

| Input voltage rang | e on SYSCLK_IN pin with respect to GND6                               | -0.3 to 3.3        | V    |

| Input voltage rang | e on other input pins <sup>(4)</sup>                                  | -0.3 to 3.3        | V    |

| Input voltage rang | e on other pins <sup>(5)</sup>                                        | -0.3 to 3.3        | V    |

| Peak LDO and SV    | V output current <sup>(6)</sup>                                       | Internally Limited |      |

| Peak current of po | ower path <sup>(2)</sup> on VBDDP, L1, L2 pins with respect to DDGNDP | 5                  | Α    |

| Storage temperatu  | ıre                                                                   | -40 to 150         | °C   |

| Maximum junction   | temperature                                                           | 125                | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

(2) VBDDP is A4 and B4 pins, L1 is A5 and B5 pins, L2 is A7 and B7 pins, and DDGNDP is A6 and B6 pins.

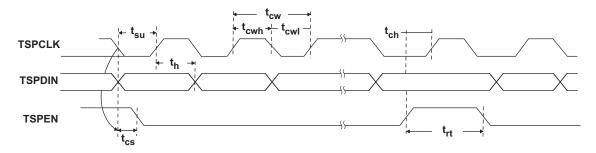

- (4) Pins are CCLK, CDATA, CSTB, TSPCLK, TSPDIN, TSPEN, CRESET, WRFON, TXON, TXONFST, TBNDSEL1, TBNDSEL2, SYSCLK\_EN and SYSCLK\_EN2 with respect to GND2.

- (5) Pins are AFC, PAVREF1, PAVREF2, and PAVREF3 with respect to GND1. Pins are SIN\_SYSCLK1, SIN\_SYSCLK2 and SIN\_SYSCLK3 with respect to GND6.

- (6) LDO and SW OUTPUT are V11\_V28TX, PA\_VDD, V12\_V28RX, V\_LNA\_FEM, V15\_V18A, V13\_V28A, VTCXO, VGGE1\_V28, VGGE2\_V28 and VGGE3\_V28.

#### DISSIPATION RATINGS(1)

| PACKAGE | $R_{	hetaJA}$ | MAX POWER DISSIPATION<br>AT T <sub>A</sub> = 25°C | DERATING FACTOR<br>T <sub>A</sub> < 25°C |

|---------|---------------|---------------------------------------------------|------------------------------------------|

| ZQE     | 51.23°C/W     | 1.95 W                                            | 19.52 mW/°C                              |

#### (1) Test board conditions

- JEDEC High-K (2S2P) board used

- 3x3 inch, 4 layer

- 1 oz copper ground/power trace in the PCB

- 2 oz copper trace on the top/bottom of the PCB

<sup>(3)</sup> Pin is VTCXO with respect to GND3. Pins are VGGE1\_V28, VGGE2\_V28, and VGGE3\_V28 with respect to GND5. Pin is VOUT with respect to DDGNDP. Pin is TEST with respect to DDGNDA.

### **RECOMMENDED OPERATING CONDITIONS**

|                                   |                                                        | MIN   | TYP   | MAX   | UNIT  |

|-----------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| $V_{VIO}$                         | Supply voltage to VIO1V8 input                         | 1.746 |       | 1.924 | V     |

|                                   | Supply voltage to VBN1 input                           | 3.1   |       | 4.5   | V     |

|                                   | Supply voltage to VBN2 input                           | 3.1   |       | 4.5   | V     |

|                                   | Supply voltage to VBN3 input                           | 3.1   |       | 4.5   | V     |

| VBAT <sup>(1)</sup>               | Supply voltage to VBN4 input                           | 3.1   |       | 4.5   | V     |

|                                   | Supply voltage to VBN5 input                           | 3.1   |       | 4.5   | V     |

|                                   | Supply voltage to VBDDP input                          | 3.1   |       | 4.5   | V     |

|                                   | Supply voltage to DDINA input                          | 3.1   |       | 4.5   | V     |

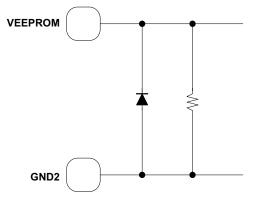

| VROM                              | Supply voltage to VEEPROM input (EEPROM WRITE VOLTAGE) | 13    | 14    | 15    | V     |

| NROM                              | Acceptable number of EEPROM writings <sup>(2)</sup>    |       |       | 10    | times |

| C <sub>OVREF1</sub> (3)           | Output capacitor at VREF1                              |       | 0.01  |       | μF    |

| C <sub>OVREF2</sub> (3)           | Output capacitor at VREF2                              |       | 0.1   |       | μF    |

| C <sub>OUTBKBT</sub> (3)          | Output capacitor at VOUT                               |       | 10    |       | μF    |

| L <sub>I2BKBT</sub>               | Inductor at L1 and L2                                  |       | 2.2   |       | μН    |

| C <sub>ERRBKBT</sub> (3)          | Phase compensation at ERR                              |       | 0.001 |       | μF    |

| C <sub>OV11</sub> (3)             | Output capacitor at V11_V28TX                          |       | 1     |       | μF    |

| C <sub>OV12</sub> <sup>(3)</sup>  | Output capacitor at V12V28R                            |       | 1     |       | μF    |

| C <sub>OV13</sub> (3)             | Output capacitor at V13_V28A                           |       | 1     |       | μF    |

| C <sub>OV15</sub> (3)             | Output capacitor at V15_V28A                           |       | 1     |       | μF    |

| C <sub>OVGGE1</sub> (3)           | Output capacitor at VGGE1_V28                          |       | 1     |       | μF    |

| C <sub>OVGGE2</sub> (3)           | Output capacitor at VGGE2_V28                          |       | 1     |       | μF    |

| C <sub>OVGGE3</sub> (3)           | Output capacitor at VGGE3_V28                          |       | 1     |       | μF    |

| C <sub>OVTCXO</sub> (3)           | Output capacitor at VTCXO                              |       | 1     |       | μF    |

| C <sub>INSYSCLK</sub> (3)         | Input capacitor at SYSCLK_IN                           |       | 0.01  |       | μF    |

| C <sub>OSIN1</sub> (3)            | Output capacitor at SIN_SYSCLK1                        |       | 0.001 |       | μF    |

| C <sub>OSIN2</sub> (3)            | Output capacitor at SIN_SYSCLK2                        |       | 0.001 |       | μF    |

| C <sub>OSIN3</sub> <sup>(3)</sup> | Output capacitor at SIN_SYSCLK3                        |       | 0.001 |       | μF    |

| T <sub>A</sub>                    | Operating ambient temperature                          | -30   |       | 85    | °C    |

| T <sub>J</sub>                    | Operating junction temperature                         | -30   |       | 125   | °C    |

<sup>(1)</sup> VBN1, VBN2, VBN3, VBN4, VBN5, VBDDP and DDINA are the same supply voltage range for VBAT.

(2) This defines the number of customer's writings after shipment from TI.

(3) B characteristics capacitor

# **ELECTRICAL CHARACTERISTICS**

|                          | PARAMETER                                     | TEST CONDITIONS                                                                                          | MIN | TYP | MAX | UNIT |

|--------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| BUCK BOOS                | T DC/DC CONVERTER                             |                                                                                                          |     |     |     | ļ    |

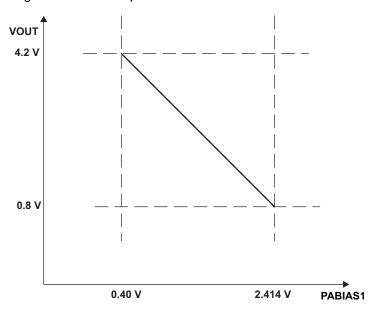

|                          |                                               | PABIAS1 pin = 2.414 V                                                                                    |     | 0.8 |     |      |

| $V_{O(BKBT)}$            | Output voltage                                | PABIAS1 pin = 1.407 V                                                                                    |     | 2.5 |     | V    |

| , ,                      |                                               | PABIAS1 pin = 0.400 V                                                                                    |     | 4.2 |     |      |

| I <sub>O(BKBT)</sub>     | Maximum output current <sup>(1)</sup>         |                                                                                                          |     |     | 550 | mA   |

| V                        | Output valtage geourges                       | VBAT = 3.8 V, $I_{LOAD}$ = 10 $\mu$ A, PABIAS1 pin voltage accuracy = $\pm 0$ mV at $T_A$ = 25°C         | -50 |     | 50  | mV   |

| V <sub>O(BKBT_ACC)</sub> | Output voltage accuracy                       | VBAT = 3.8 V, $I_{LOAD}$ = 10 $\mu$ A, PABIAS1 pin voltage accuracy = $\pm 0$ mV $^{(2)}$                | -80 |     | 80  | IIIV |

| I <sub>SD(BKBT)</sub>    | Shutdown current                              | VBDDP pin and DDINA pin at T <sub>A</sub> = 25°C                                                         |     |     | 1   | μΑ   |

| I <sub>Q(BKBT)</sub>     | Quiescent current                             | DDINA pin, I <sub>LOAD</sub> = 0 mA, PABIAS1 pin = 1.4 V, No External Component, device is not switching |     | 0.8 | 3   | mA   |

| VREG                     | Line Regulation <sup>(2)</sup>                | VBAT = 3.1 V to 4.5 V, I <sub>LOAD</sub> = 400 mA                                                        |     | 20  | 40  | mV   |

| IREG                     | Load Regulation <sup>(2)</sup>                | I <sub>LOAD</sub> = 10 μA to 400 mA                                                                      |     | 20  | 40  | mV   |

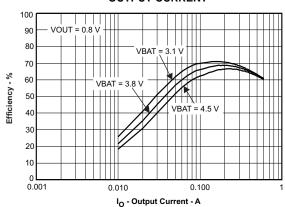

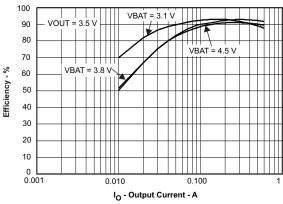

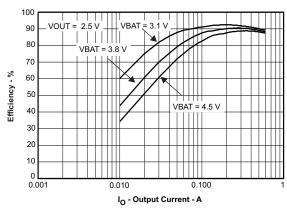

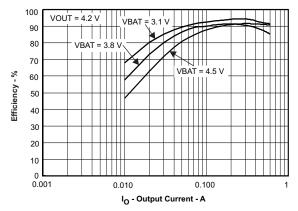

|                          |                                               | $VBAT \ge 4.0 \text{ V}, V_{0(BKBT)} = 3.5 \text{ V}, I_{LOAD} = 270 \text{ mA}$                         |     | 93% |     |      |

|                          |                                               | VBAT ≥ 3.1 V, V <sub>0(BKBT)</sub> = 4.0 V, I <sub>LOAD</sub> = 270 mA                                   |     | 90% |     |      |

|                          | Efficiency <sup>(2)</sup>                     | VBAT ≥ 3.1 V, V <sub>0(BKBT)</sub> = 2.5 V, I <sub>LOAD</sub> = 150 mA                                   |     | 90% |     |      |

|                          |                                               | $VBAT \ge 3.1 \text{ V}, V_{0(BKBT)} = 1.6 \text{ V}, I_{LOAD} = 90 \text{ mA}$                          |     | 80% |     |      |

|                          |                                               | VBAT ≥ 3.1 V, V <sub>0(BKBT)</sub> = 1.0 , I <sub>LOAD</sub> = 65 mA                                     |     | 70% |     |      |

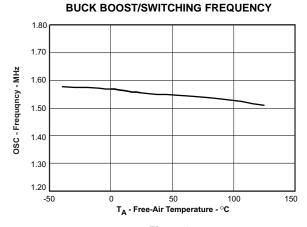

| f <sub>S</sub>           | Switching frequency                           |                                                                                                          | 1.2 | 1.5 | 1.8 | MHz  |

|                          | Max Duty                                      | Boost Mode                                                                                               | 40% | 50% | 60% |      |

| R <sub>DS(on)P</sub>     | P-channel MOSFET on resistance <sup>(2)</sup> |                                                                                                          |     | 150 |     | mΩ   |

| R <sub>DS(on)N</sub>     | N-channel MOSFET on resistance <sup>(2)</sup> |                                                                                                          |     | 150 |     | mΩ   |

|                          | Output ripple voltage <sup>(2)</sup>          | V <sub>O(BKBT)</sub> = 0.8 V ~ 4.2 V, I <sub>LOAD</sub> = 10 mA ~ 400 mA                                 |     |     | 100 | mVpp |

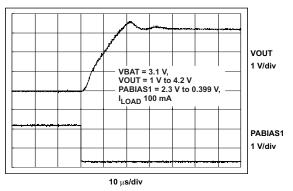

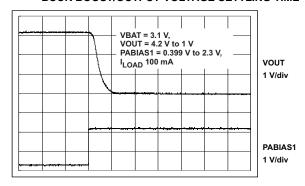

|                          |                                               | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 1 V to 4 V,<br>I <sub>LOAD</sub> = 100 mA                           |     | 25  | 50  | μs   |

|                          |                                               | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 4 V to 1 V,<br>I <sub>LOAD</sub> = 400 mA to 20 mA                  |     | 25  | 50  | μs   |

|                          |                                               | $VBAT = 4.2 \text{ V}, V_{0(BKBT)} = 1 \text{ V to } 1.5 \text{ V},$<br>$I_{LOAD} = 20 \text{ mA}$       |     | 25  | 50  | μs   |

|                          | Output voltage settling                       | $VBAT = 4.2 \text{ V}, \text{ V}_{0(BKBT)} = 2 \text{ V to } 2.5 \text{ V},$ $I_{LOAD} = 50 \text{ mA}$  |     | 25  | 50  | μs   |

|                          | time of buck mode <sup>(2)(3)</sup>           | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 3.5 V to 4 V,<br>I <sub>LOAD</sub> = 150 mA                         |     | 25  | 50  | μs   |

|                          |                                               | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 1.5 V to 1 V,<br>I <sub>LOAD</sub> = 150 mA to 20 mA                |     | 25  | 50  | μs   |

|                          |                                               | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 2.5 V to 2 V,<br>I <sub>LOAD</sub> = 200 mA to 50 mA                |     | 25  | 50  | μs   |

|                          |                                               | VBAT = 4.2 V, V <sub>0(BKBT)</sub> = 4 V to 3.5 V,<br>I <sub>LOAD</sub> = 400 mA to 150 mA               |     | 25  | 50  | μs   |

Using the reference EVM.

Not production tested. Specified by using the reference EVM.

Settling time measures ±0.2 V of the target V<sub>O(BKBT)</sub> voltage

|                       | PARAMETER                                        | TEST CONDITIONS                                                                                                                                                                                                                       | MIN                         | TYP                                                            | MAX                                                            | UNIT |

|-----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------|----------------------------------------------------------------|------|

|                       |                                                  | VBAT = 3.1 V, $V_{0(BKBT)}$ = 1 V to 4.2 V, $I_{LOAD}$ = 100 mA                                                                                                                                                                       |                             |                                                                | 50                                                             | μs   |

|                       | Output voltage settling                          | $\begin{split} \text{VBAT} &= 3.1 \text{ V}, \text{ V}_{0(\text{BKBT})} = 4.2 \text{ V to 1 V}, \\ \text{I}_{\text{LOAD}} &= 400 \text{ mA to 20 mA} \end{split}$                                                                     |                             |                                                                | 50                                                             | μs   |

|                       | time of boost mode <sup>(2)(3)</sup>             | VBAT = 3.1 V, $V_{0(BKBT)}$ = 3.5 V to 4.2 V, $I_{LOAD}$ = 400 mA                                                                                                                                                                     |                             |                                                                | 50                                                             | μs   |

|                       |                                                  | $\begin{split} \text{VBAT} &= 3.1 \text{ V}, \text{ V}_{0(\text{BKBT})} = 4.2 \text{ V to } 3.5 \text{ V}, \\ \text{I}_{\text{LOAD}} &= 400 \text{ mA to } 150 \text{ mA} \end{split}$                                                |                             |                                                                | 50                                                             | μs   |

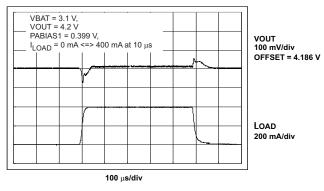

|                       |                                                  | VBAT = 4.2 V, $V_{0(BKBT)}$ = 1 V, $I_{LOAD}$ = 0 mA to 100 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                           |                             |                                                                | 200                                                            | mV   |

|                       | Output voltage shift peak voltage value (changed | VBAT = 4.2 V, $V_{0(BKBT)}$ = 2 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                           |                             |                                                                | 200                                                            | mV   |

|                       | load current) (2)                                | VBAT = 4.2 V, $V_{0(BKBT)}$ = 3.5 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 200                                                            | mV   |

|                       |                                                  | VBAT = 3.1 V, $V_{0(BKBT)}$ = 4.2 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 250                                                            | mV   |

|                       |                                                  | VBAT = 4.2 V, $V_{0(BKBT)}$ = 1 V, $I_{LOAD}$ = 0 mA to 100 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                           |                             |                                                                | 35                                                             | μs   |

|                       |                                                  | VBAT = 4.2 V, $V_{0(BKBT)}$ = 2 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                           |                             |                                                                | 35                                                             | μs   |

|                       | Output voltage shift                             | VBAT = 4.2 V, $V_{0(BKBT)}$ = 3.5 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 35                                                             | μs   |

|                       | convergence time<br>(changed load                | VBAT = 4.2 V, $V_{0(BKBT)}$ = 4 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                           |                             |                                                                | 35                                                             | μs   |

|                       | current) (4) (5)                                 | VBAT = 3.1 V, $V_{0(BKBT)}$ = 4.2 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 35                                                             | μs   |

|                       |                                                  | VBAT = 3.1 V, $V_{0(BKBT)}$ = 4.2 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 35                                                             | μs   |

|                       |                                                  | VBAT = 3.1 V, $V_{0(BKBT)}$ = 3.4 V, $I_{LOAD}$ = 0 mA to 400 mA, $I_{TR}/I_{TF}$ = 1 $\mu s$                                                                                                                                         |                             |                                                                | 35                                                             | μs   |

| R <sub>PABIAS1</sub>  | PABIAS1 input impedance                          |                                                                                                                                                                                                                                       | 100                         | 200                                                            |                                                                | kΩ   |

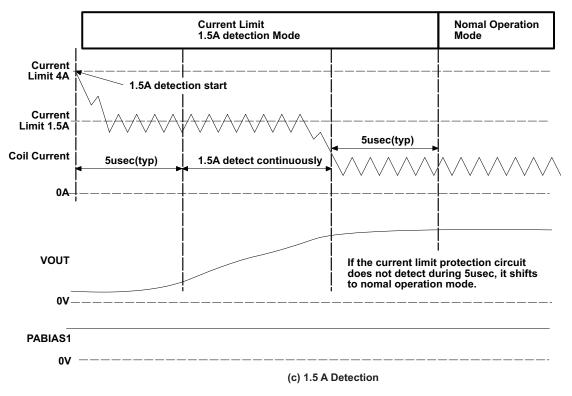

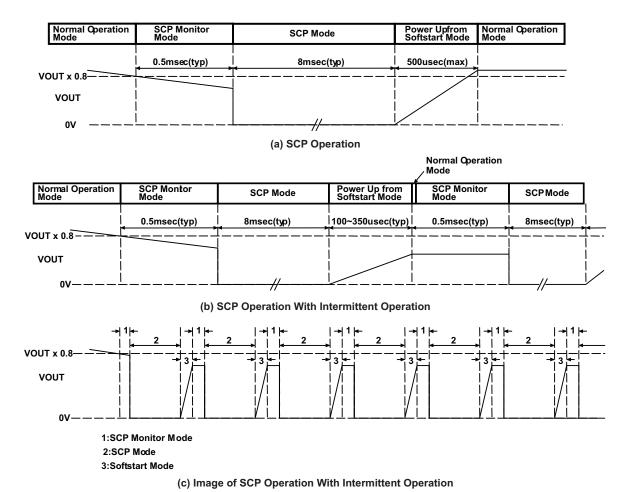

| V <sub>SCP</sub>      | Short circuit protection voltage (6)             | V <sub>0(BKBT)</sub> × 80% detection                                                                                                                                                                                                  | V <sub>0(BKBST)</sub> × 70% | $\begin{array}{c} \rm V_{0(BKBST)} \\ \times 80\% \end{array}$ | $\begin{array}{c} \rm V_{0(BKBST)} \\ \times 90\% \end{array}$ | ٧    |

|                       | SCP monitor mode count time                      | $V_{0(BKBT)} < V_{0(BKBT)} \times 80\%$                                                                                                                                                                                               |                             | 0.5                                                            |                                                                | ms   |

| t <sub>SCP</sub>      | SCP mode count time                              | Output P-channel MOSFETs are OFF, V <sub>0(BKBT)</sub> force to 0 V                                                                                                                                                                   |                             | 8                                                              |                                                                | ms   |

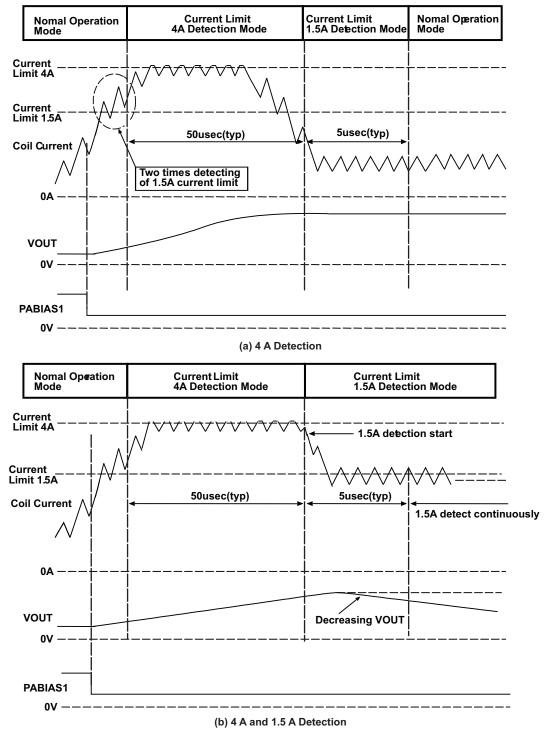

| I <sub>CL(BKBT)</sub> | Current limit protection (4)                     | VBAT = 3.8 V, $C_{OBKBT}$ = 10 $\mu$ F, $L_{1BKBT}$ = 2.2 $\mu$ H, $C_{ERRBKBT}$ = 1 nF, $T_A$ = 25°C                                                                                                                                 |                             | 1.5                                                            |                                                                | Α    |

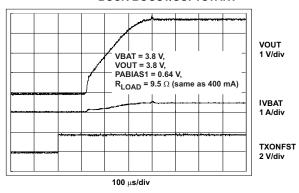

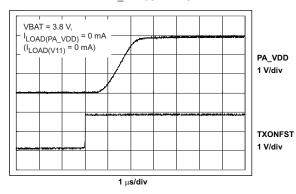

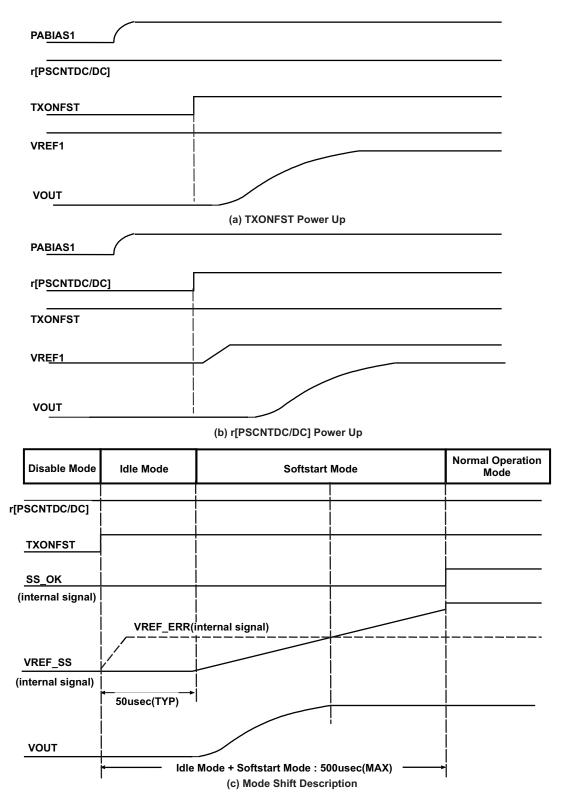

| too                   | Soft start ramp up time <sup>(4)</sup>           | $\begin{split} &V_{0(BKBT)} = 0.8 \text{ V} \sim 4.2 \text{ V}, \text{ I}_{LOAD} = 400 \text{ mA}, \\ &r[\text{PSCNTDC/DC}]^{(7)} = 1, \\ &TXONFST \text{ pin} = 0 \text{ V to V}_{VIO}, \text{ VOUT } \pm 0.2 \text{ V} \end{split}$ |                             |                                                                | 500                                                            | μs   |

| t <sub>SS</sub>       | Cont start famp up timet?                        | $\begin{aligned} &V_{O(BKBT)} = 0.8 \text{ V} \sim 4.2 \text{ V}, \text{ I}_{LOAD} = 400 \text{ mA}, \\ &TXONFST \text{ pin} = V_{VIO}, \text{ r[PSCNTDC/DC]} = 0 \text{ to 1}, \\ &VOUT \pm 0.2 \text{ V} \end{aligned}$             |                             |                                                                | 660                                                            | μs   |

$<sup>\</sup>begin{array}{ll} \text{(4)} & \text{Not production tested. Specified by using the reference EVM.} \\ \text{(5)} & \text{Convergence time measures} \pm 0.1 \text{ V of the target V}_{O(BKBT)} \text{ voltage} \\ \text{(6)} & \text{Tested at V}_{O(BKBT)} = 2.5 \text{ V} \\ \text{(7)} & \text{r[PSCNTDC/DC] is a name of register command by serial interface.} \\ \end{array}$

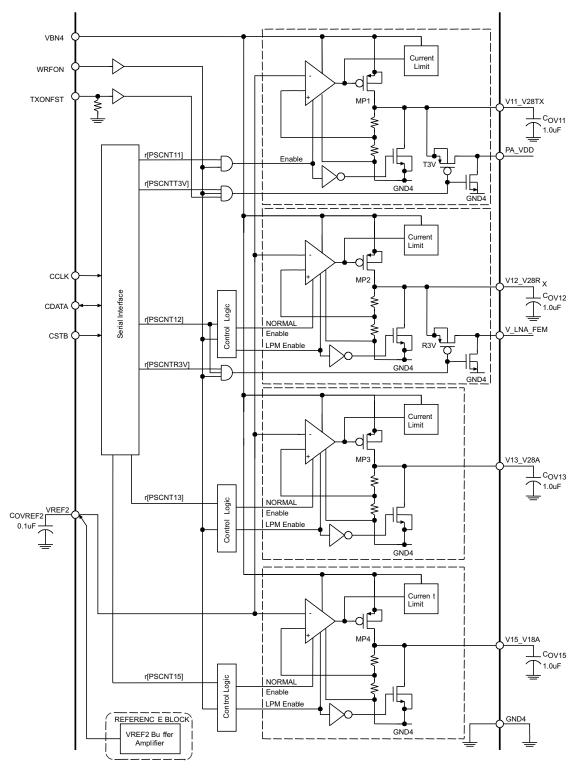

|                         | PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                                                                        | MIN  | TYP  | MAX  | UNIT  |

|-------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V11_V28TX               | (LOW DROPOUT OUTPUT)                 |                                                                                                                                                                                                                                                                        |      |      |      |       |

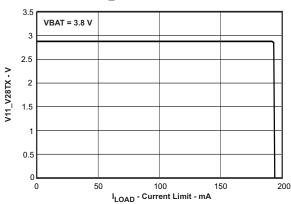

| V <sub>O(V11)</sub>     | Output voltage                       | $I_{LOAD(V11)} = 10 \text{ mA}$                                                                                                                                                                                                                                        | 2.79 | 2.85 | 2.92 | V     |

|                         | Maximum autaut aurrant               | PA_VDD is off                                                                                                                                                                                                                                                          |      |      | 130  | A     |

| I <sub>O(V11)</sub>     | Maximum output current               | PA_VDD is on, I <sub>LOAD(PA_VDD)</sub> = 20 mA                                                                                                                                                                                                                        |      |      | 110  | mA    |

| V <sub>O(V11_ACC)</sub> | Total output accuracy <sup>(1)</sup> |                                                                                                                                                                                                                                                                        | -4%  |      | 4%   |       |

| I <sub>CL(V11)</sub>    | Current limit protection             | V <sub>O(V11)</sub> = 0 V                                                                                                                                                                                                                                              |      | 170  | 280  | mA    |

| V <sub>SAT(V11)</sub>   | Output saturation voltage            |                                                                                                                                                                                                                                                                        |      |      | 0.3  | V     |

| I <sub>SD(V11)</sub>    | Shutdown current (2)                 | VBN4 pin at T <sub>A</sub> = 25°C                                                                                                                                                                                                                                      |      |      | 1    | μΑ    |

| I <sub>Q(V11)</sub>     | Quiescent current                    | VBN4 pin, $I_{LOAD(V11)}$ = 0 mA at $T_A$ = 25°C V12_V28RX, V13_V28A and V15_V18A are off                                                                                                                                                                              |      | 40   | 60   | μА    |

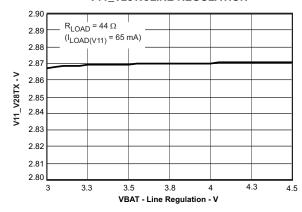

| V <sub>REG(V11)</sub>   | Line regulation                      | VBAT = $3.1 \text{ V} \sim 4.5 \text{ V}$ , $I_{\text{LOAD(V11)}} = 130 \text{ mA}$ , PA_VDD is off                                                                                                                                                                    |      | 0.1  | 0.4  | %/V   |

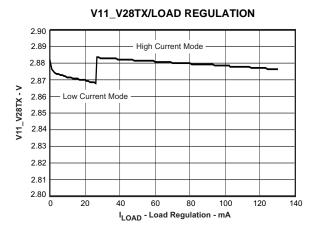

| I <sub>REG(V11)</sub>   | Load regulation (3)                  | $I_{LOAD(V11)}$ = 10 $\mu$ A to 130 mA PA_VDD is off                                                                                                                                                                                                                   |      | 50   | 100  | mV    |

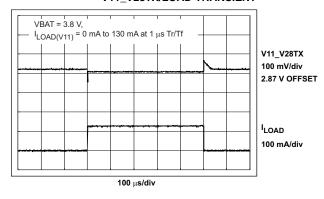

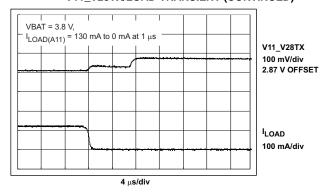

| _                       | L T (2)(4)                           | $I_{LOAD(V11)} = 10 \mu\text{A} \text{ to } 130 \text{mA}, I_{TR} = 1 \mu\text{s}$ 135                                                                                                                                                                                 | 165  | >/   |      |       |

| I <sub>TR(V11)</sub>    | Load Transient (3)(4)                | $I_{LOAD(V11)} = 130 \text{ mA to } 10 \mu\text{A}, I_{TF} = 1 \mu\text{s}$                                                                                                                                                                                            |      | 135  | 210  | mV    |

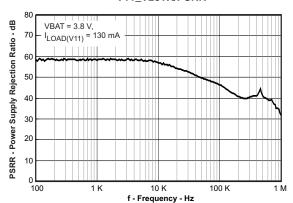

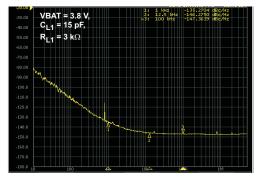

| 2022                    | Power supply ripple                  | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 1 kHz, I <sub>LOAD(V11)</sub> = 130 mA, PA_VDD is off                                                                                                                                                                              |      | 60   |      | dB    |

| PSRR <sub>(V11)</sub>   | rejection (3) (5)                    | VBAT = 3.8 V, $F_{RIPPLE}$ = 100 kHz, $I_{LOAD(V11)}$ = 130 mA, PA_VDD is off                                                                                                                                                                                          |      | 45   |      | dB    |

| V <sub>ON(V11)</sub>    | Output noise(3)                      | I <sub>LOAD(V11)</sub> = 5 mA, PA_VDD is off, 10 Hz to 100 kHz                                                                                                                                                                                                         |      | 30   |      | μVrms |

| t <sub>ST(V11)</sub>    | Startup time <sup>(3)</sup>          | $V_{O(V11)}$ > 90%, $I_{LOAD(V11)}$ = 10 μA to 130 mA r[PSCNT11] <sup>(6)</sup> = 1 and WRFON pin = 0 V to V <sub>VIO</sub> or WRFON pin = V <sub>VIO</sub> and r[PSCNT11] = 0 to 1                                                                                    |      |      | 500  | μs    |

| t <sub>F(V11)</sub>     | Output voltage falling time (3)      | $V_{O(V11)} > 10\%$ , $I_{LOAD(V11)} = 10$ mA r[PSCNT11] <sup>(6)</sup> = 1 and WRFON pin = $V_{VIO}$ to 0 V or WRFON pin = $V_{VIO}$ and r[PSCNT11] = 1 to 0                                                                                                          |      |      | 5    | ms    |

| PA_VDD                  |                                      |                                                                                                                                                                                                                                                                        |      |      |      | -     |

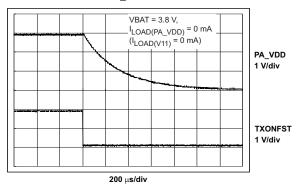

| V <sub>O(PA_VDD)</sub>  | Output voltage                       | V11_V28TX is on, $I_{LOAD(PA\_VDD)} = 20 \text{ mA}$ , $I_{LOAD(V11)} = 0 \text{ mA}$                                                                                                                                                                                  | 2.74 | 2.84 | 2.9  | ٧     |

| I <sub>O(PA_VDD)</sub>  | Maximum output current               | V11_V28TX is on                                                                                                                                                                                                                                                        |      |      | 20   | mA    |

| t <sub>ST(PA_VDD)</sub> | Startup time                         | $\begin{split} &V_{O(PA\_VDD)} > 90\%,\ I_{LOAD(PA\_VDD)} = 0\ mA\ ,\\ &VIO1V8\ pin = V_{VIO}\ and\ WRFON\ pin = V_{VIO}\\ &r[PSCNTT3V]^{(7)} = 1\ and\\ &TXONFST\ pin = 0\ V\ to\ V_{VIO},\ or\ TXONFST\ pin = V_{VIO}\\ ∧\ r[PSCNTT3V] = 0\ to\ 1^{(3)} \end{split}$ |      |      | 5    | μs    |

| t <sub>F(PA_VDD)</sub>  | Output voltage falling time          | $V_{O(PA\_VDD)}$ < 10%, $I_{LOAD(PA\_VDD)}$ = 0 mA,<br>TXONFST pin = $V_{VIO}$ to 0 $V$ , or WRFON pin = $V_{VIO}$ to 0 $V^{(3)}$ , or r[PSCNTT3V] = 1 to $O^{(3)}$                                                                                                    |      |      | 1.5  | ms    |

Total accuracy includes line and load regulation, temperature and process condition. It does not include load and line transients Shutdown current include V12\_V28RX, V13\_V28A and V15\_V18A2

<sup>(3)</sup> Not Production tested. Specified by using the reference EVM.

(4) The margin up to 2.7 V extends to the output voltage if COV11 is changed into 4.7 μ F. Specified by using the reference EVM.

<sup>(5)</sup> Ripple voltage =  $0.1 V_{PP}$

r[PSCNT11] is the name of a register command by serial interface.

r[PSCNTT3V] is the name of a register command by serial interface. The name of the switch is a T3V, and the name of the output pin is PA\_VDD.

|                            | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                         | MIN  | TYP  | MAX  | UNIT  |

|----------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V12_V28RX (L               | OW DROPOUT OUTPUT)                                              |                                                                                                                                                                                         |      |      |      |       |

|                            | Normal mode output voltage                                      | I <sub>LOAD(V12)</sub> = 10 mA                                                                                                                                                          | 2.79 | 2.85 | 2.92 |       |

| V <sub>O(V12)</sub>        | Low power mode output voltage                                   | I <sub>LOAD(V12)</sub> = 1 mA                                                                                                                                                           | 2.79 | 2.85 | 2.91 | V     |

|                            | Normal mode Maximum                                             | V_LNA_FEM is off                                                                                                                                                                        |      |      | 95   | mA    |

| I <sub>O(V12)</sub>        | output current                                                  | V_LNA_FEM is on, I <sub>LOAD(V_LNA_FEM)</sub> = 30 mA                                                                                                                                   |      |      | 65   | mA    |

| ·O(V12)                    | Low power mode maximum output current                           | V_LNA_FEM is off                                                                                                                                                                        |      |      | 5    | mA    |

| V <sub>O(V12_ACC)</sub>    | Total output accuracy <sup>(1)</sup>                            |                                                                                                                                                                                         | -4%  |      | 4%   |       |

| I <sub>CL(V12)</sub>       | Current limit protection (2)                                    | $V_{O(V12)} = 0 V$                                                                                                                                                                      |      | 160  | 270  | mA    |

| V <sub>SAT(V12)</sub>      | Output saturation voltage <sup>(2)</sup>                        |                                                                                                                                                                                         |      |      | 0.3  | V     |

| I <sub>SD(V12)</sub>       | Shutdown current <sup>(3)</sup>                                 | VBN4 pin at $T_A = 25^{\circ}C$                                                                                                                                                         |      |      | 1    | μΑ    |

| 1                          | Normal mode quiescent current                                   | VBN4 pin, $I_{LOAD(V12)}$ = 0 mA at $T_A$ = 25°C V11_V28TX, V13_V28A and V15_V18A are off                                                                                               |      | 40   | 60   |       |

| I <sub>Q(V12)</sub>        | Low power mode quiescent current                                | VBN4 pin, $I_{LOAD(V12)} = 0$ mA at $T_A = 25^{\circ}C$ V11_V28TX, V13_V28A and V15_V18A are off                                                                                        |      | 1.2  | 3    | μΑ    |

| V <sub>REG(V12)</sub>      | Line regulation <sup>(2)</sup>                                  | VBAT = 3.1 V $\sim$ 4.5 V, $I_{LOAD(V12)}$ = 95 mA, V_LNA_FEM is off                                                                                                                    |      | 0.1  | 0.4  | %/V   |

| I <sub>REG(V12)</sub>      | Load regulation (2)(4)                                          | $I_{LOAD(V12)}$ = 10 μA to 95 mA, V_LNA_FEM is off                                                                                                                                      |      | 50   | 100  | mV    |

| 1                          | Load Transiant (2) (4) (5)                                      | $I_{LOAD(V12)}$ = 10 $\mu$ A to 95 mA, $I_{TR}$ = 1 $\mu$ s                                                                                                                             |      | 130  | 160  | mV    |

| I <sub>TR(V12)</sub>       | Load Transient (2)(4)(3) $I_{LOAD(V12)} = 95 \text{ mA to } 10$ | $I_{LOAD(V12)}$ = 95 mA to 10 $\mu$ A, $I_{TF}$ = 1 $\mu$ s                                                                                                                             |      | 130  | 160  | mV    |

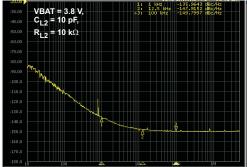

| Denn                       | Power supply ripple                                             | VBAT = 3.8 V, $F_{RIPPLE}$ = 1 kHz, $I_{LOAD(V12)}$ = 95 mA, V_LNA_FEM is off                                                                                                           |      | 60   |      | dB    |

| PSRR <sub>(V12)</sub>      | rejection (2)(4)(6)                                             | $\begin{split} & \text{VBAT} = 3.8 \text{ V, } \\ & \text{I}_{\text{LOAD(V12)}} = 95 \text{ mA, V} \\ & \text{LNA_FEM is off} \end{split}$                                              |      | 45   |      | dB    |

| V <sub>ON(V12)</sub>       | Output noise <sup>(2)(4)</sup>                                  | I <sub>LOAD(V12)</sub> = 5 mA, V_LNA_FEM is off,<br>10 Hz to 100 kHz                                                                                                                    |      | 30   |      | μVrms |

| t <sub>ST(V12)</sub>       | Startup time <sup>(2)(4)</sup>                                  | $V_{O(V12)} > 90\%$ , $I_{LOAD(V12)} = 10~\mu A$ to 95 mA VIO1V8 pin = 0 V to $V_{VIO}$ , or VIO1V8 pin = $V_{VIO}$ and WRFON pin = $V_{VIO}$ and r[PSCNT12] <sup>(7)</sup> = 0 to 1    |      |      | 500  | μs    |

| t <sub>F(V12)</sub>        | Output voltage falling time (4)                                 | $V_{O(V12)}$ < 10%, $I_{LOAD(V12)}$ = 0 mA,<br>DVIO1V8 pin = $V_{VIO}$ to 0 V, or r[PSCNT12] = 1 to 0                                                                                   |      |      | 5    | ms    |

| V_LNA_FEM                  |                                                                 |                                                                                                                                                                                         |      |      |      |       |

| V <sub>O(V_LNA_FEM)</sub>  | Output voltage <sup>(2)</sup>                                   | $V12\_V28RX$ is on $I_{LOAD(V\_LNA\_FEM)} = 30$ mA, $I_{LOAD(V12)} = 0$ mA                                                                                                              | 2.71 | 2.83 | 2.89 | V     |

| I <sub>O(V_LNA_FEM)</sub>  | Maximum output current <sup>(2)</sup>                           | V12_V28RX is on                                                                                                                                                                         |      |      | 30   | mA    |

| T <sub>ST(V_LNA_FEM)</sub> | Startup time <sup>(2)(4)</sup>                                  | $\begin{split} &V_{O(V\_LNA\_FEM)} > 90\%, \ I_{LOAD(V\_LNA\_FEM)} = 0 \ mA, \\ &r[PSCNT12] = 1 \ and \ r[PSCNTR3V]^{(5)} = 1 \ and \\ &WRFON \ pin = 0 \ V \ to \ V_{VIO} \end{split}$ |      |      | 5    | μs    |

| T <sub>F(V_LNA_FEM)</sub>  | Output voltage falling time (2)                                 | $V_{O(V\_LNA\_FEM)} < 10\%$ , $I_{LOAD(V\_LNA\_FEM)} = 0$ mA ,VIO1V8 pin = $V_{VIO}$ to 0 V, or r[PSCNT12] = 1 to $0^{(4)}$ , or r[PSCNTR3V] = 1 to $0^{(4)}$                           |      |      | 1.5  | ms    |

- Total accuracy includes line and load regulation, temperature and process condition. It does not include load and line transients

- Normal mode operation

- (3) Shutdown current include V11\_V28TX, V13\_V28A and V15\_V18A

(4) Not Production tested. Specified by using the reference EVM.

- The margin up to 2.7 V extends to the output voltage if COV12 is changed to 4.7 μF. Specified by using the reference EVM.

- (6) Ripple voltage =  $0.1 V_{PP}$

- r[PSCNT12] is a name of register command by serial interface. r[PSCNTR3V] is a name of register command by serial interface. The name of switch is a R3V and the name of output pin is V\_LNA\_FEM.

|                         | PARAMETER                                | TEST CONDITIONS                                                                                                                                                               | MIN  | TYP  | MAX  | UNIT  |

|-------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V13_V28A (              | LOW DROPOUT OUTPUT)                      |                                                                                                                                                                               |      |      |      |       |

| V                       | Normal mode output voltage               | I <sub>LOAD</sub> = 10 mA                                                                                                                                                     | 2.79 | 2.85 | 2.92 | V     |

| V <sub>O(V13)</sub>     | Low power mode output voltage            | I <sub>LOAD</sub> = 1 mA                                                                                                                                                      | 2.79 | 2.85 | 2.91 | V     |

|                         | Normal mode maximum output current       |                                                                                                                                                                               |      |      | 50   | mA    |

| I <sub>O(V13)</sub>     | Low power mode maximum output current    |                                                                                                                                                                               |      |      | 2    | mA    |

| V <sub>O(V13_ACC)</sub> | Total output accuracy <sup>(1)</sup>     |                                                                                                                                                                               | -4%  |      | 4%   |       |

| I <sub>CL(V13)</sub>    | Current limit protection <sup>(2)</sup>  | V <sub>O(V13)</sub> = 0 V                                                                                                                                                     |      | 100  | 210  | mA    |

| V <sub>SAT(V13)</sub>   | Output saturation voltage <sup>(2)</sup> |                                                                                                                                                                               |      |      | 0.3  | V     |

| I <sub>SD(V13)</sub>    | Shutdown current <sup>(3)</sup>          | VBN4 pin at T <sub>A</sub> = 25°C                                                                                                                                             |      |      | 1    | μΑ    |

|                         | Normal mode quiescent current            | VBN4 pin, $I_{LOAD}$ = 0 mA at $T_A$ = 25°C V11_V28TX, V12_V28RX and V15_V18A are off                                                                                         |      | 40   | 60   | ^     |

| I <sub>Q(V13)</sub>     | Low power mode quiescent current         | VBN4 pin, $I_{LOAD}$ = 0 mA at $T_A$ = 25°C V11_V28TX, V12_V28RX and V15_V18A are off                                                                                         |      | 1.2  | 3    | μΑ    |

| V <sub>REG(V13)</sub>   | Line regulation <sup>(2)</sup>           | VBAT = 3.1 V ~ 4.5 V, I <sub>LOAD</sub> = 50 mA                                                                                                                               |      | 0.1  | 0.4  | %/V   |

| I <sub>REG(V13)</sub>   | Load regulation (2)(4)                   | $I_{LOAD} = 10 \mu A \text{ to } 50 \text{ mA}$                                                                                                                               |      | 50   | 100  | mV    |

|                         | Load transient <sup>(2)(4)</sup>         | $I_{LOAD}$ = 10 $\mu$ A to 50 mA, $I_{TR}$ = 1 $\mu$ s                                                                                                                        |      | 110  | 150  | mV    |

| I <sub>TR(V13)</sub>    | Load transferit                          | $I_{LOAD}$ = 50 mA to 10 $\mu$ A, $I_{TF}$ = 1 $\mu$ s                                                                                                                        |      | 110  | 150  | mV    |

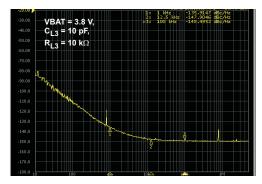

|                         | Power supply ripple                      | VBAT = 3.8 V, $F_{RIPPLE}$ = 1 kHz, $I_{LOAD}$ = 50 mA                                                                                                                        |      | 60   |      | dB    |

| PSRR <sub>(V13)</sub>   | rejection (2)(4)(5)                      | $VBAT = 3.8 \text{ V, } F_{RIPPLE} = 100 \text{ kHz,}$ $I_{LOAD} = 50 \text{ mA}$                                                                                             |      | 45   |      | dB    |

| V <sub>ON(V13)</sub>    | Output noise <sup>(2)(4)</sup>           | I <sub>LOAD</sub> = 5 mA, 10 Hz to 100 kHz                                                                                                                                    |      | 30   |      | μVrms |

| t <sub>ST(V13)</sub>    | Startup time <sup>(2)(4)</sup>           | $V_{O(V13)}$ $>$ 90%, $I_{LOAD}$ = 10 $\mu A$ to 50 mA , VIO1V8 pin = 0 V to $V_{VIO}$ , or VIO1V8 pin = $V_{VIO}$ and WRFON pin = $V_{VIO}$ and r[PSCNT13] $^{(6)}$ = 0 to 1 |      |      | 500  | μs    |

| t <sub>F(V13)</sub>     | Output voltage falling time (4)          | $V_{O(V13)}$ < 10%, $I_{LOAD}$ = 0 mA, VIO1V8 pin = $V_{VIO}$ to 0 V, or r[PSCNT13] = 1 to 0                                                                                  |      |      | 5    | ms    |

<sup>(1)</sup> Total accuracy includes line and load regulation, temperature and process condition. It does not include load and line transients

Normal mode operation

<sup>(2)</sup> Shutdown current include V11\_V28TX, V12\_V28RX and V15\_V18A1

Not production tested. Specified by using the reference EVM.

<sup>(5)</sup> Ripple voltage = 0.1 V<sub>PP</sub>

(6) r[PSCNT13] is a name of register command by serial interface.

|                         | PARAMETER                                | TEST CONDITIONS                                                                                                                                                                     | MIN  | TYP  | MAX  | UNIT        |

|-------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------|

| V15_V18A (              | LOW DROPOUT OUTPUT)                      |                                                                                                                                                                                     |      |      |      |             |

| V                       | Normal mode output voltage               | I <sub>LOAD</sub> = 5 mA                                                                                                                                                            | 1.81 | 1.85 | 1.89 | V           |

| V <sub>O(V15)</sub>     | Low power mode output voltage            | I <sub>LOAD</sub> = 1 mA                                                                                                                                                            | 1.81 | 1.85 | 1.89 | V           |

|                         | Normal mode maximum output current       |                                                                                                                                                                                     |      |      | 15   | mA          |

| I <sub>O(V15)</sub>     | Low power mode maximum output current    |                                                                                                                                                                                     |      |      | 2    | mA          |

| V <sub>O(V15_ACC)</sub> | Total output accuracy <sup>(1)</sup>     |                                                                                                                                                                                     | -4%  |      | 4%   |             |

| I <sub>CL(V15)</sub>    | Current limit protection <sup>(2)</sup>  | $V_{O(V15)} = 0 \text{ V}$                                                                                                                                                          |      | 60   | 170  | mA          |

| V <sub>SAT(V15)</sub>   | Output saturation voltage <sup>(2)</sup> |                                                                                                                                                                                     |      |      | 0.3  | V           |

| I <sub>SD(V15)</sub>    | Shutdown current <sup>(3)</sup>          | VBN4 pin at T <sub>A</sub> = 25°C                                                                                                                                                   |      |      | 1    | μΑ          |

|                         | Normal mode quiescent current            | VBN4 pin, $I_{LOAD} = 0$ mA at $T_A = 25^{\circ}C$ V11_V28TX, V12_V28RX and V13_V18A are off                                                                                        |      | 40   | 60   | A           |

| I <sub>Q(V15)</sub>     | Low power mode quiescent current         | VBN4 pin, $I_{LOAD} = 0$ mA at $T_A = 25^{\circ}C$ V11_V28TX, V12_V28RX and V13_V18A are off                                                                                        |      | 1.3  | 3    | μΑ          |

| V <sub>REG(V15)</sub>   | Line regulation <sup>(2)</sup>           | VBAT = 3.1 V ~ 4.5 V, I <sub>LOAD</sub> = 15 mA                                                                                                                                     |      | 0.1  | 0.4  | %/V         |

| I <sub>REG(V15)</sub>   | Load regulation (2)(4)                   | $I_{LOAD} = 10 \mu A \text{ to } 15 \text{ mA}$                                                                                                                                     |      | 50   | 100  | mV          |

| 1                       | Load transient (2)(4)                    | $I_{LOAD}$ = 10 $\mu$ A to 15 mA, $I_{TR}$ = 1 $\mu$ s                                                                                                                              |      | 70   | 100  | mV          |

| I <sub>TR(V15)</sub>    | Load transferit                          | $I_{LOAD}$ = 15 mA to 10 $\mu$ A, $I_{TF}$ = 1 $\mu$ s                                                                                                                              |      | 70   | 100  | mV          |

|                         | Power supply ripple                      | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 1 kHz, I <sub>LOAD</sub> = 15 mA                                                                                                                |      | 60   |      | dB          |

| PSRR <sub>(V15)</sub>   | rejection (2)(4)(5)                      | $VBAT = 3.8 \text{ V, } F_{RIPPLE} = 100 \text{ kHz,}$ $I_{LOAD} = 15 \text{ mA}$                                                                                                   |      | 45   |      | dB          |

| V <sub>ON(V15)</sub>    | Output noise (2)(4)                      | I <sub>LOAD</sub> = 5 mA, 10 Hz to 100 kHz                                                                                                                                          |      | 30   |      | $\mu V rms$ |

| t <sub>ST(V15)</sub>    | Startup time <sup>(2)(4)</sup>           | $$V_{O(V15)} > 90\%,\ I_{LOAD} = 10\ \mu A\ to\ 15\ mA\ ,$$VIO1V8\ pin = 0\ V\ to\ V_{VIO},\ or\ VIO1V8\ pin = V_{VIO}$ and WRFON pin = V_{VIO}\ and $r[PSCNT15]^{(6)} = 0\ to\ 1$$ |      |      | 500  | μs          |

| t <sub>F(V15)</sub>     | Output voltage falling time (4)          | $V_{O(V15)}$ < 10%, $I_{LOAD}$ = 0 mA, VIO1V8 pin = $V_{VIO}$ to 0 V, or r[PSCNT15] = 1 to 0                                                                                        |      |      | 5    | ms          |

| VBAT UNDE               | RVOLTAGE ELECTRICAL CHARAC               | TERISTICS <sup>(7)</sup>                                                                                                                                                            |      |      | ,    |             |

| M                       | Normal mode output voltage               | 271/41/PAT 424                                                                                                                                                                      |      | 1.85 |      | V           |

| V <sub>O(V15)</sub>     | Low power mode output voltage            | 2.7 V < VBAT < 3.1                                                                                                                                                                  |      | 1.85 |      | V           |

|                         |                                          |                                                                                                                                                                                     |      |      |      |             |

- (1) Total accuracy includes line and load regulation, temperature and process condition. It does not include load and line transients

- (2) Normal mode operation(3) Shutdown current includes V11\_V28TX, V12\_V28RX, and V13\_V28A

- (4) Not production tested. Specified by using the reference EVM.

- (5) Ripple voltage = 0.1 V<sub>PP</sub>

(6) r[PSCNT15] is a name of register command by serial interface.

- (7) V15 LDO is the only functional operation. The electrical characteristics are typical, but not specified.

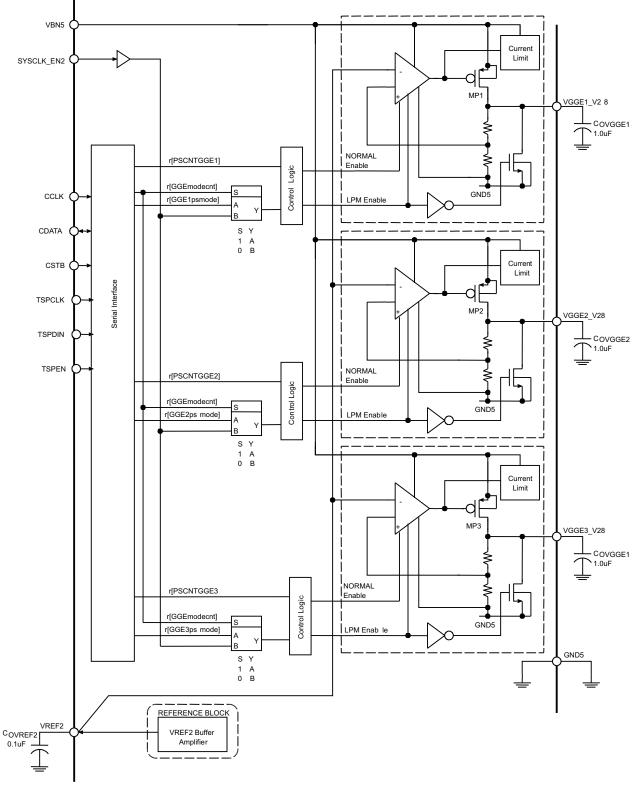

|                         | PARAMETER                                 | TEST CONDITIONS                                                                                                               | MIN  | TYP  | MAX  | UNIT  |

|-------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VGGE1_V28               | (LOW DROPOUT OUTPUT)                      |                                                                                                                               |      |      | ·    |       |

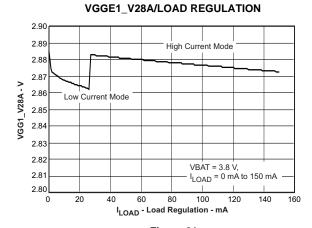

| V                       | Normal mode output voltage                | I <sub>LOAD</sub> = 10 mA                                                                                                     | 2.79 | 2.85 | 2.92 | V     |

| $V_{O(VG1)}$            | Low power mode output voltage             | I <sub>LOAD</sub> = 1 mA                                                                                                      | 2.79 | 2.85 | 2.91 | V     |

|                         | Normal mode maximum output current        |                                                                                                                               |      |      | 150  | mA    |

| I <sub>O(VG1)</sub>     | Low power mode maximum output current     |                                                                                                                               |      |      | 2    | mA    |

| V <sub>O(VG1_ACC)</sub> | Total output accuracy <sup>(1)</sup>      |                                                                                                                               | -4%  |      | 4%   |       |

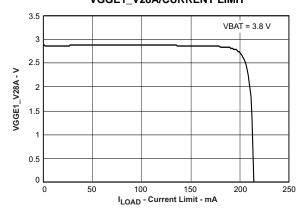

| I <sub>CL(VG1)</sub>    | Current limit protection <sup>(2)</sup>   | $V_{O(VG1)} = 0 V$                                                                                                            |      | 230  | 320  | mA    |

| V <sub>SAT(VG1)</sub>   | Output saturation voltage <sup>(2)</sup>  |                                                                                                                               |      |      | 0.3  | V     |

| I <sub>SD(VG1)</sub>    | Shutdown current <sup>(3)</sup>           | VBN5 pin at T <sub>A</sub> = 25°C                                                                                             |      |      | 1    | μΑ    |

|                         | Normal mode quiescent current             | VBN5 pin, I <sub>LOAD</sub> = 0 mA at T <sub>A</sub> = 25°C<br>VGGE2_V28, and VGGE3_V28 are off                               |      | 40   | 60   | ^     |

| I <sub>Q(VG1)</sub>     | Low power mode quiescent current          | VBN5 pin, I <sub>LOAD</sub> = 0 mA at T <sub>A</sub> = 25°C<br>VGGE2_V28, and VGGE3_V28 are off                               |      | 1.2  | 3    | μΑ    |

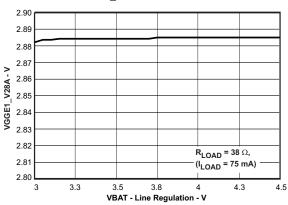

| V <sub>REG(VG1)</sub>   | Line regulation <sup>(2)</sup>            | VBAT = 3.1 V ~ 4.5 V, I <sub>LOAD</sub> = 150 mA                                                                              |      | 0.1  | 0.4  | %/V   |

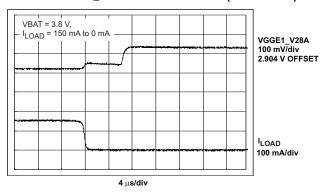

| I <sub>REG(VG1)</sub>   | Load regulation <sup>(2)(4)</sup>         | $I_{LOAD} = 10 \mu A \text{ to } 150 \text{ mA}$                                                                              |      | 50   | 100  | mV    |

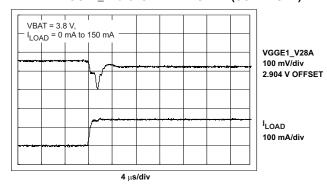

|                         | Land transition (2)(4)(5)                 | $I_{LOAD}$ = 10 $\mu$ A to 150 mA, $I_{TR}$ = 1 $\mu$ s                                                                       |      | 145  | 180  | mV    |

| I <sub>TR(VG1)</sub>    | Load transient (2)(4)(5)                  | $I_{LOAD}$ = 150 mA to 10 $\mu$ A, $I_{TF}$ = 1 $\mu$ s                                                                       |      | 145  | 230  | mV    |

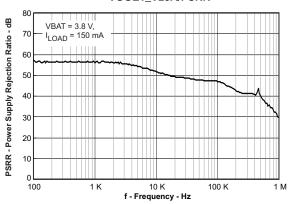

|                         | Davier events single                      | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 1 kHz, I <sub>LOAD</sub> = 150 mA                                                         |      | 60   |      | dB    |

| PSRR <sub>(VG1)</sub>   | Power supply ripple rejection (2) (4) (6) | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 100 kHz,<br>I <sub>LOAD</sub> = 150 mA                                                    |      | 45   |      | dB    |

| V <sub>ON(VG1)</sub>    | Output noise <sup>(2)(4)</sup>            | I <sub>LOAD</sub> = 5 mA, 10 Hz to 100 kHz                                                                                    |      | 30   |      | μVrms |

|                         |                                           | $V_{0(VG1)}$ > 90%, $I_{LOAD}$ = 10 $\mu A$ to 150 mA , REG_EN pin = 0 V to VBAT                                              |      |      | 850  | μs    |

| t <sub>ST(VG1)</sub>    | Startup time <sup>(2)(4)</sup>            | $V_{0(VG1)}$ > 90%, $I_{LOAD}$ = 10 $\mu A$ to 150 mA , REG_EN pin = VBAT and $r[PSCNTGGE1]^{(7)}$ = 0 to 1                   |      |      | 500  | μs    |

| t <sub>F(VG1)</sub>     | Output voltage falling time (4)           | V <sub>0(VG1)</sub> < 10%, I <sub>LOAD</sub> = 0 mA, REG_EN pin = VBAT to 0 V, or REG_EN pin = VBAT and r[PSCNTGGE1] = 1 to 0 |      |      | 5    | ms    |

| VBAT UNDE               | R VOLTAGE ELECTRICAL CHARAC               | TERISTICS(8)                                                                                                                  |      |      |      |       |

| V                       | Normal mode output voltage                | 3 V < VBAT < 3.1                                                                                                              |      | 2.85 |      | V     |

| $V_{O(VG1)}$            | Low power mode output voltage             | 3 V < VDA1 < 3.1                                                                                                              |      | 2.85 |      | V     |

- (1) Total accuracy includes line and load regulation, temperature and process condition. It does not include load and line transients

- (2) Normal mode operation

- (3) Shutdown current include VGGE2\_V28 and VGGE3\_V28.

- (4) Not Production tested. Specified by using the reference EVM.

- (5) The margin up to 2.7 V extends to the output voltage if COVGGE1 is changed to 4.7 μF. Specified by using the reference EVM.

- (6) Ripple voltage =  $0.1 V_{PP}$

- (7) r[PSCNTGGE1] is a name of register command by serial interface.

- (8) VGGE1\_V28 LDO is the only functional operation. The electrical characteristics are typical, but not specified.

Over recommended input conditions,  $T_A = -30^{\circ}\text{C}$  to 85°C, typical values are VBAT = 3.8 V, VIO1V8 = 1.85 V at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER               |                                            | TEST CONDITIONS                                                                                                            | MIN  | TYP  | MAX  | UNIT  |

|-------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VGGE2_V28               | (LOW DROPOUT OUTPUT)                       |                                                                                                                            |      |      |      |       |

| \/                      | Normal mode output voltage                 | I <sub>LOAD</sub> = 10 mA                                                                                                  | 2.79 | 2.85 | 2.92 | V     |

| $V_{O(VG2)}$            | Low power mode output voltage              | I <sub>LOAD</sub> = 1 mA                                                                                                   | 2.79 | 2.85 | 2.91 | V     |

| 1                       | Normal mode maximum output current         |                                                                                                                            |      |      | 150  | mA    |

| I <sub>O(VG2)</sub>     | Low power mode maximum output current      |                                                                                                                            |      |      | 2    | mA    |

| V <sub>O(VG2_ACC)</sub> | Total output accuracy <sup>(1)</sup>       |                                                                                                                            | -4%  |      | 4%   |       |

| I <sub>CL(VG2)</sub>    | Current limit protection (2)               | V <sub>(VG2)</sub> = 0 V                                                                                                   |      | 230  | 320  | mA    |

| V <sub>sat(VG2)</sub>   | Output saturation voltage <sup>(2)</sup>   |                                                                                                                            |      |      | 0.3  | V     |

| I <sub>SD(VG2)</sub>    | Shutdown current <sup>(3)</sup>            | VBN5 pin at T <sub>A</sub> = 25°C                                                                                          |      |      | 1    | μΑ    |

| 1                       | Normal mode quiescent current              | VBN5 pin, I <sub>LOAD</sub> = 0 mA at T <sub>A</sub> = 25°C<br>VGGE1_V28, and VGGE3_V28 are off                            |      | 40   | 60   | ^     |

| I <sub>Q(VG2)</sub>     | Low power mode quiescent current           | VBN5 pin, I <sub>LOAD</sub> = 0 mA at T <sub>A</sub> = 25°C<br>VGGE1_V28, and VGGE3_V28 are off                            |      | 1.2  | 3    | μΑ    |

| V <sub>REG(VG2)</sub>   | Line regulation <sup>(2)</sup>             | VBAT = 3.1 V ~ 4.5 V, I <sub>LOAD</sub> = 150 mA                                                                           |      | 0.1  | 0.4  | %/V   |

| I <sub>REG(VG2)</sub>   | Load regulation (2)(4)                     | $I_{LOAD}$ = 10 $\mu$ A to 150 mA                                                                                          |      | 50   | 100  | mV    |

|                         | L and transition (2)(4)(5)                 | $I_{LOAD}$ = 10 $\mu$ A to 150 mA, $I_{TR}$ = 1 $\mu$ s                                                                    |      | 145  | 180  | mV    |

| I <sub>TR(VG2)</sub>    | Load transient (2)(4)(5)                   | $I_{LOAD}$ = 150 mA to 10 $\mu$ A, $I_{TF}$ = 1 $\mu$ s                                                                    |      | 145  | 230  | mV    |

|                         | Daniel de la constante                     | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 1 kHz, I <sub>LOAD</sub> = 150 mA                                                      |      | 60   |      | dB    |

| PSRR <sub>(VG2)</sub>   | Power supply ripple rejection (2)(4)(6)    | VBAT = 3.8 V, F <sub>RIPPLE</sub> = 100 kHz,<br>I <sub>LOAD</sub> = 150 mA                                                 |      | 45   |      | dB    |

| V <sub>ON(VG2)</sub>    | Output noise <sup>(2)(4)</sup>             | I <sub>LOAD</sub> = 5 mA, 10 Hz to 100 kHz                                                                                 |      | 30   |      | μVrms |

|                         |                                            | $V_{O(VG2)}$ > 90%, $I_{LOAD}$ = 10 $\mu A$ to 150 mA, REG_EN pin = 0 V to VBAT                                            |      |      | 850  |       |

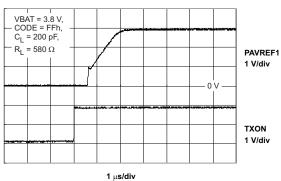

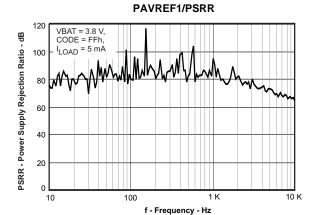

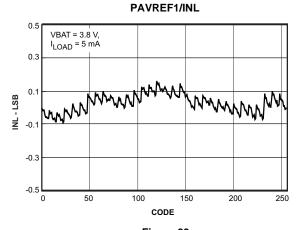

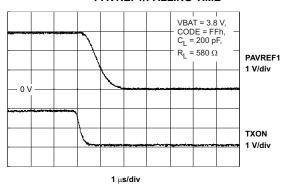

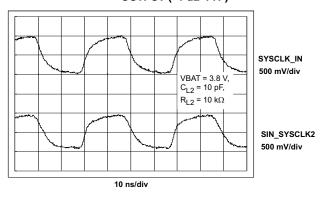

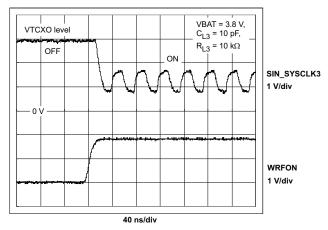

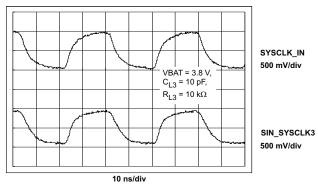

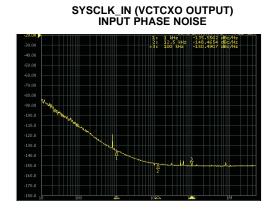

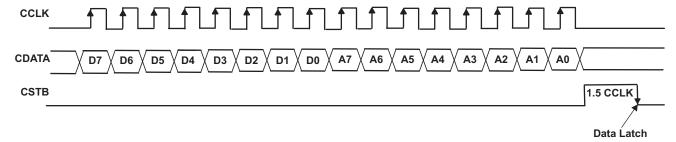

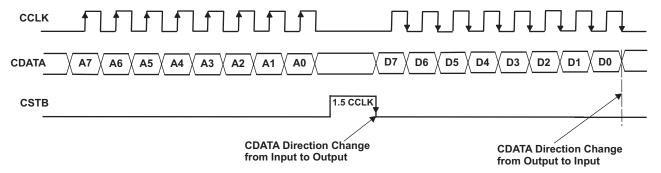

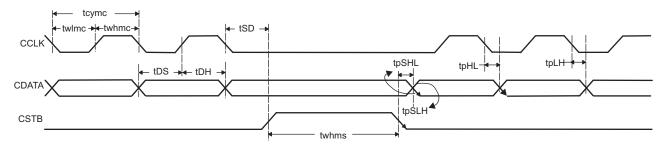

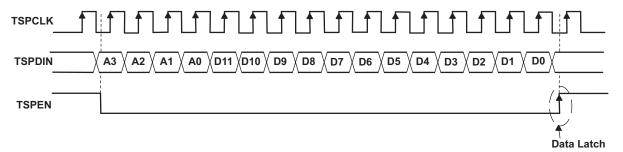

| t <sub>ST(VG2)</sub>    | Startup time (2)(4)                        | $V_{O(VG2)}$ > 90%, $I_{LOAD}$ = 10 μA to 150 mA, REG_EN pin = VBAT and r[PSCNTGGE2] <sup>(7)</sup> = 0 to 1               |      |      | 500  | μs    |